1.本发明涉及一种电路,且特别涉及一种全数字锁相回路电路(all digital phase locked loop circuit,简称adpll)及其相关反馈时钟微扰动装置。

背景技术:

2.请参照图1,其所示出为全数字锁相回路电路(adpll)示意图。全数字锁相回路电路100包括:一时间至数字转换器(time-to-digital converter,简称tdc)102、一回路滤波器(loop filter)104、数字控制振荡器(digitally controlled oscillator)106与除频元件(frequency dividing device)108。

3.在全数字锁相回路电路100中,参考振荡器(reference oscillator,未示出)产生具有一参考频率fref的参考时钟信号(reference clock signal,ckref)输入时间至数字转换器102。另外,除频元件108输出的反馈时钟信号(feedback clock signal,ckfb)也输入时间至数字转换器102。

4.时间至数字转换器102检测参考时钟信号ckref与反馈时钟信号ckfb的相位差异(phase difference)后,输出一相位误差数值(phase error value)verr至回路滤波器104。接着,回路滤波器104将相位误差数值verr转换为一控制数值(control value)vctrl至数字控制振荡器106。

5.数字控制振荡器106根据控制数值vctrl产生一输出时钟信号(output clock signal,ckout)。除频元件108接收输出时钟ckout,并将输出时钟ckout的频率除上一个除频值n后产生反馈时钟信号ckfb。其中,参考时钟信号ckref与反馈时钟信号ckfb的频率相同于参考频率fref,输出时钟ckout的频率为参考频率fref的n倍(亦即,n

×

fref)。

6.在全数字锁相回路电路100中,当参考时钟信号ckref与反馈时钟信号ckfb的相位差异小于一个tdc分辨率(tdc resolution)时,全数字锁相回路电路100会进入死区(deadband),并出现极限循环效应(limit cycle effect)。此时,时间至数字转换器102无法反应,导致抖动均方根值(rms jitter)大于预期。

7.在ieee transactions on circuits and systems i:vol.58,no.9,pp2051-2060,2001的国际期刊中,公开“spurious-free time-to-digital conversion in an adpll using short dithering sequences”。

8.请参照图2a,其所示出为现有运用于全数字锁相回路电路的中运用微扰动技术的示意图。相较于图1的全数字锁相回路电路100,其差异在于参考振荡器(reference oscillator,未示出)产生的参考时钟信号ckref先输入微扰动装置(dithering device)210并产生微扰动的参考时钟信号(dithered reference clock)ckref_d。

9.如图2a所示,微扰动装置210包括一数字至时间转换器(digital-to-time converter,简称dtc)212与一微扰动序列产生器(dithering sequence generator)214。微扰动序列产生器214接收微扰动指令与使能信号(dithering command&enable signal),产生微扰动信号nd至数字至时间转换器212。数字至时间转换器212根据微扰动信号nd来延迟

(delay)参考时钟信号ckref,并产生微扰动的参考时钟信号ckref_d。接着,时间至数字转换器202检测微扰动的参考时钟信号ckref_d与反馈时钟信号ckfb的相位差异后,输出一相位误差数值verr至回路滤波器(未示出)。

10.如图2b所示,其为现有运用于全数字锁相回路电路中除频值(n)与抖动均方根值(rms jitter)之间的关系示意图。明显地,全数字锁相回路电路中加入微扰动技术后,可以降低抖动均方根值。

技术实现要素:

11.本发明涉及一种全数字锁相回路电路,包括:一时间至数字转换器,接收一参考时钟信号与一反馈时钟信号,并产生一相位误差数值;一回路滤波器,接收该相位误差数值,并产生一控制数值;一数字控制振荡器,接收该控制数值,并产生一输出时钟信号;一反馈时钟微扰动装置,接收一输入数值,并根据该输入数值来处理该输出时钟信号,并产生该反馈时钟信号,其中该反馈时钟信号为一微扰动的反馈时钟信号。

12.为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合说明书附图,作详细说明如下:

附图说明

13.图1为全数字锁相回路电路(adpll)示意图。

14.图2a为现有运用于全数字锁相回路电路的中运用微扰动技术的示意图。

15.图2b为现有运用于全数字锁相回路电路中除频值(n)与抖动均方根值(rms jitter)之间的关系示意图。

16.图3a为本发明全数字锁相回路电路的第一实施例。

17.图3b与图3c为第一实施例全数字锁相回路电路在分数除频值与整数除频值时的抖动量的直方图。

18.图4a为本发明全数字锁相回路电路的第二实施例。

19.图4b与图4c为第二实施例全数字锁相回路电路在分数除频值与整数除频值时的抖动量的直方图。

20.100、300、400:全数字锁相回路电路

21.102、202、302:时间至数字转换器

22.104、304:回路滤波器

23.106、306:数字控制振荡器

24.108:除频元件

25.210:微扰动装置

26.212:数字至时间转换器

27.214:微扰动序列产生器

28.310、410:反馈时钟微扰动装置

29.312:除频器

30.314、416:

△-

σ调制器

31.321、323、325:积分器

element)356,且小数部分(fractional part)f输入积分器321的输入端。积分器321的输出端连接至积分器323的输入端。积分器323的输出端连接至积分器325的输入端。另外,积分器321的溢位端产生溢位信号o1,积分器323的溢位端产生溢位信号o2,积分器325的溢位端产生溢位信号o3。

43.延迟元件362的输入端接收溢位信号o3,输出端产生延迟的溢位信号(delayed overflow signal)o3d。算术元件(arithmetic element)352将溢位信号o3加上溢位信号o2减去延迟的溢位信号o3d后产生总和信号(sum signal)s1。

44.延迟元件364的输入端接收总和信号s1,输出端产生延迟的总和信号(delayed sum signal)s1d。算术元件354将溢位信号o1加上总和信号s1减去延迟的总和信号s1d后产生总和信号s2。再者,算术元件356将整数部分i与总和信号s2相加后产生整数信号m。

45.根据本发明的第一实施例,当戴而塔-辛格马调制器(

△-

σ调制器)314接收的输入数值in为分数时,戴而塔-辛格马调制器(

△-

σ调制器)314会产生时变的整数信号m。由于整数信号m持续地变化,造成微扰动的(dithered)反馈时钟信号ckfb,使得全数字锁相回路电路300不会进入死区(deadband),时间至数字转换器302维持其线性度(linearity),且不会出现极限循环效应(limit cycle effect)。

46.请参照图3b与图3c,其所示出为第一实施例全数字锁相回路电路在分数除频值与整数除频值时的抖动量(jitter amplitude)的直方图(histogram)。如图3b所示,当输入数值in为分数时,除频值n等效为分数的除频值(fractional n)。由于微扰动(dithered)的反馈时钟clfb输入时间至数字转换器(tdc)302,使得抖动量(jitter amplitude)的分布趋势类似高斯分布,代表全数字锁相回路电路300的时间至数字转换器302维持其线性度。

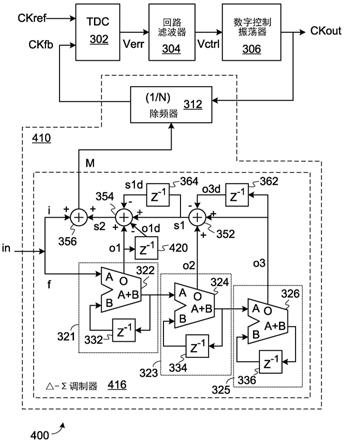

47.如图3c所示,当输入数值in为整数时,除频值n为整数的除频值(integr n)。此时,戴而塔-辛格马调制器(

△-

σ调制器)314产生的整数信号m不会变化,所以除频值n会维持在固定值,反馈时钟clfb将不会加入微扰动,使得抖动量(jitter amplitude)的分布混乱,代表全数字锁相回路电路300的时间至数字转换器302无法维持其线性度。

48.请参照图4a,其所示出为本发明全数字锁相回路电路的第二实施例。全数字锁相回路电路400包括:一时间至数字转换器302、一回路滤波器304、一数字控制振荡器306与一反馈时钟微扰动装置410。其中,反馈时钟微扰动装置410包括一除频器312与一戴而塔-辛格马调制器(

△-

σ调制器)416。

49.相较于第一实施例的全数字锁相回路电路300,其差异在于戴而塔-辛格马调制器(

△-

σ调制器)416中增加一延迟元件420。延迟元件420的输入端接收溢位信号o1,输出端产生延迟的溢位信号o1d。另外,算术元件354将溢位信号o1加上总和信号s1减去延迟的总和信号s1d减去延迟的溢位信号o1d后产生总和信号s2。

50.根据本发明的第二实施例,当戴而塔-辛格马调制器(

△-

σ调制器)416操作在整数模式时,由于延迟元件420会产生延迟的溢位信号o1d至算术元件354,使得算术元件354减去溢位信号o1,造成总和信号s2改变。因此,算术元件356将整数部分i与总和信号s2相加后会产生时变的(time variant)整数信号m至除频器312,造成微扰动的(dithered)反馈时钟信号ckfb。

51.举例来说,当反馈时钟微扰动装置410操作在非整数模式时,戴而塔-辛格马调制器(

△-

σ调制器)416中的延迟元件420会被禁能(disable),亦即延迟元件420输出的延迟

的溢位信号o1d为零,使得第二实施例全数字锁相回路电路400的运行相同于第一实施例的全数字锁相回路电路300。

52.另外,当反馈时钟微扰动装置410操作在整数模式时,戴而塔-辛格马调制器(

△-

σ调制器)416中的延迟元件420会使能(enable),同时输入数值in的小数部分(fractional part)f会设定成一个指定的分数。由于延迟元件420会产生延迟的溢位信号o1d至算术元件354,使得算术元件354减去溢位信号o1,使得反馈时钟微扰动装置410会输出等效整数的除频值n,但是仍可产生微扰动的(dithered)反馈时钟信号ckfb,使得全数字锁相回路电路400拥有跟非整数模式一样好的线性度。

53.再者,由于戴而塔-辛格马调制器(

△-

σ调制器)416切换整数信号m的次数会随小数部分(fractional part)f的设定而改变。为了让戴而塔-辛格马调制器(

△-

σ调制器)416可以频繁的改变整数信号m,在实际的运行上可以将小数部分(fractional part)f设定在0.5附近,而不设定在靠近整数附近的数值,例如0.1或者0.9。再者,由于戴而塔-辛格马调制器(

△-

σ调制器)416的特性,如果设定的小数部分(fractional part)f会被2的幂次方所整除时,戴而塔-辛格马调制器(

△-

σ调制器)416切换整数信号m的次数会较少。因此,可以将小数部分(fractional part)f设定为不会被2的幂次方整除的数字,例如0.53。

54.请参照图4b与图4c,其所示出为第二实施例全数字锁相回路电路在分数除频值与整数除频值时的抖动量的直方图。如图4b与图4c所示,除频值n为分数的除频值(fractional n)或者是整数的除频值(integer n)时,由于微扰动(dithered)的反馈时钟clfb输入时间至数字转换器(tdc)302,使得抖动量(jitter amplitude)的分布趋势类似高斯分布,代表全数字锁相回路电路400的时间至数字转换器302皆可维持其线性度。换言之,本发明在全数字锁相回路电路中加入微扰动的反馈时钟信号后,确实可改善全数字锁相回路电路的线性度,并达到更好的抖动表现(jitter performance)。

55.由以上的说明可知,本发明提出一种全数字锁相回路电路及其相关反馈时钟微扰动装置。在全数字锁相回路电路中,利用反馈时钟微扰动装置来将输出时钟ckout转换为反馈时钟ckfb。再者,本发明的戴而塔-辛格马调制器(

△-

σ调制器)314接收整数的输入数值in时,仍能产生变动的整数信号m至除频器,并产生微扰动(dithered)的反馈时钟ckfb,使得时间至数字转换器(tdc)302维持其线性度。

56.综上所述,虽然本发明已以优选实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作各种的变动与润饰。因此,本发明的保护范围当视后附的权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。