1.本发明属于电力电子技术领域,涉及一种三电平半导体开关管门极驱动电路。

背景技术:

2.近几年快速发展的宽禁带半导体包括sic

‑

mosfet与gan

‑

hemt等,具有高开关速度、低开关损耗、热稳定性好,热导率高等优势,已广泛应用于航空电源、新能源汽车变换器射频与微波等领域,为实现高功率密度、高效率的电力电子设备提供了条件。

3.为进一步提升宽禁带器件如sic

‑

mosfet开关的频率、效率和功率密度,重点是降低在高频工况下开关损耗,然而多个sic

‑

mosfet并联或者sic

‑

mosfet/si

‑

igbt混合并联应用时,现有的驱动电路不能提供足够的瞬时电流,使得开关损耗增加,成为降低开关损耗的主要瓶颈,亟需克服。

技术实现要素:

4.本发明的目的是提供一种三电平半导体开关管门极驱动电路,解决了现有技术中在多个sic

‑

mosfet并联或sic

‑

mosfet/si

‑

igbt并联应用时难以提供足够大的开通电流,开关损耗大,驱动电路触发模式少,无法适用更多的工况需求的问题。

5.本发明所采用的技术方案是,一种三电平半导体开关管门极驱动电路,包括4个mos管,分别称为m1、m2、m3、m4,其中的m2和m4为低压n沟道mosfet,m1和m3为低压p沟道mosfet;m1的漏极与m2的漏极相连,m1的栅极与m2的栅极相连,m1的源极和m2的源极共同连接有pwm信号a;m3的漏极与m4的漏极相连,m3的栅极与m4的栅极相连,m3的源极和m4的源极共同连接有pwm信号b;m1的漏极和m2的漏极共同通过电容c与m3的源极连接;vcc的负极与vee的正极相连并且接地,vcc的正极与m1的源极连接,vcc的正极通过二极管d与m3的源极及电容c连接;m3的漏极和m4的漏极共同输出驱动电路的输出信号。

6.本发明的三电平半导体开关管门极驱动电路,其特征还在于:

7.所述的pwm信号a是由负载电路中m6的漏极与源极的电压经过比较器处理后得到,该pwm信号a用于驱动m1和m2,当pwm信号a为高电平时,m2导通,当pwm信号a为低电平时,m1导通。

8.所述的pwm信号b由脉冲电源提供,该pwm信号b用于驱动m3和m4,当pwm信号b为高电平时,m4导通,当pwm信号b为低电平时,m3导通。

9.所述的vcc与vee都是正电压的直流电压源。

10.所述的输出信号与负载电路直接相连。

11.本发明的有益效果是,1)在同样具有三电平驱动功能的驱动电路中,本发明的驱动电路结构所需的器件更少,成本更低;2)通过调节rc延迟网络参数变化实现多个触发模式,既适用于驱动多个sic

‑

mosfet并联,也可满足sic

‑

mosfet与si

‑

igbt混合并联应用的模式需求;3)在开关管开通过程中可以提供更大的驱动电流,可有效减小系统的开关损耗,提高系统效率。

附图说明

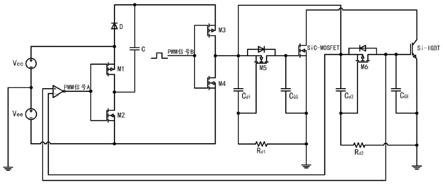

12.图1是本发明门极驱动电路及负载电路实施例的拓扑结构图;

13.图2a是本发明在si

‑

igbt开通延时、si

‑

mosfet关断延时的波形图;

14.图2b是本发明在sic

‑

mosfet和si

‑

igbt同时开通,si

‑

mosfet关断延时的波形图;

15.图2c是本发明在si

‑

igbt和si

‑

mosfet同时开通和关断的波形图(亦可应用于多个sic

‑

mosfet的并联工况);

16.图3是本发明在sic

‑

mosfet和si

‑

igbt关断时的电路状态图;

17.图4是本发明在sic

‑

mosfet先开通,si

‑

igbt开通延时电路状态图;

18.图5是本发明在sic

‑

mosfet和si

‑

igbt在开通过程中承受高驱动电压的电路状态图;

19.图6是本发明在sic

‑

mosfet和si

‑

igbt完全导通后的电路状态图;

20.图7是本发明在si

‑

igbt先关断,sic

‑

mosfet关断延时电路状态图。

具体实施方式

21.下面结合附图和具体实施方式对本发明进行详细说明。

22.参照图1,本发明门极驱动电路的结构是,包括4个mos管,分别称为m1、m2、m3、m4,其中的m2和m4为低压n沟道mosfet,m1和m3为低压p沟道mosfet;m1的漏极与m2的漏极相连,m1的栅极与m2的栅极相连,m1的源极和m2的源极共同连接有pwm信号a(附图中简写为信号a),该pwm信号a是由负载电路中m6的漏极与源极的电压经过比较器处理后得到,该pwm信号a用于驱动m1和m2,当pwm信号a为高电平时,m2导通,当pwm信号a为低电平时,m1导通;m3的漏极与m4的漏极相连,m3的栅极与m4的栅极相连,m3的源极和m4的源极共同连接有pwm信号b(附图中简写为信号b),该pwm信号b由脉冲电源提供,该pwm信号b用于驱动m3和m4,当pwm信号b为高电平时,m4导通,当pwm信号b为低电平时,m3导通;m1的漏极和m2的漏极共同通过电容c与m3的源极连接;vcc与vee都是正电压的直流电压源,vcc的负极与vee的正极相连并且接地,vcc的正极与m1的源极连接,vcc的正极通过二极管d与m3的源极及电容c连接;m3的漏极和m4的漏极共同输出驱动电路的输出信号,输出信号与负载电路直接相连。

23.参照图1,负载电路以sic

‑

mosfet和si

‑

igbt混合并联为例,电容c

gs

是sic

‑

mosfet的栅极寄生电容,电容c

ge

是si

‑

igbt的栅极寄生电容,电容c

d1

和电阻r

d1

用于控制sic

‑

mosfet的关断延迟,电容c

d2

和电阻r

d2

用于控制si

‑

igbt的开通延迟,m5选用的是低压n沟道mosfet,m6选用的是低压p沟道mosfet,m5控制sic

‑

mosfet的开通和关断,m6控制si

‑

igbt的开通和关断。

24.本发明的工作过程是,负载电路以图1所示的sic

‑

mosfet和si

‑

igbt混合并联为例,具体控制过程如下:

25.1)当pwm信号a和pwm信号b同时为高电平时,m2和m4(n沟道)导通,电容c两端电势差为vcc vee,驱动电路的输出电压为

‑

vee(负压),此时m5和m6的栅极驱动电压为正压,所以m5处于导通状态,m6处于关断状态,此时负载端的sic

‑

mosfet和si

‑

igbt处于关断状态。这一阶段的电路状态图如图3所示。

26.2)pwm信号a和pwm信号b同时为低电平时,m2和m4截止,m1和m3导通,在m1导通的瞬间电容c下端电压立刻变为vcc,导致电容c的上端电压突变为vcc (vcc vee),驱动电路的

输出电压也突变为vcc (vcc vee)。因驱动电路的输出电压为正压,m5处于关断状态,但驱动电流直接通过m5的寄生二极管给c

gs

(sic

‑

mosfet的栅极寄生电容)充电,所以sic

‑

mosfet会立即接通,sic

‑

mosfet的驱动电压为驱动电路的输出电压。同时驱动电流给电容c

d2

和m6的寄生电容充电,直到m6的栅极驱动电压达到阈值电压后导通,进而接通si

‑

igbt,所以sic

‑

mosfet可以早于si

‑

igbt导通。若将c

d2

的电容值设置的很小或者删掉c

d2

,则m6也会立即导通,那么si

‑

igbt会和sic

‑

mosfet同时导通。

27.图2a中t1~t2为si

‑

igbt的导通延迟时间,电路状态图如图4所示。图2b和图2c中t1~t2这一时间段,si

‑

igbt和sic

‑

mosfet的驱动电压都等于vcc (vcc vee),状态原理图如图5所示。

28.3)pwm信号a为高电平,pwm信号b仍为低电平时,m1由导通变为关断,m2由关断变为导通,m3和m4依旧保持前一状态不变,电容c的下端电压会瞬间由vcc变为

‑

vee,上端电压会瞬间由vcc (vcc vee)变为vcc,驱动电路的输出电压变为vcc。负载电路一侧器件的导通及关断状态不变。在这一时间段si

‑

igbt和sic

‑

mosfet处于完全导通的状态,电路状态图如图6所示,对应图2a、图2b及图2c各模式中的t2~t3。

29.4)pwm信号a维持在高电平,pwm信号b由低电平变为高电平时,m3关断,m4导通,驱动电路输出电压变为

‑

vee(负压),m6处于关断状态,si

‑

igbt的寄生电容c

ge

通过m6的寄生二极管放电,因c

ge

电容值非常小,所以si

‑

igbt会立即关断。同时驱动电流给电容c

d1

和m5的栅极寄生电容充电,直到m5的栅极驱动电压达到阈值电压后导通,m5被导通后,sic

‑

mosfet的栅极寄生电容c

gs

经过m5放电,进而关断sic

‑

mosfet,所以sic

‑

mosfet可以晚于si

‑

igbt关断。若将c

d1

的电容值设置的很小或者删掉c

d1

,则m5也会立即导通,则si

‑

igbt会和sic

‑

mosfet同时关断。

30.图2a和图2b中t3~t4为sic

‑

mosfet的关断延迟时间,电路状态图如图7所示。

31.综上所述,本发明的拓扑结构,在sic

‑

mosfet的开通过程中提供更高的驱动电压,实现mosfet的快速开通,而在器件完全导通后驱动电压又降到标准值,有效解决sic

‑

mosfet并联和sic

‑

mosfet/si

‑

igbt混合开关在开通过程中因驱动电流不足引起的开通损耗增大问题,提升系统转换效率。在控制过程中,驱动电路中的pwm信号a是由负载电路中m6的漏极和源极电压经比较器所得到的pwm信号,在一个周期里,pwm信号a的下降沿同时或略晚于pwm信号b的下降沿的到来,但pwm信号a的占空比远大于pwm信号b,使得驱动电路的输出电压在pwm信号a处于低电平期间迅速增加(sic

‑

mosfet和si

‑

igbt在开通过程中获得较高的驱动电压),pwm信号a经过短暂的低电平后会立即变为高电平,形成驱动电压经过短暂的升压后会立即降为标准电压(sic

‑

mosfet和si

‑

igbt完全导通后驱动电压恢复到标准值),为sic

‑

mosfet/si

‑

igbt混合并联提供不同的触发时序,m6、电容c

d2

和电阻r

d2

控制si

‑

igbt的开通延迟时间;m5、电容c

d1

和电阻r

d1

控制sic

‑

mosfet的关断延迟时间。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。