1.本发明涉及数字电子系统中波形合成的技术领域,尤其涉及一种频谱纯度优化的任意波形合成电路装置。

背景技术:

2.随着电子计算机技术、通信技术的快速发展,电子通信系统对于信号频率的准确度和稳定性要求越来越高,频率合成技术自出现后便受到广泛关注。作为第三代频率合成技术的直接数字频率合成技术(dds),它采用数字的方法实现了波形可调、频率可控的同时,还具有波形频率高,频率分辨率高以及可快速改变波形的特点。由于其能够充分利用数字电路的可编程特性、具有更高的集成度和更低的成本,目前dds在许多数字通信系统中得到了广泛的应用。

3.主流的dds实现结构100如图1所示,包含相位发生器101、移相加法器102、相位截断模块103、波形查找表104、数模转换器105以及低通滤波器106,其中通过数字电路实现的部分有相位发生器101、移相加法器102和相位截断模块103及波形查找表104。

4.目前实现直接数字频率波形的过程中通常很容易会产生误差,一般包括相位截断误差,查找表幅值量化误差。误差产生的原因是:查找表深度和宽度的限制所带来的相位上的截断误差和幅度上的舍入误差。相位截断误差由相位位宽截断造成,n为相位累加器位宽,k为查找表地址位宽,b=n

‑

k为相位截断位宽。相位发生器产生相位,经过移相加法器输出带偏移的相位。由于相位发生器位宽n大于查找表地址位宽k,通常取相位的高k位用于查找表的地址寻址。查找表对于相位发生器只是提供了一部分数据,在这些数据之外,输出只是一个对上一个值的保持,直到下一个值到来,相位截断误差由此产生。理论上希望n尽可能的大,n越大输出波形质量越好,但是实际上n越大所需要的查找表地址越大,即查找表本身的深度也就越大,会消耗大量资源。同时由于在波形生成的过程中,相位截断会形成周期性的误差,相位截断误差在频谱上呈多个单独的谱线,表现为谐波,导致波形频谱纯度降低。

技术实现要素:

5.为克服现有技术的缺陷,本发明要解决的技术问题是提供了一种频谱纯度优化的任意波形合成电路装置,其能够解决由相位截断误差带来的波形频谱纯度低、杂散范围大的问题,硬件开销小。

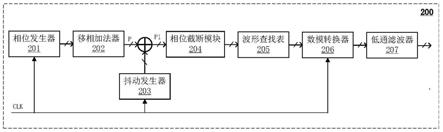

6.本发明的技术方案是:这种频谱纯度优化的任意波形合成电路装置(200),其包括:相位发生器(201)、移相加法器(202)、抖动发生器(203)、相位截断模块(204)、波形查找表(205)、数模转换器(206)以及低通滤波器(207);

7.相位发生器(201)包括:频率控制字(301)、n位全加器(302)和相位寄存器(303);移相加法器(202)为n位全加器;在系统时钟的控制下,对相位以频率控制字为梯度进行累加操作,将累加结果保存在相位寄存器,同时也将累加结果输出送至移相加法器中,进行相

位偏移处理得到带相位偏移的相位;

8.抖动发生器(203)随机生成信号,由多个r/s电路(401)并联,达到随机产生n比特随机信号,将n位相位输出结果与n位随机信号进行叠加,产生带扰动信号的相位;

9.将带扰动信号的相位送至相位截断模块(204),获取高有效k位数据和低无效b位数据,其中b k=n,直接将高有效k位数据用于波形查找表(205)地址寻址,然后输出波形数据。

10.本发明的相位发生器在系统时钟的控制下,对相位以频率控制字为梯度进行累加操作,将累加结果保存在相位寄存器,同时也将累加结果输出送至移相加法器中,进行相位偏移处理得到带相位偏移的相位,因此工作频率宽,频率分辨率高;针对相位截断带来的周期误差,将带扰动信号的相位送至相位截断模块,打乱周期性,从而进一步减小输出波形的频谱杂散,因此能够解决由相位截断误差带来的波形频谱纯度低、杂散范围大的问题;只增加一个抖动发生器,抖动发生器产生的干扰信号与相位数据叠加,抖动发生器通过r/s电路实现,增加很少的电路资源开销,可以在不增加查找表消耗量,也不增加其他数据计算单元的条件下,就可以实现有效的降低相位截断噪声。

11.还提供了一种频谱纯度优化的任意波形合成电路装置的工作方法,对相位引入一个干扰信号q,打破由相位截断产生的周期性,

12.扰动信号产生机制:p表示带相位偏移的输出相位,q表示抖动发生器中产生的干扰信号,p1表示经过抖动发生器叠加处理后的相位;单元电路采用r/s电路,由两个与非门构成;当系统时钟处于低电平时,此时q和均为1,但当时钟上升沿到来时,q和的值处于不确定状态,但两者必定一个为0,另一个为1;根据相位发生器需要截断的位宽确定r/s单元电路需要的个数,这里为b个r/s单元电路;此外由于相位发生器输出相位位宽为n,这里在对q进行高n

‑

b位0值,将q位宽拓展到n位。

附图说明

13.图1示出了现有技术中主流的dds实现结构。

14.图2是根据本发明的频谱纯度优化的任意波形合成电路装置的结构示意图。

15.图3是根据本发明的频谱纯度优化的任意波形合成电路装置的相位发生器的结构示意图。

16.图4是根据本发明的频谱纯度优化的任意波形合成电路装置的抖动发生器的结构示意图。

具体实施方式

17.为了使本发明的目的、技术方案及优点更加清楚明白,下面结合附图和具体实施例对本发明作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

18.为了使本揭示内容的叙述更加详尽与完备,下文针对本发明的实施方式与具体实施例提出了说明性的描述;但这并非实施或运用本发明具体实施例的唯一形式。实施方式中涵盖了多个具体实施例的特征以及用以建构与操作这些具体实施例的方法步骤与其顺

序。然而,亦可利用其它具体实施例来达成相同或均等的功能与步骤顺序。

19.如图2所示,这种频谱纯度优化的任意波形合成电路装置200,其包括:相位发生器201、移相加法器202、抖动发生器203、相位截断模块204、波形查找表205、数模转换器206以及低通滤波器207;

20.相位发生器201包括:频率控制字301、n位全加器302和相位寄存器303;移相加法器202为n位全加器;在系统时钟的控制下,对相位以频率控制字为梯度进行累加操作,将累加结果保存在相位寄存器,同时也将累加结果输出送至移相加法器中,进行相位偏移处理得到带相位偏移的相位;

21.抖动发生器203随机生成信号,由多个r/s电路401并联,达到随机产生n比特随机信号,将n位相位输出结果与n位随机信号进行叠加,产生带扰动信号的相位;

22.将带扰动信号的相位送至相位截断模块204,获取高有效k位数据和低无效b位数据,其中b k=n,直接将高有效k位数据用于波形查找表205地址寻址,然后输出波形数据。

23.本发明的相位发生器在系统时钟的控制下,对相位以频率控制字为梯度进行累加操作,将累加结果保存在相位寄存器,同时也将累加结果输出送至移相加法器中,进行相位偏移处理得到带相位偏移的相位,因此工作频率宽,频率分辨率高;针对相位截断带来的周期误差,将带扰动信号的相位送至相位截断模块,打乱周期性,从而进一步减小输出波形的频谱杂散,因此能够解决由相位截断误差带来的波形频谱纯度低、杂散范围大的问题;只增加一个抖动发生器,抖动发生器产生的干扰信号与相位数据叠加,抖动发生器通过r/s电路实现,增加很少的电路资源开销,可以在不增加查找表消耗量,也不增加其他数据计算单元的条件下,就可以实现有效的降低相位截断噪声。

24.优选地,所述全加器为kogge

‑

stone树形加法器。这样能够进一步降低工作延迟,从而达到提升系统性能的目的。

25.优选地,所述波形查找表205采用同步双端口ram。可实现读写波形数据同时进行,实现了波形的任意合成输出。优势在于可以动态的对输出波形进行快速变换。根据双端口ram的特点,两个系统时钟clk1和clk2,在系统时钟clk1的控制下进行查找表寻址输出波形的同时将在系统时钟clk2的控制下将另一个原始波形写入ram中。当读完数据输出波形后,紧接着便可继续读取刚写入原始波形的数据,可实现无延迟过渡波形,实时性更强。

26.还提供了一种频谱纯度优化的任意波形合成电路装置的工作方法,对相位引入一个干扰信号q,打破由相位截断产生的周期性,

27.扰动信号产生机制:p表示带相位偏移的输出相位,q表示抖动发生器中产生的干扰信号,p1表示经过抖动发生器叠加处理后的相位;单元电路采用r/s电路,由两个与非门构成;当系统时钟处于低电平时,此时q和均为1,但当时钟上升沿到来时,q和的值处于不确定状态,但两者必定一个为0,另一个为1;根据相位发生器需要截断的位宽确定r/s单元电路需要的个数,这里为b个r/s单元电路;此外由于相位发生器输出相位位宽为n,这里在对q进行高n

‑

b位0值,将q位宽拓展到n位。

28.优选地,设定移相加法器输出数据为p[n

‑

1:0],利用p的低b位数据,由抖动发生器产生的干扰信号q与移相加法器产生的相位p进行叠加。

[0029]

优选地,增加干扰信号位宽越多,向p[b]位进位为1的可能性越接近进位为0的可

能性;递推关系为公式(2),增加b位干扰信号,相位截断舍弃b位,所以最多增加b位的干扰信号

[0030][0031]

优选地,相位经过干扰信号叠加后再进行相位截断,保留高k位,此时周期性误差被大大减弱,随后对查找表进行寻址,输出波形数据。

[0032]

优选地,对波形查找表采用双端口ram,根据双端口ram的特点,两个系统时钟clk1和clk2,在系统时钟clk1的控制下进行查找表寻址输出波形的同时将在系统时钟clk2的控制下将另一个原始波形写入ram中;当读完数据输出波形后,继续读取刚写入原始波形的数据。

[0033]

以下更详细地说明本发明。

[0034]

如图2所示,本发明实施的原理框图,包括相位发生器201、移相加法器202、抖动发生器203、相位截断模块204、波形查找表205、数模转换器206和低通滤波器207。由公式(1)可知,决定输出波形频率的参数为系统时钟clk、相位累加器位宽n以及频率控制字w301。相位发生器201实现在系统时钟上升沿到来时,对频率控制字301进行累加,输出n位相位值。后在移相加法器202中实现相位偏移操作,并产生带偏移的相位p。由于相位发生器201位宽比波形查找表205地址宽很多,通常需要对相位进行截断,选取高k位,用于波形查找表205地址寻址,但由于相位截断,从而会造成误差。由于在频率控制字301不变时,相位发生器201在系统时钟上升沿不断触发下进行相位累加。相位通过移向加法器202产生带偏移的相位p。相位经相位截断模块204处理后,舍弃的低位数据会重复出现,造成周期性误差,由此导致比较严重的波形杂散问题。故本发明通过对相位引入一个干扰信号q,如图4所示,打破由相位截断产生的周期性,从而达到降低杂散的目的,实现波形频谱纯度优化。

[0035][0036]

扰动信号产生机制:p表示带相位偏移的输出相位,q表示抖动发生器203中产生的干扰信号,p1表示经过抖动发生器203叠加处理后的相位。单元电路采用r/s电路401,由两个与非门构成。当系统时钟处于低电平时,此时q和均为1,但当时钟上升沿到来时,q和的值处于不确定状态,但可以确定两者必定一个为0,另一个为1。根据相位发生器201需要截断的位宽确定r/s单元电路401需要的个数,这里为b个r/s单元电路。此外由于相位发生器201输出相位位宽为n,这里在对q进行高(n

‑

b)位0值将q位宽拓展到到n位,便于进行加法操作,如图4所示。

[0037]

设定移相加法器202输出数据为p[n

‑

1:0],通常会直接采用舍弃低b位的策略,用p[n

‑

1:b]对波形查找表205进行寻址,这会产生严重的周期性误差。如果对p[b

‑

1]位采取四舍五入的方法,仍会造成周期性误差,无法从根本上解决问题。本发明利用了p的低b位数据,由抖动发生器产生的干扰信号q与移相加法器产生的相位p进行叠加,这样就大大减弱了周期性误差。

[0038]

以下进行说明,如果只对p[b

‑

1]位增加干扰信号,如表1所示。

[0039]

p[b

‑

1]q[b

‑

1]向p[b]位的进位p1[b

‑

1]0000010110011110

[0040]

表1

[0041]

可以发现,如果仅对p[b

‑

1]位进行增加干扰信号,则舍弃低b位后,向p[b]位进位为1的可能性为1/4,向p[b]位进位为0的可能性为1/4。

[0042]

如果对p[b

‑

1:b

‑

2]两位增加干扰信号,如表2所示。

[0043]

p[b

‑

1]p[b

‑

2]q[b

‑

1]q[b

‑

2]向p[b]位的进位p1[b

‑

1]p1[b

‑

2]0000000000100100100100011011010000101010100110011011110010000101001011101010010111011100011110110011101011111110

[0044]

表2

[0045]

可以发现,如果对p[b

‑

1:b

‑

2]两位进行增加干扰信号,则舍弃低b位后,向p[b]位进位为1的可能性为3/8,向p[b]位进位为0的可能性为5/8。

[0046]

由此类推,增加干扰信号位宽越多,向p[b]位进位为1的可能性越接近进位为0的可能性。可得递推关系如公式1

‑

2所示,增加b位干扰信号,相位截断舍弃b位,所以最多增加b位的干扰信号。当全部舍弃为均参与时,向p[b]位进位为1的可能性和进位为0的可能性相差最小,理想情况各位1/2。即进位为0和进位为1是等可能的,但又是随机的,可满足打乱周期性的要求,很好的降低相位噪声造成的谱线幅度,有效提高系统的静态无杂散动态范围(sfdr)。

[0047][0048]

相位经过干扰信号叠加后再进行相位截断,保留高k位,此时周期性误差被大大减弱,随后对查找表进行寻址,输出波形数据。

[0049]

特别说明,对波形查找表205可采用双端口ram替代普通的单端口ram实现,优势在于可以动态的对输出波形进行快速变换。根据双端口ram的特点,两个系统时钟clk1和clk2,在系统时钟clk1的控制下进行查找表寻址输出波形的同时将在系统时钟clk2的控制下将另一个原始波形写入ram中。当读完数据输出波形后,紧接着便可继续读取刚写入原始波形的数据,可实现无延迟过渡波形,实时性更强。

[0050]

本发明的有益效果为:

[0051]

1、工作频率宽,频率分辨率高

[0052]

根据直接数字频率合成公式可知,系统时钟、相位累加器位宽和频率控制字决定着波形频率,系统时钟和相位累加器位宽决定了频率分辨率,当系统时钟确定后,相位累加器位宽越大,频率分辨率理论上越高,频率控制字和频率分辨率决定了工作频率带宽,此外可考虑采用kogge

‑

stone树形加法器实现相位累加器,进一步降低工作延迟,从而达到提升系统性能的目的。

[0053]

2、波形可实现无延迟过渡

[0054]

本发明中采用双端口ram实现查找表,可实现读写波形数据同时进行,实现了波形的任意合成输出。

[0055]

3、波形频谱杂散减小

[0056]

本发明针对相位截断带来的周期误差,提出采用叠加干扰信号的方法,打乱周期性,从而进一步减小输出波形的频谱杂散。

[0057]

4、硬件开销小

[0058]

误差处理模块只需要在系统中增加一个抖动发生器,抖动发生器产生的干扰信号与相位数据叠加。抖动发生器通过r/s电路实现,仅需要两个与非门电路,增加很少的电路资源开销,可以在不增加查找表消耗量,也不增加其他数据计算单元的条件下,就可以实现有效的降低相位截断噪声。

[0059]

以上所述,仅是本发明的较佳实施例,并非对本发明作任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。