循环转换sar adc电路、sar adc方法

技术领域

1.本发明涉及集成电路设计领域,特别是涉及一种循环转换sar adc电路、sar adc方法。

背景技术:

2.逐次逼近(successive approximation,sar)adc是一种应用非常广的adc,特别是针对一些高速高精度低功耗的应用。而随着工艺节点向纳米级的推进,sar adc的优势越来越明显,因为其内部主要是电容和比较器以及一些逻辑开关构成,使得面积逐渐变小而精度更容易提高,功耗也可以进一步压缩。

3.随着应用需求的发展,信号测量精度要求越来越准,信号转换速度要求越来越高,adc的速度和精度也在不断刷新,芯片面积也要求越来越小,因此,高速高精度低成本sar adc成为adc研究的一个重要课题。传统sar adc主体模块包括:采样保持单元、dac 、比较器、sar控制逻辑单元。其中dac 和比较器的设计决定了芯片的面积、精度、速度,sar逻辑主要是数字电路,因为其可以不考虑电压摆幅,可以用低压器件来实现数字电路设计,其速度和面积都相对不占主导因素。基于此,如果目的是要实现一个高速高精度adc,主要突破点应集中在dac和比较器上。

4.dac的面积大小取决于精度要求,如果实现一个n

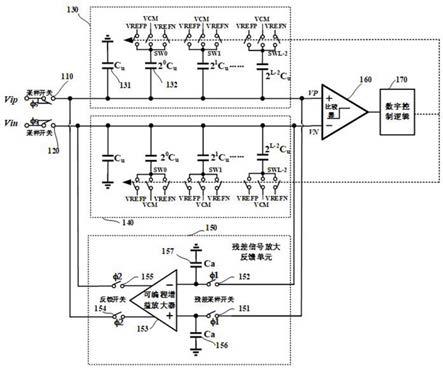

‑

bit sar adc,假设使用上级板采样方式和二进制cdac电容阵列排列方式,最终需要的单位电容cu个数为2

n

‑1而且如果要保证一定的匹配精度,单位电容的尺寸又不能取太小(单位电容的匹配正比于电容面积的倒数)。换而言之,如果每提高1bit,电容的总面积就要翻一倍,12bit sar adc单位电容总数为2048个, 16bit sar adc电容的总个数为32768个,此数目是非常的庞大,而且16bit的匹配更加苛刻,单位电容不能取太小,导致电容面积主导了整个adc的面积。随着技术的发展,人们提出了新的架构来解决电容如此大的问题比如引入桥接电容架构,但是匹配问题依然存在,单个电容依然不能取太小,而且在设计超过12bit 精度的sar adc时,dac必须经过校准,这又提高了单颗adc芯片的成本。

5.另一方面,比较器的设计主要是解决噪声,精度和速度问题,其要求在短时间内快速识别很微弱的输入信号,设计难度也是相当高,一般是使用多级设计加上自动校零,其架构比较复杂。因此,设计一个高速高精度sar adc必须综合考虑,同时解决上述两个问题,方能成功。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种循环转换sar adc电路、sar adc方法,用于解决现有技术中数模转换单元中单位电容随输出精度每升高1bit电容面积翻一倍及比较器噪声、精度和速度问题。

7.为实现上述目的及其他相关目的,本发明提供一种循环转换sar adc电路,包括:第一采样开关、第二采样开关、第一数模转换单元、第二数模转换单元、残差信号

放大反馈单元、比较器及sar控制逻辑单元,其中:所述第一采样开关用于接收差分信号的正端输入;所述第二采样开关用于接收差分信号的负端输入;所述第一数模转换单元连接于所述第一采样开关及所述残差信号放大反馈单元的第一输出端,用于数模转换;所述第二数模转换单元连接于所述第二采样开关及所述残差信号放大反馈单元的第二输出端,用于数模转换;所述残差信号放大反馈单元连接于所述第一数模转换单元及所述第二数模转换单元的输出端,用于对所述第一数模转换单元及所述第二数模转换单元输出的残差信号进行采样和放大,并分别反馈至所述第一数模转换单元及所述第二数模转换单元的输入端;所述比较器的第一输入端连接于所述第一数模转换单元的输出端,第二输入端连接于所述第二数模转换单元的输出端,用于对所述第一数模转换单元及所述第二数模转换单元的输出信号进行比较,并输出比较结果;所述sar控制逻辑单元连接于所述比较器的输出端,基于所述比较结果输出数字信号并产生所述第一数模转换单元及所述第二数模转换单元的切换控制信号。

8.优选地,所述残差信号放大反馈单元包括:第一残差采样开关、第二残差采样开关、可编程增益放大器、第一反馈开关、第二反馈开关、第一残差信号采样电容及第二残差信号采样电容;所述可编程增益放大器的第一输入端经由所述第一残差采样开关连接所述第一数模转换单元的输出端,第二输入端经由所述第二残差采样开关连接所述第二数模转换单元的输出端,第一输出端经由所述第一反馈开关连接所述第一数模转换单元的输入端,第二输出端经由所述第二反馈开关连接所述第二数模转换单元的输入端;所述可编程增益放大器的第一输入端与第一输出端同相,第二输入端与第二输出端同相;所述第一残差信号采样电容的上极板连接所述可编程增益放大器的第一输入端,下极板连接参考地;所述第二残差信号采样电容的上极板连接所述可编程增益放大器的第二输入端,下极板连接参考地。

9.优选地,所述可编程增益放大器的放大倍数为2

l

,其中,l为所述循环转换sar adc电路的位数。

10.优选地,所述第一残差采样开关与所述第二残差采样开关同步导通,同步断开;所述第一反馈开关与所述第二反馈开关同步导通,同步断开。

11.优选地,所述第一数模转换单元与所述第二数模转换单元均包括第一电容及l

‑

1个权重位电容;所述第一电容的上极板连接于对应采样开关与所述比较器输入端之间,下极板连接参考地;各所述权重位电容的上极板连接于对应采样开关与所述比较器输入端之间,下极板分别通过一切换开关连接正相参考电压、反相参考电压或共模电压;各所述权重位电容的权重从低到高以2为等比系数依次递增,其中,l为所述循环转换sar adc电路的位数。

12.优选地,所述循环转换sar adc电路的位数小于等于8bit。

13.优选地,所述循环转换sar adc电路的输出精度=所述循环转换sar adc电路的位数 所述循环转换sar adc电路的位数

×

循环转换次数。

14.本发明还提出一种sar adc方法,所述sar adc方法基于所述sar adc电路实现,至

少包括:基于所述第一采样开关及所述第二采样开关将差分信号采样至所述第一数模转换单元及所述第二数模转换单元,然后进行逐次逼近转换,输出第一组数字信号,同时得到第一残差信号;基于所述第一残差采样开关及所述第二残差采样开关对所述第一残差信号进行采样,并基于所述可编程增益放大器对采样到的所述第一残差信号进行放大;基于所述第一反馈开关及所述第二反馈开关,将放大后的所述第一残差信号反馈至所述第一数模转换单元及所述第二数模转换单元,并进行逐次逼近转换,输出第二组数字信号,同时得到第二残差信号;基于所述第一残差采样开关及所述第二残差采样开关对所述第二残差信号进行采样,并基于所述可编程增益放大器对采样到的所述第二残差信号进行放大;基于所述第一反馈开关及所述第二反馈开关,将放大后的所述第二残差信号反馈至所述第一数模转换单元及所述第二数模转换单元,并进行逐次逼近转换,输出第三组数字信号,同时得到第三残差信号;重复对得到的残差信号进行放大、反馈及逐次逼近转换操作,其中所述放大、反馈及逐次逼近转换操作为一次完整的循环转换;当达到设定的所述循环转换次数,结束循环转换,依次拼接各组数字信号,完成所述sar adc的一次完整转换。

15.如上所述,本发明的一种循环转换sar adc电路、芯片及sar adc方法,具有以下有益效果:1、与传统sar adc电路架构相比,本发明使用循环转换的方法,反复利用低位数sar adc,避开高精度sar adc转换需要大量数目的dac电容以及高精度比较器的设计难题。

16.2、通过对残差信号放大,降低比较器设计的复杂程度,通过循环转化,减少电容数量,增加单位电容面积满足高精度的匹配要求,比传统sar adc电路架构的电容总面积小。

附图说明

17.图1显示为本技术实施例一中提供的循环转换sar adc电路。

18.图2显示为本技术实施例二中提供的一种sar adc方法时序逻辑图。

19.元件标号说明110

‑

第一采样开关;120

‑

第二采样开关;130

‑

第一数模转换单元;131

‑

第一电容;132

‑

权重位电容;140

‑

第二数模转换单元;150

‑

残差信号放大反馈单元;151

‑

第一残差采样开关;152

‑

第二残差采样开关;153

‑

可编程增益放大器;154

‑

第一反馈开关;155

‑

第二反馈开关;156

‑

第一残差信号采样电容;157

‑

第二残差信号采样电容;160

‑

比较器;170

‑ꢀ

sar控制逻辑单元;201

‑

对差分信号采样的过程;202

‑

对差分信号逐次逼近的过程;203

‑

对第一残差信号采样的过程;204

‑

对第一残差信号放大和反馈的过程;205

‑

第一次循环转换过程;206

‑

对第二残差信号采样的过程;207

‑

对第二残差信号放大和反馈的过程;208

‑

第二次循环转换过程;s1~s7

‑

步骤。

具体实施方式

20.以下由特定的具体实施例说明本发明的实施方式,熟悉此技术的人士可由本说明书所揭露的内容轻易地了解本发明的其他优点及功效。

21.请参阅图1至图2。须知,本说明书所附图式所绘示的电路、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何电路的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“下”、“左”、“右”、“中间”及“一”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

22.实施例一如图1所示,本实施例提供一种循环转换sar adc电路,包括:第一采样开关110、第二采样开关120、第一数模转换单元130、第二数模转换单元140、残差信号放大反馈单元150、比较器160及sar控制逻辑单元170,其中:所述第一采样开关110用于接收差分信号的正端输入;所述第二采样开关120用于接收差分信号的负端输入;所述第一数模转换单元130连接于所述第一采样开关110及所述残差信号放大反馈单元150的第一输出端,用于数模转换;所述第二数模转换单元140连接于所述第二采样开关120及所述残差信号放大反馈单元150的第二输出端,用于数模转换;所述残差信号放大反馈单元150连接于所述第一数模转换单元130及所述第二数模转换单元140的输出端,用于对所述第一数模转换单元130及所述第二数模转换单元140输出的残差信号进行采样和放大,并分别反馈至所述第一数模转换单元130及所述第二数模转换单元140的输入端;所述比较器160的第一输入端连接于所述第一数模转换单元130的输出端,第二输入端连接于所述第二数模转换单元140的输出端,用于对所述第一数模转换单元130及所述第二数模转换单元140的输出信号进行比较,并输出比较结果;所述sar控制逻辑单元170连接于所述比较器160的输出端,基于所述比较结果输出数字信号并产生所述第一数模转换单元130及所述第二数模转换单元140的切换控制信号。

23.具体地,在本实施例中,所述残差信号放大反馈单元150包括:第一残差采样开关151、第二残差采样开关152、可编程增益放大器153、第一反馈开关154、第二反馈开关155、第一残差信号采样电容156及第二残差信号采样电容157。所述可编程增益放大器153的第一输入端经由所述第一残差采样开关151连接所述第一数模转换单元130的输出端,第二输入端经由所述第二残差采样开关152连接所述第二数模转换单元140的输出端,第一输出端经由所述第一反馈开关154连接所述第一数模转换单元130的输入端,第二输出端经由所述第二反馈开关155连接所述第二数模转换单元140的输入端;作为示例,所述可编程增益放大器153的第一输入端与第一输出端同相,第二输入端与第二输出端同相。所述第一残差信号采样电容156的上极板连接所述可编程增益放大器153的第一输入端,下极板连接参考

地。所述第二残差信号采样电容157的上极板连接所述可编程增益放大器153的第二输入端,下极板连接参考地。

24.需要说明的是,所述第一残差采样开关151、第二残差采样开关152、第一反馈开关154及第二反馈开关155包括但不限于二极管、三极管、场效应管、晶闸管,任意可作为开关功能的器件均适用,在此不一一赘述。所述可编程增益放大器153架构包括但不限于微处理器、数字信号处理器、可编程逻辑门阵列,任意可作为可编程增益放大器的架构均适用,在此不一一赘述。在本实施例中,所述第一残差信号采样电容156及第二残差信号采样电容157为片内电容,通过光刻工艺制造出来。

25.更具体地,所述可编程增益放大器153的放大倍数为2

l

,其中,l为所述循环转换sar adc电路的位数;所述可编程增益放大器153放大倍数的设置方式包括但不限于配置、自适应,任意可以设置可编程增益放大器放大倍数的实现方式均适用,在此不一一赘述。

26.更具体地,所述第一残差采样开关151与所述第二残差采样开关152同步导通,同步断开;所述第一反馈开关154与所述第二反馈开关155同步导通,同步断开;所述第一残差采样开关151、所述第二残差采样开关152、所述第一反馈开关154及所述第一反馈开关155的同步设置方式包括但不限于配置、自适应,任意可以设置开关同步的实现方式均适用,在此不一一赘述。

27.具体地,所述第一数模转换单元130与所述第二数模转换单元140均包括第一电容131及l

‑

1个权重位电容132;所述第一电容131的上极板连接于对应采样开关与所述比较器160输入端之间,下极板连接参考地;各所述权重位电容132的上极板连接于对应采样开关与所述比较器160输入端之间,下极板分别通过一切换开关连接正相参考电压vrefp、反相参考电压vrefn或共模电压vcm;各所述权重位电容132的权重从低到高以2为等比系数依次递增,其中,l为所述循环转换sar adc电路的位数。

28.具体地,所述循环转换sar adc电路的位数小于等于8bit,因此所述第一数模转换单元130和所述第二数模转换单元140的电容的数目很小(小于等于128个)。

29.具体地,所述循环转换sar adc电路的输出精度=所述循环转换sar adc电路的位数 所述循环转换sar adc电路的位数

×

循环转换次数。

30.本发明的循环转换sar adc电路占用面积小、成本低,但输出精度高。

31.实施例二本实施例提供一种sar adc方法,所述sar adc方法基于如实施例一提供的所述sar adc循环转换电路实现,至少包括:步骤s1:如图1及图2所示,基于所述第一采样开关110及所述第二采样开关120将差分信号采样至所述第一数模转换单元130及所述第二数模转换单元140,即图2中对差分信号采样的过程201,然后进行逐次逼近转换,即图2中对差分信号逐次逼近的过程202,输出第一组数字信号,同时得到第一残差信号。

32.步骤s2:如图1及图2所示,基于所述第一残差采样开关151及所述第二残差采样开关152对所述第一残差信号进行采样,即图2中对第一残差信号采样的过程203,并基于所述可编程增益放大器153对采样到的所述第一残差信号进行放大,即图2中对第一残差信号放大和反馈的过程204。

33.步骤s3:如图1及图2所示,基于所述第一反馈开关154及所述第二反馈开关155,将

放大后的所述第一残差信号反馈至所述第一数模转换单元130及所述第二数模转换单元140,并进行逐次逼近转换,即图2中第一次循环转换过程205,输出第二组数字信号,同时得到第二残差信号。

34.步骤s4:如图1及图2所示,基于所述第一残差采样开关151及所述第二残差采样开关152对所述第二残差信号进行采样,即图2中对第二残差信号采样的过程206,并基于所述可编程增益放大器153对采样到的所述第二残差信号进行放大,即图2中对第二残差信号放大和反馈的过程207。

35.步骤s5:如图1及图2所示,基于所述第一反馈开关154及所述第二反馈开关155,将放大后的所述第二残差信号反馈至所述第一数模转换单元130及所述第二数模转换单元140,并进行逐次逼近转换,即图2中的第二次循环转换过程208,输出第三组数字信号,同时得到第三残差信号。

36.步骤s6:重复对得到的残差信号进行放大、反馈及逐次逼近转换操作,其中所述放大、反馈及逐次逼近转换操作为一次循环转换;步骤s7:当达到设定的所述循环转换次数,结束循环转换,依次拼接各组数字信号,完成所述sar adc方法。

37.更具体地,作为示例,如图1所示,vip和vin是待转换的输入差分信号,采样时,所述第一采样开关110和所述第二采样开关120导通,其首先被采样到所述第一数模转换单元130和所述第二数模转换单元140的上极板上,然后所述第一采样开关110和所述第二采样开关120断开,接着,所述循环转换sar adc电路完成一次正常的转换,此时输出位数为l

‑

bit,记为d0<l

‑

1:0>,然后得到残差信号(vp

‑

vn)1,此时所述第一残差采样开关151和所述第二残差采样开关152导通,残差信号(vp

‑

vn)1输入到所述可编程增益放大器153的第一输入端和第二输入端,需要注意的是所述可编程增益放大器153的放大倍数必须是2

l

倍,以此保证最终数据在拼接时不会存在非线性或者增益偏差,因此所述可编程增益放大器153的输出为2

l *(vp

‑

vn)1,然后所述第一残差采样开关151和所述第二残差采样开关152断开,所述第一反馈开关154和所述第二反馈开关155闭合,大小为2

l *(vp

‑

vn)1的残差信号被采样到所述第一数模转换单元130和所述第二数模转换单元140的上极板上,然后所述循环转换sar adc电路开始第一次循环转换,将采样得到的残差信号转换成数字输出,其输出位数仍然是l

‑

bit,第一次循环转换结果记为dcycle_1<l

‑

1:0>,依次类推,可以实现第二次、第三次、

…

、第m次的循环转换,输出结果分别记为dcycle_2<l

‑

1:0>、dcycle_3<l

‑

1:0>、

……

、 dcycle_m<l

‑

1:0>。最终,adc输出总的位数为l*(m 1),其拼接得到的总的数字输出为dout = 2

(l*m)

*d0<l

‑

1:0> 2

(l*(m

‑

1))

*dcycle_1<l

‑

1:0> 2

(l*(m

‑

2))

*dcycle_2<l

‑

1:0>

ꢀ…ꢀ

20*dcycle_m<l

‑

1:0>。

38.需要说明的是,作为示例,如图2所示,如果所述循环转换sar adc电路位数l=5,循环转换次数为2,总共得到15bit的数字输出,对应的输出dout<14:0>=2

5*2

*d0<4:0> 2

(5*1) *dcycle_1<4:0> 2

(5*0) *dcycle_2<4:0>。

39.综上所述,本发明提供一种循环转换sar adc电路、芯片及sar adc方法,包括:所述循环转换sar adc电路至少包括:第一采样开关、第二采样开关、第一数模转换单元、第二数模转换单元、残差信号放大反馈单元、比较器及sar控制逻辑单元,其中:所述第一采样开关用于接收第一差分信号;所述第二采样开关用于接收第二差分信号;所述第一数模转换

单元连接于所述第一采样开关及所述残差信号放大反馈单元的第一输出端,用于数模转换;所述第二数模转换单元连接于所述第二采样开关及所述残差信号放大反馈单元的第二输出端,用于数模转换;所述残差信号放大反馈单元连接于所述第一数模转换单元及所述第二数模转换单元的输出端,用于对所述第一数模转换单元及所述第二数模转换单元输出的残差信号进行采样和放大,并分别反馈至所述第一数模转换单元及所述第二数模转换单元的输入端;所述比较器的第一输入端连接于所述第一数模转换单元的输出端,第二输入端连接于所述第二数模转换单元的输出端,用于对所述第一数模转换单元及所述第二数模转换单元的输出信号进行比较,并输出比较结果;所述sar控制逻辑单元连接于所述比较器的输出端,基于所述比较结果输出数字信号并产生所述第一数模转换单元及所述第二数模转换单元的切换控制信号。本发明的循环转换sar adc电路、芯片及sar adc方法,与传统sar adc电路架构相比,本发明使用循环转换的方法,反复利用低位数sar adc,避开高精度sar adc转换需要大量数目的dac电容以及高精度比较器的设计难题;通过对残差信号放大,降低比较器设计的复杂程度,通过循环转换减少电容数量,增加单位电容面积满足高精度的匹配要求,比传统sar adc电路架构的电容总面积小。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

40.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。