1.本发明涉及一种阻塞信号抵消低噪声放大器系统。

背景技术:

2.在片上收发机上集成多协议、多频带使得接收链的设计具有极大的吸引力和挑战性。在拥挤的频段如1.93

‑

1.99ghz的个人通讯服务(pcs)频段和2.4

‑

2.4835ghz ism频段(industrial scientific medical band,工业的、科学的、医学的频段)上,接收机(rx)的性能对大功率阻塞信号(blocker)非常敏感。因此,针对每一种通信标准而设计的接收机都需要满足相应的阻塞忍受标准,该标准通常包含了在某一频率偏移下接收机能接受的最大阻塞功率。

技术实现要素:

3.本发明主要提供一种阻塞信号抵消低噪声放大器系统,下面具体说明。

4.一种实施例中提供一种阻塞信号抵消低噪声放大器系统,包括第一低噪声放大器,第二低噪声放大器,阻塞信号提取和偏置产生电路,偏置切换电路,以及偏置切换信号产生电路;

5.所述第一低噪声放大器用于动态的输入匹配,其接收输入信号进行放大后输出;所述第一低噪声放大器具有阻塞模式和小信号模式,在所述小信号模式下,所述第一低噪声放大器的偏置信号为直流偏置电压信号v

b1

,在所述阻塞模式下,所述第一低噪声放大器的偏置信号为直流偏置电压信号v

b2

;

6.所述阻塞信号提取和偏置产生电路用于从所述第一低噪声放大器的输出信号中提取阻塞信号,并输出一与阻塞信号的强度呈反向关系的直流电压信号,以作为所述直流偏置电压信号v

b2

;

7.所述偏置切换电路用于将所述第一低噪声放大器在所述阻塞模式和小信号模式之间切换;所述偏置切换电路通过将所述第一低噪声放大器的偏置信号切换为所述直流偏置电压信号v

b1

,以将所述第一低噪声放大器切换为所述小信号模式;所述偏置切换电路通过将所述第一低噪声放大器的偏置信号切换为所述直流偏置电压信号v

b2

,以将所述第一低噪声放大器切换为所述阻塞模式;

8.所述偏置切换信号产生电路用于将所述直流偏置电压信号v

b2

与一预设的参考电压信号v

ref

进行比较,当所述直流偏置电压信号v

b2

小于所述参考电压信号v

ref

时,则所述偏置切换信号产生电路产生第一切换信号,所述第一切换信号用于使得所述偏置切换电路将所述第一低噪声放大器切换或维持为阻塞模式;反之,当所述直流偏置电压信号v

b2

大于所述参考电压信号v

ref

时,则所述偏置切换信号产生电路产生第二切换信号,所述第二切换信号用于使得所述偏置切换电路将所述第一低噪声放大器切换或维持为小信号模式;

9.所述第二低噪声放大器与所述第一低噪声放大器连接,用于同时被a类偏置电压v

ba

和c类偏置电压v

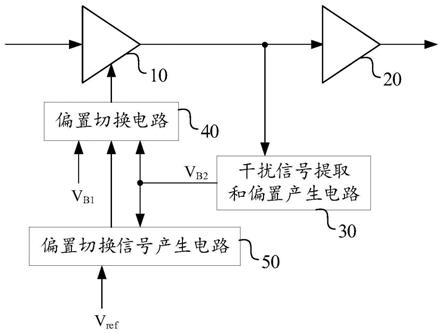

bc

所偏置,以对所述第一低噪声放大器的输出信号进行阻塞消除和放

大。

10.一实施例中,所述第一低噪声放大器包括晶体管m11、晶体管m12、晶体管m13、晶体管m14、晶体管m15、晶体管m16、电感l10、电感l11、电感l12、电感l13、电容c10、电容c11、电容c12、电容c13和电容c14;

11.所述晶体管m11的第二极、晶体管m12的第二极分别与电感l13的第一端、第二端连接,电感l13的第三端接地;晶体管m11的控制极和第二极之间连接有电容c11,晶体管m11的控制极还用于通过电感l11连接所述第一低噪声放大器的输入信号的正端;晶体管m11的控制极还通过电容c13与晶体管m15的第一极连接,晶体管m15的第二极接地;晶体管m12的控制极和第二极之间连接有电容c12,晶体管m12的控制极还用于通过电感l12连接所述第一低噪声放大器的输入信号的负端;晶体管m12的控制极还通过电容c14与晶体管m16的第一极连接,晶体管m16的第二极接地;

12.所述晶体管m13的第二极与晶体管m11的第一极连接;所述晶体管m13的控制与晶体管m14的控制极连接,并用于接收电压信号v

cas1

;晶体管m13的第一极与电容c10的一端连接,电容c10的另一端与晶体管m14的第一极连接;晶体管m13的第一极还与电感l10的第一端连接,电感l10的第二端与晶体管m14的第一极连接,电感l10的第三端用于接收工作电压v

dd

;晶体管m14的第二极与晶体管m12的第一极连接;

13.所述晶体管m11的控制极还通过所述偏置切换电路接收所述直流偏置电压信号v

b1

或所述直流偏置电压信号v

b2

;所述晶体管m12的控制极还通过所述偏置切换电路接收所述直流偏置电压信号v

b1

或所述直流偏置电压信号v

b2

;其中,所述第一切换信号包括第一状态的控制电压v

en

和第二状态的控制电压v

blk

,当接收到所述第一切换信号时,所述偏置切换电路响应于所述第一状态的控制电压v

en

将所述直流偏置电压信号v

b1

从所述晶体管m11的控制极断开,以及响应于所述第二状态的控制电压v

blk

将所述直流偏置电压信号v

b2

接入到所述晶体管m11的控制极;所述第二切换信号包括第二状态的控制电压v

en

和第一状态的控制电压v

blk

,当接收到所述第二切换信号时,所述偏置切换电路响应于所述第二状态的控制电压v

en

将所述直流偏置电压信号v

b1

接入到所述晶体管m11的控制极,以及响应于所述第一状态的控制电压v

blk

将所述直流偏置电压信号v

b2

从所述晶体管m11的控制极断开;所述晶体管m15和晶体管m16的控制极还用于接收所述控制电压v

en

;

14.所述晶体管m13的第一极、晶体管m14的第一极分别作为所述第一低噪声放大器输出的负端和正端。

15.一实施例中,所述晶体管m11和晶体管m12为相同参数的晶体管;所述晶体管m13和晶体管m14为相同参数的晶体管;所述晶体管m15和晶体管m16为相同参数的晶体管;所述电感l11和电感l12为相同参数的电感;所述电容c11和电容c12为相同参数的电容;所述电容c13和电容c14为相同参数的电容。

16.一实施例中,所述第一态为低电平,所述第二态为高电平。

17.一实施例中,所述第二低噪声放大器包括晶体管m21、晶体管m22、晶体管m23、晶体管m24、晶体管m25、晶体管m26、电感l20、电感l21、电感l22、电感l23、电感l24、电容c20、电容c21、电容c22、电容c23和电容c24;

18.所述晶体管m21的第一极与晶体管m24的第一极连接,晶体管m21的第二极接地,晶体管m21的控制极还通过电感l21接收所述c类偏置电压v

bc

;晶体管m21的控制极还与电容

c21的一端连接,电容c21的另一端与电容c23的一端连接,电容c23的另一端与晶体管m23的控制极连接,晶体管m23的控制极还通过电感l23接收所述a类偏置电压v

ba

;晶体管m23的第二极接地;电容c21与电容c23连接的那端,还作为所述第二低噪声放大器输入的负端;

19.所述晶体管m22的第一极与晶体管m23的第一极连接,晶体管m22的第二极接地,晶体管m22的控制极还通过电感l22接收所述c类偏置电压v

bc

;晶体管m22的控制极还与电容c22的一端连接,电容c22的另一端与电容c24的一端连接,电容c24的另一端与晶体管m24的控制极连接,晶体管m24的控制极还通过电感l24接收所述a类偏置电压v

ba

;晶体管m24的第二极接地;电容c22与电容c24连接的那端,还作为所述第二低噪声放大器输入的正端;

20.所述晶体管m25的第二极与晶体管m21的第一极连接;所述晶体管m25的控制与晶体管m26的控制极连接,并用于接收电压信号v

cas2

;晶体管m25的第一极与电容c20的一端连接,电容c20的另一端与晶体管m26的第一极连接;晶体管m25的第一极还与电感l20的第一端连接,电感l20的第二端与晶体管m26的第一极连接,电感l20的第三端用于接收工作电压v

dd

;晶体管m26的第二极与晶体管m22的第一极连接;

21.所述晶体管m25的第一极、晶体管m26的第一极分别作为所述第二低噪声放大器输出的负端和正端。

22.一实施例中,所述晶体管m21和晶体管m22为相同参数的晶体管;所述晶体管m23和晶体管m24为相同参数的晶体管;所述晶体管m25和晶体管m26为相同参数的晶体管;所述电感l21和电感l22为相同参数的电感;所述电感l23和电感l24为相同参数的电感;所述电容c21和电容c22为相同参数的电容;所述电容c23和电容c24为相同参数的电容。

23.一实施例中,所述阻塞信号提取和偏置产生电路包括包络检测电路和直流信号提取电路;

24.所述包络检测电路检测所述第一低噪声放大器的输出信号的包络,并输出与包络的幅度呈反向关系的信号;

25.所述直流信号提取电路用于从所述包络检测电路的输出信号中提取直流电压信号,作为所述直流偏置电压信号v

b2

。

26.一实施例中,所述包络检测电路包括晶体管m30、晶体管m31、晶体管m32、电感l31、电感l32、电容c31和电容c32;

27.所述晶体管m31的第一极与晶体管m32的第一极连接,晶体管m31的第二极接地,晶体管m31的控制极还通过电感l31接收偏置电压v

th1

;晶体管m31的控制极与电容c31的一端连接,电容c31的另一端作为所述包络检测电路输入的负端;

28.所述晶体管m32的第二极接地,晶体管m32的控制极还通过电感l32接收偏置电压v

th2

;晶体管m32的控制极与电容c32的一端连接,电容c32的另一端作为所述包络检测电路输入的正端;

29.所述晶体管m30的第一极与晶体管m31的第一极连接,晶体管m30的第二极用于接收工作电压v

dd

,晶体管m30的控制极用于接收电压v

ben

;晶体管m31的第一极还作为所述包络检测电路的输出端。

30.一实施例中,所述晶体管m31和晶体管m32为相同参数的晶体管;所述电感l31和电感l32为相同参数的电感;所述电容c31和电容c32为相同参数的电容。

31.一实施例中,所述偏置电压v

th1

的值所述晶体管m31的阈值电压的值;所述偏置电

压v

th2

的值所述晶体管m32的阈值电压的值。

32.一实施例中,所述直流信号提取电路包括低通滤波器。

33.一实施例中,所述偏置切换信号产生电路包括比较器。

34.一实施例中,所述比较器用于将所述直流偏置电压信号v

b2

与一预设的参考电压信号v

ref

进行比较,当所述直流偏置电压信号v

b2

小于所述参考电压信号v

ref

时,所述比较器输出低电平的控制电压v

en

和高电平的控制电压v

blk

,作为所述第一切换信号;当所述直流偏置电压信号v

b2

大于所述参考电压信号v

ref

时,所述比较器输出高电平的控制电压v

en

和低电平的控制电压v

blk

,作为所述第二切换信号。

35.一实施例中,所述阻塞信号抵消低噪声放大器系统还包括缓冲器,所述缓冲器用于接收所述第二低噪声放大器的输出信号,所述缓冲器的输出作为所述阻塞信号抵消低噪声放大器系统的输出。

36.依据上述实施例的阻塞信号抵消低噪声放大器系统,在不引入lo和混频器的情况下解决了通带相互混频的问题,从而减少nf。

附图说明

37.图1为本技术所涉及的文献的列表图;

38.图2为文献1中所涉及的方案的原理框图;

39.图3为本技术一种实施例的阻塞信号抵消低噪声放大器系统的结构示意图;

40.图4为本技术一种实施例的共源级电感退化匹配结构的示意图;

41.图5为2.4ghz工作频率下距离为80mhz的阻塞强度对图4结构输入匹配和等效小信号跨导g

m1eq

的影响的示意图;

42.图6为本技术一种实施例的动态匹配网络原理图;

43.图7(a)和图7(b)为本技术一些实施例的输入匹配仿真示意图,具体地,图7(a)为阻塞模式下匹配示意图,图7(b)切换到小信号模式下的匹配示意图;其中l1=8.3nh(q=12.9),c2=437ff,l2=2nh(q=12);

44.图8为本技术一种实施例的构造的阻塞电流消除结构的原理图;

45.图9为本技术一种实施例的阻塞信号抵消低噪声放大器系统的结构示意图;

46.图10(a)和图10(b)为本技术两种实施例的第一低噪声放大器的结构示意图;

47.图11为本技术一种实施例的阻塞信号抵消低噪声放大器系统的结构示意图;

48.图12(a)和图12(b)为本技术两种实施例的包络检测电路的结构示意图;

49.图13为本技术一种实施例的阻塞信号提取和偏置产生电路的特性曲线图;

50.图14为本技术一种实施例的比较器的结构示意图;

51.图15为本技术图14中所涉及的比较器的传递函数图;

52.图16(a)和图16(b)为本技术两种实施例的第二低噪声放大器的结构示意图;

53.图17为本技术一种实施例的阻塞信号抵消低噪声放大器系统的结构示意图;

54.图18(a)、图18(b)和图18(c),展示了图16(b)中晶体管m

a

、晶体管m

c

和晶体管m

cas2

的阻塞抵消点的电流频谱;

55.图19为本技术一种实施例的晶体管m

a

和晶体管m

c

中阻塞电流的瞬态仿真结果示意图;

56.图20为本技术一种实施例在小信号模式下的后仿真s参数和nf的示意图;

57.图21为本技术一种实施例在

‑

15dbm、2.48ghz阻塞注入下的后仿真s参数和nf;

58.图22为本技术一种实施例在

‑

10dbm、2.48ghz阻塞注入下的后仿真s参数和nf;

59.图23为本技术和其他阻塞过滤射频前端结构的性能的总结和比较的表格图。

具体实施方式

60.下面通过具体实施方式结合附图对本发明作进一步详细说明。其中不同实施方式中类似元件采用了相关联的类似的元件标号。在以下的实施方式中,很多细节描述是为了使得本技术能被更好的理解。然而,本领域技术人员可以毫不费力的认识到,其中部分特征在不同情况下是可以省略的,或者可以由其他元件、材料、方法所替代。在某些情况下,本技术相关的一些操作并没有在说明书中显示或者描述,这是为了避免本技术的核心部分被过多的描述所淹没,而对于本领域技术人员而言,详细描述这些相关操作并不是必要的,他们根据说明书中的描述以及本领域的一般技术知识即可完整了解相关操作。

61.另外,说明书中所描述的特点、操作或者特征可以以任意适当的方式结合形成各种实施方式。同时,方法描述中的各步骤或者动作也可以按照本领域技术人员所能显而易见的方式进行顺序调换或调整。因此,说明书和附图中的各种顺序只是为了清楚描述某一个实施例,并不意味着是必须的顺序,除非另有说明其中某个顺序是必须遵循的。

62.本文中为部件所编序号本身,例如“第一”、“第二”等,仅用于区分所描述的对象,不具有任何顺序或技术含义。而本技术所说“连接”、“联接”,如无特别说明,均包括直接和间接连接(联接)。

63.需要说明的是,本文的晶体管,如无特殊说明,则其可以是任何结构的晶体管,比如双极型晶体管(bjt)或者场效应晶体管(fet);当晶体管为双极型晶体管时,其控制极是指双极型晶体管的栅极,第一极可以为双极型晶体管的集电极或发射极,对应的第二极可以为双极型晶体管的发射极或集电极,在实际应用过程中,“发射极”和“集电极”可以依据信号流向而互换;当晶体管为场效应晶体管时,其控制极是指场效应晶体管的栅极,第一极可以为场效应晶体管的漏极或源极,对应的第二极可以为场效应晶体管的源极或漏极,在实际应用过程中,“源极”和“漏极”可以依据信号流向而互换。

64.请参照图1的文献表格,其涉及下列的文献:

65.文献1:一种用于无saw无线接收器的阻塞过滤技术(h.darabi,"a blocker filtering technique for saw

‑

less wireless receivers,"in ieee journal of solid

‑

state circuits,vol.42,no.12,pp.2766

‑

2773,dec.2007);

66.文献2:一种采用0.35um cmos的900

‑

mhz双变频低中频gsm接收器(s.tadjpour,s.cijvat,e.hegazi,and a.a.abidi,“a 900

‑

mhz dualconversion low

‑

if gsm receiver in 0.35

‑

_m cmos,”ieee j.solid

‑

state circuits,vol.36,no.12,pp.1992

–

2002,dec.2001);

67.文献3:一种具有1850至2400mhz调谐范围的高动态范围可编程cmos前端滤波器(k.t.christensen,t.h.lee,and e.bruun,“a high dynamic range programmable cmos front

‑

end filter with a tuning range from 1850to 2400mhz,”analog integrated circuits and signal processing,vol.42,pp.55

–

64,2005);

68.文献4:一种深亚微米cmos工艺中q增强型lc槽的带宽设置概念比较(d.bormann,t.d.werth,n.zimmermann,r.wunderlich,and s.heinen,“a comparison of bandwidth setting concepts for q

‑

enhanced lc

‑

tanks in deep

‑

sub micron cmos processes,”in ieee int.conf.electronics,circuits and systems,sep.2008,pp.726

–

729);

69.文献5:一种用于无线接收器的阻塞过滤技术(h.darabi,“a blocker filtering technique for wireless receivers,”in ieee int.solid

‑

state circuits conf.,isscc 2007,dig.tech.papers,feb.11

–

15,2007,pp.84

–

588);

70.文献6:一种集成阻塞过滤射频前端(a.safarian,a.shameli,a.rofougaran,m.rofougaran,and f.de flaviis,“integrated blocker filtering rf front ends,”in proc.2007ieee radio frequency integrated circuits(rfic)symp.,jun.3

–

5,2007,pp.13

–

16);

71.文献7:一种用于射频接收器前端阻塞滤波的有源反馈阻塞消除技术(t.d.werth,c.schmits,r.wunderlich and s.heinen,"an active feedback interference cancellation technique for blocker filtering in rf receiver front

‑

ends,"in ieee journal of solid

‑

state circuits,vol.45,no.5,pp.989

‑

997,may 2010);

72.文献8:一种使用互易混合消除的相位噪声和杂散滤波技术(m.mikhemar,d.murphy,a.mirzaei and h.darabi,"a phase

‑

noise and spur filtering technique using reciprocal

‑

mixing cancellation,"2013ieee international solid

‑

state circuits conference digest of technical papers,2013,pp.86

‑

87)。

73.发明人研究了这些文献,文献1表示带外阻塞恶化接收机性能主要表现在增益的压缩和噪声系数的升高,而文献2则表示带内阻塞可能会因为互调,相互混频等效应使rx减敏。过去的片上阻塞消除技术主要包含了品质因数(q)增强型带通滤波器的使用文献1和文献3中的有源抵消、文献5和文献6使用的滤波器正向抵消,以及文献6和文献7使用的反馈抵消等方法。然而文献6已经表明反馈抵消对i/q失配并不敏感,并且高品质、高选择性的滤波器不仅有插入损耗而且很难设计。对于文献1中的转换环路法,虽然相互混频引入的噪声被滤波器抑制,但在阻塞抵消部分,本振和上变频混频器的噪声被叠加到了接收信号上,原理如图2所示。对文献7来说,在有源抵消中引入的相互混频噪声较大地恶化了射频前端的噪声系数,同时其功耗超过了60mw,已经难以满足如今的低功耗设计需求。在小信号下,文献1和文献7的射频前端在1.9ghz附近能分别达到3.5db和7db,其噪声系数也处于较高的状态,而且抵消环路间的相位不匹配也会存在。文献8则通过利用震荡信号近似对称的频谱特性来产生一个镜像的相互混频噪声来抵消另一路被污染的信号。然而该接收机的噪声会被另一路的噪声严重限制,并且目前其测试数据仅限于基带部分。

74.本技术提出了一种基于动态输入匹配和偏置策略的阻塞信号直接抵消低噪声放大器(lna,low

‑

noise amplifier)的结构,在不引入lo和混频器的情况下解决了通带相互混频的问题,从而减少nf。一些实施例中,全差分结构使lna在阻塞抵消路径上能提供最好的相位匹配。一些实施例,选定各器件的参数后,在80mhz偏移处,本技术设计的低噪声放大器系统最高可抵消

‑

10dbm的阻塞功率。

75.本技术一些实施例中提出了一种能在时域上直接抵消阻塞信号(blocker)的低噪声放大器(lna)结构;该电路采用了两级结构,第一级负责动态的输入匹配,第二级负责阻

塞信号的抵消,并引入了比较器和包络检测器来进行阻塞信号的判断和工作模式的切换,即该lna能工作在小信号模式和阻塞模式下。相比于过去基于频域的阻塞信号过滤射频接收机(rx)前端技术,该技术简化了克服阻塞用的rx设计。同时,该lna在抵消阻塞中不再使用信号处理用滤波器,混频器和本振,从而进一步减少了噪声和插入损耗的引入,避免了相互混频(reciprocal mixing)的问题。动态匹配和动态偏置技术使得该lna能保证双模式下良好的输入匹配并缓解增益压缩的现象。除此之外,在全差分结构的设计下,时域上抵消阻塞的策略保证了抵消过程中拥有最小化的信号相位误差,进一步提高了抵消效果。此lna采用tsmc 65nm工艺,芯片面积为0.89

×

0.59mm2,工作频率为2.4ghz。在小信号模式下,lna有27

‑

33db可变增益和180mhz的3

‑

db带宽,噪声系数(nf)为2.54db,在1.2v电源电压下功耗为20.4

‑

24mw。当一个2.48ghz处的

‑

15/

‑

10dbm阻塞介入时,lna在抵消阻塞后的增益为24.5/19.4db,nf为5.75/6.72db,功耗为27.6/30mw。

76.下面详细说明。

77.本技术一些实施例中提供一种阻塞信号抵消低噪声放大器系统。请参照图3,通过采用两级差分结构的阻塞抵消低噪声放大器能提供良好的虚地和两条相位差180度的信号路径。第一级的低噪声放大器lna1具有两种工作模式:阻塞模式和小信号模式。在阻塞模式下,lna1专注于动态的输入匹配,并提供适当的增益以便于提高其输出端包络检测器ed检测阻塞信号的灵敏度。低通滤波器lpf和包络检波器ed通过配合,将检测到的阻塞强度转换成与其有一定关系(例如呈相反关系)的直流电压信号v

b2

,并作为阻塞模式下lna1的新偏置电压,也称为动态偏置策略。阻塞越强,电压v

b2

的值越小,而电压v

b2

又作为lna1在阻塞模式下的偏置电压,因此可以减缓阻塞使晶体管饱和的现象;同时,减小的偏置电压v

b2

也可以调整匹配级晶体管的跨导来帮助改善输入匹配,是动态输入匹配功能的一部分。电压v

b1

则是lna1在小信号模式下的偏置电压,一般芯片工作稳定后其值为定值。需要说明的是,虽然设计中使用了低通滤波器lpf,但它仅用于直流偏置电压提取而非信号处理使用,因此对信号不会引入插入损耗,因此阻塞信号抵消低噪声放大器系统的整个阻塞抵消过程仍然是无滤波器的。

78.上面还涉及一个核心问题,什么时候lna1工作在阻塞模式下,被电压v

b2

所偏置,什么时候lna1工作在小信号模式下,被电压v

b1

所偏置。可以这样来实现:将电压v

b2

发送到比较器comp和用户定义的参考电压v

ref

做出是否存在阻塞的判断。用户可以根据可接受的最大阻塞灵敏度来设置参考电压v

ref

,但通常会高于放大器1db压缩点下电压v

b2

读出的值。当存在较强阻塞时,比较器输出的信号或者说控制电压会闭合将电压v

b2

接入lna1偏置的开关sv

b2

,并断开将电压v

b1

接入lna1偏置的开关sv

b1

,使lna1被动态的电压v

b2

所偏置。当无阻塞时,比较器输出的信号或者说控制电压会断开将电压v

b2

接入lna1偏置的开关sv

b2

,并闭合将电压v

b1

接入lna1偏置的开关sv

b1

,使lna1被电压v

b1

所偏置。两种工作模式下,lna1内的可变输入匹配网络也会被开关控制电压改变。

79.第二级的低噪声放大器lna2利用差分信号路径、c类偏置电压v

bc

和a类偏置电压v

ba

产生的非线性和线性环境,在信号达到lna2输出负载之前通过调整电压v

ba

的大小实现阻塞消除。

80.下面对动态输入匹配和抵消原理进行分析。另外,为了方便测试,可以在本技术设计的阻塞信号抵消低噪声放大器系统的输出增加了一个差分共源级(cs)驱动来匹配50ω

的探针。

81.下面着重研究和分析非线性效应对低噪声放大器系统输入匹配和晶体管等效跨导的影响,并给出动态输入匹配网络和差分阻塞抵消路径的设计与分析。

82.先对输入匹配进行说明。

83.本技术使用共源级电感退化匹配技术,其在窄带低噪声放大器中有着易匹配和低噪声的优点,不妨以该匹配结构为研究对象。图4所示为该结构的原理图,可以得到小信号x1(t)=a1cos(ω1t)下的输入阻抗z

in

为:

[0084][0085]

其中s=jω1,g

m1

为晶体管m1在小信号下的跨导。若此时一个阻塞信号x2(t)=a2cos(ω2t)混入理想信号,且振幅a2远大于a1,那么图4中晶体管m1的漏极(漏端)的输出电流可近似表示为

[0086]

i(t)≈α1(a1cos(ω1t) a2cos(ω2t)) α2(a1cos(ω1t) a2cos(ω2t))2 α3(a1cos(ω1t) a2cos(ω2t))3ꢀꢀꢀ

(2)

[0087]

α1即为g

m1

,α2和α3为非线性下谐波的等效跨导,式(2)是交调(intermodulation)现象的近似分析,且α1,α3符号相反。展开式(2)并整理可得如下各个频率ω的信号组成,其中基频部分为:

[0088][0089]

交调产物为:

[0090][0091]

直流产物为:

[0092][0093]

由于a2远远大于a1,再根据式(3),那么晶体管m1受阻塞影响后简化的等效小信号跨导g

m1eq

可表示为:

[0094][0095]

式(6)中,g

mdc

表示阻塞信号产生的直流分量产物对晶体管m1额外的跨导贡献;式(6)表明,如果只增加阻塞强度,项将压缩跨导,但由等式(5)产生的额外直流电流产物将补偿g

m1eq

。对于晶体管中的寄生电容,偏置条件占主导地位。虽然不同阻塞下也会通过引入不同的非线性直流电流来影响栅

‑

源寄生电容c

gs

,但在低频该电容变化对输入匹配的影响可近似忽略。以上表面了阻塞模式下输入匹配主要由g

m1eq

决定。为了辅助说明,图5给出了图4结构在工作频率为2.4ghz时一个距离为80mhz阻塞下的输入匹配s11和g

m1eq

的仿真结果。当阻塞强度pblocker从

‑

30dbm增加到

‑

10dbm时,g

m1eq

增加,因为g

m1

g

mdc

占主导地位。但当阻塞功率大于

‑

10dbm时,开始主导g

m1eq

并使匹配效果迅速恶化。

[0096]

以下再对动态输入匹配网络的设计思路进行说明。

[0097]

利用共源级电感退化匹配结构和上述对输入匹配的分析,我们选择在阻塞强度为

‑

30dbm到

‑

10dbm的情况下设计阻塞模式下的匹配网络,然后在小信号情况下设计小信号

用匹配网络。图6显示了动态输入匹配网络设计的原理图。电压v

b1

为小信号模式偏置电压,电压v

b2

为阻塞模式下动态偏置电压;它们可以分别由电压控制开关ven(也即上文提及的开关sv

b1

)和vblk(也即上文提及的svb2)控制。因

‑

30dbm到

‑

10dbm的阻塞会使g

m1eq

升高且此时g

m1

g

mdc

占主导地位,所以适当降低电压v

b2

的值不仅有助于降低g

m1eq

来校准输入匹配,还能有效减轻增益压缩的问题。匹配阻塞模式时,电容c1和电压vb1不会被接入,选取合适的电感和晶体管参数并扫描

‑

30dbm到

‑

10dbm的阻塞以确定合适的动态电压v

b2

。匹配完毕后再匹配小信号模式,经过分析图7(a)和图7(b),其输入电阻从阻塞下的匹配点切换到小信号模式时在史密斯圆上的转移轨迹,我们在电容c2处添加了开关和c1,小信号输入匹配完毕。此时该模式的输入阻抗可表示为:

[0098][0099][0100]

图7(a)中靠上的十字符号表示s11(阻塞信号:

‑

15dbm)的在分析图中位置,靠下的十字符号表示s11(阻塞信号:

‑

10dbm)在分析图中位置。图7(b)中的十字符号表示s11(无阻塞信号)在分析图中位置。

[0101]

下面再对阻塞抵消结构进行设计和分析。

[0102]

下面将分析晶体管在a类和c类偏压下对放大小信号和阻塞能力的不同。图8所示为一个通过两路极性相反的差分信号求和来构造的阻塞电流消除结构。在负载晶体管m

cas

处,两路交流信号被抵消,但直流偏置电流为两路偏置电流之和。为了便于分析,我们设晶体管m

a

,晶体管m

c

的偏置电流分别为i

a

和i

c

,且这两个晶体管的长宽一致,即w

a

=w

c

,l

a

=l

c

。晶体管m

a

被电压v

ba

偏置在a类,晶体管m

c

被电压v

bc

偏置在c类。定义α

ia

和α

ic

分别代表晶体管m

a

和晶体管m

c

的第i阶跨导系数,其中i的取值范围为1,2,3。定义g

ja

和g

jc

分别为晶体管m

a

和晶体管m

c

对上述输入匹配分析中所涉及的信号x

i

(t)的总等效跨导,i的取值范围为1,2。由于a2远远大于a1,因此可以得到:

[0103][0104][0105][0106]

从式(5)中可以知道,非线性效应会产生额外的dc电流来增强小信号跨导,因此α

1c

包含了i

c

和额外的非线性电流,且大的w

c

、v

bc

和阻塞功率会增强α

1c

和α

3c

。然而,同样条件下c类偏置要比a类偏置更非线性化,因此首先α

1c

≠α

1a

且α

3c

≠α

3a

。若阻塞模式下需要匹配两路的阻塞电流,需要满足g

2a

=g

2c

,则有:

[0107][0108]

此时抵消阻塞后对小信号的净跨导为:

[0109][0110]

总体而言,发明人利用了a类偏置管和c类偏置管对小信号和大信号放大能力的不

同来设计合适的阻塞抵消结构。一些情况下,式(12)的成立需要阻塞强度不能主导输入匹配,即和不能占主导地位。当阻塞在合理范围内,g

ja

和g

jc

的变化会对晶体管m

a

和晶体管m

c

的偏置电压变化较敏感。过大的阻塞强度将使两个晶体管饱和,偏置电压对阻塞电流的控制能力下降,从而恶化抵消效果。而在小信号模式下,c类偏置路会对小信号放大能力很低,a偏置支路正常工作并可调节低噪声放大器系统的第二级的增益。

[0111]

以上是对低噪声放大器系统的分析,基于以上分析,本技术提出了一种阻塞信号抵消低噪声放大器系统。请参照图9,一些实施例中的阻塞信号抵消低噪声放大器系统包括第一低噪声放大器10,第二低噪声放大器20,阻塞信号提取和偏置产生电路30,偏置切换电路40,以及偏置切换信号产生电路50,下面具体说明。

[0112]

第一低噪声放大器10,本文中也简称为低噪声放大器lna1。第一低噪声放大器10用于动态的输入匹配,其接收输入信号进行放大后输出。第一低噪声放大器10具有阻塞模式和小信号模式;具体地,在小信号模式下,第一低噪声放大器10的偏置信号为直流偏置电压信号v

b1

;在阻塞模式下,第一低噪声放大器10的偏置信号为直流偏置电压信号v

b2

。第一低噪声放大器10的两种工作模式(即阻塞模式和小信号模式)能够通过偏置切换电路40和偏置切换信号产生电路50来自主和动态地切换,这一点在下文还会详细说明。

[0113]

请参照图10(a),一些实施例中的第一低噪声放大器10包括晶体管m11、晶体管m12、晶体管m13、晶体管m14、晶体管m15、晶体管m16、电感l10、电感l11、电感l12、电感l13、电容c10、电容c11、电容c12、电容c13和电容c14。晶体管m11的第二极、晶体管m12的第二极分别与电感l13的第一端、第二端连接,电感l13的第三端接地;晶体管m11的控制极和第二极之间连接有电容c11,晶体管m11的控制极还用于通过电感l11连接所述第一低噪声放大器的输入信号的正端;晶体管m11的控制极还通过电容c13与晶体管m15的第一极连接,晶体管m15的第二极接地;晶体管m12的控制极和第二极之间连接有电容c12,晶体管m12的控制极还用于通过电感l12连接所述第一低噪声放大器的输入信号的负端;晶体管m12的控制极还通过电容c14与晶体管m16的第一极连接,晶体管m16的第二极接地;所述晶体管m13的第二极与晶体管m11的第一极连接;所述晶体管m13的控制与晶体管m14的控制极连接,并用于接收电压信号v

cas1

;晶体管m13的第一极与电容c10的一端连接,电容c10的另一端与晶体管m14的第一极连接;晶体管m13的第一极还与电感l10的第一端连接,电感l10的第二端与晶体管m14的第一极连接,电感l10的第三端用于接收工作电压v

dd

;晶体管m14的第二极与晶体管m12的第一极连接;所述晶体管m11的控制极还通过所述偏置切换电路接收所述直流偏置电压信号v

b1

或所述直流偏置电压信号v

b2

;所述晶体管m12的控制极还通过所述偏置切换电路接收所述直流偏置电压信号v

b1

或所述直流偏置电压信号v

b2

;其中,所述第一切换信号包括第一状态的控制电压v

en

和第二状态的控制电压v

blk

,当接收到所述第一切换信号时,所述偏置切换电路响应于所述第一状态的控制电压v

en

将所述直流偏置电压信号v

b1

从所述晶体管m11的控制极断开,以及响应于所述第二状态的控制电压v

blk

将所述直流偏置电压信号v

b2

接入到所述晶体管m11的控制极;所述第二切换信号包括第二状态的控制电压v

en

和第一状态的控制电压v

blk

,当接收到所述第二切换信号时,所述偏置切换电路响应于所述第二状态的控制电压v

en

将所述直流偏置电压信号v

b1

接入到所述晶体管m11的控制极,以及响应于所述第一状态的控制电压v

blk

将所述直流偏置电压信号v

b2

从所述晶体管m11的控制极断开;所述晶体管m15和晶体管m16的控制极还用于接收所述控制电压v

en

;所述晶体管m13的第一极、

晶体管m14的第一极分别作为所述第一低噪声放大器输出的负端和正端。一些实施例中,所述第一态为低电平,所述第二态为高电平。

[0114]

一些实施例中,所述晶体管m11和晶体管m12为相同参数的晶体管;所述晶体管m13和晶体管m14为相同参数的晶体管;所述晶体管m15和晶体管m16为相同参数的晶体管;所述电感l11和电感l12为相同参数的电感;所述电容c11和电容c12为相同参数的电容;所述电容c13和电容c14为相同参数的电容。例如图10(b)是第一低噪声放大器10的另一个例子。

[0115]

第一低噪声放大器10中全差分结构能保证阻塞抵消过程中信号相位失配最小。第一级的噪声放大器即第一低噪声放大器10,由电感退化cs结构的动态输入匹配网络组成。动态偏置电压v

b2

由阻塞信号提取和偏置产生电路30在第一低噪声放大器10输出节点处感知的阻塞强度而产生。

[0116]

以上是第一低噪声放大器10的一些说明,下面对阻塞信号提取和偏置产生电路30进行说明。

[0117]

阻塞信号提取和偏置产生电路30用于从第一低噪声放大器10的输出信号中提取阻塞信号,并输出一与阻塞信号的强度呈反向关系的直流电压信号,也即阻塞信号的强度越大,直流电压信号越小,阻塞信号的强度越小,直流电压信号越大;该直流电压信号作为上述的直流偏置电压信号v

b2

,即作为第一低噪声放大器10在阻塞模式下的偏置信号。

[0118]

请参照图11,一些实施例中的阻塞信号提取和偏置产生电路30包括包络检测电路31和直流信号提取电路33。

[0119]

包络检测电路31检测第一低噪声放大器10的输出信号的包络,并输出与包络的幅度呈反向关系的信号,也即所检测到的包络的幅度越大,则包络检测电路31输出的信号越小,所检测到的包络的幅度越小,则包络检测电路31输出的信号越大。

[0120]

请参照图12(a),一些实施例中,包络检测电路31包括晶体管m30、晶体管m31、晶体管m32、电感l31、电感l32、电容c31和电容c32。晶体管m31的第一极与晶体管m32的第一极连接,晶体管m31的第二极接地,晶体管m31的控制极还通过电感l31接收偏置电压v

th1

;晶体管m31的控制极与电容c31的一端连接,电容c31的另一端作为所述包络检测电路输入的负端;晶体管m32的第二极接地,晶体管m32的控制极还通过电感l32接收偏置电压v

th2

;一些实施例中,所述偏置电压v

th1

的值所述晶体管m31的阈值电压的值;所述偏置电压v

th2

的值所述晶体管m32的阈值电压的值。晶体管m32的控制极与电容c32的一端连接,电容c32的另一端作为所述包络检测电路输入的正端;晶体管m30的第一极与晶体管m31的第一极连接,晶体管m30的第二极用于接收工作电压v

dd

,晶体管m30的控制极用于接收电压v

ben

;晶体管m31的第一极还作为所述包络检测电路的输出端。

[0121]

一些实施例中,所述晶体管m31和晶体管m32为相同参数的晶体管;所述电感l31和电感l32为相同参数的电感;所述电容c31和电容c32为相同参数的电容。例如图12(b)是包络检测电路31的另一个例子。

[0122]

直流信号提取电路33用于从包络检测电路31的输出信号中提取直流电压信号,作为所述直流偏置电压信号v

b2

。一些实施例中,所述直流信号提取电路33包括低通滤波器lpf。

[0123]

图12(a)和图12(b)是差分包络检测电路。第一低噪声放大器10输出端的信号(即输出信号)会被耦合到包络检测电路31,电压v

b2

由不同振幅的检测信号(即包络检测电路31

的输出信号)经低通滤波器lpf产生。晶体管m

d

被偏置在其阈值电压附近以最大化跨导效率。随着阻塞信号振幅的增加,电压v

b2

下降。阻塞信号vout

–

或vout 的振幅与电压v

b2

间的仿真关系如图13所示。改变电压v

ben

可以使特性曲线上下移动,以满足最佳的动态偏置需求。

[0124]

以上是阻塞信号提取和偏置产生电路30的一些说明,下面对偏置切换电路40进行说明。

[0125]

偏置切换电路40用于将第一低噪声放大器10在阻塞模式和小信号模式之间切换;偏置切换电路40通过将第一低噪声放大器10的偏置信号切换为直流偏置电压信号v

b1

,以将所述第一低噪声放大器10切换为小信号模式;偏置切换电路40通过将第一低噪声放大器10的偏置信号切换为直流偏置电压信号v

b2

,以将第一低噪声放大器10切换为所述阻塞模式。

[0126]

一些实施例中,偏置切换电路40可以包括开关电路,例如上文所涉及的开关sv

b1

和开关sv

b2

,这两者可以通过第一切换信号和第二切换信号来控制。例如所述第一切换信号包括第一状态的控制电压v

en

和第二状态的控制电压v

blk

,当接收到所述第一切换信号时,所述偏置切换电路响应于所述第一状态的控制电压v

en

将所述直流偏置电压信号v

b1

从所述晶体管m11的控制极断开,以及响应于所述第二状态的控制电压v

blk

将所述直流偏置电压信号v

b2

接入到所述晶体管m11的控制极;所述第二切换信号包括第二状态的控制电压v

en

和第一状态的控制电压v

blk

,当接收到所述第二切换信号时,所述偏置切换电路响应于所述第二状态的控制电压v

en

将所述直流偏置电压信号v

b1

接入到所述晶体管m11的控制极,以及响应于所述第一状态的控制电压v

blk

将所述直流偏置电压信号v

b2

从所述晶体管m11的控制极断开。

[0127]

偏置切换信号产生电路50用于将直流偏置电压信号v

b2

与一预设的参考电压信号v

ref

进行比较,当直流偏置电压信号v

b2

小于参考电压信号v

ref

时,则偏置切换信号50产生电路产生上述的第一切换信号,第一切换信号用于使得偏置切换电路40将第一低噪声放大器10切换或维持为阻塞模式;反之,当直流偏置电压信号v

b2

大于参考电压信号v

ref

时,则偏置切换信号产生电路50产生上述的第二切换信号,第二切换信号用于使得偏置切换电路40将第一低噪声放大器10切换或维持为小信号模式。

[0128]

一些实施例中,偏置切换信号产生电路50包括比较器comp。请参照图14,一些实施例中,比较器comp用于将直流偏置电压信号v

b2

与一预设的参考电压信号v

ref

进行比较,当直流偏置电压信号v

b2

小于所述参考电压信号v

ref

时,比较器comp输出低电平的控制电压v

en

和高电平的控制电压v

blk

,作为所述第一切换信号;当直流偏置电压信号v

b2

大于所述参考电压信号v

ref

时,比较器comp输出高电平的控制电压v

en

和低电平的控制电压v

blk

,作为所述第二切换信号。

[0129]

通过偏置切换信号产生电路50和阻塞信号提取和偏置产生电路30配合工作,可以决定切换工作模式的阻塞强度应该多大。比较器comp所涉及的传递函数如图15所示。当比较器comp的参考电压v

ref

被设置为0.4v,根据图15可知,当vout

‑

(即图10(b)中的输出端口)处的信号摆幅小于350mv时,第一低噪声放大器10将在小信号模式下工作,反之,将切换到阻塞模式下。用户可以参考第一低噪声放大器10的1db压缩点和图13来设置参考电压v

ref

的值。

[0130]

第二低噪声放大器20与第一低噪声放大器10连接,用于同时被a类偏置电压v

ba

和c类偏置电压v

bc

所偏置,以对第一低噪声放大器10的输出信号进行阻塞消除和放大。

[0131]

请参照图16(a),一些实施例中,第二低噪声放大器20包括晶体管m21、晶体管m22、晶体管m23、晶体管m24、晶体管m25、晶体管m26、电感l20、电感l21、电感l22、电感l23、电感l24、电容c20、电容c21、电容c22、电容c23和电容c24;所述晶体管m21的第一极与晶体管m24的第一极连接,晶体管m21的第二极接地,晶体管m21的控制极还通过电感l21接收所述c类偏置电压v

bc

;晶体管m21的控制极还与电容c21的一端连接,电容c21的另一端与电容c23的一端连接,电容c23的另一端与晶体管m23的控制极连接,晶体管m23的控制极还通过电感l23接收所述a类偏置电压v

ba

;晶体管m23的第二极接地;电容c21与电容c23连接的那端,还作为所述第二低噪声放大器输入的负端;所述晶体管m22的第一极与晶体管m23的第一极连接,晶体管m22的第二极接地,晶体管m22的控制极还通过电感l22接收所述c类偏置电压v

bc

;晶体管m22的控制极还与电容c22的一端连接,电容c22的另一端与电容c24的一端连接,电容c24的另一端与晶体管m24的控制极连接,晶体管m24的控制极还通过电感l24接收所述a类偏置电压v

ba

;晶体管m24的第二极接地;电容c22与电容c24连接的那端,还作为所述第二低噪声放大器输入的正端;所述晶体管m25的第二极与晶体管m21的第一极连接;所述晶体管m25的控制与晶体管m26的控制极连接,并用于接收电压信号v

cas2

;晶体管m25的第一极与电容c20的一端连接,电容c20的另一端与晶体管m26的第一极连接;晶体管m25的第一极还与电感l20的第一端连接,电感l20的第二端与晶体管m26的第一极连接,电感l20的第三端用于接收工作电压v

dd

;晶体管m26的第二极与晶体管m22的第一极连接;所述晶体管m25的第一极、晶体管m26的第一极分别作为所述第二低噪声放大器输出的负端和正端。

[0132]

一些实施例中,所述晶体管m21和晶体管m22为相同参数的晶体管;所述晶体管m23和晶体管m24为相同参数的晶体管;所述晶体管m25和晶体管m26为相同参数的晶体管;所述电感l21和电感l22为相同参数的电感;所述电感l23和电感l24为相同参数的电感;所述电容c21和电容c22为相同参数的电容;所述电容c23和电容c24为相同参数的电容。例如图16(b)为第二低噪声放大器20的另一个例子。

[0133]

第二低噪声放大器20的全差分结构能保证阻塞抵消过程中信号相位失配最小。第二低噪声放大器20为抵消级。大的w

c

可以确保施加较低的v

bc

来保证良好的c类偏置,也可以在阻塞模式下提供较大的小信号增益,然而w

c

的取值需要和引入的影响工作频率的寄生电容做折中。因此一些实施例中,w

c

设为192um,v

bc

的范围设置为0

‑

100mv。a类偏置电压v

ba

的调谐范围应该尽可能大来匹配晶体管m

c

的阻塞电流,因此w

a

应当小于wc,一些实施例中可以取16um。同时应避免阻塞模式下晶体管m

a

处于c类工作状态恶化低噪声放大器的噪声或处于线性区,即晶体管m

a

的偏置电压v

ba

应处于其阈值电压和电压m

cas2

之间。

[0134]

请参照图17,一些实施例中阻塞信号抵消低噪声放大器系统还包括缓冲器60,缓冲器60用于接收第二低噪声放大器20的输出信号,缓冲器60的输出作为所述阻塞信号抵消低噪声放大器系统的输出。

[0135]

以上是本技术一些实施例中阻塞信号抵消低噪声放大器系统的说明。

[0136]

一些实施例中,本技术的阻塞信号抵消低噪声放大器系统可以由65nm cmos工艺制造,芯片面积(包括输出驱动)为0.88

×

0.59mm2。在小信号模式,1.2v电源电压下静态消耗电流为17

‑

20ma,在

‑

15/

‑

10dbm阻塞下消耗23/25ma电流。

[0137]

先对阻塞抵消效果和相位不匹配进行仿真和说明。

[0138]

图18(a)、图18(b)和图18(c),展示了图16(b)中晶体管m

a

、晶体管m

c

和晶体管m

cas2

的阻塞抵消点的电流频谱,其横坐标为频率freq,单位为ghz,纵坐标为电流mag,单位为ma。当一个2.48ghz、

‑

15dbm的阻塞和2.4ghz、

‑

50dbm的期望小信号混合输入系统时,晶体管m

a

、晶体管m

c

和晶体管m

cas2

都含有2.4ghz,2.48ghz成分和交调产物。在图18(a)和图18(b)中,通过调整电压v

ba

和v

bc

让晶体管m

a

和晶体管m

c

阻塞电流频谱值的绝对值相等来最大化抵消效果,分别为5.22ma和5.2ma。在抵消后,晶体管m

cas2

中的阻塞电流降低至244.2ua。剩余小信号电流变为80.7ua。

[0139]

虽然抵消阻塞过程中会存在2.56ghz的互调分量,但其距离理想信号频段为阻塞的两倍。并且lna的窄带特性也会进一步抑制互调的放大。如果接收机采用高性能本振做下变频处理,互调分量不会造成显著的相互混频问题。

[0140]

图19为晶体管m

a

和晶体管m

c

中阻塞电流的瞬态仿真结果。晶体管m

a

和晶体管m

c

中的电流相位对齐效果较好,表明实现了最大的相位匹配;但额外不可避免的相位失配问题会由版图设计和制造过程中引入,但该误差影响通常非常微小。

[0141]

再对s参数和噪声系数nf进行仿真和说明。

[0142]

小信号情况的后仿真s参数如图20所示。在工作频率为2.4ghz下,系统增益为27db,

‑

3db带宽为160mhz,nf为2.55db。s11和s22在2.2

‑

2.8ghz范围内小于

‑

10db,这表明输入输出匹配良好。反向隔离度s12低于

‑

90db。通过调谐v

ba

(0.4v

‑

0.7v),增益范围为27

‑

33db。

[0143]

当一个单音的2.48ghz、

‑

15dbm阻塞信号注入并调整系统至抵消后,如图21所示在2.4ghz增益为24.4db。由于引入了晶体管m

c

的寄生电容增益峰值略向低频移动。在动态输入匹配和偏置策略的帮助下,s11和s22在2.2

‑

2.8ghz范围内仍保持在

‑

10db以下。nf从小信号模式的2.54db上升到5.75db。图22还给出了

‑

10dbm阻塞时的性能。在2.4ghz时,增益为19.4db,nf为6.72db。当没有阻塞时,2.4ghz的1db压缩点p1db为

‑

33.2dbm。在为

‑

15dbm和

‑

10dbm阻塞下,2.4ghz处的仿真p1db分别为

‑

18dbm和

‑

15dbm。由于测试用输出驱动会限制p1db,但低噪声放大器的输出往往连接到下一级混频器,这种情况下p1db会得到缓解。

[0144]

图23的表格对本技术和其他阻塞过滤射频前端结构的性能进行了总结和比较,其中文献8所涉及的为接收机。在2.4ghz,本技术小信号模式下功耗在24mw以内,nf为2.54db。与文献7的方案相比两种模式下,本技术的nf、功耗和核心面积都明显降低,也解决了互相混频的问题。和文献1的方案相比,本技术小信号模式的nf有所下降。

[0145]

本技术一些实施例提出了一种新的在拥挤频段直接于时域上抵消阻塞信号的低噪声放大器结构。采用动态输入匹配和偏置技术,在小信号模式下,2.4ghz处该lna的nf为2.54db,增益可达27

‑

33db。在80mhz、

‑

15/10dbm的阻塞下,nf和增益分别为5.75/6.72db和24.4/19.4db的增益,功耗为27.6/30mw。本技术一些实施例在阻塞处理中不使用本振、混频器和滤波器,实现了抵消阻塞时最小的相位失配,且不会引入相互混频问题。然而在电感退化输入匹配网络结构下,过大的阻塞功率会容易使晶体管饱和、非线性效应会增强,从而恶化输入匹配的效果和阻塞消除的能力。

[0146]

本文参照了各种示范实施例进行说明。然而,本领域的技术人员将认识到,在不脱离本文范围的情况下,可以对示范性实施例做出改变和修正。例如,各种操作步骤以及用于执行操作步骤的组件,可以根据特定的应用或考虑与系统的操作相关联的任何数量的成本函数以不同的方式实现(例如一个或多个步骤可以被删除、修改或结合到其他步骤中)。

[0147]

虽然在各种实施例中已经示出了本文的原理,但是许多特别适用于特定环境和操作要求的结构、布置、比例、元件、材料和部件的修改可以在不脱离本披露的原则和范围内使用。以上修改和其他改变或修正将被包含在本文的范围之内。

[0148]

前述具体说明已参照各种实施例进行了描述。然而,本领域技术人员将认识到,可以在不脱离本披露的范围的情况下进行各种修正和改变。因此,对于本披露的考虑将是说明性的而非限制性的意义上的,并且所有这些修改都将被包含在其范围内。同样,有关于各种实施例的优点、其他优点和问题的解决方案已如上所述。然而,益处、优点、问题的解决方案以及任何能产生这些的要素,或使其变得更明确的解决方案都不应被解释为关键的、必需的或必要的。本文中所用的术语“包括”和其任何其他变体,皆属于非排他性包含,这样包括要素列表的过程、方法、文章或设备不仅包括这些要素,还包括未明确列出的或不属于该过程、方法、系统、文章或设备的其他要素。此外,本文中所使用的术语“耦合”和其任何其他变体都是指物理连接、电连接、磁连接、光连接、通信连接、功能连接和/或任何其他连接。

[0149]

具有本领域技术的人将认识到,在不脱离本发明的基本原理的情况下,可以对上述实施例的细节进行许多改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。