1.本发明涉及一种可配置分数分频器,特别是一种用于多相时钟输入的可配置分数分频器,属于集成电路技术领域。

背景技术:

2.在电路设计中,通常采用分频器从一个高频率输入时钟产生另一个低频率输出时钟,以满足电路中不同单元对时钟的频率要求。分频器一般分为整数分频器和分数分频器。整数分频器一般通过计数器即可实现,实现方法简单。

3.分数分频器通常采用σ

‑

δ调制控制整数分频,使整数分频的平均值达到分数分频目标,从而实现分数分频功能。但采用σ

‑

δ调制设计的分数分频器电路结构较为复杂,所需电路面积和功耗较大,分频值唯一,且需要考虑量化噪声的抑制。

技术实现要素:

4.本发明解决的技术问题是:克服现有技术的不足,提出一种可配置分数分频器,降低分数分频器复杂度,减少分数分频器的面积和功耗,提升分数分频值灵活性,可广泛的应用于可编程逻辑、可重构电路的设计中。

5.本发明解决技术的方案是:

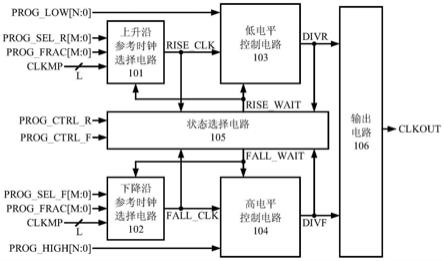

6.一种可配置分数分频器,包括上升沿参考时钟选择电路、下降沿参考时钟选择电路、低电平控制电路、高电平控制电路、状态选择电路和输出电路,

7.上升沿参考时钟选择电路和下降沿参考时钟选择电路采用相同的电路结构,低电平控制电路和高电平控制电路采用相同的电路结构;

8.可配置分数分频器接收l个输入时钟clkmp,通过配置信号控制输出时钟边沿翻转时刻和高低电平持续时间,产生所需频率的输出时钟clkout;clkmp需满足频率相同相位相差360

°

/l的要求。

9.进一步的,上升沿参考时钟选择电路通过配置输入信号prog_sel_r[m:0]、prog_frac[m:0]和内部控制信号rise_wait的控制,从l个时钟输入信号clkmp中选择其中一个时钟信号输出到内部时钟信号rise_clk,rise_clk传输到低电平控制电路和状态选择电路,用作clkout上升沿翻转时刻的参考时钟。

[0010]

进一步的,下降沿参考时钟选择电路通过配置输入信号prog_sel_f[m:0]、prog_frac[m:0]和内部控制信号fall_wait的控制,从l个时钟输入信号clkmp中选择其中一个时钟信号输出到内部时钟信号fall_clk,fall_clk传输到高电平控制电路和状态选择电路,用作clkout下降沿翻转时刻的参考时钟。

[0011]

进一步的,低电平控制电路接收配置输入信号prog_low[n:0]、内部控制信号rise_wait和内部时钟信号rise_clk,当rise_wait为高电平时,低电平控制电路准备低电平初始计数值prog_low[n:0];当rise_wait为低电平时,在rise_clk的每个上升沿,低电平控制电路执行低电平计数值减1,直到减到0为止;当低电平计数值为0时,低电平控制电路

计数指示信号divr同步输出半个rise_clk时钟周期宽度的高电平脉冲。

[0012]

进一步的,高电平控制电路接收配置输入信号prog_high[n:0]、内部控制信号fall_wait和内部时钟信号fall_clk,当fall_wait为高电平时,高电平控制电路准备高电平初始计数值prog_high[n:0];当fall_wait为低电平时,在fall_clk的每个上升沿,高电平控制电路执行高电平计数值减1,直到减到0为止;当高电平计数值为0时,高电平控制电路计数指示信号divf同步输出半个fall_clk时钟周期宽度的高电平脉冲。

[0013]

进一步的,状态选择电路接收配置输入信号prog_ctrl_r、prog_ctrl_f、内部控制信号divr、divf和内部时钟信号rise_clk、fall_clk;在divr和divf的边沿,通过prog_ctrl_r、prog_ctrl_f、rise_clk、fall_clk的控制,rise_wait和fall_wait进行电平切换,实现对可配置分数分频器工作状态的控制。

[0014]

进一步的,输出电路接收内部控制信号divr、divf,当divr为高电平、divf为低电平时,clkout由低电平转到高电平;当divr为低电平、divf为高电平时,clkout由高电平转到低电平;当divr和divf均为低电平时,clkout输出保持不变;从而实现正确的分数分频功能。

[0015]

进一步的,配置信号的取值中,表示向下取整,表示向上取整,m、n表示信号的位数。

[0016]

本发明与现有技术相比的有益效果是:

[0017]

(1)本发明的可配置分数分频器,采用加法器、减法计数器和简单的控制逻辑实现,电路复杂度低,减小了电路所需面积和功耗;

[0018]

(2)本发明的可配置分数分频器,采用可配置控制信号配置分数分频值,提升了分数分频器的通用性和灵活性,可更广泛的应用于可编程逻辑、可重构电路的设计中。

附图说明

[0019]

图1为本发明的可配置分数分频器整体结构示意图;

[0020]

图2为本发明的可配置分数分频器中上升沿参考时钟选择电路和下降沿参考时钟选择电路示意图;

[0021]

图3为本发明的可配置分数分频器中低电平控制电路和高电平控制电路示意图;

[0022]

图4为本发明的可配置分数分频器中状态选择电路结构示意图;

[0023]

图5为本发明的可配置分数分频器中输出电路结构示意图;

[0024]

图6为本发明实施例八相时钟5.375分频波形图。

具体实施方式

[0025]

下面结合实施例对本发明作进一步阐述。

[0026]

图1为本发明的可配置分数分频器整体结构示意图。该分数分频器包括上升沿参考时钟选择电路101、下降沿参考时钟选择电路102、低电平控制电路103、高电平控制电路104、状态选择电路105和输出电路106。其中,上升沿参考时钟选择电路101和下降沿参考时钟选择电路102采用相同的电路结构,低电平控制电路103和高电平控制电路104采用相同

的电路结构。

[0027]

定义分数分频值为i.f,其中i为分频值的整数部分、f为分频值的分数部分。所述可配置分数分频器接收l(l≥4)相时钟clkmp,通过配置信号prog_ctrl_r、prog_ctrl_f、prog_sel_r[m:0]、prog_sel_f[m:0]、prog_frac[m:0]、prog_low[n:0]、prog_high[n:0]控制输出时钟边沿翻转时刻和高低电平持续时间实现分频功能,产生分频输出信号clkout。配置信号的取值如表1所示,其中,表示向下取整,表示向上取整。l相时钟clkmp需满足频率相同相位相差360

°

/l的要求,可来源于数控延时链、压控振荡器或其他可产生同频率多相位时钟的电路。l值决定了可配置分数分频器的分频值精度。定义分频值精度为p,p=1/l。

[0028]

表1配置信号取值

[0029][0030]

所述上升沿参考时钟选择电路101接收时钟输入信号clkmp、配置输入信号prog_sel_r[m:0]、prog_frac[m:0]和内部控制信号rise_wait。通过prog_sel_r[m:0]、prog_frac[m:0]和rise_wait的控制,从l个clkmp中选择其中一个时钟信号输出到内部时钟信号rise_clk。rise_clk传输到低电平控制电路103和状态选择电路105,用作clkout上升沿翻转时刻的参考时钟。

[0031]

所述下降沿参考时钟选择电路102接收时钟输入信号clkmp、配置输入信号prog_sel_f[m:0]、prog_frac[m:0]和内部控制信号fall_wait。通过prog_sel_f[m:0]、prog_frac[m:0]和fall_wait的控制,从l个clkmp中选择其中一个时钟信号输出到内部时钟信号fall_clk。fall_clk传输到高电平控制电路104和状态选择电路105,用作clkout下降沿翻转时刻的参考时钟。

[0032]

所述低电平控制电路103接收配置输入信号prog_low[n:0]、内部控制信号rise_

wait和内部时钟信号rise_clk。当rise_wait为高电平时,低电平控制电路103准备低电平初始计数值prog_low[n:0];当rise_wait为低电平时,在rise_clk的每个上升沿,低电平控制电路103执行低电平计数值减1,直到减到0为止。当低电平计数值为0时,低电平控制电路103计数指示信号divr同步输出半个rise_clk时钟周期宽度的高电平脉冲。

[0033]

所述高电平控制电路104接收配置输入信号prog_high[n:0]、内部控制信号fall_wait和内部时钟信号fall_clk。当fall_wait为高电平时,高电平控制电路104准备高电平初始计数值prog_high[n:0];当fall_wait为低电平时,在fall_clk的每个上升沿,高电平控制电路104执行高电平计数值减1,直到减到0为止。当高电平计数值为0时,高电平控制电路104计数指示信号divf同步输出半个fall_clk时钟周期宽度的高电平脉冲。

[0034]

所述状态选择电路105接收配置输入信号prog_ctrl_r、prog_ctrl_f、内部控制信号divr、divf和内部时钟信号rise_clk、fall_clk。在divr和divf的边沿,通过prog_ctrl_r、prog_ctrl_f、rise_clk、fall_clk的控制,rise_wait和fall_wait进行电平切换,实现对可配置分数分频器工作状态的控制。

[0035]

所述输出电路106接收内部控制信号divr、divf。当divr为高电平、divf为低电平时,clkout由低电平转到高电平;当divr为低电平、divf为高电平时,clkout由高电平转到低电平;当divr和divf均为低电平时,clkout输出保持不变。从而实现正确的分数分频功能。

[0036]

图2为本发明的可配置分数分频器中上升沿参考时钟选择电路和下降沿参考时钟选择电路示意图。该参考时钟选择电路包括加法器201和多路选择器202。

[0037]

所述加法器201输入端连接prog_sel_r[m:0]/prog_sel_f[m:0]、prog_frac[m:0]、rise_wait/fall_wait、rise_clk/fall_clk,输出端连接多路选择器202的选择信号rise_sel[m:0]/fall_sel[m:0]。配置信号prog_sel_r[m:0]/prog_sel_f[m:0]为选择信号rise_sel[m:0]/fall_sel[m:0]的初始值,在rise_wait/fall_wait为高电平后的rise_clk/fall_clk的第一个上升沿,加法器执行一次加法操作并输出到rise_sel[m:0]/fall_sel[m:0],实现rise_sel[m:0]/fall_sel[m:0]=rise_sel[m:0]/fall_sel[m:0] prog_frac[m:0]。

[0038]

所述多路选择器202输入端连接l相时钟clkmp和选择信号rise_sel[m:0]/fall_sel[m:0],根据选择信号rise_sel[m:0]/fall_sel[m:0]的控制选择相应相位的clkmp输出到rise_clk/fall_clk。

[0039]

图3为本发明的可配置分数分频器中低电平控制电路和高电平控制电路示意图。电平控制电路包括延迟电路301、加载电路302、减法计数器303和检测电路304。

[0040]

所述延迟电路301输入端连接rise_wait/fall_wait、rise_clk/fall_clk,输出端连接rise_wait_dl/fall_wait_dl。延迟电路301为一个异步置位、同步复位电路。当rise_wait/fall_wait从低电平切换到高电平时,rise_wait_dl/fall_wait_dl立即从低电平切换到高电平;当rise_wait/fall_wait从高电平切换到低电平时,rise_wait_dl/fall_wait_dl在遇到rise_clk/fall_clk的上升沿后才从高电平切换到低电平。

[0041]

所述加载电路302输入端连接prog_low[n:0]/prog_high[n:0]、rise_wait_dl/fall_wait_dl,输出端连接low_init[n:0]/high_init[n:0]。当rise_wait_dl/fall_wait_dl为高电平时,加载电路302将prog_low[n:0]/prog_high[n:0]传输到low_init[n:0]/

high_init[n:0],对减法计数器303赋初值;当rise_wait_dl/fall_wait_dl为低电平时,low_init[n:0]/high_init[n:0]输出为0。

[0042]

所述减法计数器303输入端连接low_init[n:0]/high_init[n:0]、rise_wait_dl/fall_wait_dl、rise_clk/fall_clk,输出端连接low_cnt[n:0]/high_cnt[n:0]。当rise_wait_dl/fall_wait_dl为高电平时,low_cnt[n:0]/high_cnt[n:0]输出为0;当rise_wait_dl/fall_wait_dl为低电平时,减法计数器303从初始值low_init[n:0]/high_init[n:0]开始在rise_clk/fall_clk上升沿每次执行减1计数,直到减到0为止。

[0043]

所述检测电路304输入端连接low_cnt[n:0]/high_cnt[n:0]、rise_wait_dl/fall_wait_dl、rise_clk/fall_clk,输出端连接divr/divf。当rise_wait_dl/fall_wait_dl为高电平时,divr/divf输出低电平;当rise_wait/fall_wait为低电平时,检测电路304对low_cnt[n:0]/high_cnt[n:0]进行检测,若low_cnt[n:0]/high_cnt[n:0]为0,divr/divf输出半个rise_clk/fall_clk时钟周期宽度的高电平脉冲,否则divr/divf持续输出低电平。

[0044]

图4为本发明的可配置分数分频器中状态选择电路示意图。状态选择电路包括反相器401、402、404、407、411、412、414、417,与门405、415,或非门406、416,带时钟端rs触发器403、413,rs触发器408、418,和初始化电路400。反相器401的输入端连接rs触发器408的输出端;反相器402的输入端连接上升沿指示信号divr;带时钟端rs触发器403的时钟端连接上升沿参考时钟rise_clk,低电平有效复位输入端连接反相器401的输出端,低电平有效置位输入端连接反相器402的输出端;反相器404的输入端连接配置信号prog_ctrl_f;与门405的一个输入端连接反相器404的输出端,另一个输入端连接下降沿指示信号divf;或非门406的一个输入端连接与门405的输出端,另一个输入端连接带时钟端rs触发器413的输出端;反相器407的输入端连接带时钟端rs触发器403的输出端;rs触发器408的低电平有效复位输入端连接或非门406的输出端,低电平有效置位输入端连接反相器407的输出端,输出端连接上升沿等待信号rise_wait。反相器411的输入端连接rs触发器418的输出端;反相器412的输入端连接下降沿指示信号divf;带时钟端rs触发器413的时钟端连接下降沿参考时钟fall_clk,低电平有效复位输入端连接反相器411的输出端,低电平有效置位输入端连接反相器412的输出端;反相器414的输入端连接配置信号prog_ctrl_r;与门415的一个输入端连接反相器414的输出端,另一个输入端连接上升沿指示信号divr;或非门416的一个输入端连接与门415的输出端,另一个输入端连接带时钟端rs触发器403的输出端;反相器417的输入端连接带时钟端rs触发器413的输出端;rs触发器418的低电平有效复位输入端连接或非门416的输出端,低电平有效置位输入端连接反相器417的输出端,输出端连接下降沿等待信号fall_wait。初始化电路400输出端连接rise_wait和fall_wait。带时钟端rs触发器403、413真值表如表2所示。rs触发器408、418真值表如表3所示。

[0045]

所述初始化电路400对rise_wait和fall_wait初始化为高电平,并在可配置分数分频器开始工作时,控制rise_wait从高电平切换到低电平。可配置分数分频开始工作后,根据prog_ctrl_r和prog_ctrl_f的不同,rise_wait和fall_wait在divr和divf的边沿进行电平切换,从而实现对可配置分数分频器工作状态的控制。当prog_ctrl_r=0时,在divr上升沿,fall_wait从高电平切换到低电平;在divr下降沿,rise_wait从低电平切换到高电平。当prog_ctrl_r=1时,在divr下降沿,rise_wait从低电平切换到高电平,fall_wait从

高电平切换到低电平。当prog_ctrl_f=0时,在divf上升沿,rise_wait从高电平切换到低电平;在divf下降沿,fall_wait从低电平切换到高电平。当prog_ctrl_f=1时,在divf下降沿,rise_wait从高电平切换到低电平,fall_wait从低电平切换到高电平。

[0046]

图5为本发明的可配置分数分频器中输出电路示意图。输出电路包括反相器501~502、rs触发器503、缓冲器504。反相器501的输入端连接下降沿指示信号divf;反相器502的输入端连接上升沿指示信号divr;rs触发器503的低电平有效复位输入端连接反相器501的输出端,低电平有效置位输入端连接反相器502的输出端;缓冲器504的输入端连接rs触发器503的输出端,输出端连接分频输出信号clkout。rs触发器503真值表如表3所示。通过divr和divf的触发控制clkout的翻转,从而实现分频功能。

[0047]

表2带时钟端rs触发器403、413真值表

[0048][0049][0050]

表3 rs触发器408、418、503真值表

[0051]

rnsnq00101010111保持

[0052]

图6为本发明实施例八相时钟5.375分频波形图。由图1所述可知,八相时钟分频值精度p为0.125,分频值为5.375时满足分频值精度要求,clkmp时钟个数l为8且相位相差45

°

,分频值整数部分i为5,分频值分数部分f为375。m为2,n不小于1,各配置信号赋值情况为:prog_ctrl_r为0,prog_ctrl_f为0,prog_sel_r为0,prog_sel_f为5,prog_frac为3,prog_low为2,prog_high为2。8个clkmp时钟分别为clkmp0(相位为0

°

)、clkmp1(相位为45

°

)、clkmp2(相位为90

°

)、clkmp3(相位为135

°

)、clkmp4(相位为180

°

)、clkmp5(相位为225

°

)、clkmp6(相位为270

°

)、clkmp7(相位为315

°

)。

[0053]

在时刻0之前,可配置分数分频器处于初始状态。各配置信号按相应值完成配置,clkmp正常输出八相时钟,rise_wait、fall_wait、rise_wait_dl、fall_wait_dl输出高电平,divr、divf、clkout输出低电平,rise_sel为prog_sel_r(取值为0),fall_sel为prog_sel_f(取值为5),low_init为prog_low(取值为2),high_init为prog_high(取值为2),low_cnt为0,high_cnt为0。

[0054]

在时刻0,可配置分数分频器开始工作。rise_wait从高电平切换到低电平。

[0055]

在时刻1,受rise_wait控制,所述低电平控制电路103中延迟电路301的输出rise_wait_dl在rise_clk的上升沿从高电平切换到低电平;受rise_wait_dl控制,所述低电平控制电路103中加载电路302输出low_init为0,所述低电平控制电路103中减法计数器303输出low_cnt从2开始执行减一计数。

[0056]

在时刻2,所述低电平控制电路103中减法计数器303计数输出low_cnt为0;所述低电平控制电路103中检测电路304检测到low_cnt为0时,输出divr输出半个rise_clk时钟周期宽度的高电平脉冲;divr由低电平切换到高电平时,所述状态选择电路105的输出fall_wait从高电平切换到低电平,所述输出电路106的输出clkout由低电平切换到高电平。

[0057]

在时刻3,divr输出高电平脉冲的过程完成,由高电平切换到低电平,所述状态选择电路105的输出rise_wait从低电平切换到高电平。受rise_wait控制,所述低电平控制电路103中延迟电路301输出rise_wait_dl从低电平切换到高电平。受rise_wait_dl控制,所述低电平控制电路103中加载电路302输出low_init为2。

[0058]

在时刻4,受fall_wait控制,在fall_clk上升沿所述高电平控制电路104中延迟电路301输出fall_wait_dl从高电平切换到低电平。受fall_wait_dl控制,所述高电平控制电路104中加载电路302输出high_init为0,所述高电平控制电路104中减法计数器303输出high_cnt从2开始执行减一计数。

[0059]

在时刻5,受rise_wait控制,所述上升沿参考时钟选择电路101中加法器201在rise_clk上升沿完成rise_sel=rise_sel prog_frac操作,输出rise_sel为5;所述上升沿参考时钟选择电路101中多路选择器202选择clkmp5输出到rise_clk。

[0060]

在时刻6,所述高电平控制电路104中减法计数器303计数输出high_cnt为0;所述高电平控制电路104中检测电路304检测到high_cnt为0时,输出divf输出半个fall_clk时钟周期宽度的高电平脉冲;divf由低电平切换到高电平时,所述状态选择电路105的输出rise_wait从高电平切换到低电平,所述输出电路106的输出clkout由高电平切换到低电平。

[0061]

在时刻7,divf输出高电平脉冲的过程完成,由高电平切换到低电平,所述状态选择电路105的输出fall_wait从低电平切换到高电平。受fall_wait控制,所述高电平控制电路104中延迟电路301输出fall_wait_dl从低电平切换到高电平。受fall_wait_dl控制,所述高电平控制电路104中加载电路302输出high_init为2。

[0062]

在时刻8,受rise_wait控制,在rise_clk上升沿,所述低电平控制电路103中延迟电路301输出rise_wait_dl从高电平切换到低电平。受rise_wait_dl控制,所述低电平控制电路103中加载电路302输出low_init为0,所述低电平控制电路103中减法计数器303输出low_cnt从2开始执行减一计数。

[0063]

在时刻9,受fall_wait控制,所述下降沿参考时钟选择电路102中加法器201在

fall_clk上升沿完成fall_sel=fall_sel prog_frac操作,输出fall_sel为0;所述下降沿参考时钟选择电路102中多路选择器202选择clkmp0输出到fall_clk。

[0064]

在时刻10,所述低电平控制电路103中减法计数器303计数输出low_cnt为0;所述低电平控制电路103中检测电路304检测到low_cnt为0时,输出divr输出半个rise_clk时钟周期宽度的高电平脉冲;divr由低电平切换到高电平时,所述状态选择电路105的输出fall_wait从高电平切换到低电平,所述输出电路106的输出clkout由低电平切换到高电平。

[0065]

至此,从时刻2到时刻10可配置分数分频器完成一次5.375分频,并周期往复完成后续分频。

[0066]

本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。