1.本发明涉及电流生成电路、驱动电路和电流调整方法。

背景技术:

2.存在电流生成电路,生成用于驱动开关元件的电流(例如,专利文献1)。现有技术文献专利文献

3.专利文献1:国际公开第2017/195864号

技术实现要素:

发明所要解决的技术问题

4.在将电流生成电路集成化时,例如,由于电路面积的要件,电流生成电路所生成的电流有时会受到布线电阻的影响。其结果是,电流生成电路有时无法生成目标电流。

5.本发明鉴于上述现有问题而完成,其目的在于提供一种能生成精度较高的电流的电流生成电路。用于解决技术问题的技术手段

6.解决上述问题的本发明的电流生成电路的第1方式包括:mos晶体管,该mos晶体管中,电源线和接地线中的任一条线与源极端子相连接;电压生成电路,该电压生成电路生成与所述一条线和所述源极端子之间的布线的电阻值相对应的第1电压;以及控制电路,该控制电路基于所述第1电压,使所述mos晶体管生成规定电流。

7.此外,本发明的电流生成电路的第2方式包括:2个以上的n个mos晶体管,该mos晶体管中,电源线和接地线中的任一条线与源极端子相连接;电压生成电路,该电压生成电路对于所述n个布线的每一个生成与所述一条线和所述n个mos晶体管各自的所述源极端子之间的所述n个布线各自的电阻值相对应的第1电压;以及控制电路,该控制电路基于所述n个所述第1电压,使所述n个所述mos晶体管生成规定电流。

8.此外,本发明的驱动电路的方式是基于第1信号使开关元件导通、基于第2信号使开关元件截止的驱动电路,其包括:pmos晶体管,该pmos晶体管中,电源线与源极端子相连接;电压生成电路,该电压生成电路生成与所述电源线和所述pmos晶体管的所述源极端子之间的第1布线电阻的电阻值相对应的第1电压;控制电路,该控制电路在所述第1信号被输入时,基于所述第1电压,使所述pmos晶体管生成用于对所述开关元件的栅极电容进行充电的规定电流;以及第1nmos晶体管,该第1nmos晶体管中,接地线与源极端子相连接,基于所述第2信号来导通,并对所述开关元件的所述栅极电容进行放电。

9.此外,本发明的电流调整方法的方式中,对电流生成电路执行第1步骤和第2步骤,所述电流生成电路包括:mos晶体管,该mos晶体管中,电源线和接地线中的任一条线与源极端子相连接;电压生成电路,该电压生成电路包含可变电阻电路,并生成与所述一条线和所述源极端子之间的布线的电阻值相对应的电压;以及控制电路,该控制电路基于所述电压

生成电路的电压,使所述mos晶体管生成电流,所述第1步骤中,测定所述mos晶体管所生成的电流,所述第2步骤中,对所述可变电阻电路的电阻值进行调整,以使得所述mos晶体管所生成的电流成为规定电流。发明效果

10.根据本发明,可以提供一种能生成精度较高的电流的电流生成电路。

附图说明

11.图1是示出功率模块100的结构的图。图2是示出lvic210的结构的图。图3是示出驱动电路410a的结构的一个示例的图。图4是示出可变电阻12a的一个示例的图。图5是对调整可变电阻时的驱动电路410a进行说明的图。图6是示出由半导体测试装置600执行的可变电阻12a的示例性调整方法700的图。图7是对调整可变电阻时的驱动电路410a进行说明的图。图8是示出开关53的示例性调整方法800的图。图9是示出将驱动电路410a用于驱动电路410、420、430的情况下的各相的输出电流的图。图10是示出驱动电路415的构成的一例的图。图11是示出驱动电路415的各相的输出电流的图。图12是示出驱动电路410b的结构的一个示例的图。图13是示出用于代替放电电路50的放电电路55的一个实施方式的图。

具体实施方式

12.相关申请的相互参照本技术基于2019年9月11日提交的日本专利申请特愿2019

‑

165321主张优先权,并援引其内容。

13.通过本说明书及附图的记载,至少以下事项变得明确。

14.=====本实施方式=====图1是示出本发明的一个实施方式即功率模块100的结构的图。功率模块100是驱动三相电动机120的半导体装置,包含功率转换用的桥式电路200、lvic210、hvic220、230、240、以及端子hu、hv、hw、lx、ly、lz、p、u、v、w、nx、ny、nz。

15.桥式电路200构成为包含igbt(insulated gate bipolar transistor:绝缘栅型双极型晶体管)300、301、302、303、304、305(以下称为“igbt300~305”)、fwd(free wheeling diode:回流二极管)310、311、312、313、314、315、以及电阻rx、ry、rz。

16.igbt300是u相的开关元件,igbt301是x相的开关元件,igbt300、301分别设有fwd310、311。

17.igbt302是v相的开关元件,igbt303是y相的开关元件,igbt302、303分别设有fwd312、313。

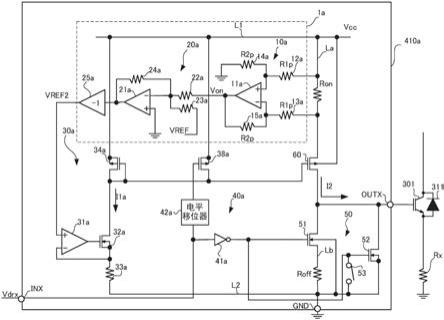

18.igbt304是w相的开关元件,igbt305是z相的开关元件,igbt304、305分别设有

fwd314、315。

19.另外,本实施方式中,作为功率模块100的开关元件,使用了igbt300~305,但例如也可以使用功率mos晶体管。

20.电阻rx、ry、rz分别是检测流过x相、y相、z相的开关元件的电流的电阻。

21.端子p施加有电源电压vdc,端子u、v、w设有负载即三相电动机120,端子nx、ny、nz接地。

22.hvic220、230、240分别是集成电路,用于根据经由端子hu、hv、hw输入的来自微机(未图示)的信号,对上臂的igbt300、302、304进行开关。

23.lvic210是集成电路,用于根据经由端子lx、ly、lz输入的来自微机(未图示)的驱动信号vdrx、vdry、vdrz,对下臂的igbt301、303、305进行开关。

24.如图2所示,lvic210包含用于三相的驱动电路410、420、430。

25.<<<驱动电路410a的结构>>>图3是示出驱动电路410的一个实施方式即驱动电路410a的结构的一个示例的图。驱动电路410a是通过使pmos晶体管60或nmos晶体管51导通来驱动igbt301的电路。驱动电路410a构成为包括:包含电压检测电路10a和加法电路20a的电压生成电路1a;控制电路30a;切换电路40a;放电电路50;以及pmos晶体管60。

26.<<电压生成电路1a>>电压生成电路1a是生成调整后的基准电压vref2的电路,该调整后的基准电压vref2与电源线l1和pmos晶体管60的源极端子之间的布线的电阻值相对应。

27.<<电压检测电路10a>>电压检测电路10a是生成调整电压von的电路,该调整电压von与电源线l1和pmos晶体管60的源极端子之间的布线la的布线电阻ron相对应。电压检测电路10a构成为包含运算放大器11a以及可变电阻12a、13a、14a、15a(以下称为“可变电阻12a~15a”)。

28.这里,pmos晶体管60中,流过用于驱动igbt301的大电流,因此尺寸变大。其结果是,集成电路内的pmos晶体管60的布线变长,因此,在pmos晶体管60的源极端子与电源线l1之间产生布线电阻ron。另一方面,pmos晶体管60的背栅极端子连接到电源线l1。然后,在pmos晶体管60中产生使pmos晶体管60的阈值电压上升的背栅效应。

29.因此,即使pmos晶体管60的栅极电压为所希望的电压,pmos晶体管60的输出电流值也根据pmos晶体管60的源极端子与电源线l1之间的布线电阻ron的值而偏离目标输出电流值。

30.因此,本实施方式中,为了抑制布线电阻ron的影响而设置了可变电阻12a~15a。另外,关于可变电阻12a~15a的详细情况,将在后文中阐述。

31.为了检测在布线电阻ron的两端之间产生的电压降,可变电阻12a、13a各自的一端连接到布线la的电源线l1附近、以及pmos晶体管60的源极端子附近。其中,图3中,为了便于理解,描述为可变电阻12a、13a的一端分别远离电源线l1附近、源极端子附近。

32.可变电阻12a的另一端连接到可变电阻14a的一端以及运算放大器11a的非反相输入端子。电阻元件14a的另一端接地。可变电阻13a的另一端连接到可变电阻15a的一端以及运算放大器11a的反相输入端子。可变电阻15a的另一端连接到运算放大器11a的输出端子。

33.此外,pmos晶体管60的背栅极端子连接到电源线l1。pmos晶体管60的漏极端子连

接到端子outx。

34.因此,电压检测电路10a所生成的、与布线电阻ron相对应的调整电压von成为(1)。

35.von=(r2p/r1p)

×

(v2p-v1p)

···

(1)这里,电阻值r1p是可变电阻12a、13a的电阻值,电阻值r2p是可变电阻14a、15a的电阻值。此外,电压v1p是将pmos晶体管60的源极端子与可变电阻13a相连接的节点的电压,电压v2p是将布线la的电源线l1与可变电阻12a相连接的节点的电压。

36.另外,布线电阻ron相当于“第1布线电阻”,电源线l1相当于“电源线”。此外,运算放大器11a相当于“电压输出电路”,可变电阻12a~15a相当于“可变电阻电路”,调整电压von相当于“第2电压”。

37.<<可变电阻12a的一个示例>>图4是示出可变电阻12a的一个示例的图。可变电阻电路是能利用所内置的开关使其电阻值变化的电路。另外,这里,对可变电阻12a进行说明,但可变电阻13a~15a也相同。

38.可变电阻12a例如构成为包含:电阻510、521、522、523、524、525、526(以下称为“电阻521~526”);开关540、551、552、553、554、555(以下称为“开关551~555”);以及eprom560。

39.可变电阻12a的电阻510的一端称为输入端子,另一端与电阻521~526各自的一端相连接。电阻521~525的另一端分别连接至开关551~555的一端。开关551~555的另一端和电阻526的另一端连接到可变电阻12a的输出端子。

40.此外,开关540连接在电阻510的一端与另一端之间,电阻526在输入端子与输出端子之间串联连接到电阻510。

41.开关540、551~555例如由mos晶体管构成。因此,开关540、551~555通过在晶片试验时存储在eprom560中的数据来设定导通或断开。

42.另外,本实施方式中,作为用于实现可变电阻12a的要素使用了芯片,但并不限于此。例如,为了实现可变电阻,也可以使用能进行齐纳切换的齐纳二极管、或能进行激光微调的多晶硅熔断器。

43.<<加法电路20a>>加法电路20a是如下电路:将调整电压von与规定的基准电压vref相加,并将由此得到的电压作为基准电压vref2来生成。加法电路20a构成为包含运算放大器21a、电阻22a、23a、24a(以下称为“电阻22a~24a”)、以及反相放大器25a。另外,详细内容将在后文中阐述,但调整电压von预先进行调整,以使得pmos晶体管60能生成规定的电流值。

44.电阻22a的一端连接到运算放大器11a的输出端子,电阻22a的另一端连接到运算放大器21a的反相输入端子。电阻23a的一端施加有基准电压vref,电阻23a的另一端连接到运算放大器21a的反相输入端子。电阻24a的一端连接到运算放大器21a的反相输入端子,电阻24a的另一端连接到运算放大器21a的输出端子。此外,运算放大器21a的非反相输入端子接地。此外,运算放大器21a的输出端子连接到反相放大器25a。此外,反相放大器25a输出调整后的基准电压vref2。

45.本实施方式中,电阻22a~24a的电阻值r相同,因此,调整后的基准电压vref2能如下那样来求出。

46.vref2=vref von

···

(2)

另外,加法电路20a相当于“加法电路”,基准电压vref2相当于“第1电压”。

47.<<控制电路30a>>控制电路30a是基于基准电压vref2使pmos晶体管60生成电流的电路。控制电路30a构成为包含运算放大器31a、nmos晶体管32a、电阻33a、pmos晶体管34a、pmos晶体管38a。

48.运算放大器31a的非反相输入端子施加有基准电压vref2。运算放大器31a的反相输入端子与电阻33a的一端以及nmos晶体管32a的源极端子相连接,上述电阻33a用于对流过nmos晶体管32a和pmos晶体管34a的电流i1a进行检测。

49.当pmos晶体管38a截止时,电流从被二极管连接的pmos晶体管34a被提供给nmos晶体管32a。然后,运算放大器31a对nmos晶体管32a进行控制,以使得反相输入端子的电压成为施加于非反相输入端子的基准电压vref2。

50.其结果是,由基准电压vref2和电阻33a的电阻值所确定的电流i1a流过被二极管连接的pmos晶体管34a。

51.此外,pmos晶体管34a与pmos晶体管60构成电流镜电路。因此,与流过pmos晶体管34a的电流i1a相对应的电流i2流过pmos晶体管60。

52.另外,pmos晶体管38a是用于基于电平移位器42a(后述)的输出来切换pmos晶体管34a和pmos晶体管60的导通、截止的元件。本实施方式中,当pmos晶体管38a截止时,pmos晶体管34a和pmos晶体管60进行动作,因此,pmos晶体管60生成电流i2。

53.另一方面,当pmos晶体管38a导通时,pmos晶体管34a和pmos晶体管60变为截止,因此电流i2的生成停止。

54.另外,接地线l2相当于“接地线”,将pmos晶体管60、电压检测电路10a、加法电路20a、控制电路30a组合后得到的电路相当于“电流生成电路”。

55.<<切换电路40a>>在来自微机(未图示)的驱动信号vdrx例如为低电平(以下,设为l电平)的情况下,为了使igbt301截止,切换电路40a使放电电路50动作。此外,在驱动信号vdrx例如为高定平(以下,设为h电平)的情况下,为了使igbt301导通,切换电路40a使由pmos晶体管p34a和pmos晶体管60构成的电流镜电路动作。

56.切换电路40a构成为包含逆变器41a和电平移位器42a。

57.逆变器41a使驱动信号vdrx的逻辑电平反转,并输出到放电电路50(后述)的nmos晶体管51、52的栅极端子。

58.电平移位器42a对驱动信号vdrx进行电平移位,并输出使控制电路30a的pmos晶体管38a导通/截止的信号。具体而言,若驱动信号vdrx成为h电平,则pmos晶体管38a截止,因此,pmos晶体管60生成电流i2。另一方面,若驱动信号vdrx成为l电平,则电平移位器42a使pmos晶体管38a导通,并将pmos晶体管34a的栅极端子上拉。其结果是,pmos晶体管60的电流i2的生成停止。

59.另外,h电平的驱动信号vdrx相当于“第1信号”,l电平的驱动信号vdrx相当于“第2信号”。

60.<<放电电路50>>放电电路50是用于在驱动信号vdrx成为l电平时使igbt301的栅极电容放电来使igbt301截止的电路。放电电路50构成为包含nmos晶体管51、52以及开关53。

61.nmos晶体管51、52的栅极端子连接到切换电路40a的逆变器41a的输出。nmos晶体管51、52的漏极端子连接到端子outx。

62.这里,nmos晶体管51中,流过用于对igbt301的栅极电容进行放电的大电流,因此尺寸变大。然后,在对集成电路内的nmos晶体管51进行布线时,在nmos晶体管51的源极端子与接电线l2之间产生布线电阻roff。此外,nmos晶体管51的背栅极端子与接地线l2相连接。

63.因此,在nmos晶体管51中产生使nmos晶体管51的阈值电压上升的背栅效应。因此,由于布线电阻roff与nmos晶体管51的背栅效果,有可能无法在短时间内对igbt301的栅极电容进行放电。

64.因此,本实施方式中,为了防止无法在短时间内对igbt301的栅极电容进行放电的情况,对nmos晶体管51设置了被并联连接的nmos晶体管52。

65.另外,nmos晶体管52在nmos晶体管51无法在短时间内对ibgt301的栅极电容进行放电的情况下进行动作即可。

66.因此,在对nmos晶体管51的放电进行辅助的nmos晶体管52的栅极端子与接地线l2之间连接有开关53。另外,详细内容将在后文中阐述,但在布线电阻roff与nmos晶体管51的导通电阻的合计比规定值要大的情况下开关53被断开。

67.此外,布线电阻roff相当于“第2布线电阻”,nmos晶体管51相当于“第1nmos晶体管”,nmos晶体管52相当于“第2nmos晶体管”。

68.<<可变电阻12a~15a的调整方法>>图5是用于对可变电阻12a~15a的调整进行说明的图。图5中,为了方便起见,仅显示主要的结构。

69.图6是示出由半导体测试装置600执行的可变电阻12a~15a的示例性调整方法700的图。另外,在后述的驱动电路410b、410c中也能同样地进行可变电阻的调整。

70.这里,在测试搭载有驱动电路410a的lvic210的晶片时,进行可变电阻12a~15a的调整。此外,对驱动电路410a提供电源。

71.首先,半导体测试装置600将h电平的驱动信号vdrx施加到端子inx,并对位于来自电压检测电路10a的输出端子的布线上的测试焊盘603施加测试电压vtest(s710)。另外,这里,电压检测电路10a停止来自使电压检测电路10a动作的偏置电流电路(未图示)的偏置电流,并停止动作。

72.若施加测试电压vtest,则加法电路20a将测试电压vtest与基准电压vref相加并输出调整后的基准电压vref2。控制电路30a中,流过与调整后的基准电压vref2和电阻33a的电阻值相对应的电流i1a。其结果是,pmos晶体管60中,流过与电流i1a相对应的、用于对igbt301的栅极电容进行充电的源极电流i2。

73.然后,当从端子outx输出了源极电流i2时,半导体测试装置600对与测试电压vtest相对应的源极电流i2进行测量(s720)。

74.此外,半导体测试装置600对测试电压vtest进行调整,以使得源极电流i2成为规定电流值ia(s730)。另外,若执行测试电压vtest的调整,则半导体测试装置600使偏置电流电路(未图示)动作,该偏置电流电路使电压检测电路10a动作。

75.然后,半导体测试装置600执行可变电阻12a~15a的电阻值的调整,以使得电压检测电路10a的调整电压von与电流i2等于规定电流值ia时的测试电压vtest变为相等

(s740)。

76.具体而言,半导体测试装置600生成存储于eprom560的数据,以使得电压检测电路10a的调整电压von与电流i2等于规定电流值ia时的测试电压vtest变为相等。其结果是,可变电阻12a的开关即mos晶体管基于eprom560的数据来导通或截止。

77.另外,在对可变电阻12a进行调整的要素中采用了能进行齐纳切换的齐纳二极管的情况下也相同。半导体测试装置600对齐纳二极管的两端施加电压,并烧断齐纳二极管,以使得电压检测电路10a的调整电压von与电流i2等于规定电流值ia时的测试电压vtest变为相等。

78.另外,在对可变电阻12a进行调整的要素中采用了能进行激光微调的多晶硅熔断器的情况下也相同。半导体测试装置600对熔断器照射激光来切断熔断器,以使得电压检测电路10a的调整电压von与电流i2等于规定电流值ia时的测试电压vtest变为相等。

79.另外,s710、s720、s730、s740相当于“电流调整方法”。此外,s720相当于“第1步骤”,s740相当于“第2步骤”。

80.以上,示出可变电阻12a~15a的调整方法的一个示例。还存在其它各种同样的调整方法,并可以采用这些调整方法。

81.<<开关53的调整方法>>图7是用于对开关53的调整进行说明的图,这里,为了方便起见,仅显示主要的结构。图8是示出开关53的示例性调整方法800的图。

82.另外,这里,半导体测试装置600在向驱动电路410a提供了电源的状态下,进行开关53的调整。

83.首先,半导体测试装置600在驱动电路410a向端子outx输出l电平的信号时,将规定电流提供给outx(s810)。这里,“规定电流”是成为规定的电流值(例如,1a)的电流。

84.此外,半导体测试装置600基于规定电流的电流值和端子outx的电压值,来测量nmos晶体管51的导通电阻与布线lb的布线电阻roff的合计的电阻值(s820)。

85.在测量结果表示电阻值比规定值要大的情况下,半导体测试装置600将使开关53断开的数据存储在eprom560中(s830)。

86.其结果是,当nmos晶体管51导通时,nmos晶体管52也导通。因此,放电电路50能防止igbt301的栅极电容的放电时间变长。

87.另外,与可变电阻12a的情况同样地,也可以用能进行齐纳切换的齐纳二极管、多晶硅熔断器等其它要素来实现开关53。

88.<<<驱动电路410a的动作>>>接着,对驱动电路410a的动作进行说明。另外,这里,图3的驱动电路410a的可变电阻12a~15a已通过执行图6的处理进行了调整,开关53通过执行图8的处理而被断开。

89.如驱动电路410a中的驱动信号vdrx成为h电平,则切换电路40a的逆变器41a将l电平的信号施加到nmos晶体管51、52的栅极端子,因此,nmos晶体管51、52截止。

90.另一方面,电平移位器42a将pmos晶体管43a的栅极端子设为h电平,因此,pmos晶体管43a截止。其结果是,pmos晶体管34a的栅极端子未被上拉,由pmos晶体管34a和pmos晶体管60构成的电流镜电路进行动作。

91.这里,电压检测电路10a生成与布线la的布线电阻ron的电阻值相对应的调整电压

von。然后,加法电路20a将调整电压von与基准电压vref相加,来生成调整后的基准电压vref2。

92.控制电路30a的运算放大器31a基于调整后的基准电压vref2和电阻33a来调整输出电压,以使得电流i1a流过。

93.其结果是,pmos晶体管60生成用于对igbt301的栅极电容进行充电的规定电流值ia,而与布线la的布线电阻ron的电阻值无关。

94.此外,若驱动信号vdrx成为l电平,则电平移位器42a将pmos晶体管38a的栅极端子设为l电平,因此,pmos晶体管38a导通。其结果是,pmos晶体管34a的栅极端子被上拉,pmos晶体管60截止。

95.另一方面,切换电路40a的逆变器41a将h电平的信号施加到nmos晶体管51、52的栅极端子,因此,nmos晶体管51、52导通。

96.其结果是,nmos晶体管51、52对igbt301的栅极电容进行放电。

97.<<<将驱动电路410a用于图2的驱动电路410、420、430的情况下的各相的输出电流>>>图9是示出将驱动电路410a分别用于图2的驱动电路410、420、430的情况下的各相的输出电流的图。另外,将驱动电路410a分别用于驱动电路410、420、430的情况是指如下情况:将驱动电路410设为驱动电路410a,将驱动电路420设为驱动电路410a,将驱动电路430设为驱动电路410a。

98.在对驱动电路410、420、430的每一个使用了驱动电路410a的情况下,一般情况下,驱动电路410、420、430各自的pmos晶体管60的源极侧的布线电阻ron具有较大不同。然而,在本实施方式的驱动电路410、420、430中,例如,执行如图6所示的调整方法。

99.其结果是,布线电阻ron的影响降低,驱动电路410、420、430能将各自的输出电流设为规定电流值ia。

100.另外,规定电流值ia是在pmos晶体管60为规定的尺寸的情况下输出的电流值。因此,在使pmos晶体管60的尺寸变化了的情况下,例如,通过执行图6所示的调整方法,也能使与pmos晶体管60的尺寸相对应的规定电流值ia流过。

101.由此,在使用将驱动电路410a分别用于驱动电路410、420、430而得的功率模块100的情况下,例如,能以较高精度使下臂侧的三相电流相一致。

102.<<<驱动电路415的结构>>>图10是示出一般的驱动电路415的结构的图。驱动电路415是决定源极电流的电流值的电路,该源极电流用于基于基准电压vref来驱动igbt301。驱动电路415构成为包含控制电路30a、切换电路40a、pmos晶体管60、nmos晶体管51。

103.控制电路30a、切换电路40a的结构与驱动电路410a相同,因此省略说明。此外,nmos晶体管51的动作与驱动电路410a相同。

104.另一方面,pmos晶体管60流过igbt301的源极电流仅由基准电压vref的电压值来确定。上述情况下,pmos晶体管60的源极电流受到布线la的布线电阻ron的电阻值的影响。

105.<<<将驱动电路415用于图2的驱动电路410、420、430的情况下的各相的输出电流>>>图11是示出将驱动电路415分别用于图2的驱动电路410、420、430的情况下的各相

的输出电流的图。另外,将驱动电路415分别用于驱动电路410、420、430的情况是指如下情况:将驱动电路410设为驱动电路415,将驱动电路420设为驱动电路415,将驱动电路430设为驱动电路415。

106.驱动电路415利用仅由基准电压vref的值来确定的源极电流的电流值来驱动igbt301。因此,驱动电路410、420、430分别受到布线la的布线电阻ron的电阻值的影响。其结果是,驱动电路410、420、430各自的输出电流将偏离规定电流值ia。

107.因此,在使用将一般的驱动电路415分别用于驱动电路410、420、430而得的功率模块100的情况下,例如,难以用较高精度使下臂侧的三相电流相一致。

108.<<<驱动电路410b的结构>>>图12是示出驱动电路410的一个实施方式即驱动电路410b的结构的一个示例的图。驱动电路410b构成为包含控制电路30a、切换电路40a、放电电路50、pmos晶体管60、分压电路70。

109.控制电路30a、切换电路40a、放电电路50和pmos晶体管60与驱动电路410a相同,因此省略说明。

110.<<分压电路70>>分压电路70是对规定的电压v1进行分压来生成调整后的基准电压vref2的电路。分压电路70构成为包含:电阻71、72、73、74(以下称为“电阻71~74”);以及开关75、76、77、78(以下称为“开关75~78”)。

111.电阻71~74串联连接在施加有规定的电压v1的一端与被接地的另一端之间。开关75~78分别与电阻71~74并联连接。

112.这里,分压电路70的开关的调整例如能用与上述图6同样的方法来实施。具体而言,半导体测试装置600调整开关75~78,以生成将pmos晶体管60的电流i2设为规定电流值ia的基准电压vref3。

113.其结果是,驱动电路410b能用规定电流值ia对igbt301的栅极电容进行充电,而与pmos晶体管60的源极侧的布线电阻ron的大小无关。

114.另外,与驱动电路410a同样地,可以将驱动电路410b分别用于图2的驱动电路410、420、430。该情况下,能以较高精度使各相的输出电流相一致。

115.此外,分压电路70相当于“可变电阻电路”,调整后的基准电压vref3相当于“第1电压”。此外,规定的电压v1相当于“规定电压”,提供调整后的基准电压vref3的节点相当于“规定的节点”。

116.<<<放电电路的其它结构>>>图13是示出用于代替放电电路50的放电电路55的一个实施方式的图。

117.放电电路55是用规定的电流i3对igbt301的栅极电容进行放电的电路,构成为包括:包含电压检测电路10b和加法电路20b的电压生成电路1b;控制电路30b;切换电路40b;以及nmos晶体管51。

118.<<电压生成电路1b>>电压生成电路1b是生成调整后的基准电压vref4的电路,该调整后的基准电压vref4与电源线l2和nmos晶体管51的源极端子之间的布线的电阻值相对应。

119.<<电压检测电路10b>>

电压检测电路10b是生成调整电压voff的电路,该调整电压voff与电源线l2和nmos晶体管51的源极端子之间的布线lb的布线电阻roff的电阻值相对应。电压检测电路10b构成为包含运算放大器11b以及可变电阻12b、13b、14b、15b(以下称为“可变电阻12b~15b”)。

120.另外,电压检测电路10b的结构与电压检测电路10a的结构相同,因此省略说明。另外,可变电阻12b~15b与可变电阻12a同样地进行调整。

121.<<加法电路20b>>加法电路20b是如下电路:将调整电压voff与基准电压vref相加,并将由此得到的电压作为调整后的基准电压vref4来输出。加法电路20b构成为包含运算放大器21b、电阻22b、23b、24b、以及反相放大器25b。

122.另外,加法电路20b的结构与加法电路20a的结构相同,因此省略说明。

123.<<控制电路30b>>控制电路30b是基于调整后基准电压vref4使nmos晶体管51生成电流的电路。控制电路30b构成为包含运算放大器31b、nmos晶体管32b、电阻33b、pmos晶体管35b、36b、以及nmos晶体管37b。

124.运算放大器31b的非反相输入端子被施加有调整后的基准电压vref4。运算放大器31b的反相输入端子与电阻33b的一端以及nmos晶体管32b的源极端子相连接,其中,上述电阻33b用于对流过nmos晶体管32b和pmos晶体管35b的电流i1b进行检测。此外,电阻33b的另一端连接到接地线l2。

125.电流从被二极管连接的pmos晶体管35b被提供至nmos晶体管32b。然后,运算放大器31b对nmos晶体管32b进行控制,以使得反相输入端子的电压成为施加于非反相输入端子的基准电压vref4。

126.其结果是,由基准电压vref4和电阻33b的电阻值所确定的电流i1b流过被二极管连接的pmos晶体管35b。

127.此外,pmos晶体管35b、36b构成电流镜电路,因此,与电流i1b相对应的电流流过被二极管连接的nmos晶体管37b。然后,nmos晶体管37b和nmos晶体管51也构成电流镜电路。因此,当nmos晶体管38b截止时,nmos晶体管51生成与电流i1b相对应的电流i3。

128.另外,nmos晶体管38b是用于基于驱动信号vdrx来切换nmoms晶体管37b和nmos晶体管51的导通、截止的元件。本实施方式中,当nmos晶体管38b截止时,nmos晶体管51生成与电流i1b相对应的电流i3。

129.另一方面,当nmos晶体管38b导通时,nmos晶体管51截止,因此,电流i3的生成停止。

130.这里,放电电路55中,可变电阻12b~15b通过上述图6的方法来调整。其结果是,放电电路55能以规定的电流值对igbt301的栅极电容进行放电,而与布线电阻roff的大小无关。

131.此外,若上述放电电路55分别用于驱动电路410、420、430,则功率模块100的下臂侧的三相灌电流以较高精度变得相一致。

132.===其他===本实施方式的电压检测电路10a、分压电路70对可变电阻的电阻值进行调整来生

成基准电压,但也可以使用其它方法来使电压检测电路10a、分压电路70生成所希望的电压(例如,调整电压von、基准电压vref2)。

133.例如,可以使用生成基于erpom中所存储的数字值的模拟电压的模拟

·

数字转换器,来生成所希望的电压。该情况下,模拟

·

数字转换器相当于“电压生成电路”。

134.===总结===以上,对本实施方式的功率模块100进行了说明。一般而言,在集成了功率模块100的多个驱动电路410、420、430的lvic210中,根据驱动电路的配置,驱动电路内的布线la、lb的布线电阻ron、roff变为不同。其结果是,无法使受到布线电阻ron的电阻值的影响的驱动电路410、420、430的输出电流接近目标值。然而,例如,本实施方式的驱动电路410a对由布线电阻ron、roff所产生的输出电流的变动进行调整。由此,能降低布线电阻ron、roff的影响,能使驱动电路410a的输出电流接近目标值。

135.此外,通过使pmos晶体管60、nmos晶体管51生成与布线la的布线电阻ron以及布线lb的布线电阻roff相对应的电流,从而能使驱动电路410a的输出电流接近目标值。

136.此外,利用生成与布线la的布线电阻ron的电阻值相对应的调整电压von的电压检测电路10a、加法电路20a,能对驱动电路410a的输出电流进行线性微调,能降低布线电阻ron的电阻值的影响。此外,假设在需要使驱动电路410a的输出电流的目标值变化的情况下,有时难以仅基于调整电压von来使输出电流接近目标值。然而,本实施方式中,能基于基准电压vref和调整电压von来使输出电流变化。因此,即使在使输出电流的目标值大幅变化的情况下,也能容易地调整输出电流的值。

137.此外,通过生成由分压电路70调整后的基准电压vref3,从而能以较小的电路规模来制造降低了布线电阻ron的电阻值的影响的驱动电路410b。

138.此外,驱动电路410a的电压检测电路10a、加法电路20a和控制电路30a如驱动电路410c的电压检测电路10b、加法电路20b和控制电路30b那样,也可以应用于使nmos晶体管51生成电流。

139.此外,在对3个(n个)驱动电路410、420、430分别使用了驱动电路410a的情况下,也能使各个驱动电路410、420、430的输出电流接近目标值。

140.此外,也可以实现将使pmos晶体管60生成igbt301的源极电流的电路、与使nmos晶体管51、52对igbt301的栅极电容进行放电的电路相组合而得的电路。该电路也能使对igbt301的栅极电容进行放电的电路的规模变小。

141.此外,通过测定流过驱动电路410a的端子outx的源极电流来调整可变电阻的电阻值,从而能调整为使流过端子outx的源极电流接近目标值。标号说明

142.100 功率模块,120 三相电动机,200 桥式电路,210 lvic,220、230、240 hvic,300~305 igbt,310~315 fwd,

410、410a、410b、410c、415、420、430 驱动电路,1a、1b 电压生成电路,10a、10b 电压检测电路,20a、20b 加法电路,30a、30b 控制电路,40a 切换电路,50、55 放电电路,70 分压电路,34a、43a、60、35b、36b、38a pmos晶体管,32a、51、52、32b、37b、38b nmos晶体管,53、75~78、540、551~555 开关,12a~15a、12b~15b 可变电阻,22a~24a、22b~24b、33a、33b、71~74、510、521~526 电阻,11a、21a、31a、11b、21b、31b 运算放大器,25a、25b 反相放大器,41a 逆变器,42 电平移位器,560 eprom。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。