一种用于瞬态抑制器的低触发高鲁棒性scr器件及保护电路

技术领域

1.本发明涉及集成电路静电防护技术领域,具体而言,涉及一种用于瞬态抑制器的低触发高鲁棒性scr器件及保护电路。

背景技术:

2.静电放电是集成电路可靠性的重要分支之一,集成电路在制造、运输与使用过程中都有可能因esd(electro

‑

static discharge,静电放电)而损坏。在集成电路中,二极管、mosfet,scr器件等都可以用来充当esd保护器件,其中scr器件是最具有效率的esd保护器件之一。scr器件由于其维持电压很低,所以能够承受很高的esd电流;因此,scr器件天然具有高的esd鲁棒性。相较其它esd保护器件,scr器件的单位面积esd保护能力最强。现有的scr器件虽然能够降低触发电压,但是可控性较差,并且scr器件中电容的电荷积累会影响的scr器件运行的可靠性。

技术实现要素:

3.本发明的目的在于提供一种用于瞬态抑制器的低触发高鲁棒性scr器件及保护电路,用以实现提高scr器件可控性和运行可靠性的技术效果。

4.第一方面,本发明提供了一种用于瞬态抑制器的低触发高鲁棒性scr器件,包括p型衬底;在所述p型衬底上从左到右依次设置且相邻接的第一p阱、n阱和第二p阱;所述第一p阱的表面区域间隔设置有第一p型重掺杂区和第一n型重掺杂区;所述n阱的表面区域间隔设置有第二n型重掺杂区和第二p型重掺杂区;所述第二p阱的表面区域间隔设置有第三n型重掺杂区和第三p型重掺杂区;且所述n阱与所述第二p阱的邻接处跨接有第四n型重掺杂区;所述第二n型重掺杂区和所述第二p型重掺杂区均与一个阳极端口相连;所述第一p型重掺杂区、所述第三n型重掺杂区和所述第三p型重掺杂区均与一个阴极端口相连;所述n阱位于所述第二p型重掺杂区和所述第四n型重掺杂区之间的表面上设有第一栅氧化层;所述第一栅氧化层的左侧边缘与所述第二p型重掺杂区的右侧边缘连接;所述第一栅氧化层的右侧边缘与所述第四n型重掺杂区的左侧边缘连接;所述第二p阱位于所述第三n型重掺杂区和所述第四n型重掺杂区之间的表面上设有第二栅氧化层;所述第二栅氧化层的右侧边缘与所述第三n型重掺杂区的左侧边缘连接;所述第二栅氧化层的左侧边缘与所述第四n型重掺杂区的左侧边缘连接;所述第一栅氧化层的上表面和所述第二栅氧化层的上表面均与所述第二n型重掺杂区连接。

5.进一步地,所述第一p型重掺杂区、所述第一n型重掺杂区、第二p型重掺杂区、所述第二n型重掺杂区、第三p型重掺杂区、所述第三n型重掺杂区和所述第四n型重掺杂区均呈条状排布。

6.进一步地,所述第一栅氧化层和所述第二栅氧化层均呈条状设置。

7.进一步地,所述第一栅氧化层和所述第二栅氧化层中至少有一个采用比例分割排布。

8.第二方面,本发明提供了一种保护电路,包括被保护电路以及设置在所述被保护电路上的上述低触发高鲁棒性scr器件。

9.本发明能够实现的有益效果是:本发明提供的用于瞬态抑制器的低触发高鲁棒性scr器件通过第一n型重掺杂区、第一p阱、n阱以及与阳极端口连接的第二p型重掺杂区构成了第一个scr器件;通过与阳极端口连接的第二p型重掺杂区、第二p阱、n阱以及与阴极端口连接的第三n型重掺杂区构成了第二个scr器件;同时通过第二p阱、n阱、第一栅氧化层、第二栅氧化层构成了rc电路;通过第三n型重掺杂区、第四n型重掺杂区和第二栅氧化层构成了寄生nmos器件,提高了scr器件的可控性和运行可靠性。

附图说明

10.为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

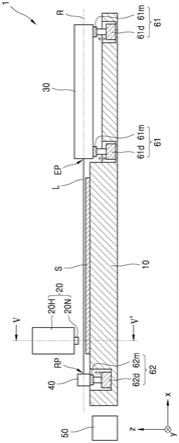

11.图1为本发明实施例提供的一种低触发高鲁棒性scr器件的剖切结构图;图2为本发明实施例提供的一种低触发高鲁棒性scr器件的等效电路图;图3为本发明实施例提供的第一种低触发高鲁棒性scr器件的俯视结构示意图;图4为本发明实施例提供的第二种低触发高鲁棒性scr器件的俯视结构示意图。

12.图标:10

‑

低触发高鲁棒性scr器件;100

‑

p型衬底;110

‑

第一p阱;111

‑

第一p型重掺杂区;112

‑

第一n型重掺杂区;120

‑

n阱;121

‑

第二n型重掺杂区;122

‑

第二p型重掺杂区;130

‑

第二p阱;131

‑

第三n型重掺杂区;132

‑

第三p型重掺杂区;140

‑

第四n型重掺杂区;150

‑

第一栅氧化层;160

‑

第二栅氧化层。

具体实施方式

13.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行描述。

14.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。同时,在本发明的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

15.请参看图1和图2,图1为本发明实施例提供的一种低触发高鲁棒性scr器件的剖切结构图;图2为本发明实施例提供的一种低触发高鲁棒性scr器件的等效电路图。

16.在一种实施方式中,本发明实施例提供了一种用于瞬态抑制器的低触发高鲁棒性scr器件10,该低触发高鲁棒性scr器件10包括p型衬底100;在p型衬底100上从左到右依次设置且相邻接的第一p阱110、n阱120和第二p阱130;第一p阱110的表面区域间隔设置有第一p型重掺杂区111和第一n型重掺杂区112;n阱120的表面区域间隔设置有第二n型重掺杂区121和第二p型重掺杂区122;第二p阱130的表面区域间隔设置有第三n型重掺杂区131和第三p型重掺杂区132;且n阱120与第二p阱130的邻接处跨接有第四n型重掺杂区140;第二n型重掺杂区121和第二p型重掺杂区122均与一个阳极端口相连;第一p型重掺杂区111、第三n型重掺杂区131和第三p型重掺杂区132均与一个阴极端口相连;n阱120位于第二p型重掺杂区122和第四n型重掺杂区140之间的表面上设有第一栅氧化层150;第一栅氧化层150的

左侧边缘与第二p型重掺杂区122的右侧边缘连接;第一栅氧化层150的右侧边缘与第四n型重掺杂区140的左侧边缘连接;第二p阱130位于第三n型重掺杂区131和第四n型重掺杂区140之间的表面上设有第二栅氧化层160;第二栅氧化层160的右侧边缘与第三n型重掺杂区131的左侧边缘连接;第二栅氧化层160的左侧边缘与第四n型重掺杂区140的左侧边缘连接;第一栅氧化层150的上表面和第二栅氧化层160的上表面均与第二n型重掺杂区121连接。

17.在上述实现过程中,通过第一n型重掺杂区112、第一p阱110、n阱120以及与阳极端口连接的第二p型重掺杂区122构成了第一个scr器件(scr1);通过与阳极端口连接的第二p型重掺杂区122、第二p阱130、n阱120以及与阴极端口连接的第三n型重掺杂区131构成了第二个scr器件(scr2);同时通过第二p阱130、n阱120、第一栅氧化层150、第二栅氧化层160构成了rc通路;通过第三n型重掺杂区131、第四n型重掺杂区140和第二栅氧化层160构成了寄生nmos器件,提高了scr器件的可控性和运行可靠性。

18.具体地,第一栅氧化层150与n阱120之间形成一个电容c

f

;第二栅氧化层160与第二p阱130之间可以形成一个电容c

g

。在正常工作时,rc通路开路,nmos器件关断,且scr1和scr2关断,该scr器件不影响被保护电路的正常工作,处于高阻状态。

19.在esd事件到来时,rc通路因为较大的dv/dt(电压上升速率)而导通,并对寄生nmos器件的栅电容充电,电容c

g

上的电压上升。当c

g

上的电压大于nmos器件的阈电压,nmos器件导通电流。nmos器件的电流从与阳极相连的第二n型重掺杂区121,经过n阱120后进入寄生nmos器件。由于n阱120电阻r

nw

的存在,当r

nw

上的压降使n阱120的p /nw结正偏,寄生pnp2管开启,该pnp2管的集电极电流流向第二p阱130内的p 区,并在第二p阱130电阻r

pw2

上产生压降使npn2管导通,第一个scr器件(scr1)导通。同时,由于p /nw结正偏,使pnp1导通,进而npn1导通,第二个scr器件(scr2)导通,泄放esd电流。同时,通过设计内部的rc通路的参数,能够主泄放器件的触发电压,使该触发电压可调制。

20.请参看图3和图4,图3为本发明实施例提供的第一种低触发高鲁棒性scr器件的俯视结构示意图;图4为本发明实施例提供的第二种低触发高鲁棒性scr器件的俯视结构示意图。

21.在一种实施方式中,第一p型重掺杂区111、第一n型重掺杂区112、第二p型重掺杂区122、第二n型重掺杂区121、第三p型重掺杂区132、第三n型重掺杂区131和第四n型重掺杂区140均呈条状排布。第一栅氧化层150和第二栅氧化层160均呈条状设置。

22.在一种实施方式中,第一栅氧化层150和第二栅氧化层160中至少有一个采用比例分割排布。通过这种方式在实现相同功能的情况下可以降低消耗的材料。

23.在一种实施方式中,本发明实施例还提供了一种保护电路,该保护电路包括被保护电路以及设置在被保护电路上的上述低触发高鲁棒性scr器件10。通过该保护电路可以提高整个电路运行的稳定性和可靠性。

24.综上所述,本发明实施例提供一种用于瞬态抑制器的低触发高鲁棒性scr器件及保护电路,包括p型衬底;在p型衬底上从左到右依次设置且相邻接的第一p阱、n阱和第二p阱;第一p阱的表面区域间隔设置有第一p型重掺杂区和第一n型重掺杂区;n阱的表面区域间隔设置有第二n型重掺杂区和第二p型重掺杂区;第二p阱的表面区域间隔设置有第三n型重掺杂区和第三p型重掺杂区;且n阱与第二p阱的邻接处跨接有第四n型重掺杂区;第二n型

重掺杂区和第二p型重掺杂区均与一个阳极端口相连;第一p型重掺杂区、第三n型重掺杂区和第三p型重掺杂区均与一个阴极端口相连;n阱位于第二p型重掺杂区和第四n型重掺杂区之间的表面上设有第一栅氧化层;第一栅氧化层的左侧边缘与第二p型重掺杂区的右侧边缘连接;第一栅氧化层的右侧边缘与第四n型重掺杂区的左侧边缘连接;第二p阱位于第三n型重掺杂区和第四n型重掺杂区之间的表面上设有第二栅氧化层;第二栅氧化层的右侧边缘与第三n型重掺杂区的左侧边缘连接;第二栅氧化层的左侧边缘与第四n型重掺杂区的左侧边缘连接;第一栅氧化层的上表面和第二栅氧化层的上表面均与第二n型重掺杂区连接。通过这种方式提高了scr器件的可控性和运行可靠性。

25.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。