2mhz/2mbit/s信号的抖动生成方法及系统

技术领域

1.本发明涉及信号处理领域,更具体地说,涉及一种2mhz/2mbit/s信号的抖动生成方法及系统。

背景技术:

2.信号的抖动会使数字电路的传输性能劣化,时钟或数据的抖动会影响到数据的建立、保持时间,在数据再生时,数据比特流中就会引入错误。

3.抖动分为系统抖动和随机抖动。

4.(1)系统抖动是在信号再生电路时间上不准,或是在幅频转换中的不准确的电缆均衡造成的。系统抖动取决于系统的性能。

5.(2)随机抖动来源于内部或是外部的干扰信号,如噪声、串扰、反射等。随机抖动与传输信号的系统无关。

6.itu

‑

t g.812规范定义了同步网中2.048mhz/2.048mbit/s信号的抖动产生、抖动容限、抖动传递函数测试方法和要求。要进行这些测试,需要使用仪表产生相应的附带抖动的2.048mhz/2.048mbit/s信号。

技术实现要素:

7.本发明要解决的技术问题在于,针对现有技术的上述缺陷,提供一种2mhz/2mbit/s信号的抖动生成方法及系统。

8.本发明解决其技术问题所采用的技术方案是:构造一种2mhz/2mbit/s信号的抖动生成方法,包括以下步骤:

9.s1、生成256mhz不带抖动的标准时钟;

10.s2、接收抖动整形数据;

11.s3、循环读取整形数据,根据数据来翻转抖动时钟。

12.优选地,所述步骤s1还包括以下步骤:

13.使用256m时钟产生一个抖动的2.048m时钟;

14.所述步骤s3中,根据数据来翻转抖动的2.048m时钟。

15.优选地,以256m时钟周期为步长,创建了一个计数器,每当计数值同读到的整形数据相等时,就把2mhz/2mbit/s信号的电平翻转一次。

16.优选地,所述步骤s1还包括以下步骤:

17.提供控制信号,所述控制信号包括初始的复位信号、向随机存取存储器写数据使能信号。

18.优选地,所述控制信号还包括表示一组按正弦变化数据中的数据总个数的信号。

19.优选地,所述控制信号还包括表示隔特定数量的2.048m时钟周期加抖动一次的信号。

20.一种2mhz/2mbit/s信号的抖动生成系统,包括:

21.抖动生成模块,用于生成2mhz/2mbit/s抖动时钟;

22.随机存取存储器,用于接收抖动整形数据;

23.控制器,循环从所述随机存取存储器读取整形数据,根据数据来翻转抖动时钟。

24.优选地,所述抖动生成模块使用256m时钟产生一个抖动的2.048m时钟,所述控制器根据数据来翻转抖动的2.048m时钟。

25.优选地,所述抖动生成模块以256m时钟周期为步长,创建了一个计数器,每当计数值同读到的整形数据相等时,就把2mhz/2mbit/s信号的电平翻转一次。

26.优选地,所述控制器提供控制信号,所述控制信号包括初始的复位信号、向随机存取存储器写数据使能信号、表示一组按正弦变化数据中的数据总个数的信号、表示隔特定数量的2.048m时钟周期加抖动一次的信号。

27.实施本发明的2mhz/2mbit/s信号的抖动生成方法及系统,具有以下有益效果:信号加抖动,需改变原来时钟信号的相位,通过循环读取整形数据,并根据整形数据来翻转抖动时钟,使抖动的处理完全电路化、数字化,抖动生成的分辨率高,抖动图样可以自定义,抖动生成即时设置即时生效,没有延时。

附图说明

28.下面将结合附图及实施例对本发明作进一步说明,附图中:

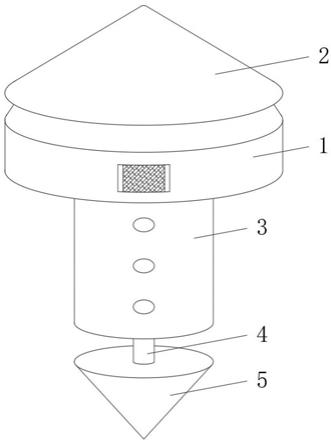

29.图1是本发明实施例中的2mhz/2mbit/s信号的抖动生成方法流程示意图;

30.图2是本发明实施例中的2mhz/2mbit/s信号的抖动生成系统电路原理示意图。

具体实施方式

31.为了对本发明的技术特征、目的和效果有更加清楚的理解,现对照附图详细说明本发明的具体实施方式。

32.如图1所示,本发明一个优选实施例中的2mhz/2mbit/s信号的抖动生成方法包括以下步骤:

33.s1、生成256mhz不带抖动的标准时钟;

34.s2、接收抖动整形数据;

35.s3、循环读取整形数据,根据数据来翻转抖动时钟。

36.信号加抖动,需改变原来时钟信号的相位,通过循环读取整形数据,并根据整形数据来翻转抖动时钟,使抖动的处理完全电路化、数字化,抖动生成的分辨率高,抖动图样可以自定义,抖动生成即时设置即时生效,没有延时。

37.步骤s1还包括以下步骤:

38.使用256m时钟产生一个抖动的2.048m时钟;

39.步骤s3中,根据数据来翻转抖动的2.048m时钟。

40.以256m时钟周期为步长,创建了一个计数器,每当计数值同读到的整形数据相等时,就把2mhz/2mbit/s信号的电平翻转一次。

41.步骤s1还包括以下步骤:

42.提供控制信号,控制信号包括初始的复位信号、向随机存取存储器写数据使能信号。

43.控制信号还包括表示一组按正弦变化数据中的数据总个数的信号、以及表示隔特定数量的2.048m时钟周期加抖动一次的信号,特定数量可以按需求设置。

44.通常,抖动生成模块用256m时钟产生一个抖动的2.048m时钟,由于256mhz/2.048mhz=125,1/125=0.008,所以使用256m时钟产生的带抖动2.048m时钟,分辨率能达到0.008ui。

45.抖动生成模块以256m时钟周期为步长,创建了一个计数器,每当计数值同读到的整形数据相等时,就把2mhz/2mbit/s信号的电平翻转一次。

46.优选地,将zynq系列的fpga内嵌arm硬核作为cpu控制逻辑器件工作。

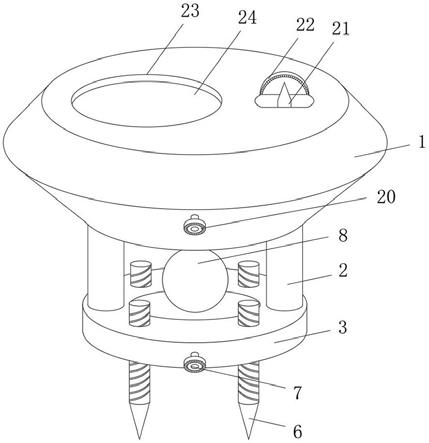

47.结合图2所示,本发明还提供一种2mhz/2mbit/s信号的抖动生成系统,包括:

48.抖动生成模块,用于生成2mhz/2mbit/s抖动时钟;

49.随机存取存储器,用于接收抖动整形数据,优选地,随机存取存储器为fpga内嵌的ram;

50.控制器,循环从随机存取存储器读取整形数据,根据数据来翻转抖动时钟,优选地,控制器为fpga内嵌arm。

51.抖动生成模块使用256m时钟产生一个抖动的2.048m时钟,控制器根据数据来翻转抖动的2.048m时钟。

52.抖动生成模块以256m时钟周期为步长,创建了一个计数器,每当计数值同读到的整形数据相等时,就把2mhz/2mbit/s信号的电平翻转一次。

53.控制器提供控制信号,控制信号包括初始的复位信号、向随机存取存储器写数据使能信号、表示一组按正弦变化数据中的数据总个数的信号、表示隔特定数量的2.048m时钟周期加抖动一次的信号。

54.参考以下示例说明,我们要加一个频率为ω,峰峰值为a个ui的正弦波到2mhz/2mbit/s时钟上。那么这个正弦波函数可以表示成f(x)=0.5*a*sinωx。这一个正弦波周期中包含了2048000/ω个2mhz/2mbit/s时钟周期。如果在每个2mhz/2mbit/s时钟周期均匀的加入上面的正弦波信号,则步长δx=2*π/ω/(2048000/ω)=2*π*0.00000048828125,

55.每次调整的ui值0.5*a*sin(ω*δx) 1,除以分辨率0.008,得到fpga的一个以256m时钟计数的计数值。对应正弦波上某一个点n(n=1,2

…

2048000/ω),可得到对应的计数值

56.c(n)=(0.5*a*sin(ω*δx*n) 1)/0.008

57.这些计数值就作为整形数据依次写入ram,抖动生成模块读出整形数据,再按照其计数值控制2mhz/2mbit/s时钟的高低电平翻转,就得到了配置输入参数为ω、a的带抖动的2mhz/2mbit/s时钟。

58.本方案优点:

59.抖动生成电路、信号处理完全数字化;

60.抖动生成分辨率高达0.008ui;

61.抖动图样受软件控制,完全可自定义;

62.抖动生成电路不需要使用锁相环,即时设置即时生效,没有延时;

63.可以理解地,上述各技术特征可以任意组合使用而不受限制。

64.以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发

明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。