1.本公开主张2020年4月14日申请的美国正式申请案第16/848,359号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

2.本公开涉及一种垂直存储器结构以及其制备方法。特别涉及一种具有气隙以降低电容耦合的垂直存储器结构及其制备方法。

背景技术:

3.半导体晶粒广泛地使用在电子产业。半导体晶粒可具有相对小的尺寸、多功能特性及/或相对低的制造成本。半导体晶粒可归类为以下其中之一:存储逻辑数据的半导体存储器晶粒、处理逻辑数据的半导体逻辑晶粒,以及同时具有半导体存储晶粒的功能与半导体逻辑晶粒的功能的混合半导体晶粒。

4.相对高速与相对低电压的半导体晶粒可满足电子晶粒的所欲的特性(例如高速及/或低功耗),而电子晶粒包括半导体晶粒。半导体晶粒可相对地高度整合。半导体晶粒的可靠度可通过半导体晶粒的相对高度整合密度而降低。

5.上文的“现有技术”说明仅提供背景技术,并未承认上文的“现有技术”说明公开本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

技术实现要素:

6.本公开的一实施例提供一种垂直存储器结构,包括一半导体堆叠,具有一下半导体图案结构,充填在一基底上的一凹陷,并从该基底的一上表面在一第一方向突伸,该第一方向大致垂直该基底的该上表面;多个栅极电极,围绕该半导体堆叠的一侧壁设置,该多个栅极电极分别位在不同位面,以便在该第一方向相互分开设置;以及多个气隙结构,分别设置在该多个栅极电极的外侧处。

7.在本公开的一些实施例中,该多个气隙结构包括一衬垫层,该衬垫层包围一气隙设置。

8.在本公开的一些实施例中,该垂直存储器结构还包括一导电线,且该多个气隙结构将该导电线与该多个栅极电极分隔开。

9.在本公开的一些实施例中,该下半导体图案结构包括依序在该第一方向堆叠的一第一未掺杂半导体图案、一掺杂半导体图案以及一第二未掺杂半导体图案。

10.在本公开的一些实施例中,该垂直存储器结构还包括一上半导体图案,在该下半导体图案结构上并在该第一方向延伸,其中该掺杂半导体图案的一下表面低于该基底的该上表面。

11.在本公开的一些实施例中,该下半导体图案结构的该掺杂半导体图案的一上表面,高于最下面的该栅极电极的一下表面,并低于最下面的该栅极电极的一上表面。

12.在本公开的一些实施例中,该垂直存储器结构还包括一第一扩散防止图案以及一

第二扩散防止图案,该第一扩散防止图案位在该第一未掺杂半导体图案与该掺杂半导体图案之间,该第二扩散防止图案位在该掺杂半导体图案与该第二未掺杂半导体图案之间。

13.在本公开的一些实施例中,该第一扩散防止图案与该第二扩散防止图案中的每一个,为掺杂有碳的一半导体图案。

14.在本公开的一些实施例中,该第二扩散防止图案为掺杂有碳与硼的一半导体图案。

15.在本公开的一些实施例中,该垂直存储器结构还包括一杂质层,位在该基底的一上部处。

16.在本公开的一些实施例中,该掺杂半导体图案接触该杂质层。

17.在本公开的一些实施例中,该掺杂半导体图案的一下表面高于该杂质层的一下表面。

18.在本公开的一些实施例中,该掺杂半导体图案的一下表面低于该杂质层的一下表面。

19.在本公开的一些实施例中,该杂质层包含p型杂质。

20.本公开的另一实施例提供一种垂直存储器结构的制备方法,包括:形成一半导体堆叠,该半导体堆叠具有一下半导体图案结构,充填在一基底上的一凹陷,并从该基底的一上表面在一第一方向突伸,该第一方向大致垂直该基底的该上表面;形成多个栅极电极以围绕该半导体堆叠的一侧壁,该多个栅极电极分别位在不同位面,以便在该第一方向相互分开设置;以及形成多个气隙结构分别在该多个栅极电极的外侧处。

21.在本公开的一些实施例中,形成该多个气隙结构包括:形成多个能量可移除区块分别在该多个栅极电极的外侧处;密封该多个能量可移除区块;以及执行一热处理工艺以从该多个能量可移除区块形成多个气隙结构。

22.在本公开的一些实施例中,形成该多个能量可移除区块包括:形成一能量可移除层以覆盖该多个栅极电极的外侧;以及执行一非等向性蚀刻工艺以移除该能量可移除层的一部分,同时余留邻近该多个栅极电极处的该多个能量可移除区块。

23.在本公开的一些实施例中,该能量可移除层具有一基础材料以及一可分解成孔剂材料,而该可分解成孔剂材料包括一多孔有机化合物。

24.在本公开的一些实施例中,该热处理工艺转变该多个能量可移除区块成为多个气隙结构,而该多个气隙结构具有一衬垫层,该衬垫层包围一气隙设置。

25.在本公开的一些实施例中,该垂直存储器结构的制备方法还包括:形成一导电线,并以该多个气隙结构分隔开该导电线与该多个栅极电极。

26.该垂直存储器结构具有设置在该基底上的多个导电特征(例如栅极电极以及导电线),且这些导电特征通过该等气隙结构而相互电性分隔。因此,可降低在该等导电特征之间的寄生电容,并可改善整体元件的效能(例如降低的功耗以及电阻

‑

电容延迟(rc delay)),且可提升半导体元件的良率。

27.上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术

人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的精神和范围。

附图说明

28.参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

29.图1为依据本公开一些实施例中一种具有气隙以降低在多个导电特征之间的电容耦合的垂直存储器结构的制备方法的流程示意图。

30.图2为依据本公开一些实施例中形成一堆叠结构在该垂直存储器结构的一基底上的一中间阶段的剖视示意图。

31.图3为依据本公开一些实施例中形成一通道孔以穿经该堆叠结构并进入该基底的一中间阶段的剖视示意图。

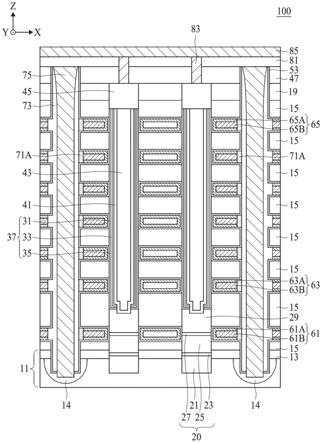

32.图4到图8为依据本公开一些实施例中形成一下通道结构在该通道孔的一下部的一中间阶段的剖视示意图。

33.图9为依据本公开一些实施例中形成一电荷存储结构(charge storage structure)以及一上通道结构在该通道孔中并在该下通道结构上的一中间阶段的剖视示意图。

34.图10为依据本公开一些实施例中形成一开口(opening)以穿经该堆叠结构并进入该基底的一中间阶段的剖视示意图。

35.图11到图14为依据本公开一些实施例中移除多个牺牲图案(牺牲层)并经由该开口形成多个栅极电极的一中间阶段的剖视示意图。

36.图15到图18为依据本公开一些实施例中形成一能量可移除区块以邻近该等栅极电极处,并以一源极线及一介电材料充填该开口的一中间阶段的剖视示意图。

37.图19为依据本公开一些实施例中执行一热处理以转变该能量可移除区块成为一气隙结构,且该气隙结构具有被一衬垫层所围绕的一气隙的一中间阶段的剖视示意图。

38.附图标记说明:

39.100:垂直存储器结构

40.10:方法

41.11:基底

42.11a:凹陷

43.12:堆叠结构

44.12a:通道孔

45.13:第一杂质区

46.14:第二杂质区

47.140:第二隔离夹层

48.15:隔离层

49.15a:隔离图案

50.17:牺牲层

51.17a:牺牲图案

52.19:硬遮罩

53.19a:开口

54.20:下通道结构

55.21:第一未掺杂半导体图案

56.23:第一扩散防止图案

57.25:掺杂半导体图案

58.27:第二扩散防止图案

59.29:第二未掺杂半导体图案

60.31:第一阻挡图案

61.33:电荷存储图案

62.35:通道隔离图案

63.37:电荷存储结构

64.41:上通道结构

65.43:填充图案

66.45:罩盖图案

67.47:第三隔离夹层

68.49:开口

69.51:间隙

70.53:第二阻挡层

71.55:栅极阻障层

72.57:栅极导电层

73.61:第一栅极电极

74.61a:第一栅极阻障图案

75.61b:第一栅极导电图案

76.63:第二栅极电极

77.63a:第二栅极阻障图案

78.63b:第二栅极导电图案

79.65:第三栅极电极

80.65a:第三栅极阻障图案

81.65b:第三栅极导电图案

82.67:硬遮罩

83.67a:开口

84.69:覆盖层

85.71:能量可移除层

86.71a:能量可移除区块

87.72:气隙结构

88.72a:气隙

89.72b:衬垫层

90.73:第二间隙子

91.75:共源极/漏极线

92.81:第四隔离夹层

93.83:导电栓塞

94.85:位元线

95.s11:步骤

96.s13:步骤

97.s15:步骤

98.s17:步骤

99.s19:步骤

100.s21:步骤

101.s23:步骤

102.s25:步骤

103.x:方向

104.y:方向

105.z:方向

具体实施方式

106.以下描述了组件和配置的具体范例,以简化本公开的实施例。当然,这些实施例仅用以例示,并非意图限制本公开的范围。举例而言,在叙述中第一部件形成于第二部件之上,可能包含形成第一和第二部件直接接触的实施例,也可能包含额外的部件形成于第一和第二部件之间,使得第一和第二部件不会直接接触的实施例。另外,本公开的实施例可能在许多范例中重复参照标号及/或字母。这些重复的目的是为了简化和清楚,除非内文中特别说明,其本身并非代表各种实施例及/或所讨论的配置之间有特定的关系。

107.此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下面(below)”、“下部的(lower)”、“上方(above)”、“上部的(upper)”等空间相对关系用语来阐述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对关系用语旨在除图中所示出的取向外亦囊括元件在使用或操作中的不同取向。所述装置可具有其他取向(旋转90度或处于其他取向)且本文中所用的空间相对关系描述语可同样相应地进行解释。

108.应当理解,当形成一个部件在另一个部件之上(on)、与另一个部件相连(connected to)、及/或与另一个部件耦合(coupled to),其可能包含形成这些部件直接接触的实施例,并且也可能包含形成额外的部件介于这些部件之间,使得这些部件不会直接接触的实施例。

109.应当理解,尽管这里可以使用术语第一,第二,第三等来描述各种元件、部件、区域、层或区段(sections),但是这些元件、部件、区域、层或区段不受这些术语的限制。相反,这些术语仅用于将一个元件、组件、区域、层或区段与另一个区域、层或区段所区分开。因此,在不脱离本发明进步性构思的教导的情况下,下列所讨论的第一元件、组件、区域、层或区段可以被称为第二元件、组件、区域、层或区段。

110.除非内容中另有所指,否则当代表定向(orientation)、布局(layout)、位置(location)、形状(shapes)、尺寸(sizes)、数量(amounts),或其他测量(measures)时,则如在本文中所使用的例如“同样的(same)”、“相等的(equal)”、“平坦的(planar)”,或是“共面

的(coplanar)”等术语(terms)并非必要意指一精确地完全相同的定向、布局、位置、形状、尺寸、数量,或其他测量,但其意指在可接受的差异内,是包含差不多完全相同的定向、布局、位置、形状、尺寸、数量,或其他测量,而举例来说,所述可接受的差异可因为制造流程(manufacturing processes)而发生。术语“大致地(substantially)”可被使用在本文中,以表现出此意思。举例来说,如大致地相同的(substantially the same)、大致地相等的(substantially equal),或是大致地平坦的(substantially planar),为精确地相同的、相等的,或是平坦的,或者是其可为在可接受的差异内的相同的、相等的,或是平坦的,而举例来说,所述可接受的差异可因为制造流程而发生。

111.在本公开中,一半导体存储器晶粒通常意指可通过利用半导体特性(semiconductor characteristics)运行的一元件,而一光电元件(electro

‑

optic device)、一发光显示元件(light

‑

emitting display device)、一半导体线路(semiconductor circuit)以及一电子元件(electronic device),均包括在半导体晶粒的范畴中。

112.应当理解,在本公开的描述中,上方(above)(或之上(up))是对应z方向箭头的该方向,而下方(below)(或之下(down))是对应z方向箭头的相对方向。

113.图1为依据本公开一些实施例中一种具有气隙以降低在多个导电特征之间的电容耦合的垂直存储器结构的制备方法10的流程示意图。方法10可作为多个步骤执行。应当理解,方法10可以任何顺序执行,并可具有相同、更多或较少的步骤。应当理解,方法10可通过一或多个半导体制造设备或制造工具所执行。

114.在一些实施例中,方法10包括步骤s11、s13、s15、s17、s19、s21、s23以及s25。图1的步骤s11到s25是结合下列附图进行详细说明。

115.图2为依据本公开一些实施例中形成垂直存储器结构100的一中间阶段的剖视示意图。在一些实施例中,方法10开始于步骤s11,其是形成一堆叠结构12,包括多个隔离层15与多个牺牲层17交错并重复堆叠在一基底11上。在一些实施例中,多个杂质(impurities)可植入在基底11的一上部中,以形成第一杂质区13,且该等隔离层15与该等牺牲层17可交错并重复形成在基底11上,且基底11具有第一杂质区13。因此,多个隔离层15与多个牺牲层17可在一第一方向(z方向)相互交错堆叠在基底11上。

116.在一些实施例中,基底11可为一半导体晶圆,例如硅晶圆。另外或此外,半导体基底11可包括元素半导体材料、化合物半导体材料及/或合金半导体材料。元素半导体材料的例子可包括结晶硅(crystal silicon)、多晶硅(polycrystalline silicon)、非晶硅(amorphous silicon)、锗(germanium)及/或钻石(diamond),但并不以此为限。化合物半导体材料的例子可包括碳化硅(silicon carbide)、砷化镓(gallium arsenic)、磷化镓(gallium phosphide)、磷化铟(indium phosphide)、砷化铟(indium arsenide)、及/或锑化铟(indium antimonide),但并不以此为限。合金半导体材料的例子可包括硅锗(sige)、砷磷化镓(gaasp)、铟砷化铝(alinas)、镓砷化铝(algaas)、铟砷化镓(gainas)、铟磷化镓(gainp)、及/或磷砷化镓铟(gainasp),但并不以此为限。

117.在一些实施例中,半导体基底11具有一外延层(epitaxial layer)。举例来说,半导体基底11具有一外延层,是覆盖一块状半导体(bulk semiconductor)。在一些实施例中,半导体基底11为一绝缘体上覆半导体(semiconductor

‑

on

‑

insulator)基底,其可包括一基

底、在该基底上的一埋入氧化物层以及在该埋入氧化物层上的一半导体层,例如一绝缘体上覆硅(silicon

‑

on

‑

insulator,soi)基底、一绝缘体上覆硅锗(silicon germanium

‑

on

‑

insulator,sgoi)基底,或一绝缘体上覆锗(germanium

‑

on

‑

insulator,goi)基底。该等绝缘体上覆半导体基底可使用氧离子注入隔离(separation by implantation of oxygen,simox)工艺、一晶圆接合(wafer bonding)工艺、其他可应用的方法来制造。

118.在一些实施例中,半导体基底11可为多种材料,包括蓝宝石(sapphire)、硅、氮化锗(gallium nitride,gan)、锗或碳化硅,但并不以此为限。半导体基底11可为绝缘体上覆硅(soi)。在本公开的一些实施例中,半导体基底11为硅。一大致单晶体半导体(monocrystalline semiconductor)基底的晶体方向(crystallographic orientation),可为在米勒指数(miller indices)上的(100)、(111)或(110)中任一个。亦可能为其他晶体方向。半导体基底11的晶体方向可为偏切(offcut)。在本公开的一些实施例中,半导体基底11为具有结晶基底表面区的(100)硅,而该结晶机底表面区具有立方结晶度(cubic crystallinity)。在其他的实施例中,对于一(100)硅半导体基底11而言,半导体表面可斜切(miscut)或偏切(offcut),举例来说,朝向(110)的2

‑

10度角。在其他实施例中,半导体基底11为具有结晶基底表面区的(111)硅,而该结晶基底表面区具有六角结晶度(hexagonal crystallinity)。

119.在一些实施例中,第一杂质区13可通过一离子植入工艺所形成。在举例的实施例中,离子植入工艺可使用p型杂质所执行,例如硼、铝等等,也因此第一杂质区13可包含p型杂质。

120.在一些实施例中,该等隔离层15与该等牺牲层17可通过下列工艺所形成:化学气相沉积(cvd)工艺、等离子体加强化学气相沉积(pe

‑

cvd)工艺、原子层沉积(ald)工艺等等。举例来说,最下面的隔离层15可通过基底11的一上表面的热氧化(thermal oxidation)工艺所形成。

121.在一些实施例中,隔离层15可由一硅氧化物材料所制,例如等离子体加强正硅酸四乙酯(plasma

‑

enhanced tetraethylorthosilicate,pe

‑

teos)、高密度等离子体(hdp)氧化物、等离子体加强氧化物(peox)等等。该等牺牲层17可由一材料所制,该材料具有相对于该等隔离层5的一蚀刻选择性,该材料是例如氮化硅。

122.请参考图3,在如图2所示的方法10中的步骤s13,执行多个制造程序以形成一通道孔(channel hole),以穿经该堆叠结构并进入该基底。在一些实施例中,一硬遮罩19具有多个开口(openings)19a,硬遮罩19可形成在楼梯结构(staircase structure)的一上表面上以及在第一隔离夹层图案(first insulating interlayer pattern)的一上表面上。硬遮罩19可由一氧化物所制,例如氧化硅,也因此可与第一隔离夹层图案及/或最上面的隔离层15合并。该等隔离层15与该等牺牲层17可使用硬遮罩19当作一蚀刻遮罩进行蚀刻,以形成将其穿经的一通道孔12a,以暴露基底11的一上表面。

123.在举例的实施例中,可形成多个通道孔12a,例如在第二方向(x方向)以及第三方向(y方向)相互分开设置,以形成一通道孔阵列(channel hole array)。在举例的实施例中,通道孔阵列可具有一第一通道孔列(column)以及一第二通道孔列,第一通道孔列具有多个第一通道孔,而多个第一通道孔配置在第二方向,第二通道孔列与第一通道孔列在第三方向相互间隔设置,且第二通道孔列具有多个第二通道孔,而多个第二通道孔配置在第

二方向。第一通道孔列及第二通道孔列可交错并重复形成在第三方向,以形成一通道孔区块(block)。

124.在举例的实施例中,当形成通道孔12a时,可移除基底11的一上表面的一部分,以形成一凹陷11a在基底11中。通道孔12a可包括位在基底11中的凹陷11a,例如凹陷可界定出通道孔12a的底部。凹陷11a可具有一深度,大于第一杂质区13的一下表面,例如凹陷11a可延伸经过第一杂质区13,以具有一底部,是低于相对于基底11的底部的第一杂质区13的下表面。

125.请参考图4,如图2所示的方法10中的步骤s15,一下通道结构形成在该通道孔的一下部处。在一些实施例中,可形成一第一未掺杂半导体图案21,以充填通道孔12a的一下部。举例来说,可执行一第一选择外延生长(seg),是使用基底11通过凹陷11a当成一种层(seed)所暴露的一部分所执行,以形成第一未掺杂半导体图案21,进而部分充填通道孔12a。因此,第一未掺杂半导体图案21可具有单晶硅(single crystalline silicon)、单晶锗(single crystalline germanium)等等,其取决于基底11的材料。

126.在举例的实施例中,可执行第一seg工艺,使用一半导体源(semiconductor source)气体、一蚀刻气体以及一载子气体。在一举例的实施例中,半导体源气体可包括一硅源(silicon source)气体,例如二氯硅烷(dichlorosilane,sih2cl2);蚀刻气体可包括例如氯化氢(hydrogen chloride,hcl)气体;且载子气体可包括例如氢(hydrogen,h2)气体。因此,第一未掺杂半导体图案21可包括未掺杂杂质的单晶硅。

127.在其他例子中,第一未掺杂半导体图案21可通过下列方法所形成:形成一非结晶(amorphous)半导体层以充填通道孔12a,并执行一激光外延生长(leg)工艺或一固相外延(spe)工艺。

128.在举例的实例中,第一未掺杂半导体图案21的一上表面可低于基底11的一上表面,而基底11并未形成凹陷,例如第一未掺杂半导体图案21的上表面可低于在图4中的第一杂质区13的下表面。在一举例的实施例中,第一未掺杂半导体图案21的上表面可高于第一杂质区13的下表面,例如相对于基底11的底部。然而,该等实施例并未以此为限。

129.请参考图5,一第一气相沉积(gpd)工艺可执行在第一未掺杂半导体图案21上,以形成一第一扩散防止图案(first diffusion prevention pattern)23在第一未掺杂半导体图案21上。在举例的实施例中,第一gpd工艺可使用一碳源(carbon source)气体所执行,也因此可形成掺杂有碳的一半导体图案作为第一扩散防止图案23。当第一未掺杂半导体图案21包含单晶硅时,第一扩散防止图案23可包含掺杂有碳的单晶硅。

130.图5是显示第一扩散防止图案23的一下表面高于第一杂质区13的下表面。然而,该等实施例并未以此为限,例如第一扩散防止图案23的下表面可低于或大致共面于第一杂质区13的下表面。

131.请参考图6,一掺杂半导体图案25可形成在第一扩散防止图案23上,以部分充填通道孔12a。在一些实施例中,可执行一第二seg工艺,是使用第一未掺杂半导体图案21当作一种层(seed),而此时的第一未掺杂半导体图案21上具有第一扩散防止图案23,以形成掺杂半导体图案25,进而部分充填通道孔12a。因此,掺杂半导体图案25可包含单晶硅、单晶锗等等,其是取决于第一未掺杂半导体图案21的材料。

132.在举例的实施例中,执行第二seg工艺可使用一半导体源气体、一杂质源

(impurity source)气体、一蚀刻气体以及一载子气体。在一举例的实施例中,半导体源气体可包括一硅源气体,例如二氯硅烷(sih2cl2);杂质源气体可包括一p型杂质源气体,例如二硼烷(diborane,b2h6);蚀刻气体可包括例如氯化氢(hcl)气体;且载子气体可包括例如氢(h2)气体。因此,掺杂半导体图案25可包括掺杂p型杂质的单晶硅,p型杂质是例如硼。

133.例如,当执行形成掺杂半导体图案25的第二seg工艺时,使用p型杂质源气体,以提供多个杂质在生长的掺杂半导体图案25内。因此,掺杂半导体图案25在第一方向可具有一相对均匀的掺杂浓度,或是可具有一所欲的掺杂轮廓(profile)。意即,当相较于执行一离子植入工艺以植入多个杂质进入一已经形成的未掺杂半导体图案时,在举例的实施例中的杂质源气体在seg工艺期间使用,而seg工艺是形成掺杂半导体图案25,所以掺杂半导体图案25伴随该等杂质生长,而不是具有植入在其中的该等杂质,以具有一均匀掺杂轮廓或一所欲掺杂轮廓。

134.意即,当在第二方向和第三方向上形成多个通道孔12a时,多个未掺杂的半导体图案的厚度或高度沿第一方向可以具有分布,而第一方向意即相对于基板的上表面的垂直方向。因此,若是该等完全掺杂半导体图案形成在该等通道孔12a的底部中的话,且若是该等杂质通过离子植入工艺而植入在该等未掺杂半导体图案中的话,则合成的该等掺杂半导体图案是依据该等未掺杂半导体图案的厚度分布,在第一方向具有一掺杂浓度分布。换言之,由于离子植入工艺是将离子沿垂直方向植入到位在该等未掺杂半导体图案内的一预定深度,所以合成的该等半导体图案在第一方向可具有一变化的掺杂浓度。

135.然而,依据举例的实施例,当该等掺杂半导体图案25通过第二seg工艺并使用杂质源气体所形成时,该等掺杂半导体图案25可伴随着该等杂质而外延地生长。因此,例如相较于从已经形成的未掺杂半导体图案的一上部植入该等杂质,该等掺杂半导体图案25的掺杂浓度可不被该等掺杂半导体图案25的厚度分布所影响,并可相对均匀。

136.当掺杂半导体图案25通过第二seg工艺所形成时,第一扩散防止图案23可形成在掺杂半导体图案25下方,例如第一扩散防止图案23余留在第一未掺杂半导体图案21与掺杂半导体图案25之间。因此,掺杂进入掺杂半导体图案25的该等杂质并未扩散进入位在下面的第一未掺杂半导体图案21。据此,掺杂半导体图案25可具有一所欲掺杂轮廓,且可不增加掺杂半导体图案25的掺杂浓度分布。

137.在举例的实施例中,掺杂半导体图案25的一下表面可低于基底11的上表面,且掺杂半导体图案25的一上表面可高于最下面的牺牲层17的一下表面。因此,掺杂半导体图案25可以在与基底11的上表面大致平行的一水平方向上,在基底11的上部以及最下面的牺牲层17重叠第一杂质区域13。

138.在举例的实施例中,掺杂半导体图案25的上表面可低于最下面的牺牲层17的一上表面。然而,该等实施例并未以此为限。

139.请参考图7,一第二gpd工艺可执行在掺杂半导体图案25上,以形成第二扩散防止图案27在掺杂半导体图案25上。在举例的实施例中,执行第二gpd工艺可使用一碳源气体,也因此可形成掺杂碳及硼的一半导体图案当作第二扩散防止图案27。当掺杂半导体图案25包含单晶硅时,第二扩散防止图案27可包含掺杂碳及硼的单晶硅。

140.请参考图8,一第二未掺杂半导体图案29可形成在第二扩散防止图案27上,以部分充填通道孔12a。在一些实施例中,可执行一第三seg工艺,并使用掺杂半导体图案25当作一

种层(seed),此时掺杂半导体图案25上具有第二扩散防止图案27,以形成第二未掺杂半导体图案29,进而部分充填通导孔12a。因此,第二未掺杂半导体图案29可包含单晶硅、单晶锗,其取决于掺杂半导体图案25的材料。

141.在举例的实施例中,执行第三seg工艺可使用类似于第一seg工艺的一半导体源气体、一蚀刻气体以及一载子气体。因此,第二未掺杂半导体图案29可包含未掺杂该等杂质的单晶硅。

142.在举例的实施例中,第二未掺杂半导体图案29的一下表面可低于最下面的牺牲层17的上表面。然而,该等实施例并未以此为限。第二未掺杂半导体图案29的一上表面可位在一第二位面(second level)处的其中一隔离层15的下表面与上表面之间,而第二位面是在第一方向从基底11的上表面起算。

143.当执行第三seg工艺时,第一扩散防止图案23与第二扩散防止图案27分别形成在掺杂半导体图案25的下表面与上表面,也因此掺杂进入掺杂半导体图案25的该等杂质不能扩散进入第一未掺杂半导体图案21与第二未掺杂半导体图案29中。据此,掺杂半导体图案25可维持所欲的掺杂轮廓。

144.依序堆叠在基底11上的第一未掺杂半导体图案21、第一扩散防止图案23、掺杂半导体图案25、第二扩散防止图案27以及第二未掺杂半导体图案29,可形成下半导体图案结构。位在下半导体图案结构的下部与上部的第一未掺杂半导体图案21与第二未掺杂半导体图案29,并未掺杂该等杂质。

145.因此,当相较于通过伴随该等杂质的一单一seg工艺所形成的一半导体图案,而该等杂质是通过从半导体图案的一上部的离子植入所植入,则仅在举例的实施例中的下半导体图案结构的一小部分在第一方向掺杂该等杂质。据此,可减少在相对应通道孔12a中的该等下半导体图案结构之间的掺杂轮廓分布。掺杂半导体图案25可不通过独立的离子植入工艺进行掺杂,但可在第二seg工艺期间进行掺杂,也因此在多个掺杂半导体图案25中的掺杂轮廓可不被该等掺杂半导体图案25的厚度分部而影响而变得相对均匀。

146.下半导体图案结构可当作一通道,例如类似于依序形成的一上通道结构41。因此,下半导体图案结构与上通道结构41可分别当作是下通道结构以及上通道结构。

147.请参考图9,如图2所示的方法10中的步骤s17,一电荷存储结构以及一上通道结构形成在通道孔中并位在下通道结构上。在一些实施例中,一第一阻挡层(first blocking layer)、一电荷存储层(charge storage layer)、一通道隔离层以及一第一间隙子层,可依序形成在该等通道孔12a的侧壁上、在该等下半导体图案结构的上表面上以及在硬遮罩19的一上表面上。可非等向地蚀刻第一间隙子层,以形成一第一间隙子在该等通道孔12a的侧壁上,并可使用第一间隙子当作一蚀刻遮罩对第一阻挡层进行蚀刻,以分别形成通道隔离图案35、电荷存储图案33以及第一阻挡图案31在下半导体图案结构的上表面上以及在通道孔12a的侧壁上,其是具有底部呈开放状的一似杯型(cup

‑

like)形状。在蚀刻工艺期间,亦可部分移除下半导体图案结构的一上部,例如第二未掺杂半导体图案29。通道隔离图案35、电荷存储图案33以及第一阻挡图案31可形成一电荷存储结构37。第一阻挡层可由一氧化物所制,例如氧化硅;电荷存储层可由一氮化物所制,例如氮化硅;通道隔离层可由一氧化物所制,例如氧化硅;且第一间隙子层可由一氮化物所制,例如氮化硅。

148.在移除第一间隙子之后,一上半导体层可形成在暴露的第二未掺杂半导体图案29

上、在通道隔离图案35上以及在硬遮罩19上。一填充层可形成在上半导体层上,以充分地充填通道孔12a所余留的部分。上半导体层可由掺杂或未掺杂多晶硅或非晶硅所制。填充层可由一氧化物所制,例如氧化硅。

149.可平坦化填充层与上半导体层,直到硬遮罩19的一上表面可被暴露为止,以形成一填充图案43,而填充图案43是充填每一通道孔12a所余留的部分,且上半导体层可转变成一上通道结构41。因此,电荷存储结构37、上通道结构41以一填充图案43可依序堆叠在每一通道孔12a中的下半导体图案结构上。电荷存储结构37可具有底部呈开放状的一似杯型形状,上通道结构41可具有一似杯型形状,且填充图案43可具有一柱型形状。

150.如上所述,每一下半导体图案结构与上通道结构41可当作是一通道,且下半导体图案结构与上通道结构41可形成一通道结构。当该等通道孔12a可形成通道孔列、通道孔区块以及通道孔阵列时,通道结构亦可形成一通道结构列、一通道结构区块以及一通道结构阵列。

151.请参考图10,如图2所示的方法10中的步骤s19,执行制造程序以形成一开孔,进而穿过堆叠结构12。在一些实施例中,可移除第一结构的一上部以形成一沟槽,而第一结构具有填充图案43、通道结构以及电荷存储结构37。可形成罩盖图案(capping pattern)45,以充填该沟槽。在一些实施例中,在通过一回蚀工艺而移除第一结构的上部以形成该沟槽之后,充填该沟槽的一罩盖层(capping layer)可形成在第一结构与硬遮罩19上,且可平坦化罩盖层的一上部,直到硬遮罩19的上表面暴露为止,以形成罩盖图案45。在举例的实施例中,罩盖层可由掺杂或未掺杂多晶硅或非晶硅所制。当罩盖层形成并包含非晶硅时,可进一步在其上执行一结晶化(crystallization)工艺。

152.第三隔离夹层47可形成在硬遮罩19与罩盖图案45上,一第二遮罩可形成在第三隔离夹层47上,且一开口49可形成穿经第二与第三隔离夹层140与47、该等隔离层15以及该等牺牲层17,以暴露基底11的一上表面。据此,当开口49在第二方向延伸时,每一隔离层15可转换成多个隔离图案15a,而该等隔离图案15a在第三方向相互分开设置,且每一隔离图案15a可在第二方向延伸。此外,每一牺牲层17可转变成多个牺牲图案17a,该等牺牲图案17a在第三方向相互分开设置,且每一牺牲图案17a可在第二方向延伸。第三隔离夹层47可由一氧化物所制,例如氧化硅。在举例的实施例中,开口49可在第二方向延伸,并位在该等通道结构区块之间,且多个开口49可形成在第三方向。

153.请参考图11,如图2所示的方法10中的步骤s21,移除该等牺牲图案(层)17a,且多个栅极电极形成以穿过该开口。在一些实施例中,在移除第二遮罩之后,可移除经由开口49而暴露的该等牺牲图案17a,以形成一间隙51位在各自位面的该等隔离图案15a之间,且第一阻挡图案31的一外侧壁的一部分以及下半导体图案结构的一侧壁的一部分,经由间隙51而暴露。下半导体图案结构的掺杂半导体图案25的一侧壁的至少一部分,经由间隙51而暴露。在举例的实施例中,可通过使用一蚀刻剂的一湿蚀刻工艺,移除通过间隙51而暴露的该等牺牲图案17a,而蚀刻剂是例如磷酸(phosphoric acid)或硫酸(sulfuric acid)。

154.请参考图12,一第二阻挡层53形成在第一阻挡图案31的外侧壁的暴露部分上、在下半导体图案结构的侧壁的暴露部分上、在间隙51的一内壁上、在该等隔离图案15a的表面上、在基底11的暴露上表面上以及在第三隔离夹层47的一上表面上;接着,一栅极阻障层55形成在第二阻挡层53上。然后,一栅极导电层57可形成在栅极阻障层55上,一充分地充填间

隙51的一余留部分。

155.第二阻挡层53可由一金属氧化物所制,例如氧化铝、氧化铪(hafnium oxide)、氧化镧(lanthanum oxide)、氧化铝镧(lanthanum aluminum oxide)、氧化铪镧(lanthanum hafnium oxide)、氧化铝铪(hafnium aluminum oxide)、氧化钛、氧化钽及/或氧化锆(zirconium oxide)。栅极导电层57可由一金属所制,该金属具有一低电阻,例如钨、钛、钽、铂等等,且栅极阻障层55可由一金属氮化物所制,例如氮化钛、氮化钽等等。或者是,可形成栅极阻障层55以具有依序堆叠的一第一层与一第二层,而第一层包括一金属,第二层包括一金属氮化物层。

156.请参考图13,可部分移除栅极导电层57与栅极阻障层55,以分别形成一栅极导电图案以及一栅极阻障图案在间隙51中,其可形成一栅极电极。在举例的实施例中,可通过一湿蚀刻工艺而部分移除栅极导电层57与栅极阻障层55。在举例的实施例中,一可形成栅极电极以在第二方向延伸,且多个栅极电极可形成在第三方向。意即,每一个在第二方向延伸的多个栅极电极,可通过开口49而在第三方向相互分开设置。

157.栅极电极可包括在第一方向依序堆叠的第一、第二以及第三栅极电极61、63、65。第一栅极电极61可当作是一接地选择线(gsl),第二栅极电极63可当作是一字元线,而第三栅极电极65可当作是一串行的选择线(ssl)。第一到第三栅极电极61、63、65的每一个可形成在一单一位面处或多个位面处。

158.在举例的实施例中,第一栅极电极61可形成在一最下面的位面处,第三栅极电极65可形成在一最上面的位面处以及在最上面的位面下方的一位面处,而第二栅极电极63可形成在第一与第三栅极电极61、65之间的偶数字面处。因此,第一栅极电极61可形成在邻近下半导体图案结构处,更尤其是邻近掺杂半导体图案25处,而第二及第三栅极电极63、65的每一个可形成在邻近上通道结构41处。

159.第一栅极电极61可包括第一栅极导电图案61b以及第一栅极阻障图案61a,而第一栅极阻障图案61a是覆盖第一栅极导电图案61b的上、下表面以及一侧壁的一部分。第二栅极电极63可包括第二栅极导电图案63b以及第二栅极阻障图案63a,而第二栅极阻障图案63a覆盖第二栅极导电图案63b的上、下表面以及一侧壁的一部分。第三栅极电极65可包括第三栅极导电图案65b以及第三栅极阻障图案65a,而第三栅极阻障图案65a覆盖第三栅极导电图案65b的上、下表面以及一侧壁的一部分。

160.请参考图13,该等杂质可植入基底11通过开口49而暴露的一上部中,以形成第二杂质区14。在举例的实施例中,该等杂质可包括n型杂质,例如磷、砷等等。

161.请参考图14,形成一覆盖层(coverage layer)69以充填开口49,且经由一硬遮罩67的一开口67a以移除覆盖层69的一部分,以使覆盖层69选择地覆盖第一、第二、第三栅极电极61、63、65的一些部分,同时第一、第二、第三栅极电极61、63、65的其他部分则通过开口49而暴露。

162.请参考图15,如图2所示的方法10中的步骤s23,执行制造程序以形成一能量可移除区块在邻近该等栅极电极处,然后以一源极线以及一介电材料充填该开口。在一些实施例中,形成一能量可移除层71以充填开口49。在一些实施例中,能量可移除层的材料包括一热可分解材料。在一些其他实施例中,能量可移除层的材料可包括一光可分解材料、一电子束可分解材料或其他可应用的能量可分解材料。尤其是,在一些实施例中,能量可移除层的

材料包括一基础材料以及一可分解成孔剂材料,而该可分解成孔剂材料是在暴露在一能量源(意即热源)时而被大致地移除。

163.在一些实施例中,基础材料包含氢倍半硅氧烷(hydrogen silsesquioxane,hsq)、甲基硅酸盐(methylsilsesquioxane,msq)、多孔聚芳醚(porous polyarylether,pae)、多孔silk(porous silk)或多孔氧化硅(porous sio2),而可分解成孔剂材料包含一成孔剂有机化合物(porogen organic compound),其是可提供孔隙率给原本被在接下来的工艺的该等能量可移除层所占用的空间。

164.请参考图16,经由硬遮罩67的开口67a而执行一非等向性蚀刻工艺,以便选择地移除能量可移除层71在开口67a左下处的一部分,同时余留邻近第一、第二、第三栅极电极61、63、65处的多个能量可移除区块。

165.请参考图17,移除硬遮罩67与覆盖层69,以重新形成开口49,且一第二间隙子可形成在开口49的暴露的上表面上、在第二杂质区14的一上表面上、开口49的一侧壁上以及第三隔离夹层47的一上表面上。接着,可非等向性地蚀刻第二间隙子层,以形成第二间隙子73在开口49的侧壁上。因此,可暴露第二杂质区14位在基底11的一上部处的一部分。第二间隙子层可由一氧化物所制,例如氧化硅。

166.接着,一共源极/漏极线(csl)75可形成在暴露的第二杂质区14上,以充填开口49的一余留部分。在举例的实施例中,一导电层可形成在第二杂质区14、第二间隙子73以及第三隔离夹层47的暴露的上表面上,以充分地充填开口49的一余留的部分,并可平坦化,直到第三隔离夹层47的一上表面暴露为止,以形成共源极/漏极线75。亦可移除位在第三隔离夹层47上的第二阻挡层53。举例来说,导电层可由一金属、一金属氮化物及/或一金属硅化物所制。

167.请参考图18,一第四隔离夹层81可形成在第三隔离夹层47上、在共源极/漏极线75上、在第二间隙子73上以及在第二阻挡层53上。接着,可形成导电栓塞83以穿经第三及第四隔离阻挡夹层47、81,进而接触罩盖图案45。

168.第四隔离夹层81可由一氧化物所制,例如氧化硅,也因此可与下层的第三隔离夹层47合并在一起。接触栓塞83可由一金属所制,例如钨、钽、钛等等,或者是由一金属氮化物所制,例如氮化钛、氮化钽、氮化钨等等。

169.一第五隔离夹层可形成在第四隔离夹层81与接触栓塞83上,并可形成一位元线85以穿经第五隔离夹层。在举例的实施例中,位元线85可通过一镶嵌(damascene)工艺所形成,并可由一金属所制,例如钨、钽、钛等等,或是由一金属氮化物所制,例如氮化钛、氮化钽、氮化钨等等。位元线85可接触到接触栓塞85的一上表面。在举例的实施例中,位元线85可在第三方向延伸,且多个位元线85可形成在第二方向上。

170.请参考图19,如图5所示的方法10中的步骤s25,依据一些实施例以执行一热处理工艺。在一些实施例中,在热处理工艺期间,能量可移除区块71a转变成一气隙结构72,而气隙结构72包括被一衬垫层72b所包围的一气隙72a。

171.在一些其他实施例中,热处理工艺可被一光处理工艺、一电子束处理工艺、其组合或其他可应用的能量处理工艺所取代。举例来说,一紫外(uv)光或激光可用来移除该等能量可移除区块17a的可分解成孔剂材料,以获得气隙结构72,而气隙结构72包括被衬垫层72b所包围的气隙72a。

172.通过上述的程序,可制造出具有气隙结构72的垂直存储器结构100。如上所述,举例的实施例的下通道结构20并未通过执行一单一seg工艺所形成,而该单一seg工艺是伴随在一离子植入工艺之后。因此,可以防止或大致上最小化由于离子植入可能在下半导体图案结构中产生的厚度分布或高度分布,例如,在不同的下半导体图案结构中造成不同的杂质掺杂轮廓。

173.依据举例的实施例,下通道结构20可通过多个seg工艺所形成,且该等杂质可仅在一些seg工艺中进行掺杂。因此,当相较于经由离子植入使该等杂质掺杂进入下通道结构20的整个部分时,由于该等杂质仅掺杂进入下通道结构20的一部分中,例如仅进入掺杂半导体图案25中,所以可减少在下通道结构20间的杂质掺杂轮廓分布。此外,该等杂质并未通过离子植入工艺而被植入到掺杂半导体图案25中,但却经由使用在seg工艺中的一杂质源气体,借此提供一所欲杂质掺杂轮廓。第一及第二扩散防止图案23、27可分别形成在掺杂半导体图案25下方及其上,也因此掺杂进入掺杂半导体图案25中的该等杂质无法通过seg工艺或一热处理工艺而扩散到第一及第二未掺杂半导体图案21、29中。据此,可维持在掺杂半导体图案25中的所欲的杂质掺杂轮廓。

174.再者,垂直存储器结构100具有设置在基底11上的多个导电特征(例如栅极电极以及共源极/漏极线),且气隙结构72与介电的第二间隙子73电性分隔该等导电特征。因此,可降低在该等导电特征之间的寄生电容。特别地是,栅极电极61、63、65通过气隙结构72而与共源极/漏极线75分开设置,而气隙结构72包括被衬垫层72b所包围的气隙72a。因此,可改善整体元件的效能(例如降低的功耗以及电阻

‑

电容延迟(rc delay)),且可提升半导体元件的良率。

175.本公开的一实施例提供一种垂直存储器结构,包括一半导体堆叠,具有一下半导体图案结构,充填在一基底上的一凹陷,并从该基底的一上表面在一第一方向突伸,该第一方向大致垂直该基底的该上表面;多个栅极电极,围绕该半导体堆叠的一侧壁设置,该多个栅极电极分别位在不同位面,以便在该第一方向相互分开设置;以及多个气隙结构,分别设置在该多个栅极电极的外侧处。

176.本公开的另一实施例提供一种垂直存储器结构的制备方法,包括:形成一半导体堆叠,该半导体堆叠具有一下半导体图案结构,充填在一基底上的一凹陷,并从该基底的一上表面在一第一方向突伸,该第一方向大致垂直该基底的该上表面;形成多个栅极电极以围绕该半导体堆叠的一侧壁,该多个栅极电极分别位在不同位面,以便在该第一方向相互分开设置;以及形成多个气隙结构分别在该多个栅极电极的外侧处。

177.虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

178.再者,本公开的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤包含于本公开的权利要求内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。