1.实施例涉及一种交织器,以及更特别地,涉及一种用于经ldpc(ldpc=低密度奇偶校验码)编码的码字的交织器。其他实施例涉及用于具有阶梯式节点分布(staircase node distribution)的ldpc码字的迭代决策指导信道估计(iterative decision directed channel estimation)的混合逐块随机交织器。

背景技术:

2.低密度奇偶校验码(ldpc,low

‑

density parity

‑

check code)由于其令人惊叹的性能以及相对较低的复杂性而被视为数字通信领域中的突破。其容量接近性能(capacity approaching performance)使得其可用于需要稳健性以及可靠性的众多应用。此外,其稀疏性质促进在坦纳(tanner)图上的置信度传播(bp)解码。

3.ldpc解码器的开始点涉及先验对数似然比(llr,apriori log likelihood ratio)的计算。出于该目的,应借助于已知前置码序列估计信道衰落系数,以及将其馈送至ldpc解码器。然而,前置码仅能够提供关于衰落信道的短期信息。这意味着,仅可以估计第一相邻系数。结果,其余符号将不具有信道状态信息(csi)。换句话讲,ldpc解码器将能够计算前几个符号的先验llr,而其余符号将被视为抹除项(erasure)。这些抹除项致使不可能触发ldpc的bp解码。

4.一方面,增大导频码元的数目将得到较长的信道估计跨度。因此,可以估计较多衰落系数,以及将其提供至ldpc解码器,这可实现较佳性能。而另一方面,这种增强的性能将由于发送较多的非数据导频码元而付出降低有效数据速率的代价。

5.ldpc码可以由其坦纳图来描述。(n,k)个ldpc码具有表示n个经编码位的n个变量节点,以及表示奇偶校验等式的n

‑

k个校验节点。系统性ldpc码会将其k个信息位映射至前k个变量节点。其余n

‑

k个变量节点类似于n

‑

k个奇偶校验位。变量节点与校验节点之间的连接根据给定ldpc码的奇偶校验矩阵来进行。

6.一类ldpc码,诸如为即将到来的ieee 802.15.4w[1]所提出的码以及dvb

‑

ngh标准中所采用的码,以阶梯式节点分布为特征。这意味着,除了表示系统性信息部分的前k个变量节点外,变量节点与校验节点的连接遵循阶梯形式。换句话讲,每一变量节点连接至两个连续的校验节点。第(k 1)个变量节点连接至第一和第二校验节点。第(k 2)个变量节点连接至第二和第三校验节点,依此类推。第n个变量节点连接至第(n

‑

k)个校验节点。

[0007]

图1示出[3]中提出的(736,184)ldpc码的坦纳图10的示例,其码率为r=1/4。其具有n=736个变量节点12,以及n

‑

k=552个校验节点14。前k个变量节点12对应于系统性信息部分。它们的节点度(node degree)达到d=10,并且它们具有与校验节点14的随机连接16。除了最后一个变量节点之外,其余551个变量节点展现至与校验节点14对应的阶梯连接,以及具有度,d=2。

[0008]

当信道估计器提供关于少数码元的csi时,具有阶梯式节点分布的ldpc码很容易遭受解码失败。这种性能劣化背后的原因来自校验节点至对应变量节点的连接模式。举例

而言,对于(736,184)码,除了第一校验节点外,每一个具有度d=4。每一校验节点从前k个变量节点随机连接至两个变量节点。其余两个边缘经由连续的变量节点连接而遵循阶梯结构。这意味着短前置码序列将仅提供关于系统性部分的前几个位的信息。这使得坦纳图的所有校验节点具有至少两个从其对应变量节点接收的已抹除llr。因此,bp解码算法将无法开始。

技术实现要素:

[0009]

因此,本发明的目的是提供以下概念:允许ldpc的置信度传播(bp,belief propagation)解码算法的可行性,即使在具有有限数目个估计衰落系数的情况下也是如此。

[0010]

此目的是通过独立权利要求来解决的。

[0011]

在附属权利要求中阐述了有利实施方式。

[0012]

实施例提供一种用于对经ldpc编码的位序列(ldpc encoded bit sequence)进行交织的交织器,其中所述交织器包括:分段级(segmentation stage),被配置为将所述经ldpc编码的位序列分段[例如,划分]为[例如,相等长度的]多个分块(chunk),所述多个分块包括第一分块以及一个或多个其他分块[例如,第二分块以及视需要第三分块];第一交织器级,被配置为对所述一个或多个其他分块或者其级联版本进行交织[例如,对所述第二分块以及视需要所述第三分块交织,或者对所述第二分块以及所述第三分块的级联版本(concatenated version)进行交织];第二交织器级,被配置为将所述多个分块中的所述第一分块与由所述第一交织器级提供的经交织的位序列逐块交织,以获得所述经ldpc编码的位序列的经交织版本,其中所述多个分块中的所述第一分块由第一类型的位组成[例如,仅包括第一类型的位],其中所述第一类型的位

[0013]

‑

是所述经ldpc编码的位序列的错误校正位,

[0014]

‑

是所述经ldpc编码的位序列的重复累积位,和/或

[0015]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以所述经ldpc编码的位序列的坦纳图表示(tanner graph representation)来表示。

[0016]

在实施例中,所述第一分块绕过(bypass)所述第一交织器级[例如,所述第一分块不由所述第一交织器级交织]。

[0017]

在实施例中,所述一个或多个其他分块中的一个分块[例如,所述第二分块]由第二类型的位组成,其中所述第二类型的位

[0018]

‑

是所述经ldpc编码的位序列的信息位[以及例如,所述经ldpc编码的位序列的其余错误校正位],和/或

[0019]

‑

通过包括与错误校正校验节点的伪随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0020]

在实施例中,所述一个或多个其他分块是两个或者更多个其他分块,其中所述两个或者更多个其他分块中的另一分块[例如,所述第三分块]由所述第一类型的位组成。

[0021]

在实施例中,所述第一交织器级是伪随机交织器。

[0022]

在实施例中,所述伪随机交织器是基于线性移位寄存器。

[0023]

在实施例中,所述伪随机交织器是逐块交织器。

[0024]

在实施例中,所述第一交织器级被配置为基于以下语法对所述一个或多个其他分块[例如,所述其他分块的级联版本]进行交织:

[0025]

for j=0:((n

chunks

‑

1)n

bits/chunk

)

‑1[0026][0027]

end

[0028]

其中j表示控制变量,其中n

chunks

表示将经ldpc编码的位序列分段而成的多个分块的数目,其中n

bits/chunk

表示每分块的位的数目,其中表示经交织的位序列[例如,一个或多个其他分块的经交织版本(级联版本)],其中表示一个或多个其他分块的级联版本,其中π表示线性反馈移位寄存器的置换(permutation)索引向量。

[0029]

在实施例中,所述第二交织器级是逐块交织器。

[0030]

在实施例中,所述第二交织器级被配置为在多个子数据分组上分布所述经ldpc编码的位序列的所述经交织版本。

[0031]

在实施例中,所述第二交织器级被配置为在至少两个轮次中在所述多个子数据分组上逐块地分布所述多个分块中的所述第一分块的位[例如,使得在第一轮次中,所述第一分块的位[例如,两个位]的连续块循环地映射至所述多个子数据分组,以及在第二轮次中,所述第一分块的位[例如,两个位]的其他连续块循环地映射至所述多个子数据分组]。

[0032]

在实施例中,所述第二交织器级被配置为在所述多个子数据分组上均匀地逐块地分布由所述第一交织器级提供的所述经交织的位序列的位[例如,所述多个子数据分组用由所述第一交织器级提供的所述经交织的位序列的位均匀地填满]。

[0033]

在实施例中,所述第二交织器级被配置为基于以下语法将所述第一分块与由所述第一交织器级提供的所述经交织的位序列交织:

[0034]

[0035]

其中i表示控制变量,其中j表示控制变量,其中k表示控制变量,其中n

chunks

表示将经ldpc编码的位序列分段而成的分块的数目,其中n

hops

表示在其上分布所述经ldpc编码的位序列的所述经交织版本的子数据分组的数目,其中表示每轮次取自第一分块且被分布在多个子数据分组上的位的数目,其中n

bits/hop

表示每子数据分组的位的数目,其中表示经ldpc编码的位序列的经交织版本,其中ch1表示第一分块,其中表示经交织的位序列[例如,一个或多个其他分块的经交织版本(级联版本)]。

[0036]

在实施例中,所述经ldpc编码的位序列分段而成的所述多个分块的数目等于一除以所述经ldpc编码的位序列[nchunks=1/r]的码率。

[0037]

在实施例中,所述分段级被配置为基于以下语法将所述经ldpc编码的位序列102分段为所述多个分块:

[0038][0039]

其中i表示控制变量,其中j表示控制变量,其中n

chunks

表示将经ldpc编码的位序列分段而成的分块的数目,其中n

bits/chunk

表示每分块的位的数目,其中ch

i

表示所述多个分块中的每一个,以及其中v表示所述经ldpc编码的位序列。

[0040]

在实施例中,所述一个或多个其他分块是两个或者更多个其他分块,其中所述第一交织器级被配置为对所述两个或者更多个其他分块的级联版本进行交织。

[0041]

在实施例中,所述交织器包括级联级,所述级联级被配置为将所述两个或者更多个其他分块级联,以获得所述两个或者更多个其他分块的级联版本。

[0042]

在实施例中,所述级联级被配置为基于以下语法将所述多个分块中的所述一个或多个其他分块级联:

[0043][0044][0045]

其中k表示控制变量,其中i表示控制变量,其中j表示控制变量,其中n

bits/chunk

表

示每分块的位的数目,其中表示一个或多个其他分块的级联版本,其中ch

i

表示所述多个分块中的每一个。

[0046]

在实施例中,所述交织器被配置为基于以下语法对所述经ldpc编码的位序列进行交织,以获得所述经ldpc编码的位序列的经交织版本:

[0047]

[0048][0049]

其中i表示控制变量,

[0050]

其中j表示控制变量,

[0051]

其中n表示所述经ldpc编码的位序列的位(例如,信息位 冗余位)的数目,

[0052]

其中k表示控制变量,

[0053]

其中r表示码率,

[0054]

其中n

chmnks

表示将经ldpc编码的位序列分段而成的分块的数目,

[0055]

其中n

hops

表示在其上分布所述经ldpc编码的位序列的所述经交织版本的子数据分组的数目,

[0056]

其中表示分布所述第一分块的位所需的轮次的数目,

[0057]

其中表示每轮次取自所述第一分块且被分布在所述多个子数据分组上的位的数目,

[0058]

其中表示每轮次取自所述其他分块且被分布在所述多个子数据分组上的位的数日,

[0059]

其中n

bits/hop

表示每子数据分组的位的数目,

[0060]

其中n

bits/chunk

表示每分块的位的数目,

[0061]

其中n

bits/chunk/hop

表示每跳变(hop)每分块的位的数目,

[0062]

其中v表示所述经ldpc编码的位序列,

[0063]

其中表示所述经ldpc编码的位序列的所述经交织版本,

[0064]

其中ch

i

表示所述多个分块中的每一个,

[0065]

其中ch1表示所述第一分块,

[0066]

其中表示所述经交织的位序列[例如,所述一个或多个其他分块的经交织版本[级联版本]]。

[0067]

进一步的实施例提供一种用于对经ldpc编码的码字进行交织的交织器,所述经ldpc编码的码字包括具有736个经fec编码位的位序列,其中所述交织器包括:分段级,被配置为将具有736个经fec编码位的所述位序列z分段为四个相等大小的分块,所述四个分块包括编号一分块、编号二分块、编号三分块以及编号四分块;第一交织器级,被配置为伪随机地扰乱由所述编号一分块、所述编号三分块以及所述编号四分块组成的位序列y,以获得所述位序列的经扰乱版本y

′

,其中所述序列y被使用扰乱向量u伪随机地扰乱,所述扰乱向量u是从由10位伽罗瓦(galois)lfsr以生成多项式g(x)=x

10

x7 1产生的位随机序列v导出的;第二交织器级,被配置为通过基于以下语法取决于索引n分配所述编号二分块(110_1)的每一位c

n

、无线电突发索引l以及在所述无线电突发内的位置i,在l个无线电突发上分布所述编号二分块:

[0068][0069][0070]

其中n∈{0,1,2...183},其中n=0指代编号二分块(110_1)的第一位c0,

[0071]

其中所述第二交织器级(108)被配置为通过基于以下语法取决于索引m分配无线电突发索引l和位置i,在所述l个无线电突发上分布所述位序列的所述经扰乱版本y

′

(112):

[0072][0073]

i(m)=8 (m mod 24),

[0074]

其中m∈{0,1,2...551},其中m=0指代所述位序列的所述经扰乱版本y

′

(112)的第一位y’0。

[0075]

其他实施例提供一种发送器,包括:根据本文中所描述的实施例中的一个的交织器;ldpc编码器,被配置为提供经ldpc编码的位序列;以及发送单元,被配置为使用多个子数据分组发送所述经ldpc编码的位序列的经交织版本,其中所述多个子数据分组被非同时地[例如,使用跳时和/或跳频模式]发送。

[0076]

其他实施例提供一种用于对经ldpc编码的位序列的经交织版本进行解交织的解交织器,所述解交织器包括:第一解交织器级,被配置为对所述经ldpc编码的位序列的所述经交织版本逐块进行解交织,以获得第一分块以及经交织的位序列[例如,一个或多个其他分块[例如,第二分块以及视需要第三分块]的经交织版本或者两个或者更多个其他分块[例如,第二分块以及第三分块]的级联版本];第二解交织器级,被配置为对所述经交织的位序列进行解交织,以获得所述一个或多个其他分块[例如,所述第二分块以及视需要所述第三分块];级联级,被配置为级联的所述第一分块与所述一个或多个其他分块,以获得所述经ldpc编码的位序列,其中所述多个分块中的所述第一分块由第一类型的位组成[例如,仅包括第一类型的位],其中所述第一类型的位

[0077]

‑

是所述经ldpc编码的位序列的错误校正位,

[0078]

‑

是所述经ldpc编码的位序列的重复累积位(repeat accumulate bit),和/或

[0079]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以所述经ldpc编码的位序列的坦纳图表示来表示。

[0080]

在实施例中,所述第一分块绕过所述第二解交织器级[例如,所述第一分块不由所述第二解交织器级解交织]。

[0081]

在实施例中,所述一个或多个其他分块中的一个分块[例如,所述第二分块]由第二类型的位组成,其中所述第二类型的位

[0082]

‑

是所述经ldpc编码的位序列的信息位[以及例如,所述经ldpc编码的位序列的其余错误校正位],和/或

[0083]

‑

通过包括与错误校正校验节点的伪随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0084]

在实施例中,所述一个或多个其他分块是两个或者更多个其他分块,其中所述两个或者更多个其他分块中的另一分块[例如,所述第三分块]由所述第一类型的位组成。

[0085]

在实施例中,所述第一解交织器级是逐块解交织器。

[0086]

在实施例中,所述第二解交织器级是伪随机解交织器。

[0087]

在实施例中,所述伪随机解交织器是基于线性移位寄存器。

[0088]

在实施例中,所述伪随机解交织器是逐块解交织器。

[0089]

在实施例中,所述经交织的位序列是两个或者更多个其他分块的级联版本的经交

织版本,其中所述第二解交织器级被配置为对所述两个或者更多个其他分块的所述级联版本的所述经交织版本进行解交织。

[0090]

其他实施例提供一种接收器,其中所述接收器包括:接收单元,被配置为接收从发送器非同时地[例如,使用跳时和/或跳频模式]发送至所述接收器的多个子数据分组;根据前述技术方案中的一个的解交织器,其中所述解交织器被配置为使用描述所述发送器与所述接收器之间的信道的信道状态信息对利用所述多个子数据分组发送的经ldpc编码的位序列的衰落版本迭代地解交织;以及迭代解码器,被配置为对由所述解交织器迭代地提供的所述经ldpc编码的位序列迭代地解码,其中所述信道状态信息基于由所述迭代解码器提供的经解码位序列而迭代地更新。

[0091]

其他实施例提供一种用于对经ldpc编码的位序列进行交织的方法。所述方法包括以下步骤:将所述经ldpc编码的位序列分段为多个分块,所述多个分块包括第一分块以及一个或多个其他分块。另外,所述方法包括以下步骤:对所述一个或多个其他分块或者其级联版本进行交织,以获得经交织的位序列。另外,所述方法包括以下步骤:将所述多个分块中的所述第一分块与所述经交织的位序列逐块交织,以获得所述经ldpc编码的位序列的经交织版本。由此,所述多个分块中的所述第一分块由第一类型的位组成,其中所述第一类型的位

[0092]

‑

是所述经ldpc编码的位序列的错误校正位,

[0093]

‑

是所述经ldpc编码的位序列的重复累积位,和/或

[0094]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0095]

其他实施例提供一种用于对经ldpc编码的码字进行交织的方法,所述经ldpc编码的码字包括具有736个经fec编码位的位序列。所述方法包括以下步骤:将具有736个经fec编码位的所述位序列z分段为四个相等大小的分块,所述四个分块包括编号一分块、编号二分块、编号三分块以及编号四分块。另外,所述方法包括以下步骤:伪随机地扰乱由所述编号一分块、所述编号三分块以及所述编号四分块组成的位序列y,以获得所述位序列的经扰乱版本y

′

,其中所述序列y被使用扰乱向量u伪随机地扰乱,所述扰乱向量u是从由10位伽罗瓦lfsr以生成多项式g(x)=x

10

x7 1产生的位随机序列v导出的。另外,所述方法包括以下步骤:通过基于以下语法取决于索引n分配所述编号二分块(110_1)的每一位c

n

、无线电突发索引l以及在所述无线电突发内的位置i,在l个无线电突发上分布所述编号二分块(110_1):

[0096][0097][0098]

其中n∈{0,1,2

…

183},其中n=0指代所述编号二分块(110_1)的第一位c0。另外,所述方法包括以下步骤:通过基于以下语法取决于索引m分配无线电突发索引l以及位置i,在所述l个无线电突发上分布所述位序列的所述经扰乱版本y

′

(112):

[0099][0100]

i(m)=8 (m mod 24),

[0101]

其中m∈{0,1,2

…

551},其中m=0指代所述位序列的所述经扰乱版本y

′

(112)的第一位y'0。

[0102]

其他实施例提供一种用于对经ldpc编码的位序列的经交织版本进行解交织的方法。所述方法包括以下步骤:对所述经ldpc编码的位序列的所述经交织版本逐块解交织,以获得第一分块以及一个或多个其他分块的经交织版本。另外,所述方法包括以下步骤:对所述一个或多个其他分块的所述经交织版本进行解交织,以获得所述一个或多个其他分块。另外,所述方法包括以下步骤:将所述第一分块与所述一个或多个其他分块级联,以获得所述经ldpc编码的位序列。由此,所述多个分块中的所述第一分块由第一类型的位组成,其中所述第一类型的位

[0103]

‑

是所述经ldpc编码的位序列的错误校正位,

[0104]

‑

是所述经ldpc编码的位序列的重复累积位,和/或

[0105]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

附图说明

[0106]

本文中参考附图描述本发明的实施例。

[0107]

图1示出[3]中所提出的ldpc码的坦纳图表示的示意图,

[0108]

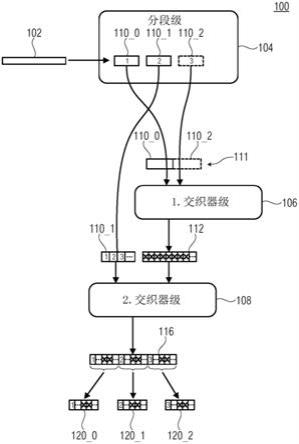

图2示出根据本发明的实施例的交织器的示意性方块图,

[0109]

图3示出根据实施例的包括发送器和接收器的系统的示意性方块图,

[0110]

图4示出根据本发明的实施例的用于对由ldpc编码器提供的经ldpc编码的位序列进行交织的交织器的示意性方块图,

[0111]

图5示出根据本发明的实施例的用于对由ldpc编码器提供的经ldpc编码的位序列进行交织的交织器的示意性方块图,

[0112]

图6示出根据本发明的实施例的由分段级执行的分段方法的流程图,

[0113]

图7示出根据本发明的实施例的由级联级执行的级联的方法的流程图,

[0114]

图8示出10位伽罗瓦线性反馈移位寄存器(lfsr)的示意性方块图,

[0115]

图9示出根据本发明的实施例的基于lfsr产生伪随机索引的方法的流程图,

[0116]

图10示出根据本发明的实施例的由第一交织器级执行的随机交织方法的流程图,

[0117]

图11示出根据本发明的实施例的由第二交织器级执行的逐块交织方法的流程图,

[0118]

图12示出根据本发明的实施例的用于对经ldpc编码的位序列的经交织版本进行解交织的解交织器的示意性方块图,

[0119]

图13示出根据本发明的实施例的迭代解码器的示意性方块图,

[0120]

图14示出根据本发明的实施例的解码方法的流程图,

[0121]

图15示出根据本发明的实施例的用于对经ldpc编码的位序列进行交织的方法的流程图,

[0122]

图16示出根据本发明的实施例的用于对经ldpc编码的位序列的经交织版本进行解交织的方法的流程图,以及

[0123]

图17示出处于初始状态的10位伽罗瓦线性反馈移位寄存器(lfsr)的示意性方块图。

[0124]

相等或者等效元件或者具有相等或者等效功能性的元件在以下描述中通过相等或者等效参考编号指示。

具体实施方式

[0125]

在以下描述中,阐述多个细节以提供对本发明的实施例的较透彻解释。然而,本领域技术人员应清楚,本发明的实施例可以在没有这些特定细节的情况下加以实践。在其他情况下,以方块图形式而非详细地示出公知结构和设备以便避免混淆本发明的实施例。另外,除非另外特定指出,否则可以将下文中所描述的不同实施例的特征彼此组合。

[0126]

图2示出根据本发明的实施例的用于对经ldpc编码的位序列102进行交织的交织器100的示意性方块图。交织器100包括分段级104、第一交织器级108以及第二交织器级110。

[0127]

分段级104可以被配置为将经ldpc编码的位序列102分段(例如,划分)为(例如,相等长度的)多个分块110_0至110_n

chunks

‑

1,n

chunks

≥2,其中所述多个分块包括第一分块110_1以及一个或多个其他分块,诸如第零分块110_0以及视需要第二分块110_2。

[0128]

由此,(例如,分段级104可以被配置为以如下方式将经ldpc编码的位序列102分段为多个分块110_0至110_n

chunks

‑

1)第一分块110_1由第一类型的位组成(例如,仅包括第一类型的位),其中第一类型的位是以下至少一种情况:

[0129]

‑

是所述经ldpc编码的位序列102的错误校正位,

[0130]

‑

是所述经ldpc编码的位序列102的重复累积位,

[0131]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以所述经ldpc编码的位序列102的坦纳图表示来表示。

[0132]

第一交织器级108可以被配置为对由分段级106提供的一个或多个其他分块(诸如第零分块110_0以及视需要第二分块110_2)进行交织,或者在两个或者更多个其他分块是由分段级104提供的情况下对两个或者更多个其他分块的级联版本(例如,第零分块110_0与第二分块110_2的级联版本)进行交织,以获得经交织的位序列112。

[0133]

第二交织器级110可以被配置为对由分段级104提供的第一分块110_1以及由第一交织器级106提供的经交织的位序列112逐块交织,以获得经ldpc编码的位序列的经交织版本116。

[0134]

如图2中所示,第一分块110_1绕过第一交织器级106,或者换句话讲,所述第一分块110_1不由第一交织器级106交织。

[0135]

可以观察到,在实施例中,第一分块110_1不是指多个分块的次序(或者序列)的特定分块,例如,不是指编号一分块,该编号一分块是多个分块的次序(或者序列)的开始或者起点,即,后面跟随编号二分块以及视需要编号三分块,如图2中由分块内的编号1、2以及3所指示。恰恰相反,第一分块110_1是指多个分块中由第一类型的位组成的分块,即经ldpc编码的位序列的错误校正位、经ldpc编码的位序列的重复累积位和/或通过包括与至少两个错误校正校验节点的非随机连接的变量节点且以经ldpc编码的位序列的坦纳图表示来表示的位。举例而言,参考[3]中提出的(736,184)ldpc码且假设所述ldpc码分段为相等大小的四个分块:编号一分块(例如,具有位1至736中的位1至184),后面跟随编号二分块(例

如,具有位1至736中的位185至368),后面跟随编号三分块(例如,具有位1至736中的位369至552),后面跟随编号四分块(例如,具有位1至736中的位553至736);该第一分块110_1表示(或者指代)编号二分块,这是因为编号二分块是由经ldpc编码的位序列的错误校正位、经ldpc编码的位序列的重复累积位和/或通过包括与至少两个错误校正校验节点的非随机连接的变量节点且以经ldpc编码的位序列的坦纳图表示来表示的位组成。

[0136]

在实施例中,(例如,分段级104可以被配置为以如下方式将经ldpc编码的位序列102分段为多个分块110_0至110_n

chunks

‑

1)所述一个或多个其他分块中的一个分块(诸如第零分块110_0)由第二类型的位组成,其中第二类型的位为以下至少一种情况:

[0137]

‑

为所述经ldpc编码的位序列的信息位,和/或

[0138]

‑

通过包括至错误校正校验节点的伪随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0139]

在实施例中,(例如,分段级104可以被配置为以如下方式将经ldpc编码的位序列102分段为多个分块110_0至110_n

chunks

‑

1)所述其他分块中的另一分块(诸如第二分块110_2)由第一类型的位组成(例如,仅包括第一类型的位),即,是以下至少一种情况:

[0140]

‑

是所述经ldpc编码的位序列102的错误校正位,

[0141]

‑

是所述经ldpc编码的位序列102的重复累积位,

[0142]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点]以所述经ldpc编码的位序列102的坦纳图表示来表示。

[0143]

在实施例中,第一交织器级106可以是伪随机交织器,诸如基于线性反馈移位寄存器的交织器或者块交织器。

[0144]

在实施例中,第二交织器级108可以是逐块交织器。逐块交织器108可以被配置为在多个子数据分组120_0至120_n

hops

‑

1(n

hops

≥2)上分布经ldpc编码的位序列116的经交织版本。

[0145]

由此,逐块交织器108可以被配置为在至少两个轮次中在所述多个子数据分组120_0至120_n

hops

‑

1上逐块地分布所述多个分块中的第一分块110_1的位,例如,使得在第一轮次中,所述第一分块110_1的位[例如,两个连续位]的连续块循环地映射至所述多个子数据分组120_0至120_n

hop

‑

1,以及在第二轮次中,所述第一分块110_1的位[例如,两个连续位]的其他连续块循环地映射至所述多个子数据分组120_0至120_n

hop

‑

1,依此类推,直至第一分块110_1的所有位逐块地分布于多个子数据分组120_0至120_n

hop

‑

1上。

[0146]

举例而言,例示性地假设经ldpc编码的位序列的经交织版本116分布于三个子数据分组120_0至120_2上,逐块交织器108可以被配置为在第一轮次中将第一分块110_1的第零以及第一位映射至第零子数据分组120_0,将第一分块110_1的第二和第三位映射至第一子数据分组120_1,以及将第一分块110_1的第四以及第五位映射至第二子数据分组120_2。另外,逐块交织器108可以被配置为在第二轮次中将第一分块110_1的第六以及第七位映射至第零子数据分组120_0,将第一分块110_1的第八以及第九位映射至第一子数据分组120_1,以及将第一分块110_1的第十以及第十一位映射至第二子数据分组120_2。可以重复此程序,直至第一分块110_1的所有位分布于多个子数据分组上。

[0147]

另外,逐块交织器108可以被配置为在所述多个子数据分组上均匀地逐块地分布

由所述第一交织器级106提供的所述经交织的位序列112的位(例如,所述多个子数据分组120_0至120_n

hops

‑

1用由所述第一交织器级106提供的所述经交织的位序列112的位均匀地填满)。

[0148]

举例而言,继续经ldpc编码的位序列的经交织版本116分布于三个子数据分组110_0至110_2上的示例,逐块交织器108可以被配置为通过将经交织的位序列112的位的第零块映射至第零子数据分组120_0而填满第零子数据分组120_0,通过将经交织的位序列112的位的第一块映射至第一子数据分组120_1而填满第一子数据分组120_1,以及通过将经交织的位序列112的位的第二块映射至第二子数据分组120_2而填满第二子数据分组120_2。

[0149]

随后,更详细地描述交织器100的实施例。

[0150]

1.混合逐块随机交织器

[0151]

为了克服如在本专利申请的引言部分描述的有限信道知识的不利影响,在实施例中,以可以改良(例如,优化)最初估计的衰落系数的使用的方式对ldpc码字的位进行排序。这意味着即使在具有少数估计衰落系数的情况下也仍能触发ldpc解码器的bp算法。举例而言,由这可以借助于最初经解码ldpc码字起始决策指导信道估计(ddce)[2]。迭代解码器可以持续遍历信道估计器与ldpc解码器之间的信息,直至成功地解码整个ldpc码字为止。

[0152]

实施例提供交织器100,其旨在以展现阶梯结构的码率r≤1/2重构ldpc码的坦纳图。根据实施例的交织器100的目的是以有限数目个估计衰落系数允许bp解码算法的可行性。因为前置码序列仅能够估计前几个相邻符号,因此交织器100对ldpc位进行排序,使得最初估计的衰落系数满足ldpc解码器的最小触发阈值值。换句话讲,交织器100使得有可能增大使校验节点具有从其对应变量节点接收的仅一个已抹除llr的机率。

[0153]

在实施例中,采用两个策略。第一策略是将展现随机连接的k个变量节点与具有阶梯连接的前k个变量节点调换。对于将其k个信息位映射至经编码码字的前k个位的系统码,进行此操作。在系统性信息位未置放在码字的起点的情况下,不需要此调换步骤。换句话讲,目的是以具有阶梯连接的k个变量节点开始。第二策略是将位分布在发送跳变上。对于调换的阶梯分块,采用逐块交织器。此逐块交织器在连续轮次中将阶梯分块的位分布在跳变上。每一轮次将两个连续位置放在一个跳变上。其余码字位通过随机交织器交织。最终,其在逐块分布的位之后分布于跳变上。

[0154]

根据实施例的混合交织器的本质在于两方面:第一,其分解经编码码字的阶梯结构。第二,其将系统性部分分布在跳变上。这意味着第一估计衰落系数将被跨码字扰乱,而非堆叠在一个分块中。因此,ldpc解码器即使在具有最少估计衰落系数的情况下也可以触发。

[0155]

图3示出根据实施例的包括发送器202和接收器204的系统200的示意性方块图。

[0156]

发送器202包括:ldpc编码器206,被配置为提供经ldpc编码的码字102(例如,经ldpc编码的位序列),交织器100被配置为对经ldpc编码的码字102进行交织,以获得经ldpc编码的码字的经交织版本116;以及导频序列插入单元208,被配置为将导频序列210添加(例如,附加)至经ldpc编码的码字的经交织版本116。

[0157]

接收器204包括信道估计器212、解交织器140、迭代ldpc解码器214,以及交织器100,其中交织器100与解交织器彼此互补。

[0158]

换句话讲,图3示出根据实施例的(混合)交织器100的系统模型。长度为k个位的信息向量由速率为r的ldpc编码器206编码,以产生长度为n个位的输出码字v=[v

0 v1…

v

n

‑1]102,其中n=k/r。接着,根据实施例,由交织器100对经编码码字102进行交织,以产生相同长度的经交织码字)116。此后,将长度为l

p

的前置码序列210附加至经交织向量116。最后,对数据进行调制并在衰落信道上发送。

[0159]

在接收器204侧处,提取前置码序列210且将其馈送至信道估计器212。由于前置码大小有限,因此信道估计器212最初仅能够提供关于第一相邻符号的csi。所接收序列以及部分估计的衰落向量两者经解交织且馈送至ldpc解码器214。尽管csi最初稀缺,但所提出的交织器设计允许触发ldpc解码器214。因此,ldpc解码器214仍能够提供非本征信息。该经解码信息接着被经交织且反馈至信道估计器212作为补充导频码元。这允许估计较多衰落系数以便以额外先验概率触发ldpc的置信度传播解码。迭代解码过程连续地重复,直至整个ldpc码字被解码为止。

[0160]

图4示出根据本发明的实施例的用于对由ldpc编码器206提供的经ldpc编码的位序列102进行交织的交织器的示意性方块图。交织器100包括分段级104、级联级105、第一交织器级106以及第二交织器级108。

[0161]

分段级104可以被配置为将经ldpc编码的位序列102分段(例如,划分)为(例如,相等长度的)多个分块110_0至110_n

chunks

‑

1,n

chunks

≥2,其中所述多个分块包括第一分块110_1以及两个或者更多个其他分块110_0、110_2至n

chunks

‑

1。

[0162]

由此,(例如,分段级104可以被配置为以如下方式将经ldpc编码的位序列102分段为多个分块110_0至110_n

chunks

‑

1)第一分块110_1由第一类型的位组成(例如,仅包括第一类型的位),其中第一类型的位是以下至少一种情况:

[0163]

‑

是所述经ldpc编码的位序列102的错误校正位,

[0164]

‑

是所述经ldpc编码的位序列102的重复累积位,

[0165]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以所述经ldpc编码的位序列102的坦纳图表示来表示。

[0166]

所述级联级被配置为将所述两个或者更多个其他分块110_0、110_2至110_n

chunks

‑

1级联,以获得所述两个或者更多个其他分块110_0、110_2至110_n

chunks

‑

1的级联版本111。

[0167]

例如(伪)随机交织器的第一交织器级108可以被配置为例如基于线性反馈移位寄存器(lfsr)107对所述两个或者更多个其他分块110_0、110_2至110_n

chunks

‑

1的级联版本111进行交织。

[0168]

例如逐块交织器的第二交织器级110可以被配置为对由分段级104提供的第一分块110_1以及由第一交织器级106提供的经交织的位序列112逐块交织,以获得经ldpc编码的位序列的经交织版本116。

[0169]

换句话讲,图4示出根据实施例的混合逐块随机交织器100的方块图。交织器100采用长度为n位的经ldpc编码的码字v102,以及输出相同长度的经交织版本116。交织过程涉及四个步骤:分段(例如,由分段级104执行)、级联(例如,由级联级105执行)、随机置换(例如,由第一交织器级106执行)以及逐块分配(例如,由第二交织器级108执行)。首先,分段步骤意味着将n位码字102分裂为长度相等的n

chunks

=1/r个分块110_0至110_n

chunks

‑

1,其中r

为码率。第一分块110_1被放在一边,而其余(n

chunks

‑

1)个分块110_0、110_2至110_n

chunks

‑

1被再次级联。此后,将可以借助于线性反馈移位寄存器(lfsr)107产生的伪随机交织器106应用于级联的序列111。这得到新序列112,其中级联的序列111的元素根据lfsr 107的置换索引而置放。最后,将交织序列112与分离的分块110_1一起馈送至逐块交织器108。后者的目的是将位均匀地分布在所发送的跳变(或者子数据分组120_0至120_n

hops

‑

1)上。其首先始于将来自分离的分块110_1的两个位置放在每一跳变120_0至120_n

hops

‑

1上。

[0170]

在遍历了所有跳变120_0至120_n

hops

‑

1之后,通过在每一跳变上分配另外两个位来开始下一轮次。重复此过程,直至分离的分块110_1的所有位用完为止。同时,随机交织的序列112均匀地分布在跳变120_0至120_n

hops

‑

1上。这意味着,每一跳变将以逐块方式以1:n

chunks

‑

1的比率分别包括来自分离的分块110_1的位,后面跟随随机交织的分块的位。在接下来的部分中将对这些四个步骤进行透彻描述。

[0171]

图5示出根据本发明的实施例的用于对由ldpc编码器206提供的经ldpc编码的位序列102交织的交织器的示意性方块图。交织器100包括分段级104、级联级105、第一交织器级106以及第二交织器级108。

[0172]

分段级104可以被配置为将经ldpc编码的位序列102分段(例如,划分)为(例如,相等长度的)四个分块110_0至110_3,其中所述四个分块包括第一分块110_1以及三个其他分块110_0、110_2、110_3。

[0173]

由此,(例如,分段级104可以被配置为以如下方式将经ldpc编码的位序列102分段为四个分块110_0至110_3)第一分块110_1由第一类型的位组成(例如,仅包括第一类型的位),其中第一类型的位是以下至少一种情况:

[0174]

‑

是所述经ldpc编码的位序列102的错误校正位,

[0175]

‑

是所述经ldpc编码的位序列102的重复累积位,

[0176]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以所述经ldpc编码的位序列102的坦纳图表示来表示。

[0177]

级联级105可以被配置为将三个其他分块110_0、110_2、110_3级联,以获得所述三个其他分块110_0、110_2、110_3的级联版本111。

[0178]

例如(伪)随机交织器的第一交织器级108可以被配置为例如基于线性反馈移位寄存器(lfsr)107对所述三个其他分块110_0、110_2、110_3的级联版本111进行交织。

[0179]

例如逐块交织器的第二交织器级110可以被配置为对由分段级104提供的第一分块110_1与由第一交织器级106提供的经交织的位序列112逐块交织,以获得经ldpc编码的位序列的经交织版本116。

[0180]

换句话讲,图5描绘根据应用于[3]中给出的(736,184)ldpc码的实施例的(混合)交织器100的示例。因为码率为1/4,因此应将ldpc码字102分段为n

chunks

=4个分块。每一分块具有n/n

chunks

=184个位。第一分块110_1被分离,而第零、第二和第三分块110_0、110_2、110_3重新级联以形成长度为3

×

184=552个位的向量111。此级联向量111被随机交织(例如,通过第一交织器级106),以及随分离的第一分块110_1一起被馈送至逐块交织器108。假设必须在n

hops

=23上发送数据,则逐块交织器108应以逐块方式将数据映射至23个跳变120_0至120_22。其首先始于将来自第一分块110_1的两个位映射在每一跳变上。在23个跳

变120_0至120_22之后,第一分块110_1的46个位将被映射。为了映射第一分块110_1的所有184个位,此过程可以重复四次。此后,随机交织向量112的552个位可以映射至跳变120_0至120_22,其中每一跳变含有在一个轮次上获取的24个位。

[0181]

1.1分段

[0182]

图6示出根据本发明的实施例的由分段级104执行的分段方法400的流程图。

[0183]

在第一步骤402中,提供输入,其中所述输入包括经ldpc编码的位序列v、经ldpc编码的位序列的数目n个位(例如,信息位 冗余位)、经ldpc编码的位序列的数目k个信息位、码率r以及经ldpc编码的位序列被分段而成的分块的数目n

chunks

。

[0184]

在第二步骤404中,基于等式n

bits/chunk

=n/n

chunks

判定每分块的位的数目n

bits/chunk

。

[0185]

在第三步骤406中,将控制变量i设置为零,i=0。

[0186]

在第四步骤408中,将控制变量j设置为零,j=0。

[0187]

在第五步骤410中,基于等式ch

i

(j)=v(j in

bits/chunk

)将经ldpc编码的位序列v的位分配给第i分块ch

i

。

[0188]

在第六步骤412中,将控制变量j增大一,j=j 1。

[0189]

在第七步骤414中,校验控制变量j是否小于每分块的位的数目n

bits/chunk

,j<n

bits/chunk

,以及如果是,则以第五步骤410继续,否则,以第八步骤416继续。

[0190]

在第八步骤416中,将控制变量i增大一,i=i 1。

[0191]

在第九步骤418中,校验控制变量i是否小于经ldpc编码的位序列待被分段而成的分块的数目n

chunks

,i<n

chunks

,以及如果是,则以第四步骤408继续,否则,以第十步骤420继续。

[0192]

在第十步骤420中,提供多个分块作为输出。

[0193]

在实施例中,第一步骤(=例如由分段级104执行的分段步骤)将经ldpc编码的码字102划分为相等长度的n

chunks

个分块110_0至110_n

chunks

‑

1。图6示出分段过程的流程图。分段块104以长度为n位的码字v102作为输入,以及输出n

chunks

个分块110_0至110_n

chunks

‑1,...,n

chunks

‑

1,其中n

chunks

=1/r,以及r=k/n为码率。每一分块具有从(经ldpc编码的码字102)v连续获取的n

bits/chunk

=n/n

chunks

个位。每一分块ch

i

由下式给出:

[0194][0195]

以(736,184)ldpc码为例,经编码码字102被划分为长度为n

bits/chunk

=736/4=184个位的四个分块110_0至110_3。

[0196]

在实施例中,分段级104可以被配置为基于以下语法(例如,通过执行以下伪码)而将经ldpc编码的位序列102分段为多个分块:

[0197][0198]

其中i表示控制变量,其中j表示控制变量,其中n

chunks

表示将经ldpc编码的位序列

分段而成的分块的数目,其中n

bits/chunk

表示每分块的位的数目,其中ch

i

表示所述多个分块中的每一个,以及其中v表示所述经ldpc编码的位序列。

[0199]

1.2级联

[0200]

图7示出根据本发明的实施例的由级联级105执行的级联的方法500的流程图。

[0201]

在第一步骤502中,提供输入,其中所述输入包括一个或多个其他分块ch

i

,

…

,n

chunks

‑

1,i≠1、经ldpc编码的位序列的数目n个位(例如,信息位 冗余位)以及经ldpc编码的位序列待被分段而成的分块的数目n

chunks

。

[0202]

在第二步骤504中,基于等式n

bits/chunk

=n/n

chunks

判定每分块的位的数目n

bits/chunk

。

[0203]

在第三步骤506中,将控制变量i设置为零,i=0。

[0204]

在第四步骤508中,将控制变量k设置为零,k=0。

[0205]

在第五步骤510中,将控制变量j设置为零,j=0。

[0206]

在第六步骤512中,基于等式级联一个或多个其他分块。

[0207]

在第七步骤514中,将控制变量j增大一,j=j 1。

[0208]

在第八步骤516中,校验控制变量j是否小于每分块的位的数目n

bits/chunk

,j<n

bits/chunk

,以及如果是,则重复第六步骤512至第八步骤516,否则,以第九步骤518继续。

[0209]

在第九步骤518中,将控制变量i增大一,i=i 1。

[0210]

在第十步骤520中,校验控制变量i是否小于经ldpc编码的位序列待被分段而成的分块的数目n

chunks

,i<n

chunks

,以及如果是,则以第十一步骤522继续,否则,以第十二步骤524继续。

[0211]

在第十一步骤522中,校验控制变量i是否等于一,i==1,以及如果是,则以第九步骤518继续,否则,以第十三步骤526继续。

[0212]

在第十三步骤526中,将控制变量k增大一,k=k 1,以及以第五步骤510继续。

[0213]

在第十二步骤524中,提供一个或多个其他分块的级联版本作为输出。

[0214]

在实施例中,在将ldpc码字102分段为n

chunks

个分块110_0至110_n

chunks

‑

1之后,第一分块110_1被分离,而其余n

chunks

‑

1个分块110_0、110_2至110_n

chunks

‑

1可以重新级联在一起。图7描绘级联的过程。级联器将取ch

i

,

…

,n

chunks

‑

1,i≠1(即,一个或多个其他分块110_0、110_2至110_n

chunks

‑

1),以及将其级联为长度为(n

chunks

‑

1)

×

n

bits/chunk

的一个复合向量111。级联向量由下式给出:

[0215][0216]

在实施例中,级联级105可以被配置为基于以下语法(例如,通过执行以下伪码)将多个分块(110_0

‑

110_n

chunks

‑

1)110_0至110_n

chunks

‑

1中的一个或多个其他分块110_0、110_

2至110_n

chunks

‑

1级联:

[0217][0218]

其中k表示控制变量,其中i表示控制变量,其中j表示控制变量,其中n

chunks

表示将所述经ldpc编码的位序列分段而成的分块的数目,其中n

bits/chunk

表示每分块的位的数目,其中表示所述一个或多个其他分块的级联版本,其中ch

i

表示所述多个分块中的每一个。

[0219]

1.3随机交织器

[0220]

在实施例中,下一步骤(=随机交织器步骤,例如,由第一交织器级106执行)使级联向量111随机交织。为此目的,一种可能性是利用线性反馈移位寄存器(lfsr)107以便产生伪随机索引。所部署的lfsr 107的缓存器数目n

r

必须满足以下不等式:

[0221][0222]

对于(736,184)ldpc示例,级联向量ch0→

3\1

111具有3

×

184个位。这意味着至少n

r

=10个缓存器的lfsr 107是必需的,以便提供唯一的置换索引。循环冗余校验(crc)可能是此类lfsr 107初始化的有效的潜在候选项。其是通过将级联向量ch0→

3\1

111依次移位至lfsr后面跟随n

r

个零来计算的。

[0223]

图8示出10位伽罗瓦lfsr 107的示例,其生成多项式g(x)=x

10

x7 1=0x240,以及初始状态对应于0x2d7的校验和。lfsr 107遍历除全零状态之外的所有个状态进行迭代。此类lfsr的下一状态为0x32b,其等于十进制索引811。此索引值大于所需置换索引的数目。因此,所述索引被丢弃,以及lfsr进入下一迭代。

[0224]

图9示出根据本发明的实施例的基于lfsr产生伪随机索引的方法600的流程图。

[0225]

在第一步骤602中,提供输入,其中所述输入包括生成多项式gen、lfsr的初始状态initial、经ldpc编码的位序列的数目n个位(例如,信息位 冗余位)以及经ldpc编码的位序列待被分段而成的分块的数目n

chunks

。

[0226]

在第二步骤604中,基于等式n

bits/chunk

=n/n

chunks

判定每分块的位的数目n

bits/chunk

,以及基于等式l=(n

chunks

‑

1)

×

n

bits/chunk

判定所需索引的长度l。

[0227]

在第三步骤606中,将控制变量j设置为零,j=0。

[0228]

在第四步骤608中,将lfsr的反馈(feedback)设置为初始状态initial&1,feedback=initial&1,即,初始状态的最末位(最低有效位)提供为feedback。

[0229]

在第五步骤610中,将lfsr的初始状态initial向右移位一个位置,inital>>1。

[0230]

在第六步骤612中,校验lfsr的feedback是否等于1,feedback=1,以及如果是,则以第七步骤614继续,否则以第八步骤616继续。

[0231]

在第七步骤614中,将lfsr的初始状态initial与lfsr的生成多项式进行异或,以获得新的初始状态

[0232]

在第八步骤616中,校验lfsr的初始状态initial的十进制当量是否等于或者小于所需索引的长度l,以及如果是,则以第九步骤618继续,否则以第四步骤608继续。

[0233]

在第九步骤618中,将位置j处的置换索引向量π设置为initial减一,π(j)=initial

‑

1。

[0234]

在第十步骤620中,将控制变量j增大一,j=j 1。

[0235]

在第十一步骤622中,校验控制变量j是否小于l,j<l,以及如果是,则以第四步骤608继续,否则以第十二步骤624继续。

[0236]

在第十二步骤624中,将置换索引向量π提供为输出。

[0237]

换句话讲,图9中示出借助于lfsr 107进行的伪随机索引产生器的流程图。lfsr 107由度为n

r

的原始生成多项式产生,以及由crc校验和或者其个循环跨度内的任意初始状态初始化。在每次迭代之后,lfsr展现对应于候选置换索引的新状态。此索引必须与所需索引的长度l=(n

chunks

‑

1)

×

n

bits/chunk

进行比较。如果所产生的索引小于l,则将其附加至置换索引向量π。否则,丢弃所述状态,以及lfsr进入下一状态。当π中产生的索引数达到l时,算法停止。

[0238]

图10示出根据本发明的实施例的由第一交织器级106(例如,lfsr随机交织器)执行的用于随机交织的方法700的流程图。

[0239]

在第一步骤702中,提供输入,其中所述输入包括其他分块的级联版本置换索引向量π、经ldpc编码的位序列的数目n个位(例如,信息位 冗余位)以及经ldpc编码的位序列待被分段而成的分块的数目n

chunks

。

[0240]

在第二步骤704中,基于等式n

bits/chunk

=n/n

chunks

判定每分块的位的数目n

bits/chunk

,以及基于等式l=(n

chunks

‑

1)

×

n

bits/chunk

判定所需索引的长度l。

[0241]

在第三步骤706中,将控制变量j设置为零,j=0。

[0242]

在第四步骤708中,基于置换索引向量π对其他分块进行伪随机交织,以获得经交织的位序列(例如其他分块的级联版本的经交织版本),

[0243]

在第五步骤710中,将控制变量j增大一,j=j 1。

[0244]

在第六步骤712中,校验控制变量j是否小于l,j<l,以及如果是,则以第四步骤708继续,否则以第七步骤714继续。

[0245]

在第七步骤714中,将经交织的位序列提供为输出。

[0246]

在实施例中,在产生伪随机索引之后,其可用于置换级联的(n

chunk

‑

1)分块向量(即,一个或多个其他分块110_0、110_2至110_n

chunks

‑

1的级联版本)。随机交织器106接收置换向量π以及级联向量111。其产生与长度相同的交织向量112。根据π中的置换索引完成来自的元素至的映射,使得:

[0247][0248]

其中=(n

chunks

‑

1)

×

n

bits/chunk

为级联索引的长度。图10中说明随机交织过程。

[0249]

在实施例中,第一交织器级106可以被配置为基于以下语法(例如,通过执行以下伪码)对多个分块110_0至110_n

chunks

‑

1中的其他分块110_0、110_2至110_n

chunks

‑

1的级联版本进行交织:

[0250]

for j=0:((n

chunks

‑

1)n

bits/chunk

)

‑1[0251][0252]

end

[0253]

其中j表示控制变量,其中n

chunks

表示将所述经ldpc编码的位序列分段而成的分块的数目,其中n

bits/chunk

表示每分块的位的数目,其中表示所述经交织的位序列(例如,所述一个或多个其他分块的经交织版本(级联版本)),其中表示所述一个或多个其他分块的级联版本,其中π表示线性反馈移位寄存器的置换索引向量。

[0254]

1.4逐块交织器

[0255]

图11示出根据本发明的实施例的由第二交织器级108执行的逐块交织方法800的流程图。

[0256]

在第一步骤802中,提供输入,其中输入包括第一分块ch1、经交织的位序列经ldpc编码的位序列的数目n个位(例如,信息位 冗余位)、经ldpc编码的位序列被分段而成的分块的数目n

chunks

(其等于1/r)、在其上待分布经ldpc编码的位序列的子数据分组的数目n

hops

,以及每轮次取自第一分块且被分布在多个子数据分组上的位的数目

[0257]

在第二步骤804中,基于等式n

bits/chunk

=n/n

chunks

判定每分块的位的数目n

bits/chunk

,基于等式n

bits/hop

=n/n

hops

判定每子数据分组的位的数目n

bits/hop

,基于等式n

bits/chunk/hop

=n

bits/chunk

/n

hops

判定每分块每子数据分组的位的数目n

bits/chunk/hop

,基于等式判定分布第一分块的位所需的轮次的数目以及基于等式判定每轮次取自其他分块且

被分布在多个子数据分组上的位的数目

[0258]

在第三步骤806中,将控制变量i设置为零,i=0。

[0259]

在第四步骤808中,将控制变量j设置为零,j=0。

[0260]

在第五步骤810中,将控制变量k设置为零,k=0。

[0261]

在第六步骤812中,基于等式在第六步骤812中,基于等式将第一分块ch1的位映射至经ldpc编码的位序列的交织版本

[0262]

在第七步骤814中,将控制变量k增大一,k=k 1。

[0263]

在第八步骤816中,校验k是否小于所判定的分布第一分块的位所需的轮次的数目以及如果是,则以第六步骤812继续,否则以第九步骤818继续。

[0264]

在第九步骤818中,将控制变量j增大一,j=j 1。

[0265]

在第十步骤820中,校验j是否小于每轮次取自第一分块且被分布在多个子数据分组上的位的数目以及如果是,则以第五步骤810继续,否则以第十一步骤822继续。

[0266]

在第十一步骤822中,将控制变量j设置为零,j=0。

[0267]

在第十二步骤824中,基于等式在第十二步骤824中,基于等式将经交织的位序列映射至经ldpc编码的位序列的交织版本

[0268]

在第十三步骤826中,将控制变量j增大一,j=j 1。

[0269]

在第十四步骤828中,校验控制变量j是否小于每轮次取自其他分块且被分布在多个子数据分组上的位的数目以及如果是,则以第十二步骤824继续,否则以第十五步骤830继续。

[0270]

在第十五步骤830中,将控制变量i增大一,i=i 1。

[0271]

在第十六步骤832中,校验控制变量i是否小于在其上待分布经ldpc编码的位序列的交织版本的子数据分组的数目n

hops

,以及如果是,则以第四步骤808继续,否则以第十七步骤834继续。

[0272]

在第十七步骤834中,将经ldpc编码的位序列的交织版本提供为输出。

[0273]

在实施例中,最后步骤(=第二交织步骤,例如,由第二交织器级108执行)涉及所提取的分块ch1(即,第一分块110_1)与随机经交织向量)(即,经交织的位序列112以逐块方式的交织。想法是将经编码位均匀地分布在所发送的跳变120_1至120_n

hops

‑

1上。每一跳变包括分别来自(第一分块110_1)ch1以及(其他分块110_0、110_2至110_n

chunks

‑

1)的位,比率为1∶n

chunks

‑

1。这意味着,如果要在n

hops

(n

bits/hop

=n/n

hops

)上发送n个数据位,则将从(第一分块110_1)ch1取位的1/n

chunks

,而应从(其他分块110_

0、110_2至110_n

chunks

‑

1)取其余的(n

chunks

‑

1)/n

chunks

。此外,应以的逐跳变循环方式来获取映射在每一跳变上的(第一分块110_1)ch1的位。这意味着,(第一分块110_1)ch1的前两个位映射至第一跳变120_0上。接下来的两个位置放在第二跳变120_1上,依此类推。在n

hops

之后,另一轮次始于将(第一分块110_1)ch1的两个位映射在每一跳变上。在映射在每一跳变上。在之后,(第一分块110_1)ch1的所有n

bits/chunk

个位完全映射至n

hops

。最后,在一个轮次内将经交织向量112的位映射至跳变120_0至120_n

hops

‑

1,其中一轮次在每一跳变上包括n

bits/chunk/hop

=((n

chunks

‑

1)

×

n

bits/chunk

)/n

hops

个位。

[0274]

在图11中示出逐块随机交织器的流程图。(第一分块110_1)ch1以及(经交织的位序列112)被馈送至交织器108,从而产生输出向量116,其对应于ldpc经编码向量v102的经交织版本。交织器108在n

hops

上循环,为每一跳变分配n

bits/hop

个位。其首先始于在个轮次中将个位从(第一分块110_1)ch1映射于每一跳变上。这可以表示为:

[0275][0276]

其中

[0277]

n

hops

是跳变的数目,

[0278]

n

bits/hop

=n/n

hops

是在每一跳变上发送的位的数目,

[0279]

是每轮次从ch1映射到每一跳变上的位的数目,

[0280]

是耗尽ch1的所有位所需的轮次的总数,

[0281]

i=0,

…

,n

hops

‑

1是跳变索引,

[0282]

是轮次内的位索引,以及

[0283]

是轮次索引。

[0284]

在之后,每一跳变将具有来自(第一分块110_1)ch1的个位。每一跳变上的其余n

bits/hop

个位应取自(经交织的位序列112)因为(经交织的位序列112)已被伪随机交织,因此所述位将在一个轮次中分布在跳变120_1至120_n

hops

‑

1上(即,)。这意味着,对于每个跳变,应从(经交织的位序列112)取得取得个位。这可以由下式描述:

[0285][0286]

其中,

[0287]

n

bits/chunk/hop

=n

bits/chunk

/n

hops

大致为每一跳变上从每一分块发送的位计数,

[0288]

是在每一跳变上从映射的位的数目,

[0289]

i=0,

…

,n

hops

‑

1是跳变索引,以及

[0290]

是内的位索引。

[0291]

在实施例中,第二交织器级108可以被配置为基于以下语法(例如,通过执行以下伪码)对第一分块110_1与经交织的位序列112进行交织:

[0292][0293][0294]

其中i表示控制变量,其中j表示控制变量,其中k表示控制变量,其中n

chunks

表示将所述经ldpc编码的位序列分段而成的分块的数目,其中n

hops

表示在其上分布所述经ldpc编码的位序列的所述经交织版本的子数据分组的数目,其中表示每轮次取自所述第一分块且被分布在所述多个子数据分组上的位的数目,其中n

bits/hop

表示每子数据分组的位的数目,其中表示所述经ldpc编码的位序列的经交织版本,其中ch1表示所述第一分块,其中表示所述经交织的位序列(例如,所述一个或多个其他分块的经交织版本(级联版本))。

[0295]

2.解交织器

[0296]

图12示出根据本发明的实施例的用于对经ldpc编码的位序列的经交织版本进行解交织的解交织器140的示意性方块图。解交织器140包括第一解交织器级142、第二解交织器级144以及级联级146。

[0297]

第一解交织器级142可以被配置为对经ldpc编码的位序列的经交织版本116逐块解交织,以获得第一分块110_1以及经交织的位序列112,诸如一个或多个其他分块或者两个或者更多个其他分块的级联版本的经交织版本。

[0298]

由此,第一分块110_1由第一类型的位组成,其中所述第一类型的位是以下至少一种情况:

[0299]

‑

是所述经ldpc编码的位序列的错误校正位,

[0300]

‑

是所述经ldpc编码的位序列的重复累积位,

[0301]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点(例如,所述变量节点中的每一个连接至两个连续校验节点),以所述经ldpc编码的位序列的坦纳图表示来表示。

[0302]

第二解交织器级144可以被配置为对经交织的位序列112进行解交织,以获得一个或多个其他分块,诸如第零分块110_0以及视需要第二分块110_2。

[0303]

级联级146可以被配置为将第一分块110_1与一个或多个其他分块级联,诸如第零分块110_0以及视需要第二分块110_2,以获得经ldpc编码的位序列102。

[0304]

如图12中所示,第一分块110_1绕过第二解交织器级144,或者换句话讲,第一分块110_1不由第二解交织器级144解交织。

[0305]

在实施例中,一个或多个其他分块中的一个分块(诸如第零分块110_0)由第二类型的位组成,其中第二类型的位是以下至少一种情况:

[0306]

‑

是所述经ldpc编码的位序列的信息位,和/或

[0307]

‑

通过包括至错误校正校验节点的伪随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0308]

在实施例中,所述其他分块中的另一分块(诸如第二分块110_2)由第一类型的位组成(例如,仅包括第一类型的位),即,是以下至少一种情况:

[0309]

‑

是经ldpc编码的位序列102的错误校正位,

[0310]

‑

是经ldpc编码的位序列102的重复累积位,

[0311]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点[例如,所述变量节点中的每一个连接至两个连续校验节点],以经ldpc编码的位序列102的坦纳图表示来表示。

[0312]

在实施例中,第一解交织器级142可以是逐块解交织器。举例而言,第一解交织器级142可以与第二交织器级108(见图2)互补。

[0313]

在实施例中,第二解交织器级144可以是伪随机解交织器,诸如基于线性反馈移位寄存器的解交织器或者逐块解交织器。

[0314]

3.迭代解码器

[0315]

图13示出根据本发明的实施例的迭代解码器的示意性方块图。迭代解码器204包括信道估计器、上述解交织器140、ldpc解码器214以及上述交织器100。

[0316]

换句话讲,图11描绘经交织ldpc码字116的迭代解码器204的方块图。在接收器侧处接收的信号包括所发送信号的衰落版本,所发送信号包括前置码210以及经交织ldpc码字116。前置码210馈送至信道估计器212,所述信道估计器又产生第一d

l

衰落系数的估计。其余n

‑

d

l

个系数仍不明确。所接收的码字116以及部分估计的衰落向量两者皆经解交织(例

如,通过解交织器140),以及被馈送至ldpc解码器214,所述ldpc解码器计算与所估计的系数对应的码元的先验llr,同时将其余系数视为抹除项。这些先验llr触发ldpc的置信度传播解码。

[0317]

由于交织器100破坏了ldpc码字102的阶梯结构,因此即使只有d

l

个可用的估计衰落系数,ldpc解码器214仍然可以被触发。这导致初步解码的向量,其充当用于信道估计212的额外导频信号。接着,通过对部分解码向量进行交织并将其与原始前置码一起传递回信道估计器212来触发另一解码迭代。结果,可以估算出具有2d

l

个衰落系数的较长分块。将新估计的衰落向量再解交织一次,并传递至ldpc解码器214,从而使其能够解码所接收码字的较大分块。迭代地重复此过程,直至所接收码字的所有n个位被解码为止。

[0318]

图14示出根据本发明的实施例的解码方法900的流程图。

[0319]

在第一步骤902中,提供输入,其中所述输入包括参考导频序列(例如,前置码)p

ref

、所接收的导频序列(例如,前置码)p

rec

、码率r、经ldpc编码的位序列的位(例如,信息位 冗余位)的数目n,以及在迭代i,

…

,n

iter

‑

1处的估计系数的数目d

l

。

[0320]

在第二步骤904中,基于等式n

iter

=n/d

l

判定迭代次数n

iter

,将衰落估计向量初始化为零,将经解码码字初始化为零,

[0321]

在第三步骤906中,将控制变量i设置为零,i=0。

[0322]

在第四步骤908中,基于等式来估计衰落估计向量

[0323]

在第五步骤910中,更新衰落估计向量以便包括使得使得

[0324]

在第六步骤912中,以及r两者经解交织且馈送至ldpc解码器,其中ldpc解码器首先计算先验llr,以及接着触发置信度传播算法以尝试部分地解码所接收的码字,先计算先验llr,以及接着触发置信度传播算法以尝试部分地解码所接收的码字,

[0325]

在第七步骤914中,更新参考前置码以包括经交织的经解码ldpc分块,

[0326][0327]

在第八步骤916中,更新参考前置码的所接收版本以包括经解码ldpc分块的衰落的接收版本,p

rec

=[p

rec

r(i

×

d

l

:((i 1)

×

d

l

)

‑

1)]。

[0328]

在第九步骤918中,将控制变量i增大一,i=i 1。

[0329]

在第十步骤920中,校验控制变量i是否小于所判定的迭代次数n

iter

,以及如果是,则以第四步骤908继续,否则以第十一步骤922继续。

[0330]

在第十一步骤922中,将经解码码字提供为输出。

[0331]

换句话讲,在图14中说明解码机制的详细描述。在第一解码迭代中,将前置码初始化为所接收的前置码序列,以及将衰落估计向量以及经解码码字两者初始化为零。令表示在迭代i,

…

,n

iter

‑

1处的d

l

个估计系数的向量,其中n

iter

为解码迭代的数目。更新估计向量以使其包括使得:

[0332][0333]

此后,对以及r两者进行解交织且将其馈送至ldpc解码器214。解码器首先计算先验llr,以及接着触发置信度传播算法,以尝试对所接收码字进行部分解码。

[0334]

在每一迭代之后,更新参考前置码及其所接收版本两者以分别包括经交织的经解码ldpc分块及其衰落的接收版本。这可以通过下式描述:

[0335][0336][0337]

其中

[0338]

ξ(x)、ξ

‑1(x)分别对应于向量x的经交织版本以及解交织版本,

[0339]

ξ(x(a:b))、ξ

‑1(x(a:b))分别对应于x的经交织以及解交织版本的第a索引至第b索引的值。

[0340]

p

ref

以及p

rec

分别表示参考以及所接收的前置码。

[0341]

3.其他实施例

[0342]

图15示出根据本发明的实施例的用于对经ldpc编码的位序列进行交织的方法300的流程图。方法300包括步骤302:将经ldpc编码的位序列分段为多个分块,所述多个分块包括第一分块以及一个或多个其他分块,其中所述多个分块中的第一分块由第一类型的位组成,其中第一类型的位

[0343]

‑

是所述经ldpc编码的位序列的错误校正位,

[0344]

‑

是所述经ldpc编码的位序列的重复累积位,和/或

[0345]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0346]

另外,方法300包括步骤304:对所述一个或多个其他分块或者其级联版本进行交织,以获得经交织的位序列。另外,方法300包括步骤303:对所述多个分块中的所述第一分块以及所述经交织的位序列逐块交织,以获得所述经ldpc编码的位序列的经交织版本。

[0347]

图16示出根据本发明的实施例的用于对经ldpc编码的位序列的经交织版本进行解交织的方法320的流程图。方法320包括步骤322:对经ldpc编码的位序列的经交织版本逐块解交织,以获得第一分块以及一个或多个其他分块的经交织版本,其中所述多个分块中的第一分块由第一类型的位组成,其中第一类型的位

[0348]

‑

是所述经ldpc编码的位序列的错误校正位,

[0349]

‑

是所述经ldpc编码的位序列的重复累积位,和/或

[0350]

‑

通过包括与至少两个错误校正校验节点的非随机连接的变量节点,以所述经ldpc编码的位序列的坦纳图表示来表示。

[0351]

另外,方法320包括步骤324:对所述一个或多个其他分块的所述经交织版本进行解交织,以获得所述一个或多个其他分块。另外,方法320包括步骤326:将所述第一分块与所述一个或多个其他分块级联,以获得所述经ldpc编码的位序列。

[0352]

随后,描述本发明的其他实施例,其可以单独地或者与本专利申请中描述的实施例中的任一个组合地实施。

[0353]

实施例提供用于展现阶梯式节点分布的ldpc码(诸如针对即将到来的ieee 802.15.4w[1]所提出的码以及dvb

‑

ngh标准中所采用的码)的混合交织器。所述交织器使得有可能提供额外导频码元至信道估计器以便提供决策指导信道估计(ddce)方法[2]。所述交织器将ldpc码字分解为n_chunks个分块。其始于标志阶梯结构的开始的分块。此阶梯分块以逐块方式分布于跳变上。此后,随机地交织其余n

chunks

‑

1个分块,以及将其放置在跟随在逐块交织阶梯位之后的跳变上。根据实施例的混合逐块随机交织器的本质在于即使在存在有限数目个估计衰落系数时也能使用新结构化ldpc码字来触发置信度传播(bp)解码算法。这意味着,ldpc解码器将仍能够解码一些位。这些位将充当额外导频码元,其可以连同原始前置码序列一起反馈至信道估计器。这又将允许侦测将反馈至ldpc解码器的额外衰落系数。在ldpc解码器与决策指导信道估计器之间来回遍历信息的过程将继续,直至解码整个ldpc码字为止。

[0354]

实施例以码率r≤1/2重构展现阶梯结构的ldpc码的坦纳图。

[0355]

实施例以最大化ldpc码字的解码能力(例如,即使具有有限数目个估计衰落系数)的方式对ldpc码字进行重新排序。

[0356]

实施例对ldpc位进行排序,使得最初估计的衰落系数将满足ldpc解码器的最小触发阈值值。

[0357]

实施例增大使校验节点具有从其对应变量节点接收的仅一个已抹除llr的机率。

[0358]

实施例分解经编码码字的阶梯结构。

[0359]

实施例在跳变上分布非阶梯式系统性信息位。

[0360]

实施例间接地跨码字扰乱首先估计的衰落系数(例如,而非将其堆叠在一个分块中)。

[0361]

实施例在估计衰落系数的数目有限的情况下允许ldpc的置信度传播解码算法的可行性。

[0362]

实施例将ldpc经解码位分配为充当额外导频码元,其可以连同原始前置码序列一起反馈至信道估计器。

[0363]

实施例允许侦测将反馈至ldpc解码器的额外衰落系数。

[0364]

实施例在ldpc解码器与决策指导信道估计器之间来回地遍历信息。

[0365]

实施例促进以相对短的前置码序列增强信道估计。

[0366]

实施例消除发送长的非数据前置码序列来确保特定可靠性阈值值的需求。

[0367]

与传统导频辅助信道估计相比,在满足相同可靠性等级的情况下,实施例相对增强有效数据速率。

[0368]

与传统导频辅助信道估计相比,在采用相同前置码大小的情况下,实施例替代地提供较高等级的稳健性。

[0369]

在实施例中,交织器(例如,混合逐块随机交织器)涉及四个阶段(或者块):(1)分段、(2)级联、(3)伪随机交织,以及(4)逐块交织。

[0370]

在实施例中,划分分块区长度为n位的码字v为输入,以及输出n

chunks

个分块,个分块,其n

chunks

=1/r,以及r=k/n为码率,其中每一分块具有从v连续获取的n

bits/chunk

=n/n

chunks

个位,其中每一分块ch

i

由下式给出:

[0371][0372]

在实施例中,级联器将取ch

i

,

…

,n

chunks

‑

1,i≠1,并将其级联为长度为(n

chunks

‑

1)

×

n

bits/chunk

的一个复合向量其中级联向量由下式给出:

[0373][0374]

在实施例中,随机交织器获取由lfsr产生的置换向量π以及级联向量其中随机交织器产生经交织向量其中根据π中的置换索引完成来自的元素至的映射,使得:

[0375][0376]

其中l=(n

chunks

‑

1)

×

n

bits/chunk

为级联向量的长度。

[0377]

在实施例中,ch1以及两者馈送至逐块交织器,从而产生输出向量其对应于ldpc经编码向量v的经交织版本。交织器在n

hops

上循环,为每一跳变分配n

bits/hop

个位。其首先始于在个轮次中将来自ch1的个位映射至每一跳变上。这可以由下式表示:

[0378][0379]

其中,

[0380]

n

hops

为跳变的数目,

[0381]

n

bits/hop

=n/n

hops

是在每一跳变上发送的位的数目,

[0382]

是每轮次从ch1映射于每一跳变上的位的数目,

[0383]

是耗尽ch1的所有位所需的轮次的总数,

[0384]

i=0,

…

,n

hops

‑

1是跳变索引,

[0385]

j=0,

…

,

‑

1是轮次内的位索引,以及

[0386]

k=0,

…

,

‑

1是轮次索引。

[0387]

在实施例中,在之后,每一跳变将具有来自ch1的个位。每一跳变上的其余n

bits/hop

个位应在一个轮次中取自这意味着,对于每个跳变,应依次从取得个位。这可以由下式描述:

[0388][0389]

其中,

[0390]

n

bits/chunk/hop

=n

bits/chunk

/n

hops

大致是每一跳变上从每一分块发送的位计数,

[0391]

是在每一跳变上从映射的位的数目,

[0392]

i=0,

…

,n

hops

‑

1是跳变索引,以及

[0393]

是内的位索引。

[0394]

其他实施例提供一种用于对经ldpc编码的位序列进行交织以获得经ldpc编码的位序列的经交织版本的交织器,其中所述交织器被配置为基于以下语法(例如,通过执行以下伪码)对经ldpc编码的位序列进行交织:

[0395]

[0396][0397]

其中i表示控制变量,其中j表示控制变量,其中n表示所述经ldpc编码的位序列的位(例如,信息位 冗余位)的数目,其中k表示控制变量,其中r表示码率,其中n

chunks

表示将经ldpc编码的位序列分段而成的分块的数目,其中n

hops

表示在其上分布所述经ldpc编码的位序列的所述经交织版本的子数据分组的数目,其中表示分布所述第一分块的位所需的轮次的数目,其中表示每轮次取自第一分块且被分布在多个子数据分组上的位的数目,其中n

bits/hop

表示每子数据分组的位的数目,其中n

bits/chunk

表示每分块的位的数目,其中n

bits/chunk/hop

表示每跳变每分块的位的数目,其中v表示所述经ldpc编码的位序列,其中表示所述经ldpc编码的位序列的经交织版本,其中ch

i

表示所述多个分块中的每一个,其中ch1表示所述第一分块,其中表示所述经交织的位序列(例如,所述一个或多个其他分块的经交织版本(级联版本))。

[0398]

信道估计是成功解码ldpc码字的关键因素。为了提供足够的信道估计,需要长前置码序列。这又降低了有效数据速率。而另一方面,如果插入短前置码,则ldpc解码器将缺少足够数目的估计衰落系数。结果,ldpc解码器会将对应于非估计系数的码元视为抹除项。因此,此将致使不可能触发ldpc解码器。

[0399]

实施例提供旨在解决速率

‑

可靠性取舍困境的混合交织器。所述混合交织器处理展现阶梯式节点结构的ldpc码,诸如针对即将到来的ieee 802.15.4w所提出的码以及dvb

‑

ngh标准中所采用的码。其目的是以最大化其解码能力(即使估计衰落系数有限)的方式重构ldpc码字。交织器将ldpc码字分解为n

chunks

个分块。其始于标志阶梯结构的开始的分块。此阶梯分块以逐块方式分布在跳变上。此后,其余的(n

chunks

‑

1)个分块被伪随机交织,且被放置于跟随在逐块交织的阶梯位之后的跳变上。

[0400]

根据实施例的混合逐块随机交织器的本质在于即使在存在有限数目个估计衰落系数时也能使用新结构化ldpc码字来触发bp解码算法。这意味着,ldpc解码器将仍能够解码一些位。这些位将充当额外导频码元,其可以连同原始前置码序列一起反馈至信道估计器。这又将允许侦测将反馈至ldpc解码器的额外衰落系数。在ldpc解码器与决策指导信道估计器之间来回遍历信息的过程将继续,直至解码整个ldpc码字为止。

[0401]

其他实施例提供一种用于对经ldpc编码的码字进行交织的交织器(100),所述经ldpc编码的码字包括具有736个经fec编码位(fec=前向错误校正,forward error correction)的位序列z(102)。

[0402]

ldpc编码器的单个码字(102)的736个fec编码位的序列z应分段为4个相等大小的分块c

i

:

[0403]

z={c0,c1,c2,c3}={z0,z1,z2,....,z

735

},

[0404]

c

i

={z

i

·

184

,z

i

·

184 1

,z

i

·

184 2

,...,z

(i 1)

·

184

‑1}。

[0405]

应从序列移除第二分块c1(110_1)[例如,四个分块110_0至110_3的序列的编号二分块在本文中指定为第一分块110_1(例如与图2比较)]。其余序列y(111)[例如,(三个其他分块110_0、110_2以及110_3(的级联版本),即,编号一分块、编号二分块以及编号四分块(例如与图2比较)]由下式给出:

[0406]

y={c0,c2,c3}={y0,y1,y2,....,y

551

}

[0407]

序列y(111)应使用扰乱向量u进行伪随机扰乱,所述扰乱向量u是从由10位伽罗瓦lfsr以生成多项式g(x)=x

10

x7 1产生的伪随机序列v导出。迭代0处的lfsr移位寄存器(107)的初始值应为v0=469,其中lfsr(107)的反馈输出表示最低有效位。在迭代0时处于初始状态的lfsr(107)示出于图17中。

[0408]

通过再次迭代移位寄存器来导出迭代v

i 1

的值。如果lfsr的此迭代的值超过552,则将跳过所述值,以及再次迭代lfsr,直至所述值不超过552。接着将所述值分配给v

i 1

。

[0409]

表1中给出v的第一值的示例:

[0410]

表1 扰乱向量产生的示例

[0411]

lfsr迭代lfsr值(区间)lfsr值(位)有效性分配给v046901 1101 0101是v0168210 1010 1010否

‑

234101 0101 0101是v1374610 1110 1010否

‑

437301 0111 0101是v25

…………

[0412]

向量u由u

i

=v

i

‑

1给出,以及y的扰乱版本y’(112)[例如,经交织的位序列112]由下式给出:

[0413][0414]

第二分块c1(110_1)应通过取决于索引n分配分块的每一位c

n

、无线电突发索引l以及在无线电突发中的位置i来分布在l个无线电突发[例如,子数据分组]上。

[0415][0416][0417]

其中n∈{0,1,2...183},其中n=0指代c1的第一位c0。

[0418]

y’(112)的位[例如,经交织的位序列112]应取决于索引m来分配无线电突发索引l以及位置i,如下:

[0419][0420]

i(m)=8 (m mod 24),

[0421]

其中m∈{0,1,2...551},其中m=0指代y’的第一位y

’0。

[0422]

在两种情况下,i=0皆是指无线电突发有效负载的第一位。如果发送多个码字,则用于下一码字的i=0是指在已被放置的位之后的第一位。

[0423]

尽管已在装置的上下文中描述一些方面,但显然,这些方面也表示对应方法的描述,其中块或者设备对应于方法步骤或者方法步骤的特征。类似地,在方法步骤的上下文中所描述的方面也表示对应块或者项目或者对应装置的特征的描述。可以由(或者使用)硬件设备(比如微处理器、可编程计算机或者电子电路)执行方法步骤中的一些或者全部。在一些实施例中,可以由此设备执行最重要的方法步骤中的某一个或者多者。

[0424]

取决于某些实施要求,本发明的实施例可以在硬件或者软件中实施。实施可以使用数字存储媒体来执行,所述媒体例如软性磁盘、dvd、blu

‑

ray、cd、rom、prom、eprom、eeprom或者闪存,所述媒体上存储有电子可读控制信号,所述电子可读控制信号与可编程计算机系统协作(或者能够协作),使得执行各个方法。因此,数字存储媒体可以是计算机可读的。

[0425]

根据本发明的一些实施例包括具有电子可读控制信号的数据载体,其能够与可编程计算机系统协作,使得执行本文中所描述的方法中的一个。

[0426]

通常,本发明的实施例可以实施为具有程序代码的计算机程序产品,当计算机程序产品在计算机上执行时,程序代码操作性地用于执行所述方法中的一个。程序代码可以例如存储于机器可读载体上。

[0427]

其他实施例包括存储于机器可读载体上,用于执行本文中所描述的方法中的一个的计算机程序。

[0428]

换句话讲,本发明方法的实施例因此是计算机程序,其具有用于在计算机程序于计算机上执行时执行本文中所描述的方法中的一个的程序代码。

[0429]

因此,本发明方法的进一步实施例为数据载体(或者数字存储媒体,或者计算机可读媒体),包括记录于其上的用于执行本文中所描述的方法中的一个的计算机程序。数据载体、数字存储媒体或者所记录媒体通常是有形的和/或非暂时性的。

[0430]

因此,本发明的方法的进一步实施例是表示用于执行本文中所描述的方法中的一

个的计算机程序的数据流或者信号序列。数据流或者信号序列可以例如被配置为经由数据通讯连接(例如,经由因特网)而传送。

[0431]

进一步实施例包括处理构件,例如被配置为或者经适配以执行本文中所描述的方法中的一个的计算机或者可编程逻辑装置。

[0432]

进一步实施例包括计算机,其上安装有用于执行本文中所描述的方法中的一个的计算机程序。

[0433]

根据本发明的进一步实施例包括被配置为(例如,电子地或者光学地)传送用于执行本文中所描述的方法中的一个的计算机程序至接收器的设备或者系统。举例而言,接收器可以为计算机、列动设备、内存设备等等。装置或者系统可以(例如)包括用于传送计算机程序至接收器的文件服务器。

[0434]

在一些实施例中,可编程逻辑装置(例如,场可编程门阵行)可用以执行本文中所描述的方法的功能性中的一些或者全部。在一些实施例中,场可编程门阵行可以与微处理器协作,以便执行本文中所描述的方法中的一个。通常,所述方法较佳地由任何硬件设备来执行。

[0435]

本文中所描述的装置可以使用硬件设备或者使用计算机或者使用硬件设备与计算机的组合来实施。

[0436]

本文中所描述的装置或者本文中所描述的装置的任何元件可以至少部分地以硬件和/或以软件来实施。

[0437]

本文中所描述的方法可以使用硬件设备或者使用计算机或者使用硬件设备与计算机的组合来进行。

[0438]

本文中所描述的方法或者本文中所描述的装置的任何元件可以至少部分地由硬件和/或软件执行。

[0439]

上述实施例仅说明本发明的原理。应理解,对本文中所描述的配置以及细节的修改以及变化将对本领域技术人员显而易见。因此,其仅意欲由接下来的权利要求的范畴限制,而非由通过本文中实施例的描述解释所呈现的特定细节限制。

[0440]

参考文献

[0441]

[1]ieee p802.15.4w low power wide area

[0442]

[2]de 10 2018 206 132

[0443]

[3]s.kobayashi,n.loghin,r.ikegaya,“proposal

‑

of

‑

ldpc

‑

low

‑

density

‑

parity

‑

code

‑

for

‑

lpwa”,15

‑

18

‑

0289

‑

01

‑

004w

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。