1.本发明涉及一种时脉闸控单元(clock gating cell,cgc),且特别涉及一种适用于扫描链(scan chain)的时脉闸控单元。

背景技术:

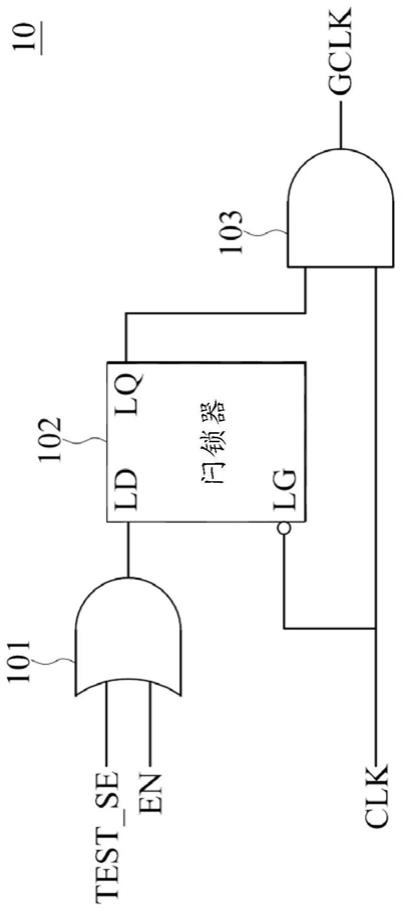

2.扫描链是可测试性设计的一种实现技术,它应用在扫描测试(scan testing)模式下检测组合逻辑电路中的各种故障(fault)。通常,扫描链是由组合逻辑电路与至少一正反器(flip-flop)所串联组成,且输入正反器的时脉信号可由时脉闸控单元所提供。举例来说,请参阅图1与图2,图1是现有时脉闸控单元的电路示意图,图2是图1的时脉闸控单元用于扫描链上的示意图。如图1所示,时脉闸控单元10包括或(or)闸101、闩锁器(latch)102和及(and)闸103。或闸101具有第一输入端与第二输入端分别接收测试致能信号test_se与时脉致能信号en,以及输出端耦接闩锁器102的资料输入端ld。

3.闩锁器102的时脉输入端lg则接收第一时脉信号clk经反相后的第二时脉信号clkb(图未绘示),且闩锁器102的资料输出端lq耦接及闸103的第一输入端。及闸103的第二输入端则接收第一时脉信号clk,并利用其输出端输出闸控时脉信号gclk,以作为输入正反器12的时脉信号。也就是说,如图2所示,正反器12的时脉输入端ck耦接及闸103的输出端,或者称作时脉闸控单元10的输出端。另外,正反器12的资料输入端d耦接组合逻辑电路14。然而,在扫描测试模式下,除了扫描样本(scan pattern)要满足测试条件以输入正反器12的资料输入端d外,扫描链1也要同时满足时脉闸控单元10的致能条件,否则将无法进行扫描测试。因此,如何设计出一种更适用于扫描链1的时脉闸控单元则成为本领域的一项重要课题。

技术实现要素:

4.有鉴于此,本发明实施例提供一种时脉闸控单元,包括选择器、第一闩锁器、或闸和第一及闸。选择器具有第一输入端与第二输入端分别接收时脉致能信号与扫描输入信号、选择端接收测试致能信号,以及输出端用来输出时脉致能信号或扫描输入信号。第一闩锁器具有时脉输入端接收第一时脉信号经反相后的第二时脉信号、资料输入端耦接选择器的输出端,以及资料输出端用来输出闩锁信号。或闸具有第一输入端、第二输入端与第三输入端分别接收测试旁通信号、测试致能信号与闩锁信号,以及输出端用来输出测试旁通信号、测试致能信号与闩锁信号所经逻辑或后的运算结果。第一及闸则具有第一输入端耦接或闸的输出端、第二输入端接收第一时脉信号,以及输出端用来输出闸控时脉信号。

5.优选地,时脉闸控单元更包括第二及闸和第二闩锁器。第二及闸具有第一输入端与第二输入端分别接收第一时脉信号与测试模式信号,以及输出端用来输出第一时脉信号与测试模式信号所经逻辑与后的运算结果。第二闩锁器则具有时脉输入端耦接第二及闸的输出端、资料输入端耦接第一闩锁器的资料输出端,以及资料输出端用来输出扫描输出信号。

6.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

7.图1是现有时脉闸控单元的电路示意图。

8.图2是图1的时脉闸控单元用于扫描链上的示意图。

9.图3是本发明实施例所提供的时脉闸控单元的电路示意图。

10.图4是图3的时脉闸控单元用于功能模式下的时序图。

11.图5a是图3的时脉闸控单元用于扫描测试模式下,但测试旁通信号被固定在低位准的时序图。

12.图5b是图3的时脉闸控单元用于扫描测试模式下,但测试旁通信号被固定在高位准的时序图。

具体实施方式

13.以下是通过特定的具体实施例来说明本发明的实施方式,本领域技术人员可由本说明书所提供的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不悖离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所提供的内容并非用以限制本发明的保护范围。

14.应当可以理解的是,虽然本文中可能会使用到“第一”、“第二”、“第三”等术语来描述各种元件或者信号,但这些元件或者信号不应受这些术语的限制。这些术语主要是用以区分一元件与另一元件,或者一信号与另一信号。另外,本文中所使用的术语“或”,应视实际情况可能包含相关联的列出项目中的任一个或者多个的组合。

15.请参阅图3,图3是本发明实施例所提供的时脉闸控单元的电路示意图。时脉闸控单元30包括选择器301、第一闩锁器302、或闸303、第一及闸304、第二及闸305与第二闩锁器306。选择器301具有第一输入端与第二输入端分别接收时脉致能信号en与扫描输入信号test_si、选择端接收测试致能信号test_se,以及输出端用来输出时脉致能信号en或扫描输入信号test_si。在本实施例中,选择器301可较佳是以2选1数据多工器(multiplexer,mux)来实现,但本发明不以此为限制。因此,当选择器301的选择端收到测试致能信号test_se为低位准(0)时,选择器301则选择第一输入端(0)所收到的时脉致能信号en作为其输出端的输出。相反地,当选择器301的选择端收到测试致能信号test_se为高位准(1)时,选择器301则选择第二输入端(1)所收到的扫描输入信号test_si作为其输出端的输出。总而言之,选择器301是根据测试致能信号test_se来选择时脉致能信号en或扫描输入信号test_si作为其输出端的输出。

16.第一闩锁器302具有时脉输入端lg接收第一时脉信号clk经反相后的第二时脉信号(图未绘示,但本实施例可将第二时脉信号标记为clkb)、资料输入端ld耦接选择器301的输出端,以及资料输出端lq用来输出闩锁信号qs。也就是说,当第一闩锁器302的时脉输入端lg收到第二时脉信号clkb为高位准(1),即第一时脉信号clk为低位准(0)时,第一闩锁器

302就可直接将资料输入端ld所收到的时脉致能信号en或扫描输入信号test_si作为闩锁信号qs输出。另外,当第一闩锁器302的时脉输入端lg收到第二时脉信号clkb为低位准(0),即第一时脉信号clk为高位准(1)时,第一闩锁器302的资料输出端lq则输出为保持前一位准的闩锁信号qs。由于闩锁器的运作原理已为本技术领域中具有通常知识者所习知,因此有关第一闩锁器302的细节于此就不再多加赘述。

17.或闸303具有第一输入端、第二输入端与第三输入端分别接收测试旁通信号test_bypass、测试致能信号test_se与闩锁信号qs,以及输出端用来输出测试旁通信号test_bypass、测试致能信号test_se与闩锁信号qs所经逻辑或后的运算结果。第一及闸304则具有第一输入端耦接或闸303的输出端、第二输入端接收第一时脉信号clk,以及输出端用来输出闸控时脉信号gclk。因此,根据以上内容的教示,本技术领域中具有通常知识者应可理解到,在测试致能信号test_se为低位准(0)时,时脉闸控单元30就可只需利用选择器301、第一闩锁器302、或闸303与第一及闸304来进行时脉闸控的功能模式。举例来说,可请一并参阅图4,图4是图3的时脉闸控单元30用于功能模式下的时序图。

18.如图4所示,在功能模式下,测试致能信号test_se被固定在低位准(0),并在第一闩锁器302的时脉输入端lg收到第二时脉信号clkb为高位准(1),即第一时脉信号clk为低位准(0)的情况下,当第一闩锁器302的资料输入端ld收到时脉致能信号en为高位准(1)时,第一闩锁器302就可直接将高位准(1)的时脉致能信号en作为闩锁信号qs输出至或闸303。同时地,因为或闸303至少收到一个为高位准(1)的输入信号,所以或闸303的输出端就输出为高位准(1)的运算结果至第一及闸304,使得第一及闸304就能直接将第一时脉信号clk作为闸控时脉信号gclk输出。另外,当时脉致能信号en为低位准(0)时,时脉闸控单元30也就中止输出闸控时脉信号gclk。由于时脉闸控的运作原理已为本技术领域中具有通常知识者所习知,因此有关上述细节于此就不再多加赘述。

19.另一方面,请参阅回图3,第二及闸305具有第一输入端与第二输入端分别接收第一时脉信号clk与测试模式信号test_mode,以及输出端用来输出第一时脉信号clk与测试模式信号test_mode所经逻辑与后的运算结果。第二闩锁器306则具有时脉输入端lg耦接第二及闸305的输出端、资料输入端ld耦接第一闩锁器302的资料输出端lq,以及资料输出端lq用来输出扫描输出信号test_so。类似地,当第二闩锁器306的时脉输入端lg收到第二及闸305的输出为高位准(1),即第一时脉信号clk与测试模式信号test_mode皆为高位准(1)时,第二闩锁器306就可直接将资料输入端ld所收到的第一闩锁器302的闩锁信号qs作为扫描输出信号test_so输出。另外,当第二闩锁器306的时脉输入端lg收到第二及闸305的输出为低位准(0),即第一时脉信号clk与测试模式信号test_mode的至少一者为低位准(0)时,第二闩锁器306的资料输出端lq则输出为保持前一位准的扫描输出信号test_so。

20.也就是说,第一闩锁器302和第二闩锁器306可作为主(master)闩锁器和从属(slave)闩锁器,使得第一闩锁器302和第二闩锁器306组构成一正反器。因此,在这样的电路设计架构下,该正反器也就能利用第一时脉信号clk的正/负缘来储存输入端的值。相对地,时脉闸控单元30所内含选择器301就是为了可选择使正反器储存不同输入端的值。另外,由于扫描输出信号test_so可被用来检测第一闩锁器302的故障,所以该正反器更可作为一扫描正反器(scan flip-flop),或者是说时脉闸控单元30更包含扫描正反器的功能,使得时脉闸控单元30将能直接被串在图2的扫描链1上。由于正反器或扫描正反器的运作原

理已为本技术领域中具有通常知识者所习知,因此有关其细节于此就不再多加赘述。

21.另外,在测试模式信号test_mode被固定在高位准(1)时,第二及闸305就能直接将第一时脉信号clk输出至第二闩锁器306的时脉输入端lg。然而,由于在非扫描测试模式(例如,时脉闸控的功能模式)下却不需用到扫描输出信号test_so,所以这时候测试模式信号test_mode将可被固定在低位准(0),使得第二及闸305中止输出第一时脉信号clk至第二闩锁器306,或者是说强制关掉没有用到的储存单元(即第二闩锁器306),以达到省电的效果。总而言之,不同于测试旁通信号test_bypass,本实施例是多设计一独立信号(即测试模式信号test_mode)来控制第二及闸305是否输出第一时脉信号clk。至于这么做的好处也是在扫描测试模式下,本实施例可直接控制测试旁通信号test_bypass,例如将测试旁通信号test_bypass直接接上测试机台的控制端。然而,有关测试旁通信号test_bypass的细节将在下文中借由其它段落做说明,故于此就先不再多加赘述。

22.然后,为了更进一步说明有关时脉闸控单元30用于扫描测试模式下的运作流程,请一并参阅图5a和图5b,图5a是图3的时脉闸控单元30用于扫描测试模式下,但测试旁通信号test_bypass被固定在低位准(0)的时序图,而图5b是图3的时脉闸控单元30用于扫描测试模式下,但测试旁通信号test_bypass被固定在高位准(1)的时序图。

23.如图5a所示,在扫描测试模式下,测试模式信号test_mode被固定在高位准(1),使得第二及闸305直接将第一时脉信号clk输出至第二闩锁器306的时脉输入端lg。另外,扫描测试模式可分为扫描移位(scan shift)期间和扫描撷取(scan capture)期间。在扫描移位期间,测试致能信号test_se被固定在高位准(1),并当选择器301的选择端收到测试致能信号test_se为高位准(1)时,选择器301则选择扫描输入信号test_si作为其输出端的输出,而这时候时脉闸控单元30将不受时脉致能信号en的影响。因此,这时候的时脉致能信号en可用以斜线框区域来表示其波形,并当第一时脉信号clk为低位准(0)时,第一闩锁器302直接将扫描输入信号test_si作为闩锁信号qs输出,而当第一时脉信号clk为高位准(1)时,第一闩锁器302则输出为保持前一位准的闩锁信号qs。

24.同时地,当第一时脉信号clk为高位准(1)时,第二闩锁器306直接将闩锁信号qs作为扫描输出信号test_so输出,而当第一时脉信号clk为低位准(0)时,第二闩锁器306则输出为保持前一位准的扫描输出信号test_so。然而,因为这时候的或闸303至少收到一个为高位准(1)的输入信号(即测试致能信号test_se),所以第一及闸304直接将第一时脉信号clk作为闸控时脉信号gclk输出。

25.接著,在扫描撷取期间,测试致能信号test_se被固定在低位准(0),并当选择器301的选择端收到测试致能信号test_se为低位准(0)时,选择器301则改选择时脉致能信号en作为其输出端的输出,而这时候时脉闸控单元30将不受扫描输入信号test_si的影响。因此,这时候的扫描输入信号test_si可用以斜线框区域来表示其波形,并当第一时脉信号clk为低位准(0)时,第一闩锁器302直接将低位准(0)的时脉致能信号en作为闩锁信号qs输出,而当第一时脉信号clk为高位准(1)时,第一闩锁器302则输出为保持前一位准的闩锁信号qs。

26.同时地,当第一时脉信号clk为高位准(1)时,第二闩锁器306直接将闩锁信号qs作为扫描输出信号test_so输出,而当第一时脉信号clk为低位准(0)时,第二闩锁器306则输出为保持前一位准的扫描输出信号test_so。然而,因为这时候的或闸303没有收到任何一

个为高位准(1)的输入信号,所以第一及闸304中止输出闸控时脉信号gclk。由于后续细节已如同前述内容所述,故于此就不再多加赘述。总而言之,在扫描移位期间,测试致能信号test_se将可被固定在高位准(1),使得第一及闸304直接将第一时脉信号clk作为闸控时脉信号gclk输出。

27.另一方面,相较于图5a的扫描撷取期间,在图5b的扫描撷取期间,由于测试旁通信号test_bypass被固定在高位准(1),所以这时候的或闸303至少收到一个为高位准(1)的输入信号,使得第一及闸304直接将第一时脉信号clk作为闸控时脉信号gclk输出。也就是说,不同于现有技术,本实施例可设计两独立信号(即测试致能信号test_se和测试旁通信号test_bypass)来分别在扫描移位期间和扫描撷取期间强制导通第一及闸304输出第一时脉信号clk作为闸控时脉信号gclk。

28.或者是说,不同于测试模式信号test_mode,本实施例是多设计一独立信号(即测试旁通信号test_bypass)来在扫描撷取期间强制导通第一及闸304输出第一时脉信号clk。如前所述,这么做的好处是在扫描测试模式下,本实施例可直接控制测试旁通信号test_bypass,例如将测试旁通信号test_bypass直接接上测试机台的控制端。这样一来,当测试旁通信号test_bypass被控制为高位准(1)时,时脉闸控单元30就能强制将第一时脉信号clk作为闸控时脉信号gclk输出,以保证扫描链上所连到第一及闸304的正反器都能因收到时脉信号而正常进行描测测试。

29.相对地,如果没有测试旁通信号test_bypass,时脉闸控单元30就必须用扫描样本,将控制值透过扫描输入信号test_si输入至第一闩锁器302,这样才能强制将第一时脉信号clk作为闸控时脉信号gclk输出,但这么做也等于额外增加了「输出闸控时脉信号gclk」的扫描样本,即导致扫描样本增加。另外,不仅仅有测试旁通信号test_bypass外,本实施例还多利用另一独立信号(即测试致能信号test_se)来在扫描移位期间强制导通第一及闸304输出第一时脉信号clk,以保证扫描移位期间时脉信号不会被停掉,避免扫描移位期间因没有时脉信号而导致扫描样本无法正常输入。由于图5b的其它区间细节已如同前述内容所述,故于此就不再多加赘述。

30.综上所述,本发明实施例提供一种适用于扫描链的时脉闸控单元,包括两闩锁器可配置为正反器,以利用第一时脉信号的正/负缘来储存输入端的值,而且还包括选择器可选择使正反器储存不同输入端的值。另外,在非扫描测试模式下,所述时脉闸控单元可透过一独立信号来强制关掉没有用的闩锁器,以达到省电的效果,并在扫描测试模式的扫描移位期间和扫描撷取期间,所述时脉闸控单元更分别透过两独立信号来强制输出第一时脉信号作为闸控时脉信号。

31.以上所提供的内容仅为本发明的优选可行实施例,并非因此局限本发明的申请专利范围,所以凡是运用本发明说明书及图式内容所做的等效技术变化,均包含于本发明的申请专利范围内。

32.【符号说明】

33.1:扫描链

34.10,30:时脉闸控单元

35.12:正反器

36.14:组合逻辑电路

37.301:选择器

38.101,303:或闸

39.102,302,306:闩锁器

40.ld,d:资料输入端

41.lq,q:资料输出端

42.lg,ck:时脉输入端

43.103,304,305:及闸

44.test_bypass:测试旁通信号

45.en:时脉致能信号

46.test_si:扫描输入信号

47.test_se:测试致能信号

48.clk:第一时脉信号

49.gclk:闸控时脉信号

50.qs:闩锁信号

51.test_mode:测试模式信号

52.test_so:扫描输出信号

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。