一种数字与pwm复合控制器

技术领域

1.本发明涉及电子技术领域,特别涉及一种数字与pwm复合控制器。

背景技术:

2.当前ethercat总线激光方案中,若需要pwm信号控制激光器,则需要单独添加一个pwm模块;而现有模块中,基本都是将数字量输入输出,模拟量输入输出和高精度pwm输出分开设计为独立的电路模块;针对激光切割机床市场,各个模块独立分开,现场使用时接线比较麻烦,成本较高,模块之间传输信号时容易受到外部干扰的影响,抗干扰性也较差。

3.因而现有技术还有待改进和提高。

技术实现要素:

4.鉴于上述现有技术的不足之处,本发明的目的在于提供一种数字与pwm复合控制器,以解决现有数字量输入输出、模拟量输入输出和pwm输出的模块独立分开导致接线麻烦、干扰性较差的问题。

5.为了达到上述目的,本发明采取了以下技术方案:一种数字与pwm复合控制器,其包括模拟量传输模块、数字量传输模块、控制模块、编译码模块、手轮处理模块、pwm输出模块和通讯模块;所述控制模块连接模拟量传输模块、编译码模块、手轮处理模块、pwm输出模块和通讯模块;编译码模块连接手轮处理模块、模拟量传输模块和数字量传输模块;所述模拟量传输模块对外部输入的模拟量信号进行模数转换后传输给控制模块进行处理,监控信号传输状态并通过编译码模块反馈给控制模块;控制模块输出的模拟量输出信号通过模拟量传输模块进行数模转换后输出;所述数字量传输模块对外部输入的数字量信号进行隔离后,通过编译码模块传输给控制模块进行处理;控制模块输出的数字量输出信号通过编译码模块传输至模拟量传输模块,模拟量传输模块进行隔离后输出;所述编译码模块用于扩展控制模块的接口并进行信号传输;所述手轮处理模块将手轮数据通过编译码模块传输给控制模块,对手轮信号进行隔离后传输给控制模块,还对控制模块输出的手轮控制信号进行隔离后输出;所述pwm输出模块对控制模块输出的pwm控制信号进行隔离、电压转换、驱动后输出对应的pwm信号;所述通讯模块与上位机通讯连接,在控制模块与上位机之间进行数据传输。

6.所述的数字与pwm复合控制器中,所述模拟量传输模块包括模拟量输入单元和模拟量输出单元;所述模拟量输入单元连接模拟量输出单元和控制模块,模拟量输出单元连接编译码模块;所述模拟量输入单元对外部输入的模拟量信号进行滤波、放大、模数转换后传输给控制模块;

所述模拟量输出单元监控信号传输状态并通过编译码模块反馈给控制模块;控制模块输出的模拟量输出信号通过模拟量输出单元进行数模转换后输出。

7.所述的数字与pwm复合控制器中,所述模拟量输入单元包括第一接口、模拟量输入芯片、第一运放电路、第二运放电路、第三运放电路和第四运放电路;所述第一接口的第1脚、第2脚与第一运放电路第一输入脚、第二输入脚一对一连接;所述第一接口的第3脚、第4脚与第二运放电路的第一输入脚、第二输入脚一对一连接;所述第一接口的第5脚、第6脚与第三运放电路的第一输入脚、第二输入脚一对一连接;所述第一接口的第7脚、第8脚与第四运放电路的第一输入脚、第二输入脚一对一连接;第一接口的第9脚连接第10脚和屏蔽地;第一运放电路的第一输出脚、第二输出脚与模拟量输入芯片的ain_0p脚、ain_0gnd脚一对一连接;第二运放电路的第一输出脚、第二输出脚与模拟量输入芯片的ain_1p脚、ain_1gnd脚一对一连接;第三运放电路3的第一输出脚、第二输出脚与模拟量输入芯片的ain_2p脚、ain_2gnd脚一对一连接;第四运放电路的第一输出脚、第二输出脚与模拟量输入芯片的ain_3p脚、ain_3gnd脚一对一连接;模拟量输入芯片的avdd脚输入第一电压,模拟量输入芯片的dvdd脚输入第二电压,模拟量输入芯片的aux_in脚连接aux_gnd脚和模拟地;模拟量输入芯片的refio脚、refcap脚分别通过一电容接模拟地;模拟量输入芯片的脚、脚、alarm脚均连接控制模块;模拟量输入芯片的sclk脚、sdi脚、sdo脚连接模拟量输出单元和控制模块;模拟量输入芯片的rdfgnd脚、脚、agnd脚、da/sy脚、dgnd脚均接地。

8.所述的数字与pwm复合控制器中,所述模拟量输出单元包括第二接口、模拟量输出芯片、第五电阻、第六电阻、第一输出电路、第二输出电路、第三输出电路和第四输出电路;所述模拟量输出芯片的dvcc脚输入第三电压,模拟量输出芯片的脚接数字地;模拟量输出芯片的脚、脚和脚均连接控制模块;模拟量输出芯片的sclk脚连接模拟量输入芯片的sclk脚和控制模块,模拟量输出芯片的sdin脚连接模拟量输入芯片的sdi脚和控制模块,模拟量输出芯片的sdo脚连接模拟量输入芯片的sdo脚和控制模块,模拟量输出芯片的refin/refout脚通过一电容连接模拟量输出芯片的gnd脚和数字地,模拟量输出芯片的avdd脚输入第一电压;模拟量输出芯片的vouta脚、voutb脚、voutc脚、voutd脚与第一输出电路的第一输入脚、第二输出电路的第一输入脚、第三输出电路的第一输入脚、第四输出电路的第一输入脚一对一连接;模拟量输出芯片的avss脚、sig_gnd脚、dac_gnd脚和epad脚均连接模拟地;第一输出电路的第一输出脚、第二输出脚与第二接口的第10脚、第9脚一对一连接;第二输出电路的第一输出脚、第二输出脚与第二接口的第8脚、第7脚一对一连接;第三输出电路的第一输出脚、第二输出脚与第二接口的第6脚、第5脚一对一连接;第四输出电路的第一输出脚、第二输出脚与第二接口的第4脚、第3脚一对一连接;第二接口的第1脚连接第2脚和屏蔽地,第一输出电路至第四输出电路的第三输出脚均连接编译码模块;第五电阻的一端输入第一电压,第五电阻的另一端连接第六电阻的一端和各个输出电路的第二输入脚,第六电阻的另一端连接模拟地。

9.所述的数字与pwm复合控制器中,所述数字量传输模块包括第三接口、第四接口、第五接口、第六接口、第七接口、48个数字量输入单元、8个数字量输出单元和监控反馈单元;

所述第三接口的第1脚连接第一数字量输入单元的输入脚,第2脚连接第二数字量输入单元的输入脚,第三接口的第15脚连接第十六数字量输入单元的输入脚;第四接口的各个引脚对应连接第十七数字量输入单元至第三十二数字量输入单元的输入脚,第五接口的各个引脚对应连接第三十三数字量输入单元至第四十八数字量输入单元的输入脚,各个数字量输入单元的输出脚均连接编译码模块;第一数字量输出单元至第四数字量输出单元的各个输出脚均连接第六接口,第五数字量输出单元至第八数字量输出单元的各个输出脚均连接第七接口,各个数字量输出单元的输入脚均连接编译码模块。

10.所述的数字与pwm复合控制器中,所述控制模块包括主控芯片和烧录接口;所述主控芯片的pa0_wkup 脚、pa1脚和pd13脚均连接手轮处理模块;主控芯片的pa2脚、pa3脚、pa4脚、pa5脚、pa6脚、pa7脚、pc8脚和pc9脚均连接通讯模块;主控芯片的pa8脚和pd15脚均连接pwm输出模块;主控芯片的pa9脚、pa10脚、pa13/jtms/swdio脚与烧录接口的第2脚、第1脚、第5脚、第6脚一对一连接;主控芯片的pb8脚、pb9脚、pb12脚与模拟量输出芯片的脚、脚、脚一对一连接;主控芯片的pb10脚、pb11脚、pb13脚、pb14脚、pb15脚、pe15脚与模拟量输入芯片的脚、alarm脚、sclk脚、sdo脚、sdi脚、脚一对一连接;主控芯片的pc0脚至pc7脚、pd0脚至pd12脚、pe5脚均连接编译码模块。

11.所述的数字与pwm复合控制器中,所述编译码模块包括9个译码单元和4个锁存单元;各个译码单元和锁存单元均连接控制模块;第一译码单元至第七译码单元均连接数字量传输模块,用于对数字量传输模块输入的数字量信号进行译码后传输给控制模块;第八译码单元连接模拟量传输模块,用于对模拟量传输模块输出的监控信号进行译码后传输给控制模块;第九译码单元连接手轮处理模块,用于对手轮处理模块传输的手轮数据进行译码后传输给控制模块;第一锁存单元至第四锁存单元均连接控制模块和数字量传输模块,用于对控制模块输出的数字量输出信号进行锁存后输出给数字量传输模块。

12.所述的数字与pwm复合控制器中,所述手轮处理模块包括手轮接口、第三光耦、第四光耦、第五光耦、第六光耦、第四电阻器、第五电阻器、第十二电阻、第十三电阻、第七电容和第八电容;所述手轮接口的第1脚和第2脚输入第五电压,手轮接口的第9脚和第10脚连接隔离地;手轮接口的第3脚、第4脚、第5脚、第6脚与第三光耦的第1脚、第3脚、第5脚、第7脚一对一连接;手轮接口的第11脚、第12脚、第13脚、第7脚与第四光耦的第3脚、第5脚、第7脚、第1脚一对一连接;手轮接口的第14脚、第15脚与第六光耦的第1脚、第4脚一对一连接;手轮接口j1的第8脚连接第五光耦的e脚;第三光耦的第2脚、第4脚、第6脚、第8脚分别通过一指示灯接隔离地;第四光耦的第2脚、第4脚、第6脚、第8脚分别通过一指示灯接隔离地;第三光耦的第16脚、第14脚、第12脚、第10脚与第四电阻器的第1脚、第2脚、第3脚、第4脚一对一连接;第三光耦的第16脚连接第四电阻器的第1脚和第九译码单元中逻辑芯片的a1脚,第三光耦的第14脚连接第四电阻器的第2脚和第九译码单元中逻辑芯片的a2脚,第三光耦的第12脚连接第四电阻器的第3脚和第九译码单元中逻辑芯片的a3脚,第三光耦的第10脚连接第四

电阻器的第4脚和第九译码单元中逻辑芯片的a4脚,第四光耦的第16脚连接第五电阻器的第1脚和第九译码单元中逻辑芯片的a5脚,第四光耦的第14脚连接第五电阻器的第2脚和第九译码单元中逻辑芯片的a6脚,第四光耦的第12脚连接第五电阻器的第3脚和第九译码单元中逻辑芯片的a7脚,第四光耦的第10脚连接第五电阻器的第4脚和第九译码单元中逻辑芯片的a8脚,第四电阻器和第五电阻器的第5脚至第8脚均输入第四电压;第三光耦和第四光耦的第15脚、第13脚、第11脚、第9脚均接数字地;第五光耦的c脚输入第五电压,第五光耦的a脚输入第四电压,第五光耦的k脚连接主控芯片的pd13脚,第六光耦的第1脚连接第七电容的一端和第十三电阻的一端;第六光耦的第2脚连接第七电容的另一端、第十三电阻的另一端和屏蔽地;第六光耦的第4脚连接第八电容的一端和第十二电阻的一端;第六光耦的第3脚连接第八电容的另一端、第十二电阻的另一端和屏蔽地,第六光耦的第8脚输入第四电压,第六光耦的第7脚、第6脚与主控芯片的pa0

‑

wkup脚、pa1脚一对一连接;第六光耦的第5脚接数字地。

13.所述的数字与pwm复合控制器中,所述pwm输出模块包括输出电压隔离芯片、 第二驱动芯片、 第三驱动芯片、 第四驱动芯片、串口、第一瞬态抑制器、第二瞬态抑制器、第十四电阻和第十五电阻;所述输出电压隔离芯片的vcc1脚输入第四电压,输出电压隔离芯片的ina脚连接第十四电阻的一端和主控芯片的pd15脚,输出电压隔离芯片的inb脚连接第十五电阻的一端和主控芯片的pa8脚; 输出电压隔离芯片的gnd1脚连接第十四电阻的另一端、第十五电阻的另一端和数字地;输出电压隔离芯片的vcc2脚输入第六电压,输出电压隔离芯片的gnd2脚连接隔离地,输出电压隔离芯片的outa脚连接第二驱动芯片的ina脚和第四驱动芯片的in 脚,输出电压隔离芯片的outb脚连接第二驱动芯片的inb脚和第三驱动芯片的in 脚;第二驱动芯片的ena脚、enb脚、vdd脚均输入第六电压;第二驱动芯片的gnd脚接隔离地,第二驱动芯片的outa脚连接第一瞬态抑制器的第2脚和串口的第4脚,第二驱动芯片的outb脚连接第一瞬态抑制器的第1脚和串口的第5脚,第三驱动芯片和第四驱动芯片的en脚均输入第六电压,第三驱动芯片和第四驱动芯片的gnd脚均接隔离地,第三驱动芯片和第四驱动芯片的vdd脚均输入第五电压,第三驱动芯片的out脚连接第二瞬态抑制器的第2脚和串口的第1脚,第四驱动芯片的out脚连接第二瞬态抑制器的第1脚和串口的第2脚;第一瞬态抑制器的第3脚、第二瞬态抑制器的第3脚,串口的第6脚、第7脚、第3脚、第8脚和第9脚均连接隔离地;串口的外壳连接屏蔽地。

14.所述的数字与pwm复合控制器中,所述通讯模块包括通讯芯片、 第一esd保护管、第二esd保护管、第一网口、第二网口、第十六电阻、第十七电阻、第十八电阻、第十九电阻、第九电容、第十电容、第十一电容和第十二电容;所述通讯芯片的oe_ext/lrdn/sclk脚、outvld/lwrn/mosi脚、sof/lecsn/scs_esc脚、wd_trig/lint/sint脚、sync_latch[0]脚、sync_latch[1]脚、lat_in/lrdy/miso脚、eep_done脚与主控芯片的pa5脚、pa7脚、pa4脚、ap2脚、pc8脚、pc9脚、ap6脚、pa3脚一对一连接;通讯芯片的p0_txop脚连接第一网口的td 脚和第一esd保护管的io2脚,通讯芯片的p0_txon脚连接第一网口的td

‑

脚和第一esd保护管的io3脚,通讯芯片的p0_rxip脚连接第一网口的rd 脚和第一esd保护管的io4脚,通讯芯片的p0_rxin脚连接第一网口的rd

‑

脚和第一esd保护管的io1脚,通讯芯片的p0_act脚连接第一网口的led2_yellow 脚,第一网口的tdc

脚依次通过第十六电阻、第九电容接数字地,第一网口的rdc脚依次通过第十七电阻、第十电容接数字地,通讯芯片的p1_txop脚连接第二网口的td 脚和第一esd保护管的io2脚,通讯芯片的p1_txon脚连接第二网口的td

‑

脚和第二esd保护管的io3脚,通讯芯片的p1_rxip脚连接第二网口的rd 脚和第二esd保护管的io4脚,通讯芯片的p1_rxin脚连接第二网口的rd

‑

脚和第二esd保护管的io1脚,通讯芯片的p1_act脚连接第二网口的led2_yellow 脚,第二网口的tdc脚依次通过第十八电阻、第十一电容接数字地,第二网口的rdc脚依次通过第十九电阻、第十二电容接数字地。

[0015]

相较于现有技术,本发明提供的数字与pwm复合控制器,包括一壳体,所述壳体内设有一电路板,所述电路板上集成了模拟量传输模块、数字量传输模块、控制模块、编译码模块、手轮处理模块、pwm输出模块和通讯模块;所述控制模块连接模拟量传输模块、编译码模块、手轮处理模块、pwm输出模块和通讯模块;编译码模块连接手轮处理模块、模拟量传输模块和数字量传输模块;所述模拟量传输模块对外部输入的模拟量信号进行模数转换后传输给控制模块进行处理,监控信号传输状态并通过编译码模块反馈给控制模块;控制模块输出的模拟量输出信号通过模拟量传输模块进行数模转换后输出;所述数字量传输模块对外部输入的数字量信号进行隔离后,通过编译码模块传输给控制模块进行处理;控制模块输出的数字量输出信号通过编译码模块传输至模拟量传输模块,模拟量传输模块进行隔离后输出;所述编译码模块用于扩展控制模块的接口并进行信号传输;所述手轮处理模块将手轮数据通过编译码模块传输给控制模块,对手轮信号进行隔离后传输给控制模块,还对控制模块输出的手轮控制信号进行隔离后输出;所述pwm输出模块对控制模块输出的pwm控制信号进行隔离、电压转换、驱动后输出对应的pwm信号;所述通讯模块与上位机通讯连接,在控制模块与上位机之间进行数据传输。将数字量输入输出、模拟量输入输出和pwm输出模块集成在一起,与现有各种功能分开设计模块相比,各模块之间的连线由电路板布局来实现,大大减小了接线麻烦和信号传输时的外部干扰。

附图说明

[0016]

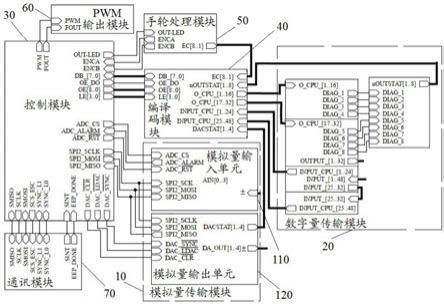

图1为本发明提供的数字与pwm复合控制器的结构框图。

[0017]

图2为本发明提供的模拟量输入单元的电路图。

[0018]

图3为本发明提供的模拟量输出单元的一部分电路图。

[0019]

图4为本发明提供的模拟量输出单元的另一部分电路图。

[0020]

图5为本发明提供的数字量传输模块的一部分电路图。

[0021]

图6为本发明提供的数字量传输模块的另一部分电路图。

[0022]

图7为本发明提供的第一数字量输入单元的电路图。

[0023]

图8为本发明提供的第一数字量输出单元的电路图。

[0024]

图9为本发明提供的监控反馈单元的电路图。

[0025]

图10为本发明提供的控制模块的电路图。

[0026]

图11为本发明提供的9个译码单元的结构框图。

[0027]

图12为本发明提供的4个锁存单元的结构框图。

[0028]

图13为本发明提供的第一译码单元的电路图。

[0029]

图14为本发明提供的第七译码单元的电路图。

[0030]

图15为本发明提供的第八译码单元的电路图。

[0031]

图16为本发明提供的第九译码单元的电路图。

[0032]

图17为本发明提供的第一锁存单元的电路图。

[0033]

图18为本发明提供的手轮处理模块的一部分电路图。

[0034]

图19为本发明提供的手轮处理模块的另一部分电路图。

[0035]

图20为本发明提供的pwm输出模块的电路图。

[0036]

图21为本发明提供的通讯模块的第一部分电路图。

[0037]

图22为本发明提供的通讯模块的第二部分电路图。

[0038]

图23为本发明提供的通讯模块的第三部分电路图。

具体实施方式

[0039]

本发明提供一种数字与pwm复合控制器。为使本发明的目的、技术方案及效果更加清楚、明确,以下参照附图并举实施例对本发明进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

[0040]

请参阅图1,本发明实施例提供的数字与pwm复合控制器(有壳体,所述壳体内设有一电路板,)设置在机床上,与上位机上的cnc系统通讯;所述电路板上集成了模拟量传输模块10、数字量传输模块20、控制模块30、编译码模块40、手轮处理模块50、pwm输出模块60和通讯模块70。所述控制模块30连接模拟量传输模块10、编译码模块40、手轮处理模块50、pwm输出模块60和通讯模块70;编译码模块40连接手轮处理模块50、模拟量传输模块10和数字量传输模块20。

[0041]

所述模拟量传输模块10对外部输入的模拟量信号进行模数转换后传输(通过spi总线传输)给控制模块30进行处理(处理方式为现有技术),监控信号传输状态(是否出现短路、过载或过热,dacstat[1..4]信号来传输)并通过编译码模块反馈给控制模块30;控制模块30控制需要输出的模拟量输出信号的电压(如0~10v),通过模拟量传输模块10进行数模转换后输出控制所接设备的工作状态(如高度、气体大小、比例阀、电机的转速、激光器的能量等)。

[0042]

所述数字量传输模块20对外部输入的数字量信号(24v)进行隔离后,通过编译码模块传输给控制模块30进行处理(处理方式为现有技术);控制模块30将需要输出的数字量输出信号db_[0..7]通过编译码模块传输至模拟量传输模块10,进行隔离后输出、控制所接设备的工作状态(如继电器的开断)。

[0043]

所述编译码模块40用于扩展控制模块30的接口并进行并口通讯。

[0044]

所述手轮处理模块50将外部输入的手轮数据通过编译码模块40传输给控制模块30,对手轮信号进行隔离后传输给控制模块30,还对控制模块30输出的手轮控制信号进行隔离后输出。

[0045]

所述pwm输出模块60对控制模块30输出的pwm控制信号(fout信号和pwm信号)进行隔离、电压转换、驱动后输出对应的pwm信号(fout5v信号、fout24v信号、pwm5v信号和pwm24v信号)。

[0046]

所述通讯模块70外接上位机,用于实现控制模块30与上位机的数据链路层通讯。

[0047]

具体实施时,例如,机床上的切割头与需要切割的钢板的距离不同,产生的电压也

不同(电压范围0~10v),切割头反馈的电压(如5v)即是一种模拟量信号,通过模拟量传输模块10进行模数转换后传输给控制模块30进行处理,控制模块30通过通讯模块70上传电压值给上位机上的cnc系统,cnc系统根据电压值即可判断当前的距离是否合适(太高切割不到,太低会烧坏钢板),cnc系统根据距离输出需要调节的轴的高度值,通过通讯模块70传输给控制模块30,控制模块30将高度值传输给模拟量传输模块10进行数模转换后输出对应的高度电压给轴,即可调节轴的高度。

[0048]

数字量信号与模拟量信号相似,只是输入路径是依次通过数字量传输模块20、编译码模块40、控制模块30再到通讯模块70,通过ethercat总线上传至上位机中进行处理;输出路径与输入路径相反。数字量信号用于实现其他的控制,如所有的开关由数字量信号来控制。

[0049]

模拟量传输模块10、数字量传输模块20、手轮处理模块50、pwm输出模块60和通讯模块70的输入输出没有先后顺序,只要外部有信号或需要输出,各个模块即可工作。

[0050]

本实施例与现有各模块分开独立设计相比,将各种功能集成在一电路板上,各个模块之间的连接是通过电路板上的走线连接。一个集成模块就能够完全解决所有的应用场景,而不需要多余的控制模块;还省去了现有独立的各模块之间连接所需要的连接线,大大减小了接线麻烦和信号传输时的外部干扰,节省成本的同时提高了抗干扰性。

[0051]

请一并参阅图2,所述模拟量传输模块10包括模拟量输入单元110和模拟量输出单元120;所述模拟量输入单元110连接模拟量输出单元120和控制模块30,模拟量输出单元120连接编译码模块40。所述模拟量输入单元对对外部输入的模拟量信号进行滤波、放大、模数转换后传输给控制模块;所述模拟量输出单元监控信号传输状态并通过编译码模块反馈给控制模块;控制模块输出的模拟量输出信号通过模拟量输出单元进行数模转换后输出。

[0052]

需要理解的是,在各个电路图中,三角形表示模拟地 若干线条依次缩短的表示数字地,有earth标号表示屏蔽地(连接外壳),有0v标号的表示24v的隔离地。

[0053]

本实施例中,所述模拟量输入单元110包括第一接口p1、型号优选为ads8664idbt的模拟量输入芯片u1、第一运放电路111、第二运放电路112、第三运放电路113和第四运放电路114;所述第一接口p1的第1脚、第2脚与第一运放电路111第一输入脚、第二输入脚一对一连接;所述第一接口p1的第3脚、第4脚与第二运放电路112的第一输入脚、第二输入脚一对一连接;所述第一接口p1的第5脚、第6脚与第三运放电路113的第一输入脚、第二输入脚一对一连接;所述第一接口p1的第7脚、第8脚与第四运放电路114的第一输入脚、第二输入脚一对一连接;第一接口p1的第9脚连接第10脚和屏蔽地(本实施例中所有earth表示屏蔽地);第一运放电路111的第一输出脚、第二输出脚与模拟量输入芯片u1的ain_0p脚、ain_0gnd脚一对一连接;第二运放电路112的第一输出脚、第二输出脚与模拟量输入芯片u1的ain_1p脚、ain_1gnd脚一对一连接;第三运放电路113的第一输出脚、第二输出脚与模拟量输入芯片u1的ain_2p脚、ain_2gnd脚一对一连接;第四运放电路114的第一输出脚、第二输出脚与模拟量输入芯片u1的ain_3p脚、ain_3gnd脚一对一连接;模拟量输入芯片u1的avdd脚输入第一电压 5v(连接第一供电端,具体实施时avdd脚可通过两个并联的电容接地,电容对输入的第一电压 5v滤波),模拟量输入芯片u1的dvdd脚输入第二电压 3v3_ad(连接第二供电端,具体实施时dvdd脚可通过两个并联的电容接地,电容对第二电压 3v3_ad滤波),

模拟量输入芯片u1的aux_in脚连接(具体可通过一电阻连接)aux_gnd脚和模拟地(三角形符号表示模拟地);模拟量输入芯片u1的refio脚、refcap脚分别通过一电容接模拟地;模拟量输入芯片u1的脚、脚、alarm脚均连接控制模块30;模拟量输入芯片u1的sclk脚、sdi脚、sdo脚连接模拟量输出单元120和控制模块30;模拟量输入芯片u1的rdfgnd脚、脚、agnd脚、da/sy脚、dgnd脚均接地。

[0054]

其中,所述第一接口p1将外部输入的4路模拟量信号(第一路模拟信号ain0

±

、第二路模拟信号ain1

±

、第三路模拟信号ain2

±

和第四路模拟信号ain3

±

)传输至对应的运放电路中,每个运放电路对相应路的模拟信号进行滤波、放大后输出给4通道、精度为12位(bit)的模拟量输入芯片u1,4路模拟量的电压范围是0v~ 10v,该模拟量输入芯片u1可以直接承受10v的电压直接输入,节省中间的高精密运算放大器,并且带有spi接口,可以直接与控制模块30中的主控芯片进行通讯。

[0055]

每个运放电路的功能和电路结构相同,只是输入输出的信号不同,此处以第一运放电路111为例,其包括第一运放m1、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一保护二极管ds1、第一电容c1和第二电容c2;所述第一电阻r1的一端(即第一运放电路111的第一输入脚,连接第一接口p1的第1脚)连接第二电阻r2的一端,第一电阻r1的另一端(即第一运放电路111的第二输入脚,连接第一接口p1的第2脚)连接第三电阻r3的一端;第二电阻r2的另一端连接第一电容c1的一端、第一保护二极管ds1的一端和第一运放的同相输入脚;第三电阻r3的另一端(即第一运放电路111的第二输出脚)连接第一电容c1的另一端、第一保护二极管ds1的另一端和模拟量输入芯片u1的ain_0gnd脚;第一运放的反相输入脚连接第一运放的输出脚和第四电阻r4的一端,第四电阻r4的另一端(即第一运放电路111的第一输出脚)连接第二电容c2的一端和模拟量输入芯片u1的ain_0p脚,第二电容c2的另一端接地。

[0056]

其中,第一电阻r1用于提供电压位,r2、r3和c1组成π型滤波电路,第一保护二极管ds1用于保护运放,r4和c2组成rc滤波电路。需要理解的是,在具体实施时,可采用型号为lm224的四运算放大器芯片,其内部集成了四个运放,可以代替每个运放电路中的运放,进一步提高电路的集成度。如图2所示,每个运放中的字母a、b、c、d即代表四运算放大器芯片中的四个运放,这四个运放外围的引脚1

‑

14即是四运算放大器芯片的引脚。

[0057]

请一并参阅图3和图4,所述模拟量输出单元120包括第二接口p2、型号优选为ad5724r的模拟量输出芯片u2、第五电阻r5、第六电阻r6、第一输出电路(由两部分组成,分别标号121_1和121_2)、第二输出电路(由两部分组成,分别标号122_1和122_2)、第三输出电路(由两部分组成,分别标号123_1和123_2)和第四输出电路(由两部分组成,分别标号124_1和124_2);所述模拟量输出芯片u2的dvcc脚输入第三电压 3v3_dac(连接第三供电端),模拟量输出芯片u2的脚接数字地;模拟量输出芯片u2的脚、脚和脚均连接控制模块30;模拟量输出芯片u2的sclk脚连接模拟量输入芯片u1的sclk脚和控制模块30,模拟量输出芯片u2的sdin脚连接模拟量输入芯片u1的sdi脚和控制模块30,模拟量输出芯片u2的sdo脚连接模拟量输入芯片u1的sdo脚和控制模块30,模拟量输出芯片u2的refin/refout脚通过一电容连接模拟量输出芯片u2的gnd脚和数字地,模拟量输出芯片u2的avdd脚输入第一电压 5v;模拟量输出芯片u2的vouta脚、voutb脚、voutc

脚、voutd脚与第一输出电路的第一输入脚、第二输出电路的第一输入脚、第三输出电路的第一输入脚、第四输出电路的第一输入脚一对一连接;模拟量输出芯片u2的avss脚、sig_gnd脚、dac_gnd脚和epad脚均连接模拟地;第一输出电路的第一输出脚、第二输出脚与第二接口p2的第10脚、第9脚一对一连接;第二输出电路的第一输出脚、第二输出脚与第二接口p2的第8脚、第7脚一对一连接;第三输出电路的第一输出脚、第二输出脚与第二接口p2的第6脚、第5脚一对一连接;第四输出电路的第一输出脚、第二输出脚与第二接口p2的第4脚、第3脚一对一连接;第二接口p2的第1脚连接第2脚和屏蔽地,第一输出电路至第四输出电路的第三输出脚均连接编译码模块40;第五电阻r5的一端输入第一电压 5v,第五电阻r5的另一端连接第六电阻r6的一端和各个输出电路的第二输入脚,第六电阻r6的另一端连接模拟地。

[0058]

其中,模拟量输出单元120的电压范围为0v~10v,spi信号(包括spi2_sclk信号、spi2_mosio信号和spi2_miso信号)与控制模块30中的主控芯片直接连接并通信,spi信号中的数据用于控制模拟量输出芯片u2的输出状态,例如从vouta脚~voutd脚中的哪个脚输出,是几路同时输出还是单路输出。信号是串行接口帧同步信号,信号的下降沿数据传输,上升沿是数据锁定;信号用于选择是更新模拟量输出还是锁存控制,,如果在写循环期间 信号保持高电平,则更新dac寄存器的输入,但是在信号的下降边缘之前不更新输出,所有模拟输出可以在 信号的下降沿上同时更新;信号用于将模拟量输出芯片u2内置的dac寄存器设置为零电平代码或者中间电平代码。第二接口p2为输出端子,外部可以接需要模拟量信号的设备,例如比例阀,激光器功率控制等;输出的模拟量信号(da_out1

±

~ da_out4

±

)用于控制这些设备的工作状态。

[0059]

每个输出电路的功能和电路结构相同,只是输入输出的信号不同,此处以第一输出电路为例,其包括第二运放m2、第三运放m3、第一共模电感l1、第七电阻r7和第一开关管q1(nmos管);所述第二运放m2的同相输入脚(即第一输出电路的第一输入脚)连接模拟量输出芯片u2的vouta脚,第二运放m2的反相输入脚连接第二运放m2的输出脚和第一共模电感的第1脚,第一共模电感的第2脚(即第一输出电路的第一输出脚)连接第二接口p2的第10脚,第一共模电感的第3脚接地,第一共模电感的第4(即第一输出电路的第二输出脚)连接第二接口p2的第9脚,第二运放m2的输出脚连接第三运放m3的反相输入脚,第三运放m3的同相输入脚(即第一输出电路的第二输入脚)连接第五电阻r5的另一端,第三运放m3的输出脚连接第七电阻r7的一端和第一开关管q1的栅极,第七电阻r7的另一端输入第一电压 5v,第一开关管q1的源极接数字地,第一开关管q1的漏极(即第一输出电路的第三输出脚)连接编译码模块40(具体可通过一电阻连接编译码模块40,图3中是4个电阻组合的电阻器)。

[0060]

其中,第二运放m2起到隔离的作用,用于防止烧坏模拟量输出芯片u2,同时加大驱动能力。图4中的电路用于监控模拟量信号是否有输出, r5和r6的分压提供一个固定的参考电平,当模拟量输出芯片u2没有输出或输出低电平时(此时dig_da1信号的电压在0v~0.5v),第三运放m3(比较器)输出高电平从而控制q1导通,dacstat1信号为低电平,通过编译码模块反馈给主控芯片。当有模拟量信号输出(此时dig_da1信号的电压大于0.5v且小于等于10v)时,第三运放m3输出低电平,q1截止,dacstat1信号为高电平。主控芯片根据

dacstat[1..4]信号的高低电平即可判断模拟量信号(da_out1

±

~ da_out4

±

)是否输出,且是哪一路输出。

[0061]

请一并参阅图5和图6,所述数字量传输模块20包括第三接口p3、第四接口p4、第五接口p5、第六接口p6、第七接口p7、48个数字量输入单元(第一数字量输入单元至第四十八数字量输入单元48)、8个数字量输出单元(第一数字量输出单元至第八数字量输出单元)和监控反馈单元;所述第三接口p3的第1脚连接第一数字量输入单元的输入脚,第2脚连接第二数字量输入单元的输入脚,以此类推,直至第三接口p3的第15脚连接第十六数字量输入单元的输入脚;同理,第四接口p4的各个引脚对应连接第十七数字量输入单元至第三十二数字量输入单元的输入脚,第五接口p5的各个引脚对应连接第三十三数字量输入单元至第四十八数字量输入单元的输入脚,各个数字量输入单元的输出脚均连接编译码模块40;第一数字量输出单元至第四数字量输出单元的各个输出脚均连接第六接口p6,第五数字量输出单元至第八数字量输出单元的各个输出脚均连接第七接口p7,各个数字量输出单元的输入脚均连接编译码模块40。

[0062]

其中,各个数字量输入单元的功能和电路结构相同,只是输入输出的信号不同,此处以第一数字量输入单元为例,请一并参阅图7,其包括第一光耦a1、第一指示灯g1、第八电阻r8、第九电阻r9、第三电容c3和第四电容c4;所述第三电容c3的一端连接第八电阻r8的一端和第一光耦a1的第1脚(即第一数字量输入单元的输入脚),第三电容c3的另一端连接第八电阻r8的另一端、第一指示灯g1的负极和隔离地,第一光耦a1的第2脚连接第一指示灯g1的正极,第一光耦a1的第3脚接数字地;第一光耦a1的第4脚(即第一数字量输入单元的输出脚)连接第九电阻r9的一端、第四电容c4的一端和编译码模块40,第九电阻r9的另一端输入第四电压 3v3(连接第四供电端),第四电容c4的另一端接数字地。

[0063]

其中第三接口p3至第五接口p5是24v输入端子,接外部的24v电压输入,一共有48路输入(即数字量信号input_[1..48]),通过各个数字量输入单元进行隔离后输出对应input_cpu_[1..48]信号,通过编译码模块传输给主控芯片。如图7所示,第一光耦a1用于隔离3.3v和24v,input_1信号为高电平24v时,第一指示灯g1被点亮,第一光耦a1导通,input_cpu_1信号为低电平。input_1信号为低电平24v时,第一指示灯g1熄灭,第一光耦a1截止,input_cpu_1信号被r9上拉为高电平。通过input_1信号的高低电平变化来传输对应的数据。

[0064]

在具体实施时,为了提高集成度,每四个数字量输入单元中为一组,可采用型号是tcmt4100的光电耦合器,其内部集成了4个光耦来代替每个数字量输入单元中的光耦;同理,四个数字量输入单元中的4个输出脚的电阻(对应r9)也可用集成了4个电阻的电阻器来代替,4个输出脚的电容(对应c4)用集成了4个电容的电容器来代替。

[0065]

各个数字量输出单元的功能和电路结构相同,只是输入输出的信号不同,此处以第一数字量输出单元为例,请一并参阅图8,其包括型号优选为bts716g的第一驱动芯片u3、型号优选为tcmt4100的第二光耦a2、第一电阻器rp1(只是将4个电阻集成在一起来缩小体积,以减小pcb板的空间,相互之间无连接)、第二电阻器rp2、第三电阻器rp3和第一电容器cp1(只是将4个电容集成在一起来缩小体积,以减小pcb板的空间,相互之间无连接);所述第二光耦a2的第1脚、第3脚、第5脚、第7脚与第一电阻器rp1的第4脚、第3脚、第2脚、第1脚一对一连接;第二光耦a2的第2脚、第4脚、第6脚和第8脚(即第一数字量输出单元的4个输入

脚)均连接编译码模块40;第二光耦a2的第16脚、第14脚、第12脚、第10脚与第二电阻器rp2的第1脚、第2脚、第3脚、第4脚一对一连接;第二光耦a2的第15脚连接第三电阻器rp3的第1脚、第一电容器cp1的第1脚和第一驱动芯片u3的in1脚;第二光耦a2的第13脚连接第三电阻器rp3的第2脚、第一电容器cp1的第2脚和第一驱动芯片u3的in2脚;第二光耦a2的第11脚连接第三电阻器rp3的第3脚、第一电容器cp1的第3脚和第一驱动芯片u3的in3脚;第二光耦a2的第9脚连接第三电阻器rp3的第4脚、第一电容器cp1的第4脚和第一驱动芯片u3的in4脚;第一电阻器rp1的第5脚至第8脚均输入第四电压 3v3,第二电阻器rp2的第5脚至第8脚均输入第五电压 24v(连接第五供电端),第三电阻器rp3的第5脚至第8脚以及第一电容器cp1的第5脚至第8脚均接隔离地,第一驱动芯片u3的vbb脚输入第五电压 24v;第一驱动芯片u3的out1脚、out2脚、out3脚、out4脚与第六接口p6的第16脚、第15脚、第14脚、第13脚一对一连接;第一驱动芯片u3的st1/2脚连接st2/4脚连接监控反馈单元。

[0066]

其中,主控芯片将需要输出的数字信号通过编译码模块输出,即o_cpu_[1..32]信号,通过对应的数字量输出单元进行隔离,再由第一驱动芯片u3(高边输出第一驱动芯片)驱动后,通过第六接口p6和第七接口p7这两个输出端子输出。当o_cpu_1信号输出低电平,a2导通,则u3的in1接口的信号被rp3中的一个电阻上拉为高电平,u3输出24v的数字量信号output1。当o_cpu_1信号输出高电平,a2截止,则u3的in1接口的信号的电压通过cp1中对应的电容泄放到地而变为低电平,u3输出低电平的数字量信号output1。

[0067]

图9所示的电路用于监测数字量信号output[1..32]的输出,当输出发生短路或过载或温度过高时,第一驱动芯片u3输出高电平的diag_信号,对应的光耦导通,noutatat1信号被下拉为低电平;noutatat[1..8]信号通过编译码模块反馈给主控芯片,主控芯片根据其高低电平即可实现短路、过载或过温监控。也可在第一驱动芯片u3的out1脚至out4脚分别连接一指示灯,output1

‑

4信号传输时对应的指示灯被点亮,方便用户了解当前数字量输出的情况。

[0068]

请一并参阅图10,所述控制模块30包括主控芯片u4(型号优选为stm32f103vc的单片机)和烧录接口jp;所述主控芯片u4的pa0_wkup 脚、pa1脚和pd13脚均连接手轮处理模块50;主控芯片u4的pa2脚、pa3脚、pa4脚、pa5脚、pa6脚、pa7脚、pc8脚和pc9脚均连接通讯模块70;主控芯片u4的pa8脚和pd15脚均连接pwm输出模块60;主控芯片u4的pa9脚、pa10脚、pa13/jtms/swdio脚与烧录接口jp的第2脚、第1脚、第5脚、第6脚一对一连接;主控芯片u4的pb8脚、pb9脚、pb12脚与模拟量输出芯片u2的脚、脚、脚一对一连接;主控芯片u4的pb10脚、pb11脚、pb13脚、pb14脚、pb15脚、pe15脚与模拟量输入芯片u1的脚、alarm脚、sclk脚、sdo脚、sdi脚、脚一对一连接;主控芯片u4的pc0脚至pc7脚、pd0脚至pd12脚、pe5脚均连接编译码模块40。

[0069]

其中,主控芯片u4是主流增强型arm cortex

‑

m3 mcu,内部设有256 kb flash、48kb ram、72 mhz的 cpu、电机控制、usb和can等模块和功能;与通讯模块70中的通讯芯片u11通过spi接口进行通信,与da和ad也是通过spi通信,而数字量输入输出则通过io口并口通信。各个信号中,enca信号是手轮a相信号输入,encb信号是手轮b相信号输入,通过手轮处理模块传输至主控芯片中,由主控芯片内部的定时器编码模块来进行信号处理(具体处理方式为现有技术)。sint信号是ethercat通讯中断信号,eep_done信号是xml文件加载成

功信号,scs_esc信号是ethercat通讯片选信号,sclk信号是ethercat通讯spi的时钟信号,smiso信号是ethercat通讯spi的输入信号,smosi信号是ethercat通讯spi的输出信号,sync_l0信号是ethercat通讯同步信号0,sync_l1信号是ethercat通讯同步信号1;这些信号组成ethercat通讯,通过通讯模块70中的通讯芯片(ax58100)与上位机进行通讯。pwm信号由主控芯片输出,用于实现pwm控制,当切割慢速时使用;fout信号是快速pwm输出信号,在需要快速切割时使用。主控芯片与烧录接口jp之间传输的uart1_tx信号(串口通讯输出信号)和uart1_rx(串口通讯输入信号),用于调试时打印数据,以方便观察各种工作状态。主控芯片与烧录接口jp之间传输的uc_swdio信号(sw接口(一种通用接口)的数据输入输出)和uc_swclk信号(sw接口的时钟信号),用于进行程序的调试、烧录和仿真。boot1信号和boot0信号输入的是主控芯片的配置引脚,用于决定单片机启动后程序从哪里开始运行。主控芯片输出信号来配置模拟量输出芯片u2内置的dac寄存器,信号用于更新dac寄存器从而更新模拟输出,信号是串行接口帧同步信号,adc_cs信号用于片选,信号用于复位,adc_alarm信号是检测输入的模拟量信号和数字量信号不正常时的报警信号。spi2_sclk信号是通讯总线spi2 的时钟信号,spi2_miso信号是通讯总线spi2 的输入信号,spi2_mosi信号是通讯总线spi2 的输输出信号,这些信号用于spi2总线通讯,为adc和dac共用,当需要与哪个芯片进行通讯时,可以去使能控制脚。db_0~db_7信号是8位并口总线通讯信号,可以输入也可以输出。oe0~oe7信号是使能信号,当为低电平时,译码单元中的芯片被使能,那么这个时候db_0到db_7接口上的数据就是input_cpu_1到input_cpu_8上的实时数据;当不用时,主控芯片把对应oe信号的电平拉高。le0~le3信号是锁存单元中74hc373芯片的锁存控制管脚,在下降沿进行输出,上升沿进行锁存,一直到下一个数据来进行更新。oe_do信号是锁存单元的输出芯片的使能片选信号,当主控芯片控制其为低电平时,db_0到db_7上的数据会输入到4个锁存芯片上,具体选择哪一个芯片来进行输出,就由le0~le3信号进行更新。out_led信号用于控制led灯,以指示产品的运行状态,如待机、运行或者出故障。

[0070]

请一并参阅图11和图12,所述编译码模块40包括9个译码单元和4个锁存单元,各个译码单元和锁存单元均连接控制模块;第一译码单元至第七译码单元均连接数字量传输模块,用于对数字量传输模块输入的数字量信号进行译码后传输给控制模块;第八译码单元连接模拟量传输模块(具体是模拟量输出单元),用于对模拟量传输模块输出的监控信号进行译码后传输给控制模块;第九译码单元连接手轮处理模块,用于对手轮处理模块传输的手轮数据进行译码后传输给控制模块;第一锁存单元至第四锁存单元均连接控制模块和数字量传输模块,用于对控制模块输出的数字量输出信号进行锁存后输出给数字量传输模块。

[0071]

各个译码单元的功能和电路结构相同,只是输入的信号不同,则对应外接的引脚不同,此处以第一译码单元为例,请一并参阅图13,其包括优选型号为nxp74hc244pw的第一逻辑芯片u5、第十电阻r10和第五电容c5;所述第一逻辑芯片u5的脚连接脚、第十电阻r10的一端和主控芯片u4的pd0脚;第十电阻r10的另一端输入第四电压 3v3,第一逻辑芯片u5的a1脚、a2脚、a3脚、a4脚、a5脚、a6脚、a7脚、a8脚与第一数字量输入单元的输出脚(即内部光耦的第4脚)、第二数字量输入单元的输出脚、第三数字量输入单元的输出脚、第

四数字量输入单元的输出脚、第五数字量输入单元的输出脚、第六数字量输入单元的输出脚、第七数字量输入单元的输出脚、第八数字量输入单元的输出脚一对一连接;第一逻辑芯片u5的vcc脚输入第四电压 3v3、还通过第五电容c5接数字地;第一逻辑芯片u5的y1脚、y2脚、y3脚、y4脚、y5脚、y6脚、y7脚、y8脚与主控芯片u4的pc0脚、pc1脚、pc2脚、pc3脚、pc4脚、pc5脚、pc6脚、pc7脚一对一连接。

[0072]

其中, oe0

‑

oe8信号用于选择需要通信的芯片,即oe0

‑

oe8信号有效(如低电平)时,a1脚与y1脚连通,a1脚上的信号传输至y1脚;a2脚与y2脚连通,a2脚上的信号传输至y2脚,以此类推。

[0073]

第七译码单元至第九译码单元的输入信号与其他译码单元有区别,第七译码单元的具体电路如图14所示,第八译码单元的具体电路如图15所示,第九译码单元的具体电路如图16所示。

[0074]

各个锁存单元的功能和电路结构相同,只是输出的信号不同,则对应外接的引脚不同,此处以第一锁存单元为例,请一并参阅图17,其包括第一锁存芯片(优选型号为74hc373的锁存器)u6、第十一电阻r11、第十二电阻r12和第六电容c6;所述第一锁存芯片u6的脚连接第十一电阻r11的一端和主控芯片u4的pe5脚,第十一电阻r11的另一端输入第四电压 3v3,第一锁存芯片u6的d0脚、d1脚、d2脚、d3脚、d4脚、d5脚、d6脚、d7脚与xx一对一连接;第一锁存芯片u6的vcc脚输入第四电压 3v3、还通过第六电容c6接数字地;第一锁存芯片u6的q0脚、q1脚、q2脚、q3脚与第一数字量输出单元的4个输入脚(即第二光耦a2的第2脚、第4脚、第6脚、第8脚)一对一连接;第一锁存芯片u6的q4脚、q5脚、q6脚、q7脚与第一数字量输出单元的4个输入脚一对一连接;第一锁存芯片u6的le脚连接主控芯片u4的pd9脚、还通过第十二电阻r12接数字地。

[0075]

其中,当主控芯片控制oe_do信号为低电平时,第一锁存芯片u6被选中,处于锁存状态,在le0信号有效(如高电平)时,db_0信号通过第一锁存芯片u6输出为对应的o_cpu_1信号,其他信号同理也对应输出,即d0脚与q0脚连通输出,d1脚与q1脚连通输出,以此类推。。

[0076]

请一并参阅图18和图19,所述手轮处理模块50包括手轮接口j1(型号优选为tcmt4100)、型号优选为tcmt4100的第三光耦a3和第四光耦a4、型号优选为hcpl

‑

181 000e的第五光耦a5 、型号优选为el0631的第六光耦a6(双通道高速光耦)、第四电阻器rp4、第五电阻器rp5、第十二电阻r12、第十三电阻r13、第七电容c7和第八电容c8;所述手轮接口j1的第1脚和第2脚输入第五电压 24v,手轮接口j1的第9脚和第10脚连接隔离地;手轮接口j1的第3脚、第4脚、第5脚、第6脚与第三光耦a3的第1脚、第3脚、第5脚、第7脚一对一连接;手轮接口j1的第11脚、第12脚、第13脚、第7脚与第四光耦a4的第3脚、第5脚、第7脚、第1脚一对一连接;手轮接口j1的第14脚、第15脚与第六光耦a6的第1脚、第4脚一对一连接;手轮接口j1的第8脚连接第五光耦a5的e脚;第三光耦a3的第2脚、第4脚、第6脚、第8脚分别通过一指示灯接隔离地;第四光耦a4的第2脚、第4脚、第6脚、第8脚分别通过一指示灯接隔离地;第三光耦a3的第16脚、第14脚、第12脚、第10脚与第四电阻器rp4的第1脚、第2脚、第3脚、第4脚一对一连接;第三光耦a3的第16脚连接第四电阻器rp4的第1脚和第九译码单元中逻辑芯片的a1脚,第三光耦a3的第14脚连接第四电阻器rp4的第2脚和第九译码单元中逻辑芯片的a2脚,第三光耦a3的第12脚连接第四电阻器rp4的第3脚和第九译码单元中逻辑芯片的a3脚,第三

光耦a3的第10脚连接第四电阻器rp4的第4脚和第九译码单元中逻辑芯片的a4脚,第四光耦a4的第16脚连接第五电阻器rp5的第1脚和第九译码单元中逻辑芯片的a5脚,第四光耦a4的第14脚连接第五电阻器rp5的第2脚和第九译码单元中逻辑芯片的a6脚,第四光耦a4的第12脚连接第五电阻器rp5的第3脚和第九译码单元中逻辑芯片的a7脚,第四光耦a4的第10脚连接第五电阻器rp5的第4脚和第九译码单元中逻辑芯片的a8脚,第四电阻器rp4和第五电阻器rp5的第5脚至第8脚均输入第四电压 3v3;第三光耦a3和第四光耦a4的第15脚、第13脚、第11脚、第9脚均接数字地;第五光耦a5的c脚输入第五电压 24v,第五光耦a5的a脚输入第四电压 3v3,第五光耦a5的k脚连接主控芯片u4的pd13脚,第六光耦a6的第1脚连接第七电容c7的一端和第十三电阻r13的一端;第六光耦a6的第2脚连接第七电容c7的另一端、第十三电阻r13的另一端和屏蔽地;第六光耦a6的第4脚连接第八电容c8的一端和第十二电阻r12的一端;第六光耦a6的第3脚连接第八电容c8的另一端、第十二电阻r12的另一端和屏蔽地,第六光耦a6的第8脚输入第四电压 3v3,第六光耦a6的第7脚、第6脚与主控芯片u4的pa0

‑

wkup脚、pa1脚一对一连接;第六光耦a6的第5脚接数字地。

[0077]

其中,手轮接口j1起到隔离作用,将外部的手轮输入的手轮数据传输至主控芯片内部的数据处理单元中进行处理。手轮数据中,x、y、z、4、5表示可以有5个轴选,x1、x10、x100则对应手轮倍率选着。a和b对应表示为a相和b相的手轮信号,通过第六光耦a6隔离后输出对应的enca信号和encb信号。主控芯片输出的手轮控制信号out_led通过第五光耦a5隔离后、从手轮接口j1输出。

[0078]

需要理解的是,手轮处理模块50中还有其他元件,如第三光耦a3和第四光耦a4的第1脚至第8脚上连接的电阻、电容、指示灯,结构和功能与第一数字量输入单元中的对应元件相同,第六光耦a6的第7脚和第6脚连接上拉电阻等,具体详见图18。

[0079]

请一并参阅图20,所述pwm输出模块60包括型号优选为iso7342c的输出电压隔离芯片u7、型号优选为ucc27524d的第二驱动芯片u8、型号优选为ucc27537dbvt的第三驱动芯片u9、型号优选为ucc27537dbvt的第四驱动芯片u10、串口j2、型号优选为pesd5v2s2ut的第一瞬态抑制器d1、第二瞬态抑制器d2、第十四电阻r14和第十五电阻r15;所述输出电压隔离芯片u7的vcc1脚输入第四电压 3v3,输出电压隔离芯片u7的ina脚连接第十四电阻r14的一端和主控芯片u4的pd15脚,输出电压隔离芯片u7的inb脚连接第十五电阻r15的一端和主控芯片u4的pa8脚; 输出电压隔离芯片u7的gnd1脚连接第十四电阻r14的另一端、第十五电阻r15的另一端和数字地;输出电压隔离芯片u7的vcc2脚输入第六电压5v0(连接第六供电端),输出电压隔离芯片u7的gnd2脚连接隔离地,输出电压隔离芯片u7的outa脚连接第二驱动芯片u8的ina脚和第四驱动芯片u10的in 脚,输出电压隔离芯片u7的outb脚连接第二驱动芯片u8的inb脚和第三驱动芯片u9的in 脚;第二驱动芯片u8的ena脚、enb脚、vdd脚均输入第六电压5v0;第二驱动芯片u8的gnd脚接隔离地,第二驱动芯片u8的outa脚连接第一瞬态抑制器d1的第2脚(一个二极管的负极)和串口j2的第4脚,第二驱动芯片u8的outb脚连接第一瞬态抑制器d1的第1脚(另一个二极管的负极)和串口j2的第5脚,第三驱动芯片u9和第四驱动芯片u10的en脚均输入第六电压5v0,第三驱动芯片u9和第四驱动芯片u10的gnd脚均接隔离地,第三驱动芯片u9和第四驱动芯片u10的vdd脚均输入第五电压 24v,第三驱动芯片u9的out脚连接第二瞬态抑制器d2的第2脚(一个二极管的负极)和串口j2的第1脚,第四驱动芯片u10的out脚连接第二瞬态抑制器d2的第1脚(另一个二极管的负极)和串口j2的第

master接口用于spi装置数据采集和输出,32个适用于工业实时i/o控制应用的数字控制i/o,以及一个i/o watchdog提供监测i/o状态来做适当处置以确保产品功能的安全性。提供两种过程数据接口 (pdi),local bus接口和spi slav串口,可透过这些接口将通讯芯片u11连接到外部传统mcu/dsp工业控制机台以支持ethercat功能。通讯芯片u11有两个内存空间,分别对应到esc内存和function缓存器,设计人员可以透过芯片选择脚位来决定存取哪一个内存空间。内部网桥会根据设定的同步条件来自动同步esc内存与功能缓存器的内容,提供ethercat master来远程控制ax58100的功能 (pwm,spi master等)。通讯芯片u11将esc和应用程序中断事件反应在中断状态缓存器,并透过条件或边缘中断触发模式来通知外部mcu/dsp来管理这些esc和应用程序中断事件。

[0084]

综上所述,本发明提供的数字与pwm复合控制器,将48路数字量输入、32路数字量输出、4路16位高精度模拟量输入、4路12位模拟量输出、高精度24v与5v的pwm输出、数字io手轮收发接口、rs485扩展接口及ethercat总线通讯接口均集成在一起为一个模块,与现有各种功能分开设计模块相比,一个模块就能够完全解决所有的应用场景,而不需要多余的控制模块;还省去了各模块之间的连线,大大减小了接线麻烦和信号传输时的外部干扰,节省成本的同时提高了抗干扰性。

[0085]

上述功能模块的划分仅用以举例说明,在实际应用中,可以根据需要将上述功能分配由不同的功能模块来完成,即划分成不同的功能模块,来完成上述描述的全部或部分功能。

[0086]

可以理解的是,对本领域普通技术人员来说,可以根据本发明的技术方案及其发明构思加以等同替换或改变,而所有这些改变或替换都应属于本发明所附的权利要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。