based on a sine

‑

wave measurement.ieee trans.circuits syst.ii express briefs 60(9),567

–

571(2013)中的数字校准需要一个非常精确的正弦波模拟信号作为adc的校准输入信号。

5.以上

背景技术:

内容的公开仅用于辅助理解本发明的构思及技术方案,其并不必然属于本专利申请的现有技术,在没有明确的证据表明上述内容在本专利申请的申请日已经公开的情况下,上述背景技术不应当用于评价本技术的新颖性和创造性。

技术实现要素:

6.为解决上述技术问题,本发明提出一种模数转换器及其数字校准方法,能够有效、经济地消除连续时间内过数转换器中的反馈dac组件的动态误差和静态误差。

7.为了达到上述目的,本发明采用以下技术方案:

8.本发明公开了一种模数转换器,包括环路滤波器、量化器、反馈dac组件、双路选择开关、基准dac单元和数字处理模块,所述反馈dac组件包括多个并行连接的反馈dac单元,从输入端到输出端之间所述环路滤波器、所述量化器和所述数字处理模块依次相互连接,所述反馈dac组件的第一端和所述基准dac单元的第一端分别以相反的极性接入所述环路滤波器,所述反馈dac组件的第二端连接所述双路选择开关的第一端,所述双路选择开关的第二端可选择的两路中的第一路连接在所述量化器和所述数字处理模块之间,第二路连接第一数字序列信号;所述基准dac单元的第二端连接第二数字序列信号。

9.本发明还公开了一种模数转换器的数字校准方法,包括误差提取步骤和误差消除步骤,其中:

10.所述误差提取步骤包括:

11.a1:将上述的模数转换器中的所述双路选择开关的第二端连通可选择的两路中的第二路,以使得所述反馈dac组件中的第i个反馈dac单元的数字输入为所述第一数字序列信号,其他反馈dac单元的数字输入设为零;

12.a2:将输入端的输入信号设为零,并使得所述基准dac单元的数字输入为所述第二数字序列信号;

13.a3:根据所述量化器的输出,计算每个时钟周期第i个反馈dac单元相对于所述基准dac单元的静态误差和动态误差;

14.a4:重复步骤a1至a3,分别得到所述反馈dac组件中的所有反馈dac单元相对于所述基准dac单元的静态误差和动态误差;

15.所述误差消除步骤包括:

16.b1:将上述的模数转换器中的所述双路选择开关的第二端连通可选择的两路中的第一路,以使得所述反馈dac组件、所述环路滤波器和所述量化器形成闭环;

17.b2:将输入端的输入信号设为正常输入信号,并使得所述基准dac单元的数字输入设为零;

18.b3:根据当前时钟周期内所有所述反馈dac单元的输入计算当前时钟周期的所有所述反馈dac单元引入的误差总和;

19.b4:在所述数字处理模块中,根据转换的数字输出和步骤b3中得到的当前时钟周期的所有所述反馈dac单元引入的误差总和,得到校准后的数字输出。

20.优选地,所述误差提取步骤还包括将所述环路滤波器设置为一阶积分器的形式。

21.优选地,步骤a1中的所述第一数字序列信号具体为:在第一个2n时钟周期和第二个2n时钟周期内,所述第一数字序列信号都由n个“10”组合组成,n为正整数。

22.优选地,步骤a2中的所述第二数字序列信号具体为:在第一个2n时钟周期内,所述第二数字序列信号由n个连续的1和n个连续的0组成;在第二个2n时钟周期内,所述第二数字序列信号由2个相同的序列组成,每个序列为n/2个连续的1和n/2个连续的0。

23.优选地,步骤a3中计算得到的每个时钟周期第i个反馈dac单元相对于所述基准dac单元的静态误差e

si

和动态误差e

di

分别为:

24.e

dr

=e

t1

‑

e

t2

[0025][0026]

其中,e

t1

为第2n时钟周期时所述量化器的输出,e

t2

为第4n时钟周期时所述量化器的输出。

[0027]

优选地,n为偶数。

[0028]

优选地,步骤b3中计算得到的当前第k个时钟周期的所有所述反馈dac单元引入的误差总和e

total

为:

[0029]

e

total

=e

stotal

e

dtotal

[0030]

其中,e

stotal

为第k个时钟周期内由反馈dac组件引入的静态误差总和:

[0031][0032]

e

si

为每个时钟周期第i个反馈dac单元相对于所述基准dac单元的静态误差,y

k

为所述模数转换器在第k个时钟周期内的数字输出;

[0033]

e

dtotal

为第k个时钟周期内由反馈dac组件引入的动态误差总和:

[0034][0035]

e

di

为每个时钟周期第i个反馈dac单元相对于所述基准dac单元的动态误差,y

k

‑1为所述模数转换器在第k

‑

1个时钟周期内的数字输出。

[0036]

优选地,步骤b4中得到的校准后的数字输出y

cal

为:

[0037]

y

cal

=y e

total

[0038]

其中,y为所述数字处理模块转换的数字输出,e

total

为步骤b3中得到的当前时钟周期的所有所述反馈dac单元引入的误差总和。

[0039]

本发明另外还公开了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令在被处理器调用和执行时,所述计算机可执行指令促使处理器实现上述的数字校准方法。

[0040]

与现有技术相比,本发明的有益效果在于:采用本发明的模数转换器及其数字校准方法,能够同时消除反馈dac组件的静态误差和动态误差,并且不会引入额外的环路延

时。并且由于校准为数字式,除了一个基准dac单元,不需要额外的模拟电路,也不需要额外的模拟信号,对各种非理想因素较为鲁棒。

附图说明

[0041]

图1是传统的连续时间delta

‑

sigma模数转换器的结构示意图;

[0042]

图2是反馈dac单元中的静态误差的示意图;

[0043]

图3是反馈dac单元中的动态误差的示意图;

[0044]

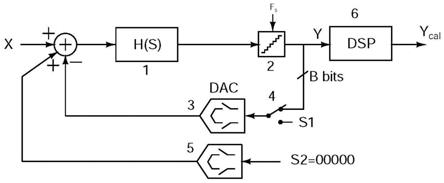

图4是本发明优选实施例的模数转换器的结构示意图;

[0045]

图5是图4中的模数转换器在提取第i个反馈dac单元误差的电路结构图;

[0046]

图6是图5中的数字序列s1和数字序列s2的示意图。

具体实施方式

[0047]

以下对本发明的实施方式作详细说明。应该强调的是,下述说明仅仅是示例性的,而不是为了限制本发明的范围及其应用。

[0048]

需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。另外,连接既可以是用于固定作用也可以是用于电路/信号连通作用。

[0049]

需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明实施例和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

[0050]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多该特征。在本发明实施例的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0051]

反馈dac误差包括静态误差和动态误差,它们都会影响delta

‑

sigmaadc的精度。dac的静态误差是指在多比特型(b bits)delta

‑

sigmaadc中,反馈dac中2

b

‑

1个dac单元的输出大小偏离标准值,形成一个样本为2

b

‑

1的随机分布,如图2所示。这使得dac的输入

‑

输出关系不再是线性的,从而会在delta

‑

sigmaadc中引入非线性失真。dac的动态误差是指由于dac输出波形的上升沿和下降沿不相等,在一段时间内dac的输出的总和与其数字输入之和不再是线性的关系。dac的动态误差可以分为线性部分和非线性部分,线性部分会随着静态误差一起被校准,而非线性部分则可以等效到上升沿部分。如图3所示,在其数字输入为1情况下,假设每个非归零型(nrz)dac单元在一个时钟周期内输出电流总和为1;其中阴影部分即为每个非归零型(nrz)dac单元在每次0

→

1转换中内引入的误差,记为δ。由于动态误差的存在,上面的例子中输出电流总和为2

‑

δ(它原本应当输出2,但它经历了1次0

→

1转换,故引入了动态误差

‑

δ);中间的例子中dac输出电流的总和为2

‑

2δ(它原本应当输出2,但它经历了2次0

→

1转换,故引入了动态误差

‑

2δ),下面的例子中电流总和为4

‑

δ(它原本应当输出4,但它经历了1次0

→

1转换,故引入了动态误差

‑

δ)。可见输出电流的总和与其数

字输入的顺序有关,如同样是4个时钟周期内数字输入为2个1和2个0,上面的例子中dac输出电流的总和为2

‑

δ,中间的例子中dac输出电流的总和为2

‑

2δ。dac动态误差的存在使得模数转换器的输出频谱上噪声增加,谐波失真变差。

[0052]

目前,有不少电路选用单比特型的dac或是归零型(rz)dac来缓解反馈dac的误差。但是单比特型dac对时钟抖动更为敏感,且在同样的adc精度要求下需要更高的过采样率(osr)和/或噪声整形阶数,而归零型(rz)dac则对环路滤波器中放大器的压摆率要求更高,且受时钟抖动影响更严重。所以,研究在使用非归零型(nrz)dac的情况下,如何有效、经济地解决静态和动态误差是非常有意义的。

[0053]

本发明提出了一种针对连续时间delta

‑

sigma模数转换器使用的开环数字校准技术,结构图如图4所示,该delta

‑

sigma模数转换器包括环路滤波器1、量化器2、反馈dac组件3、双路选择开关4、基准dac单元5和数字处理模块(dsp)6,其中反馈dac组件3包括并行的b个反馈dac单元,从输入端开始环路滤波器1、量化器2和数字处理模块6依次相互连接,双路选择开关4的一端连接反馈dac组件3,另一端的两路中的一路连接在量化器2和数字处理模块6之间,另一路连接输入序列s1;反馈dac组件3和基准dac单元5接入环路滤波器1的极性相反,基准dac单元5的另一端连接参考序列s2。其中通过在量化器2和反馈dac组件3之间插入的双路选择开关4,用于配置delta

‑

sigma模数转换器处于正常工作状态或者开环校准状态;增加的基准dac单元5可以对反馈数模转换器3的所有的反馈dac单元参照该基准dac单元5依次进行校准。在输入序列s1相同的情况下,通过输入两个不同的参考序列s2,得到各个反馈dac单元相对基准dac单元5的两个包含静态误差和动态误差的等式,由此可以解出各个反馈dac单元引入的静态误差和动态误差的大小。其中的量化器2的数字输出连接一个数字处理模块6,用于存储各个反馈dac单元的误差并且完成数字校准过程中的一些数字运算,最终得到校准后的数字输出。在电路实现中,该数字处理模块6可以和delta

‑

sigma模数转换器的抽取滤波器模块合并在一起。该数字校准技术能够同时消除反馈dac的静态和动态误差,并且不会引入额外的环路延时。此外,由于校准为数字式,除了一个基准dac单元,不需要额外的模拟电路,也不需要额外的模拟信号,对各种非理想因素较为鲁棒。

[0054]

基于上述delta

‑

sigma模数转换器进行开环数字校准的流程分为两步:第一步,在校准模式下提取2

b

‑

1个反馈dac单元相对于基准dac单元5的数字误差,包括静态误差e

s1

,e

s2

,

…

,e

si

,

…

,e

s(2^b

‑

1)

和动态误差e

d1

,e

d2

,

…

,e

di

,

…

,e

d(2^b

‑

1)

,并且在数字处理模块6中存储这些误差。第二步,根据得到的反馈dac单元的数字误差,在正常工作模式的delta

‑

sigma adc的数字输出中相应的消除这些误差,得到校准后的adc数字输出。

[0055]

如图5所示,是该delta

‑

sigma模数转换器在校准模式下第i个反馈dac单元相对于基准dac单元的误差被提取的过程。此时,双路选择开关接下端口,上端口悬空(即第i个反馈dac单元连接输入序列s1),从而把传统闭环delta

‑

sigma adc的环路断开,形成一个开环放大、量化的信号链路;同时delta

‑

sigmaadc的模拟输入x设为零,这样基准dac单元的模拟输出与反馈dac组件的模拟输出之差就是环路滤波器的输入信号,其中环路滤波器设置为一阶积分器h1(s)的形式,对误差进行累积。其中第i个反馈dac单元的数字输入为图中的数字序列s1;基准dac单元的数字输入为图中的数字序列s2,如图6所示;其他反馈dac单元的数字输入被设为0。可以看到在第一个2n(为了方便,图6中n取4)时钟周期(2n*t

s

)内,数字序列s1由n个“10”组合组成,其中有n个1和n个0,有n个0

→

1转换;数字序列s2由n个连续的1

和n个连续的0组成,有n个1和n个0,只有1个0

→

1转换。在第二个2n时钟周期内,数字序列s1由n个“10”组合组成,其中有n个1和n个0,有n个0

→

1转换;数字序列s2由2个相同的序列组成,该序列为n/2个连续的1和n/2个连续的0,共有n个1和n个0,以及2个0

→

1转换。在2n个时钟周期内,基准dac单元的模拟输出与第i个反馈dac单元的模拟输出之差就作为输入信号先被模拟滤波器h1(s)积分放大,再被量化器过采样量化(量化器的采样频率为f

s

),得到数字化的第i个反馈dac单元相对基准dac单元的误差(即图中所示的

‑

e

i

)。假设第2n时钟周期量化器的输出为e

t1

,第4n时钟周期量化器的输出为e

t2

,每个时钟周期第i个反馈dac单元相对基准dac单元的静态误差为e

si

,动态误差为e

di

,则有:

[0056]

e

t1

=n

·

e

sr

(n

‑

1)

·

e

dr

[0057]

e

t2

=n

·

e

sr

(n

‑

2)

·

e

dr

[0058]

解方程可得:

[0059]

e

dr

=e

t1

‑

e

t2

[0060][0061]

根据同样的方法,可以得到其他反馈dac单元相对基准dac单元的静态误差和动态误差。在提取某个反馈dac单元的误差的阶段,其他反馈dac单元的数字输入设为零。这样总共经过4*n*(2^b

‑

1)个时钟周期就可以提取出所有反馈dac单元的静态误差e

s1

,e

s2

,

…

,e

si

,

…

,e

s(2^b

‑

1)

和动态误差e

d1

,e

d2

,

…

,e

di

,

…

,e

d(2^b

‑

1)

。

[0062]

图4描述的是正常工作模式下电路的配置,双路选择开关接上端口,下端口悬空,反馈dac、环路滤波器和量化器形成一个正常的闭环delta

‑

sigma adc;delta

‑

sigmaadc模拟输入为x;同时基准dac单元的数字输入为零。

[0063]

假设delta

‑

sigma adc在第k个时钟周期内的数字输出为y

k

,在第k

‑

1个时钟周期内的数字输出为y

k

‑1,其中y

k

‑1和y

k

的值为0,1,2

…2b

‑

1其中一个。这也就意味着在第k时钟周期内第1,2

…

i

…

y

k

个dac单元(共y

k

个dac单元)的输入为数字1,其他第y

k 1

,y

k 2

…2b

‑

1个dac单元(共2

b

‑1‑

y

k

个dac单元)的输入为数字0;在第k

‑

1时钟周期内第1,2

…

i

…

y

k

‑1个dac单元(共y

k

‑1个dac单元)的输入为数字1,其他第y

k

‑1 1,y

k

‑1 2

…2b

‑

1个dac单元(共2

b

‑1‑

y

k

‑1个dac单元)的输入为数字0。故在第k个时钟周期内由反馈dac引入的静态误差总和为:

[0064][0065]

动态误差的计算则更为复杂,需要根据y

k

与y

k

‑1的大小关系进行分类讨论,如下面的公式所示:

[0066][0067]

所以,在第k个时钟周期内由反馈dac单元引入的误差包括静态误差和动态误差:

[0068]

e

total

=e

stotal

e

dtotal

[0069]

最终的数字输出y为(其中q为量化噪声):

[0070][0071]

在dsp中需要消除该误差总和e

total

,得到校准后的delta

‑

sigma adc的数字输出y

cal

:

[0072][0073]

最终dsp根据数字输出y和所有所述反馈dac单元引入的误差总和e

total

,得到校准后的数字输出y

cal

。

[0074]

本发明实施例还提供了一种计算机可读存储介质,该计算机可读存储介质存储有计算机可执行指令,该计算机可执行指令在被处理器调用和执行时,计算机可执行指令促使处理器实现上述的开环数字校准的流程步骤,具体实现可参见上述方法实施例,在此不再赘述。

[0075]

本发明的背景部分可以包含关于本发明的问题或环境的背景信息,而不是由其他人描述现有技术。因此,在背景技术部分中包含的内容并不是申请人对现有技术的承认。

[0076]

以上内容是结合具体/优选的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,其还可以对这些已描述的实施方式做出若干替代或变型,而这些替代或变型方式都应当视为属于本发明的保护范围。在本说明书的描述中,参考术语“一种实施例”、“一些实施例”、“优选实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。尽管已经详细描述了本发明的实施例及其优点,但应当理解,在不脱离由所附权利要求限定的范围的情况下,可以在本文中进行各种改变、替换和变更。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。