实现nand门系统和实现nor门系统的集成电路

1.本技术是pct申请号为pct/us2018/026817、国际申请日为2018年4月10日、中国申请号为201880031001.9、发明名称为“肖特基cmos异步逻辑单元”的申请的分案申请。

技术领域

2.本技术涉及半导体器件和电路,并且更具体地,涉及采用超互补金属氧化物半导体(scmos

tm

)器件并因此由于改善功耗、工作速度、电路面积和器件密度而展现出改进的器件性能的模拟、数字和混合信号集成电路(ic)。

背景技术:

3.自从引入集成电路(ic)以来,工程师一直试图增加ic上电路的密度,这降低了所谓ic的制造成本。一种方法是将更多的组件/功能放到芯片上。第二种方法是在更大的晶圆上构建更多芯片以降低ic成本。例如,硅晶圆的尺寸已从1960年代的平均直径3英寸增长到如今的12英寸。

4.过去曾尝试过各种尝试以改善ic功能、性能和成本指标。早期的ic实施方式使用双极结型晶体管(bjt),该双极结型晶体管(bjt)具有垂直堆叠的各个扩散区的层,以及包含三个开关端子(基极、发射极和集电极)以及其他电阻(r)和电容(c)电路元件的隔离晶体管袋。然而,在最近十年的ic实施方式中,是v

‑

i信号和用于在芯片上容纳更多组件的phy参数缩放。

5.cmos技术紧随其后,并超越了bjt技术,后者相对笨重,提供差的晶体管产量,展现高dc电力使用。使用互补mos(cmos)结构的器件复杂度已增长到数十亿电路元件。30多年来,通过缩小cmos晶体管的物理尺寸,实现了成本降低和cmos技术性能提高。这些尺寸缩小到在关键器件参数中只有几个分子层厚的大小。然而,cmos的进一步缩小正受到物理定律的限制。除了试图制造数百亿个具有“分子”尺寸的cmos电路元件外,这些显著更小的电路还以非常低的信号(电压)电平工作,使其信号完整性易受噪声影响,并导致速度下降和/或功率/热流失。

技术实现要素:

6.在各种实施例中,肖特基(schottky)

‑

cmos(在本文中也称为“超级cmos”和scmos

tm

)技术被用于使用诸如低阈值肖特基势垒二极管(ltsbd

tm

)的肖特基势垒二极管(sbd)来构建电路块,从而解决与对更高半导体效率的需求不断增加以及即将出现的cmos晶体管尺寸的物理限制有关的上述缺陷和问题。

7.在一些实施例中,集成电路实现nand门系统。集成电路包括耦合到第一p型肖特基二极管的阴极的第一输入和耦合到x个附加p型肖特基二极管的x个相应的阴极的x个附加输入。该集成电路另外包括第一n型晶体管,该第一n型晶体管包括耦合至第一肖特基二极管的阳极和x个附加肖特基二极管的x个阳极的栅极节点。集成电路还包括p型晶体管,该p型晶体管包括耦合至第一肖特基二极管的阳极和x个附加肖特基二极管的x个相应的阳极

的栅极节点。集成电路还包括第二n型晶体管,该第二n型晶体管包括耦合至第一p型肖特基二极管的阴极和x个附加n型晶体管的栅极节点,该x个附加n型晶体管包括耦合至x个附加p型肖特基二极管的x个的相应阴极的x个相应的栅极节点。输出耦合到第一n型晶体管的非栅极节点和p型晶体管的非栅极节点。

8.在一些实施例中,集成电路实现nor门系统。集成电路包括耦合到第一n型肖特基二极管的阳极的第一输入和耦合到x个附加n型肖特基二极管的x个相应的阳极的x个附加输入。该集成电路另外包括第一p型晶体管,该第一p型晶体管包括耦合至第一n型肖特基二极管的阴极和x个附加n型肖特基二极管的阴极的栅极节点。集成电路另外包括n型晶体管,该n型晶体管包括耦合到第一n型肖特基二极管的阴极和x个附加n型肖特基二极管的阴极耦合的栅极节点。集成电路另外包括第二p型晶体管,该第二p型晶体管包括耦合至第一n型肖特基二极管的阳极和x个附加p型晶体管的栅极节点,该x个附加p型晶体管包括耦合至x个附加n型肖特基二极管的x个相应的阳极的栅极节点。输出耦合到第一p型晶体管的非栅极节点和n型晶体管的非栅极节点。

9.在一些实施例中,集成电路实现x输入逻辑门。该集成电路包括多个肖特基二极管,该多个肖特基二极管包括x个肖特基二极管以及包括x个源极跟随器晶体管的多个源极跟随器晶体管。多个源极跟随器晶体管中的每个相应的源极跟随器晶体管包括耦合到相应的肖特基二极管的相应的栅极节点。多个源极跟随器晶体管中的第一源极跟随器晶体管串联连接至多个源极跟随器晶体管中的第二源极跟随器晶体管。

10.根据下面的描述,所公开的技术的各种优点将是显而易见的。

附图说明

11.作为在结合附图时的优选实施例的详细描述的结果,在下文中将更清楚地理解本公开的前述特征和优点以及其附加特征和优点。

12.为了更清楚地说明根据本发明实施例的技术方案,下面简要介绍实施例所需要的附图。然而,附图仅示出了本公开的更相关的特征,并且因此不应被认为是限制性的,因为描述可以允许其他有效特征。

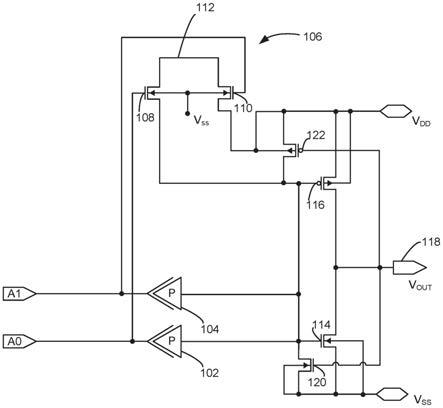

13.图1是根据一些实施例的二输入肖特基cmos nand门的电路图。

14.图2是根据一些实施例的八输入肖特基cmos nand门的电路图。

15.图3是8输入cmos nand门的电路图。

16.图4是根据一些实施例的二输入肖特基cmos nor门的电路图。

17.图5是根据一些实施例的八输入肖特基cmos nor门的电路图。

18.图6是8输入cmos nor的电路图。

19.图7是根据一些实施例的4对1复用器电路的肖特基cmos实施方式的电路图。

20.图8示出了4对1复用器电路的cmos实施方式。

21.图9是根据一些实施例的将使用肖特基cmos实现的nand门的布局面积与使用cmos实现的nand门的布局面积进行比较的图表。

22.图10是根据一些实施例的将使用肖特基cmos实现的nand门的均方根(rms)功率消耗与使用cmos实现的nand门的功率消耗进行比较的图表。

23.图11是根据一些实施例的将使用肖特基cmos实现的nand门的传播延迟与使用

nand门包括八个p型肖特基二极管202

‑

216和包括八个n型晶体管220

‑

234的源极跟随器树218。源极跟随器树218中的晶体管220

‑

234串联连接(例如,晶体管220的漏极节点耦合到晶体管224的源极节点,晶体管224的漏极节点耦合到晶体管228的源极节点,等等)。输入a0耦合到p型sbd 202的阴极和n型晶体管220的栅极节点。输入a1耦合到p型sbd 204的阴极和n型晶体管222的栅极节点。输入a2耦合到p型sbd 206的阴极和n型晶体管224的栅极节点。输入a3耦合到p型sbd 208的阴极和n型晶体管226的栅极节点。输入a4耦合到p型sbd 210的阴极和n型晶体管228的栅极节点。输入a5耦合到p型sbd 212的阴极和n型晶体管230的栅极节点。输入a6耦合到p型sbd 214的阴极和n型晶体管232的栅极节点。输入a7耦合到p型sbd 216的阴极和n型晶体管234的栅极节点。

34.sbd 202

‑

216的阳极耦合到结果晶体管236和238的栅极。结果晶体管236是n型晶体管,并且结果晶体管238是p型晶体管。输出240耦合到结果晶体管236和238的非栅极节点。具体地,输出240耦合到n型晶体管236的漏极节点,而输出240耦合到p型晶体管238的漏极节点。

35.在一些实施例中,八输入肖特基cmos nand门包括在n型晶体管242和p型晶体管244的栅极节点处接收输出信号作为输入的反馈逻辑。

36.将认识到的是,关于图1至图2示出的缩放可以被扩展到其他数量的nand门输入。对于每个附加输入,将附加sbd耦合到附加输入,并将与sbd互补的附加源极跟随器晶体管(例如,与p型sbd互补的n型晶体管)添加到源极跟随器树(例如,如图1的源极跟随器树106或图2的源极跟随器树218所示)。附加输入耦合到附加sbd(例如,耦合到p型sbd的阴极)和附加源极跟随器晶体管的栅极节点。附加sbd被耦合(例如,p型sbd的阳极)到结果晶体管集合(例如,如图1的结果晶体管114

‑

116或图2的结果晶体管236

‑

238所示)的栅极节点。

37.例如,四输入肖特基cmos nand门包括四个输入a0

‑

a3,四个p型sbd(例如,如图2的sbd 202

‑

208所示配置)和四个n型晶体管(例如,串联连接的图2的220、222、224和226所示的晶体管)。

38.在一些实施例中,肖特基cmos nand门包括在两个输入和十六个输入之间的多个输入,诸如十二个输入。

39.图3是8输入cmos nand门的电路图。cmos 8输入nand门需要三个nand门302、304和306,nor门308,以及逆变器310和312。与关于图2所描述的肖特基cmos八输入nand门相比,如图3所示的馈入nor门308的nand门302

‑

306的堆叠配置需要增加的功率和增加的供应电流,并且导致增加的布局面积、增加的开关时间和增加的传播延迟(如下文关于图9

‑

12进一步描述的)。

40.图4是根据一些实施例的二输入肖特基cmos nor门的电路图。二输入肖特基cmos nor门包括两个n型肖特基二极管402和404以及包括两个p型晶体管408和410的源极跟随器树406。源极跟随器树406中的晶体管串联连接。输入a0耦合到n型肖特基势垒二极管(sbd)402的阳极和p型晶体管408的栅极节点。输入a1耦合到n型sbd 404的阳极和p型晶体管410的栅极节点。sbd 402的阴极和sbd 404的阴极耦合到结果晶体管414和416的栅极。结果晶体管414是n型晶体管,结果晶体管416是p型晶体管。输出418耦合到结果晶体管414和416的非栅极节点。具体地说,输出418耦合到n型晶体管414的漏极节点,而输出118耦合到p型晶体管416的漏极节点。

41.在一些实施例中,二输入肖特基cmos nor门包括在n型晶体管420和p型晶体管422的栅极节点处接收输出信号作为输入的反馈逻辑。

42.尽管二输入nor门的cmos实施方式将使用耦合到nor门的每个输入的p型晶体管和n型晶体管,但是在一些实施例中,二输入nor门的肖特基cmos实施方式使用耦合到每个输入的n型sbd和p型晶体管(用肖特基cmos实施方式中的n型sbd代替现有cmos实施方式的n型晶体管)。随着nor门中输入数量的增加,用sbd替换晶体管所获得的效率也随之提高。

43.图5是根据一些实施例的八输入肖特基cmos nor门的电路图。八输入肖特基cmos nor门包括八个n型肖特基二极管502

‑

516和包括八个n型晶体管520

‑

534的源极跟随器树518。源极跟随器树518中的晶体管520

‑

534串联连接(例如,晶体管520的漏极节点耦合到晶体管524的源极节点,晶体管524的漏极节点耦合到晶体管528的源极节点,等等)。输入a0耦合到n型sbd 502的阳极和p型晶体管520的栅极节点。输入a1耦合到n型sbd 504的阳极和p型晶体管522的栅极节点。输入a2耦合到n型sbd 506的阳极和p型晶体管524的栅极节点。输入a3耦合到n型sbd 508的阳极和p型晶体管526的栅极节点。输入a4耦合到n型sbd 510的阳极和p型晶体管528的栅极节点。输入a5耦合到n型sbd 512的阳极和p型晶体管530的栅极节点。输入a6耦合到n型sbd 514的阳极和p型晶体管532的栅极节点。输入a7耦合到n型sbd 516的阳极和p型晶体管534的栅极节点。

44.sbd 502

‑

516的阴极耦合到结果晶体管536和538的栅极。结果晶体管536是n型晶体管,并且结果晶体管538是p型晶体管。输出540耦合到结果晶体管536和538的非栅极节点。具体地,输出540耦合到n型晶体管536的漏极节点,而输出540耦合到p型晶体管538的漏极节点。

45.在一些实施例中,八输入肖特基cmos nor门包括在n型晶体管542和p型晶体管544的栅极节点处接收输出信号作为输入的反馈逻辑。

46.将认识到的是,关于图4至图5示出的规模可以被扩展到其他数量的nor门输入。对于每个附加输入,将附加sbd耦合到附加输入,并且将与sbd互补的附加源极跟随器晶体管(例如,与n型sbd互补的p型晶体管)添加到源极跟随器树(例如,如图4的源极跟随器树406或图5的源极跟随器树518所示)。附加输入耦合到附加sbd(例如,耦合到n型sbd的阴极)和附加源极跟随器晶体管的栅极节点。附加sbd被耦合(例如,p型sbd的阳极)到一组结果晶体管(例如,如图4的结果晶体管414

‑

416或图4的结果晶体管536

‑

538所示)的栅极节点。

47.例如,四输入肖特基cmos nor门包括四个输入a0

‑

a3,四个n型sbd(例如,如图5的sbd 502

‑

508所示配置)和四个p型晶体管(例如,串联连接的图5的520、522、524和526所示的晶体管)。

48.在一些实施例中,肖特基cmos nor门包括在两个输入与十六个输入之间的多个输入,诸如十二个输入。

49.图6是8输入cmos nor门的电路图。cmos 8输入nor门需要四个二输入nand门602、604、606和608,两个二输入nand门610和612,二输入nor门614以及逆变器616和618。与关于图5描述的肖特基cmos八输入nor门相比,如图6所示,馈入nand门610和612、其继而馈入nor门614的nor门602

‑

608的堆叠配置需要增加的功率和增加的供应电流,并且导致增加的布局面积、增加的开关时间和增加的传播延迟。

50.图7是根据一些实施例的4对1复用器电路(mux)的肖特基cmos实施方式的电路图。

肖特基cmos mux将输入i1耦合到p型sbd 702和n型晶体管704的栅极节点。输入i2、i3和i4类似地各自耦合到p型sbd和n型晶体管的栅极节点。p型sbd 702和晶体管704的输出耦合到n型sbd 706和p型晶体管708。从i2、i3和i4接收输入的sbd和晶体管的输出类似地各自耦合到n型sbd和p型晶体管。n型sbd的输出耦合到p型结果晶体管710的栅极节点和n型结果晶体管712的栅极节点。结果晶体管的输出由输出714接收。

51.图8示出了4对1复用器电路的cmos实施方式。

52.在一些实施例中,关于图1、图2、图4、图5和/或图7描述的肖特基cmos逻辑被配置用于异步(例如,静态)操作。例如,选择一个或多个组件的大小,使得电路的操作是异步的或基本上异步的。在一些实施例中,选择肖特基cmos逻辑的一个或多个组件的大小以减小和/或最小化开关噪声抗扰性。

53.在一些实施例中,关于图1、图2、图4、图5和/或图7描述的肖特基cmos逻辑的一个或多个sbd具有阈值正向电压,该阈值正向电压低于具有耦合至sbd的栅极的晶体管的阈值正向电压(例如,其中,晶体管和sbd两者耦合至栅极的输入)。例如,参考图1,在一些实施例中,sbd 102具有低于晶体管108的阈值正向电压的阈值正向电压和/或sbd 104具有低于晶体管110的阈值正向电压的阈值正向电压。参考图2,在一些实施例中,sbd 202具有低于晶体管220的阈值正向电压的阈值正向电压,sbd 204具有低于晶体管222的阈值正向电压的阈值正向电压,和/或sbd 206具有低于晶体管224的阈值正向电压的阈值正向电压,等等。参考图4,在一些实施例中,sbd 402具有低于晶体管408的阈值正向电压的阈值正向电压和/或sbd 404具有低于晶体管410的阈值正向电压的阈值正向电压。参考图5,在一些实施例中,sbd 502具有低于晶体管520的阈值正向电压的阈值正向电压,sbd 504具有低于晶体管522的阈值正向电压的阈值正向电压,和/或sbd 506具有低于晶体管524的阈值正向电压的阈值正向电压,等等。参考图7,在一些实施例中,sbd 702具有低于晶体管704的阈值正向电压的阈值正向电压。

54.图9是根据一些实施例的将使用肖特基cmos(例如,如图1

‑

2所示)实现的nand门的布局面积与使用cmos(例如,如图3所示)实现的nand门的布局面积进行比较的图表。从图9能够看出,与随着输入数量的增加而增加cmos nand门的面积相比,肖特基cmos nand门的面积以较低的速率增加。图9表示四输入肖特基cmos nand门所需的布局面积小于2.0μm2,这显著小于四输入cmos nand门所需的面积。与具有相同输入数量的cmos nand门相比,具有三个或更多输入的肖特基cmos nand门所需的面积减少是由于例如减少的实现逻辑所需的信号线和/或电路网的数量,以及与cmos nand门的布局(例如,如图3和图6所示)相比相对较小的源极跟随器树的尺寸(例如,如106、218、406和518所示)。

55.图10是根据一些实施例的将使用肖特基cmos(例如,如图1

‑

2所示)实现的nand门的均方根(rms)功耗与使用cmos(例如,如图3所示)实现的nand门的功耗进行比较的图表。从图图10能够看出,与随着输入数量增加而cmos nand门所需的功率增加相比,肖特基cmos nand门所需的功率以较低的速率增加。图10表示四输入肖特基cmos nand门的rms功率要求小于50.0微瓦,这显著低于四输入cmos nand门所需的功率。

56.图11是根据一些实施例的将使用肖特基cmos(例如,如图1

‑

2所示)实现的nand门的传播延迟与使用cmos(例如,如图3所示)实现的nand门的传播延迟进行比较的图表。图11表示四输入肖特基cmos nand门具有小于80皮秒的传播延迟,这显著小于四输入cmos nand

门的传播延迟。

57.从图11能够看出,随着输入数量从三个输入增加到四个输入以及从六个输入增加到七个输入,cmos nand门的传播延迟表现出特别明显的增加。可以参考图12a至图12g来理解随着输入数量的增加,在nand门的cmos实施方式中出现的所需面积,功耗和传播延迟的明显增加。

58.图12a

‑

12g示出了具有各种输入数量的nand门的cmos实施方式。

59.图12a示出了使用单个二输入nand门1202实现的二输入nand逻辑。图12b示出了使用单个三输入nand门1204实现的三输入nand逻辑。

60.图12c示出了使用两个nand门1206和108以及nor门1210实现的四输入nand逻辑。当nand输入的数量从如图12b所示的三个输入增加到如图12c所示的四个输入时,使用两个nand门1206和1208(而不是图12b的单个nand门1204)以及添加nor门1210增加了通过电路的传播延迟。如图11所示,这种增加反映在传播延迟从用于三输入cmos nand的小于80皮秒到用于四输入cmos nand的大于120皮秒的传播延迟的跃升中。

61.图12d

‑

12e分别示出了五输入和六输入cmos nand门。类似于图12c所示的四输入cmos nand,五输入和六输入cmos nand门将两个nand门的输出馈送到nor门。图12d的cmos nand门将nand门1212和1214的输出馈送到nor门1216。图12e的cmos nand门将nand门1218和1220的输出馈送到nor门1222。

62.图12f示出了使用三个nand门1224、1226和1228以及nor门1230实现的七输入nand逻辑。当nand输入的数量从如图12e所示的六个输入增加到如图12f所示的七个输入时,使用三个nand门(1224、1226和1228)而不是图12e的两个nand门(1218、1220)增加了通过电路的传播延迟。如图11所示,这种增加反映在传播延迟中从用于六输入cmos nand的小于140皮秒到用于七输入cmos nand的近180皮秒的传播延迟的跃升中。

63.图12g示出了具有与关于图3描述的八输入cmos nand门相似的电路结构的八输入cmos nand门。图12g的cmos nand门将nand门1232、1234和1236的输出馈送到nor门1238。

64.如上关于图12a

‑

12g的cmos nand门所述,增加cmos nand门的输入数量需要增加nand门的数量和/或添加nor级。在一些实施例中(例如,如关于图1

‑

2和图4

‑

5所描述的),增加肖特基cmos nand门的输入的数量包括增加sbd的数量和增加源极跟随器树中的对应的晶体管的数量。在一些实施例中,与cmos方法相比,本文描述的肖特基cmos方法导致随着逻辑输入数量的增加,功耗、布局面积和传播延迟的增加更低。

65.尽管以上描述了特定实施例,但是将理解,其不旨在将本公开限制于这些特定实施例。相反,本公开包括在所附权利要求的精神和范围内的替选、修改和等同物。阐述了许多具体细节以便提供对本文提出的主题的透彻理解。但是对于本领域的普通技术人员将显而易见的是,可以在没有这些具体细节的情况下实践本主题。在其他情况下,未详细描述公知的方法、过程、组件和电路,以免不必要地使实施例的各方面不清楚。

66.在本文的公开的描述中使用的术语仅出于描述特定实施例的目的,并且不旨在限制本公开。如在本公开和所附权利要求书的描述中所使用的,单数形式“一(a/an)”和“该(the)”也旨在包括复数形式,除非上下文另外明确指出。还应理解,本文所用的术语“和/或”是指并涵盖相关联所列项目中的一个或多个的任何和所有可能的组合。将进一步理解的是,当在本说明书中使用时,术语“包括(includes)”,“包括(including)”,“包含

(comprises)”和/或“包含(comprising)”规定了陈述的特征、操作、元件和/或组件的存在,但是不排除一个或多个其他特征、操作、元件、组件和/或其组的存在或增加。

67.如本文中所使用的,具体取决于上下文,术语“如果”可被解释为意指陈述的先决条件为真的“当”或“在

……

时”或“响应于确定”或“根据确定”或“响应于检测”。类似地,取决于上下文,短语“如果确定[陈述的先决条件为真]”或“如果[陈述的先决条件为真]”或“当[陈述的先决条件为真]时”可解释为陈述的先决条件为真的“当确定

……

时”或“响应于确定”或“根据确定”或“根据检测”或“响应于检测”。

[0068]

为了解释的目的,已经参考特定实施例描述了前述描述。然而,以上说明性讨论并非旨在穷举或将本公开限制为所公开的精确形式。鉴于以上教导,许多修改和变化是可能的。选择和描述实施例是为了最好地解释本公开的原理及其实际应用,从而使本领域的其他技术人员能够最佳地利用本公开以及具有适于预期的特定用途的各种修改的各种实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。