1.本技术属于时钟数据恢复领域,尤其涉及一种频率跟踪电路及点对点接口装置、显示装置。

背景技术:

2.点对点接口装置中传输的交织信号包括数据信号和训练时钟信号,点对点接口装置的接收端需要通过时钟数据恢复电路根据训练时钟信号锁定采样信号以对上述数据信号进行采样。

3.随着显示面板尺寸及分辨率的不同,输入数据速度也会跟着增加,时钟数据恢复电路所要接收的数据的速率范围也会变宽。而传统的频率跟踪电路采用传统的锁相环对训练时钟信号进行锁定,由于交织信号的频率涵盖很大范围的频带,传统的锁相环无法应用在较大范围的频段上。

4.由于传统的频率跟踪电路的功能仅限于较窄频段上的频率锁定功能,故无法应用于较大范围的频带。

技术实现要素:

5.本技术的目的在于提供一种频率跟踪电路及点对点接口装置、显示装置,旨在解决传统的频率跟踪电路无法应用于较大范围的频带的问题。

6.本技术实施例的提供了一种频率跟踪电路,包括:

7.信号判决电路,配置为当接入交织信号时,对所述交织信号进行检测,当检测结果为训练时钟信号时,输出使能信号,当检测结果为数据信号时,停止输出所述使能信号;所述交织信号包括所述训练时钟信号和所述数据信号;

8.频率检测电路,与所述信号判决电路连接,配置为根据所述使能信号对所述交织信号进行频率检测以输出频率侦测信号;

9.锁相环电路,与所述频率检测电路和所述信号判决电路连接,配置为根据所述使能信号和所述频率侦测信号对所述训练时钟信号进行频率锁定以输出采样时钟。

10.在其中一个实施例中,所述信号判决电路包括:

11.第一计数器,配置为对所述交织信号进行计数,当所述第一计数器的计数达到第一计数阈值时输出第一触发信号并回零以重新计数;

12.第二计数器,与所述第一计数器连接,配置为对本地时钟进行计数,并根据所述第一触发信号回零以重新计数;

13.最大数检测电路,与所述第一计数器和所述第二计数器连接,配置为当接收到所述第一触发信号时,记录于预设时间内所述第二计数器输出的最大值并输出;

14.最小数检测电路,与所述第一计数器和所述第二计数器连接,配置为当接收到所述第一触发信号时,记录于预设时间内所述第二计数器输出的最小值并输出;

15.第一比较电路,与所述最大数检测电路、所述最小数检测电路、所述第一计数器以

及所述第二计数器连接,配置为当接收到所述第一触发信号时,记录所述第二计数器输出的第一计数结果,并在所述第一计数结果大于或等于预设值时输出使能信号,且在所述第一计数结果小于所述预设值时停止输出所述使能信号.

16.在其中一个实施例中,所述预设值为所述最大值和所述最小值的平均值。

17.在其中一个实施例中,所述频率检测电路包括:

18.启动信号生成电路,与所述信号判决电路连接,配置为根据使能信号和第二触发信号生成启动信号;

19.第三计数器,与所述启动信号生成电路连接,配置为当接收到所述启动信号时对所述交织信号进行计数,且当所述第三计数器的计数达到第二计数阈值时输出所述第二触发信号并回零以重新计数;

20.第四计数器,与所述第三计数器连接,配置当接收到所述启动信号时为对内部时钟进行计数,且根据所述第二触发信号回零以重新计数;

21.第二比较器,与所述启动信号生成电路和所述第四计数器连接,所述配置为根据所述启动信号检测当接收所述第二触发信号时所述第四计数器的第二计数结果,并根据所述第二计数结果生成所述频率侦测信号。

22.在其中一个实施例中,所述启动信号生成电路包括:

23.延时反相组件,与所述信号判决电路连接,配置为对所述使能信号进行延时和反相以输出第一逻辑信号;

24.与门组件,与所述信号判决电路和所述延时反相组件连接,配置为对所述第一逻辑信号和所述使能信号进行与运算以输出第二逻辑信号;

25.rs触发器,与所述与门组件和所述第三计数器连接,配置为将所述第二逻辑信号作为置位信号,并将所述第二触发信号作为复位信号以输出所述启动信号。

26.在其中一个实施例中,所述锁相环电路包括:

27.鉴频鉴相器,配置为当输入所述交织信号时,检测所述交织信号和第一时钟信号的相位差及频率差,并根据所述相位差及所述频率差输出第一控制信号及第二控制信号;

28.电荷泵,与所述鉴频鉴相器和所述频率检测电路连接,配置为根据所述第一控制信号、所述第二控制信号和所述频率侦测信号进行充放电,以输出第一控制电压;

29.低通滤波器,与所述电荷泵和压控振荡器连接,配置为对所述第一控制电压进行滤波;

30.压控振荡器,与所述低通滤波器和所述频率检测电路连接,配置为根据所述频率侦测信号输出频率与滤波后的所述第一控制电压的电压模拟量成正比的采样时钟;

31.分频组件,与所述压控振荡器、所述鉴频鉴相器以及所述信号判决电路连接,配置为根据所述使能信号对所述采样时钟进行倍频以输出所述第一时钟信号。

32.在其中一个实施例中,所述分频组件包括:

33.分频器,配置为对所述采样时钟进行倍频以输出第二时钟信号;

34.复用器,配置为基于所述使能信号将所述第二时钟信号或所述采样时钟作为所述第一时钟信号输出。

35.在其中一个支持四个频段的实施例中,所述电荷泵包括第一电流源、第二电流源、第三电流源、第四电流源、第五电流源、第六电流源、第一开关元件、第二开关元件、第三开

关元件、第四开关元件、第五开关元件、第六开关元件、第一电阻以及第一电容;

36.所述第一电流源的正极、所述第二电流源的正极以及所述第三电流源的正极共接,所述第二电流源的负极与所述第一开关元件的输入端连接,所述第三电流源的负极与所述第二开关元件的输入端连接,所述第一电流源的负极、所述第一开关元件的输出端、所述第二开关元件的输出端共同连接至所述第五开关元件的输入端,所述第四电流源的正极、所述第三开关元件的输入端以及所述第四开关元件的输入端共同连接至所述第六开关元件的输出端,所述第五开关元件的输出端、所述第六开关元件的输入端以及所述第一电阻的第一端共同连接至所述电荷泵的第一控制电压输出端,所述第三开关元件的输出端与所述第五电流源的正极连接,所述第四开关元件的输出端与所述第六电流源的正极连接,所述第一电阻的第二端与所述第一电容的第一端连接,所述第一开关元件的控制端、所述第二开关元件的控制端、所述第三开关元件的控制端以及所述第四开关元件的控制端共同连接至所述电荷泵的频率侦测信号输入端,所述第五开关元件的控制端连接至所述电荷泵的第一控制信号输入端,所述第六开关元件的控制端连接至所述电荷泵的第二控制信号输入端,所述第四电流源的负极、所述第五电流源的负极、所述第六电流源的负极以及所述第一电容的第二端共接于电源地。

37.本实用新型还提供一种点对点接口装置,所述点对点接口装置包括如上述的频率跟踪电路。

38.本实用新型还提供一种显示装置,所述显示装置包括如上述的频率跟踪电路。

39.本实用新型实施例与现有技术相比存在的有益效果是:由于锁相环电路可以根据不同的频率侦测信号设置运行参数以对所述交织信号中的训练时钟信号进行频率锁定以输出采样时钟,从而频率跟踪电路可以工作在较大的频率范围,拓宽了频率跟踪电路的工作频带。

附图说明

40.为了更清楚地说明本实用新型实施例中的技术实用新型,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

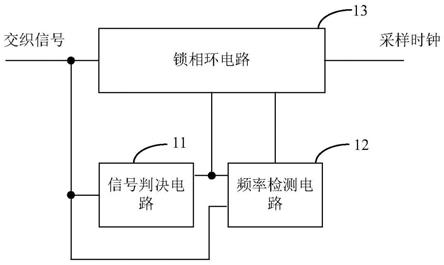

41.图1为本技术一实施例提供的频率跟踪电路的一种结构示意图;

42.图2为本技术一实施例提供的4b5b代码转换关系图;

43.图3为本技术一实施例提供的使用4b5b代码编码的数据流的一种示意图;

44.图4为本技术一实施例提供的频率跟踪电路中信号判决电路的一种结构示意图;

45.图5为本技术一实施例提供的频率跟踪电路中信号判决电路的一种时序图;

46.图6为本技术一实施例提供的频率跟踪电路中信号判决电路的另一种时序图;

47.图7为本技术一实施例提供的频率跟踪电路中频率检测电路的一种结构示意图;

48.图8为本技术一实施例提供的频率跟踪电路中启动信号生成电路的一种结构示意图;

49.图9为本技术一实施例提供的频率跟踪电路中启动信号生成电路的一种时序图;

50.图10为本技术一实施例提供的频率跟踪电路中锁相环电路的一种结构示意图;

51.图11为本技术一实施例提供的频率跟踪电路中分频组件的一种结构示意图;

52.图12为本技术一实施例提供的频率跟踪电路中电荷泵的一种示例电路原理图;

53.图13为传统的锁相环电路中采样时钟频段和第一控制电压的关系示意图;

54.图14为本技术一实施例提供的锁相环电路中采样时钟频段和第一控制电压的关系示意图。

具体实施方式

55.为了使本技术所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

56.需要说明的是,当组件被称为“固定于”或“设置于”另一个组件,它可以直接在另一个组件上或者间接在该另一个组件上。当一个组件被称为是“连接于”另一个组件,它可以是直接连接到另一个组件或间接连接至该另一个组件上。

57.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或组件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

58.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

59.图1示出了本技术较佳实施例提供的频率跟踪电路的结构示意图,为了便于说明,仅示出了与本实施例相关的部分,详述如下:

60.上述频率跟踪电路包括信号判决电路11、频率检测电路12以及锁相环电路13。

61.信号判决电路11,配置为当接入交织信号时,对交织信号进行检测,当检测结果为训练时钟信号时,输出使能信号,当检测结果为数据信号时,停止输出使能信号;交织信号包括训练时钟信号和数据信号。

62.频率检测电路12,与信号判决电路11连接,配置为根据使能信号对交织信号中的训练时钟信号进行频率检测以输出频率侦测信号。

63.锁相环电路13,与频率检测电路12和信号判决电路11连接,配置为根据使能信号和频率侦测信号对训练时钟信号进行频率锁定以输出采样时钟。

64.通过信号判决电路11当检测结果为训练时钟信号时,输出使能信号;频率检测电路12根据使能信号对交织信号进行频率检测以输出频率侦测信号;使得锁相环电路13可以根据不同的频率侦测信号设置运行参数以对交织信号中的训练时钟信号进行频率锁定以输出采样时钟;从而频率跟踪电路可以工作在较大的频率范围;随着显示面板尺寸及分辨率的不同,输入数据速度也会跟着变化,所以有着频率跟踪电路的时钟数据恢复电路能应用在不同分辨率的面板。

65.作为示例而非限定,交织信号可以为4b5b代码信号,4b5b代码是一种用于在通信信道传送任意数据的编码技术,使用4b5b代码可以减少位元冲突。4b5b代码转换关系图如

图2所示,4位数据被编码为5位代码,每个4位数据可从两个5位代码编码。如果先前的代码以“0”结尾,则使用左列代码。如果先前的代码以“1”结尾,则使用右列代码。预设情况下,编码数据流以先前的“0”开头,即第一个数据使用左列代码。

66.图3为使用4b5b代码编码的数据流的一种示意图。当输入数据流中最大有10个0,而4b5b代码数据流即只有连续3个或更少的1或0游程,减少了位元冲突。

67.如图4所示,信号判决电路11包括第一计数器111、第二计数器112、最大数检测电路113、最小数检测电路114以及第一比较电路115。

68.第一计数器111,配置为对交织信号进行计数,当第一计数器111的计数达到第一计数阈值时输出第一触发信号并回零以重新计数。

69.第二计数器112,与第一计数器111连接,配置为对本地时钟进行计数,并根据第一触发信号回零以重新计数。

70.最大数检测电路113,与第一计数器111和第二计数器112连接,配置为当接收到第一触发信号时,记录于预设时间内第二计数器112输出的最大值并输出。

71.最小数检测电路114,与第一计数器111和第二计数器112连接,配置为当接收到第一触发信号时,记录于预设时间内第二计数器112输出的最小值并输出。

72.第一比较电路115,与最大数检测电路113、最小数检测电路114、第一计数器111以及第二计数器112连接,配置为当接收到第一触发信号时,记录第二计数器112输出的第一计数结果,并在第一计数结果大于或等于预设值时输出使能信号,且在第一计数结果小于预设值时停止输出使能信号。其中,所述预设值可以为所述最大值和所述最小值的平均值。具体实施中,输出使能信号可以为输出高电平信号,停止输出使能信号可以为停止输出高电平信号且输出低电平信号。

73.具体地,信号判决电路11的时序图如图5和图6所示。第一计数器111为8位计数器,输入利用上升沿触发。第一计数器111每计数到256个上升沿,将输出一个脉冲(第一触发信号)。该脉冲是第二计数器112的清除信号,该脉冲同时也是最大数检测电路113、最小数检测电路114和第一比较电路115的启用信号或锁存信号。第二计数器112对本地时钟(例如40mhz时钟)进行计数,当输入的交织信号是数据信号(如4b5b编码数据信号)时,第二计数器112转换频率较大,第二计数器112被置为0之前的计数时间数较少,计数器输出为较小的值。当输入的交织信号为训练时钟信号时,转换的频率降低。第二计数器112被置为0之前可以有更多计数时间,计数器输出为一个较大的值。平均而言,第二计数器在数据信号时的输出值是训练时钟信号时的输出值的两倍。每256个计数,最大数检测电路113、最小数检测电路114和第一比较电路115便会从第二计数器112中采样(即在清除第二计数器112之前)。例如,最大数检测电路113记录最近1/30秒从第二计数器112的最大计数输出。最小数检测电路114记录最近1/30秒从第二计数器112的最小计数输出。第一比较电路将第二计数器112输出的第一计数结果与最大值和最小值进行比较。如果第一计数结果接近最大值,则将输出高电平的使能信号。如果第一计数结果更接近最小值,则将输出低电平信号。

74.通过上述第一计数器111、第二计数器112、最大数检测电路113、最小数检测电路114以及第一比较电路115,提高了交织信号判断的准确性,精确地判断了交织信号位于数据信号区域或训练时钟信号区域,进而输出使能信号。

75.如图7所示,频率检测电路12包括启动信号生成电路121、第三计数器122、第四计

数器123以及第二比较器124。

76.启动信号生成电路121,与信号判决电路11连接,配置为根据使能信号和第二触发信号生成启动信号。

77.第三计数器122,与启动信号生成电路121连接,配置为当接收到启动信号时对交织信号进行计数,且当第三计数器122的计数达到第二计数阈值时输出第二触发信号并回零以重新计数。

78.第四计数器123,与第三计数器122连接,配置为当接收到启动信号时对内部时钟进行计数,且根据第二触发信号回零以重新计数。

79.第二比较器124,与启动信号生成电路121和第四计数器123连接,配置为根据启动信号检测当接收第二触发信号时第四计数器123的第二计数结果,并根据第二计数结果生成频率侦测信号。

80.具体地,因为在接收使能信号时,第三计数器122开始工作,所以第三计数器122对不同频率的交织信号中的训练时钟信号进行计数(每128个计数输出一个脉冲(第二触发信号)),该脉冲是第四计数器123的清除信号,该脉冲同时也是第二比较电路的启用信号。经过第四计数器123对内部时钟(例如40mhz时钟)进行计数后,可以得到不同的第二计数结果(例如,在支持四个频段,即有四种第二计数结果),再利用第二比较器124与预设值作比较以分为四个频段band<1:0>(即频率侦测信号)以设定锁相环电路13的频段(例如,锁相环电路13中电荷泵132的频段和锁相环电路13中压控振荡器133的频段)。

81.例如,若数据传输速率为1gbps,训练时钟信号为128mhz,第二计数结果为40,由于第二计数结果大于27,属于第一频段,输出的频率侦测信号为band<1:0>=00;若数据传输速率为2gbps,训练时钟信号为256mhz,第二计数结果为20,由于第二计数结果在17和27之间,属于第二频段,输出的频率侦测信号为band<1:0>=01;若数据传输速率为3gbps,训练时钟信号为384mhz,第二计数结果为14,由于第二计数结果在12和16之间,属于第三频段,输出的频率侦测信号为band<1:0>=10;若数据传输速率为4gbps,训练时钟信号为512mhz,第二计数结果为10由于第二计数结果小于12,属于第四频段,输出的频率侦测信号为band<1:0>=11。

82.通过启动信号生成电路121、第三计数器122、第四计数器123以及第二比较器124,实现了对交织信号中的训练时钟信号的频率检测,并提高了训练时钟信号的频率检测的准确性。并且通过根据第二计数结果设置锁相环电路13的频段,可弹性调整频段所对应的输入频率,提高了频率跟踪电路进行频率跟踪的灵活性。

83.如图8所示,启动信号生成电路121包括延时反相组件1211、与门组件1212和rs触发器1213。

84.延时反相组件1211,与信号判决电路11连接,配置为对使能信号进行延时和反相以输出第一逻辑信号。

85.与门组件1212,与信号判决电路11和延时反相组件1211连接,配置为对第一逻辑信号和使能信号进行与运算以输出第二逻辑信号。

86.rs触发器1213,与与门组件1212和第三计数器122连接,配置为将第二逻辑信号作为置位信号,并将第二触发信号作为复位信号以输出启动信号。

87.启动信号生成电路121的时序图如图9所示,通过延时反相组件1211、与门组件

1212和rs触发器1213,获取了频率检测电路12进行频率检测的时间段,在该时间段之后不再进行频率检测,故节约了电能。

88.如图10所示,锁相环电路13包括鉴频鉴相器131、电荷泵132、低通滤波器135、压控振荡器133以及分频组件134。

89.鉴频鉴相器131,配置为当输入交织信号时,检测交织信号和第一时钟信号的相位及频率差,并根据相位及频率差输出第一控制信号及第二控制信号。

90.电荷泵132,与鉴频鉴相器131、低通滤波器135和频率检测电路12连接,配置为根据第一控制信号、第二控制信号和频率侦测信号进行充放电,以输出第一控制电压。

91.低通滤波器135,与电荷泵132和压控振荡器133连接,配置为对第一控制电压进行滤波。

92.压控振荡器133,与低通滤波器135和频率检测电路12连接,配置为根据频率侦测信号输出频率与滤波后的第一控制电压的电压模拟量成正比的采样时钟。

93.分频组件134,与压控振荡器133、鉴频鉴相器131以及信号判决电路11连接,配置为根据使能信号对采样时钟进行倍频以输出第一时钟信号。

94.传统的锁相环调频采用侦测第一控制电压方式来切频,容易在频段的头尾端出现跳频带,而本技术同时调整压控振荡器133的频段以及电荷泵132的频段,更大范围地调节了锁相环调频的频带并且防止了跳频带的发生。

95.需要说明的是,若是需要涵盖较大的频带,一般压控振荡器133需要较大的调谐增益,但是会造成较大抖动,而抖动的大小对于频率跟踪电路的性能有绝对的影响,所以要维持低调谐增益的目的,就需要多频段的压控振荡器133。

96.如图11所示,分频组件134包括分频器1341和复用器1342。

97.分频器1341,配置为对采样时钟进行倍频以输出第二时钟信号。

98.复用器1342,配置为基于使能信号将第二时钟信号或采样时钟作为第一时钟信号输出。

99.通过分频器1341使频率跟踪电路实现了在频率跟踪的同时进行倍频,通过复用器1342实现了在交织信号为训练时钟信号时连通锁相环电路13的反馈回路。

100.图12示出了本实用新型实施例提供支持四个频段的频率跟踪电路中电荷泵132的一种示例电路结构,为了便于说明,仅示出了与本实用新型实施例相关的部分,详述如下:

101.电荷泵132包括第一电流源i1、第二电流源i2、第三电流源i3、第四电流源i4、第五电流源i5、第六电流源i6、第一开关元件k1、第二开关元件k2、第三开关元件k3、第四开关元件k4、第五开关元件k5、第六开关元件k6、第一电阻r1以及第一电容c1。

102.第一电流源i1的正极、第二电流源i2的正极以及第三电流源i3的正极共接,第二电流源i2的负极与第一开关元件k1的输入端连接,第三电流源i3的负极与第二开关元件k2的输入端连接,第一电流源i1的负极、第一开关元件k1的输出端、第二开关元件k2的输出端共同连接至第五开关元件k5的输入端,第四电流源i4的正极、第三开关元件k3的输入端以及第四开关元件k4的输入端共同连接至第六开关元件k6的输出端,第五开关元件k5的输出端、第六开关元件k6的输入端以及第一电阻r1的第一端共同连接至电荷泵132的第一控制电压输出端,第三开关元件k3的输出端与第五电流源i5的正极连接,第四开关元件k4的输出端与第六电流源i6的正极连接,第一电阻r1的第二端与第一电容c1的第一端连接,第一

开关元件k1的控制端、第二开关元件k2的控制端、第三开关元件k3的控制端以及第四开关元件k4的控制端共同连接至电荷泵132的频率侦测信号输入端,第五开关元件k5的控制端连接至电荷泵132的第一控制信号输入端,第六开关元件k6的控制端连接至电荷泵132的第二控制信号输入端,第四电流源i4的负极、第五电流源i5的负极、第六电流源i6的负极以及第一电容c1的第二端共接于电源地。

103.以下结合工作原理对图12所示的作进一步说明:

104.当频率侦测信号band<1:0>为00时,第一开关元件k1、第二开关元件k2、第三开关元件k3以及第四开关元件k4均断开,电荷泵132的电流为1*lcp。

105.当频率侦测信号band<1:0>为01时,第一开关元件k1和第三开关元件k3连通,第二开关元件k2以及第四开关元件k4均断开,电荷泵132的电流为2*lcp。

106.当频率侦测信号band<1:0>为10时,第一开关元件k1和第三开关元件k3断开,第二开关元件k2以及第四开关元件k4均连通,电荷泵132的电流为3*lcp。

107.当频率侦测信号band<1:0>为11时,第一开关元件k1、第二开关元件k2、第三开关元件k3以及第四开关元件k4均连通,电荷泵132的电流为4*lcp。第一电容c1根据电荷泵132的电流进行充放电,以使电荷泵132输出第一控制电压。

108.传统的锁相环电路根据固定的运行参数对交织信号进行频率锁定以输出采样时钟,频率范围较窄,容易在频段的头尾端出现跳频带或抖动,其采样时钟频段和第一控制电压的关系示意图如图13所示,在本技术的实施例中,锁相环电路可以根据不同的频率侦测信号设置运行参数以对所述交织信号进行频率锁定以输出采样时钟,其采样时钟频段和第一控制电压的关系示意图如图14所示,从而频率跟踪电路可以工作在较大的频率范围并且防止了跳频带的发生,增加了频率跟踪电路的工作频带。

109.本实用新型实施例还提供一种点对点接口装置,其特征在于,所述点对点接口装置包括如上述的频率跟踪电路。

110.本实用新型还提供一种显示装置,所述显示装置包括如上述的频率跟踪电路。

111.本实用新型实施例通过信号判决电路当接入交织信号时,对交织信号进行检测,当检测结果为训练时钟信号时,输出使能信号,当检测结果为数据信号时,停止输出使能信号;交织信号包括训练时钟信号和数据信号;频率检测电路根据使能信号对交织信号进行频率检测以输出频率侦测信号;锁相环电路根据使能信号和频率侦测信号对训练时钟信号进行频率锁定以输出采样时钟;由于锁相环电路可以根据不同的频率侦测信号设置运行参数以对所述交织信号进行频率锁定以输出采样时钟,从而频率跟踪电路可以工作在较大的频率范围并且防止了跳频带的发生,增加了频率跟踪电路的工作频带。

112.应理解,上述实施例中各步骤的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

113.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。