1.本实用新型涉及电子技术领域,尤其涉及一种防止升级锁死的电路及车载设备。

背景技术:

2.t

‑

box(telematics box,简称车载t

‑

box)属于车载设备,通常用于随车实时监测车子的运行状态。市面上大部分的t

‑

box类车载设备采用单片机(即mcu),利用单片机来实现数据的采集、处理、上传。由于单片机的处理能力较低,一般用于数据量较少的使用场景中。

3.更大处理能力的tbox类车载设备需要在单片机的基础上增加处理能力更强的嵌入式处理器,单片机在设备中负责实时性较强的信号处理,嵌入式处理器则负责大数据量的处理传输。

4.嵌入式系统通常会涉及升级问题,由于t

‑

box类车载设备无法支持有线升级,只能用空中升级的方式(ota升级)。ota(over the air technology)升级在升级时会存在不稳定的问题,特别是嵌入式处理器升级后还要升级单片机;由于通常是单片机控制嵌入式处理器的电源、则会出现互锁风险。如嵌入式处理器的系统在给单片机升级时,单片机出现异常就会关断嵌入式处理器的电源;嵌入式处理器的电源一断,就会立刻停止对单片机的程序升级,导致单片机程序不完整;单片机程序升级不完整反过来就影响车载设备正常开机,导致整个车载设备不能正常工作。一般情况下,会设计单片机在出厂后不能升级。虽然能避免互锁风险导致单片机程序升级失败,但是,一旦车载设备出厂后、单片机程序有问题,则无法解决得到有效的解决,影响车载设备的质量。

技术实现要素:

5.针对上述技术问题,本实用新型实施例提供了一种防止升级锁死的电路及车载设备,以解决现有单片机与嵌入式处理器升级时会锁死导致单片机程序不完整的问题。

6.本实用新型实施例提供一种防止升级锁死的电路,连接主处理器和协处理器,其包括降压模块、响应模块和电源管理模块;所述电源管理模块连接降压模块和响应模块,所述响应模块连接协处理器,电源管理模块连接主处理器;

7.所述降压模块对输入的电源电压进行降压后输出第一电压给电源管理模块;

8.所述响应模块根据协处理器输出的预设波形的开断电信号生成对应电平电源使能信号来控制电源管理模块的开关;

9.所述电源管理模块开启时根据第一电压生成若干个主处理器工作所需的电压、给主处理器供电,电源管理模块关闭时停止供电。

10.可选地,所述的防止升级锁死的电路中,所述降压模块包括电源芯片、第一电感、第一二极管、第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、第六电阻、第七电阻、第一电容、第二电容、第三电容、第四电容、第五电容和第六电容;

11.所述电源芯片的in脚输入电源电压、该in脚还通过第一电阻连接第二电阻的一

端、第一电容的一端和电源芯片的en/sync脚;第二电阻的另一端和第一电容的另一端均接地,电源芯片的rt脚通过第三电阻接地,电源芯片的bst脚通过第二电容连接第四电阻的一端和电源芯片的sw脚,第四电阻的另一端通过第三电容接地,电源芯片的sw脚连接第一电感的一端和第一二极管的负极,第一二极管的正极接地;第一电感的另一端是第一供电端、连接第五电阻的一端和第六电容的一端;电源芯片的fb脚连接第五电阻的另一端、第六电阻的一端和第六电容的另一端;第六电阻的另一端接地,电源芯片的comp脚连接第四电容的一端和第七电阻的一端,第四电容的另一端接地,第七电阻的另一端通过第五电容接地,电源芯片的gnd脚和pad脚均接地。

12.可选地,所述的防止升级锁死的电路中,所述降压模块还包括第七电容、第八电容、第九电容和第二二极管;

13.所述第七电容的一端连接第一电感的另一端、第六电容的一端和第二二极管的负极;第七电容的另一端接地,第八电容与第七电容并联,第九电容与第八电容并联,第二二极管的正极接地。

14.可选地,所述的防止升级锁死的电路中,所述响应模块包括比较器芯片、第三二极管、第四二极管、第八电阻、第九电阻、第十电阻、第十一电阻、第十电容和第十一电容;

15.所述第十电容的一端输入开断电信号,第十电容的另一端连接第三二极管的负极和第四二极管的正极,第三二极管的正极接地;第四二极管的负极连接第八电阻的一端、第十一电容的一端和比较器芯片的in

‑

脚;第八电阻的另一端连接第十一电容的另一端和地,比较器芯片的vee脚接地,比较器芯片的in 脚连接第九电阻的一端和第十电阻的一端,第九电阻的另一端连接第一供电端,第十电阻的另一端接地,比较器芯片的vcc脚连接第一供电端和第十一电阻的一端,比较器芯片的out脚连接第十一电阻的另一端和电源管理模块。

16.可选地,所述的防止升级锁死的电路中,所述响应模块还包括第十二电容和第十三电容;

17.所述第十二电容的一端连接比较器芯片的in 脚和第九电阻的一端,第十三电容的一端连接比较器芯片的vcc脚和第十一电阻的一端,第十二电容的另一端和第十三电容的另一端均接地。

18.可选地,所述的防止升级锁死的电路中,所述电源管理模块包括电源管理芯片、第二电感、第三电感、第四电感、第五电感、第十二电阻、第十三电阻、第十四电阻、第十五电阻、第十六电阻、第十七电阻、第十八电阻、第十九电阻、第二十电阻、第十四电容、第十五电容、第十六电容、第十七电容、第十八电容、第十九电容、第二十电容和第二十一电容;

19.所述电源管理芯片的vin1脚、vin2脚、vin3脚、vin4脚、vcc脚相互连接并均连接第一供电端;电源管理芯片的vcc脚连接第二十电阻的一端,电源管理芯片的en1脚至en4脚相互连接并均连接第二十电阻的另一端和比较器芯片的out脚;

20.所述电源管理芯片的lx1脚通过第二电感连接第十四电容的一端、第十二电阻的一端和第十五电容的一端;第十五电容的一端是第二供电端,连接主处理器;电源管理芯片的fb1脚连接第十四电容的另一端、第十二电阻的另一端和第十三电阻的一端;第十三电阻的另一端连接第十五电容的另一端和地;

21.所述电源管理芯片的lx2脚通过第三电感连接第十六电容的一端、第十四电阻的一端和第十七电容的一端;第十七电容的一端是第三供电端,连接主处理器;电源管理芯片

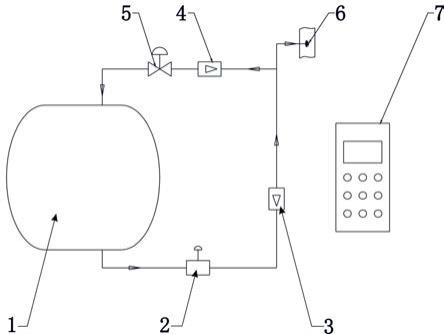

的fb2脚连接第十六电容的另一端、第十四电阻的另一端和第十五电阻的一端;第十五电阻的另一端连接第十七电容的另一端和地;

22.所述电源管理芯片的lx3脚通过第四电感连接第十八电容的一端、第十六电阻的一端和第十九电容的一端;第十九电容的一端是第四供电端,连接主处理器;电源管理芯片的fb3脚连接第十八电容的另一端、第十六电阻的另一端和第十七电阻的一端;第十七电阻的另一端连接第十九电容的另一端和地;

23.所述电源管理芯片的lx4脚通过第五电感连接第二十电容的一端、第十八电阻的一端和第二十一电容的一端;第二十一电容的一端是第五供电端,连接主处理器;电源管理芯片的fb4脚连接第二十电容的另一端、第十八电阻的另一端和第十九电阻的一端;第十九电阻的另一端连接第二十一电容的另一端和地。

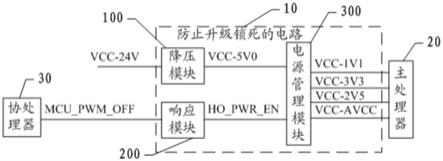

24.可选地,所述的防止升级锁死的电路中,所述电源管理芯片的vin1脚、vin2脚、vin3脚、vin4脚、vcc脚上分别通过一电容接地。

25.本实用新型实施例第二方面提供了一种车载设备,包括一主板,所述主板上设置有主处理器和协处理器,其中,所述主板上还设置有所述的防止升级锁死的电路;所述防止升级锁死的电路连接主处理器和协处理器;

26.所述防止升级锁死的电路根据协处理器输出的预设波形的开断电信号来控制对主处理器供电的通断。

27.可选地,所述的车载设备中,所述主处理器为嵌入式处理器,协处理器为单片机。

28.本实用新型实施例提供的技术方案中,车载设备包括一主板,所述主板上设置有主处理器、协处理器和防止升级锁死的电路;所述防止升级锁死的电路连接主处理器和协处理器;所述防止升级锁死的电路根据协处理器输出的预设波形的开断电信号来控制对主处理器供电的通断。只有满足预设的波形才能控制是否供电。而协处理器在升级出现异常时无法输出特定的波形,因此,当主处理器给协处理器在线升级时,协处理器不管处在何种异常状态都无法关断主处理器的电源,也就不会导致升级时异常断电使协处理器程序不完整、影响车载设备不能正常工作,将车载设备的系统损坏的问题。

附图说明

29.图1为本实用新型实施例中车载设备的结构框图。

30.图2为本实用新型实施例中降压模块的电路示意图。

31.图3为本实用新型实施例中响应模块的电路示意图。

32.图4为本实用新型实施例中电源管理模块的电路示意图。

具体实施方式

33.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。本实用新型中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

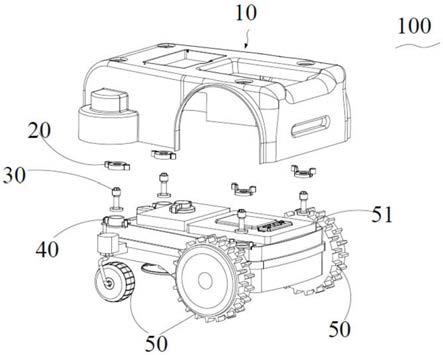

34.请参阅图1,本实用新型实施例提供的车载设备包括一主板,所述主板上设置有防止升级锁死的电路10、主处理器20和协处理器30;所述防止升级锁死的电路10连接主处理

器20和协处理器30;所述防止升级锁死的电路10根据协处理器30输出的预设波形的开断电信号mcu_pwm_off来控制对主处理器20供电的通断。

35.本实施例中,所述主处理器20为嵌入式处理器,协处理器30为单片机(即mcu),防止升级锁死的电路10适用于具有嵌入式处理器和单片机这两种处理器的t

‑

box产品。所述开断电信号mcu_pwm_off是由协处理器30产生的,是协处理器30关断和打开主处理器20电源的开关信号,属于pwm输出信号,其具有预设的特定的波形,只有满足预设的波形才能控制是否供电。而协处理器在升级出现异常时无法输出特定的波形,因此,当主处理器20给协处理器在线升级时,协处理器不管处在何种异常状态都无法关断主处理器20的电源,也就不会导致升级时异常断电使协处理器程序不完整、影响车载设备不能正常工作,将车载设备的系统损坏的问题。

36.需要理解的是,此处只是使用协处理器30输出的开断电信号mcu_pwm_off,协处理器30的具体电路结构和输出开断电信号的引脚为现有技术,此处不作详述。

37.所述防止升级锁死的电路10包括降压模块100、响应模块200和电源管理模块300;所述电源管理模块300连接降压模块100和响应模块200,所述响应模块200连接协处理器30,电源管理模块300连接主处理器20。所述降压模块100对输入的电源电压(24v)进行降压后输出第一电压(5v)给电源管理模块300;所述响应模块200根据协处理器30输出的预设波形的开断电信号mcu_pwm_off生成对应电平(高低电平)电源使能信号ho_pwr_en来控制电源管理模块300的开关(从而控制主处理器的开关机);所述电源管理模块300开启时根据第一电压生成若干个主处理器20工作所需的电压、给主处理器20供电,电源管理模块300关闭时停止供电。所述电源电压vcc

‑

24v由车载设备的obd(on

‑

board diagnostic)接口提供,是24v的直流电压。

38.请一并参阅图2,所述降压模块100包括电源芯片u1、第一电感l1、第一二极管d1、第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第五电容c5和第六电容c6;所述电源芯片u1的in脚输入电源电压(in脚连接obd接口的电源脚)、该in脚还通过第一电阻r1连接第二电阻r1的一端、第一电容c1的一端和电源芯片u1的en/sync脚;第二电阻r1的另一端和第一电容c1的另一端均接地,电源芯片u1的rt脚通过第三电阻r3接地,电源芯片u1的bst脚通过第二电容c2连接第四电阻r4的一端和电源芯片u1的sw脚,第四电阻r4的另一端通过第三电容c3接地,电源芯片u1的sw脚连接第一电感l1的一端和第一二极管d1的负极,第一二极管d1的正极接地;第一电感l1的另一端是第一供电端、连接第五电阻r5的一端和第六电容c6的一端;电源芯片u1的fb脚连接第五电阻r5的另一端、第六电阻r6的一端和第六电容c6的另一端;第六电阻r6的另一端接地,电源芯片u1的comp脚连接第四电容c4的一端和第七电阻r7的一端,第四电容c4的另一端接地,第七电阻r7的另一端通过第五电容c5接地,电源芯片u1的gnd脚和pad脚均接地。

39.其中,所述电源芯片u1优选型号为jw5116fesop的主dc

‑

dc开关电源芯片,属于buck型降压芯片,将输入的24v的电源电压vcc

‑

24v降压为5v的第一电压vcc

‑

5v0,从第一电感l1的另一端(第一供电端)输出。所述第一电感l1的另一端上预留一检测脚(即图中的圆圈),通过测量该检测脚上的电压值,即可方便了解第一电压是否正常输出。所述第一电阻r1、第二电阻r2和第一电容c1构成电源芯片u1的软启动使能电路,当电源芯片u1上电后(即

电源电压vcc

‑

24v输入后)延时一段时间再使能电源芯片u1的en/sync脚,使u1进入工作状态。所述第三电阻r3用于调节电源芯片u1工作时的开关频率。所述第二电容c2、第三电容c3和第四电阻r4构成自举电路,用于给u1内部的控制电路提供工作电压。所述第四电容c4、第五电容c5和第七电阻r7构成电源芯片u1的反馈补偿电路。所述第五电阻r5、第六电阻r6和第六电容c6构成电压反馈电路,用于调节第一供电端上输出的第一电压vcc

‑

5v0的大小。所述第一电感l1为开关电感,起到滤波、续流的作用。所述第一二极管d1为开关二极管,起到续流作用。

40.优选地,所述降压模块100还包括第七电容c7、第八电容c8、第九电容c9和第二二极管d2;所述第七电容c7的一端连接第一电感l1的另一端、第六电容c6的一端和第二二极管d2的负极;第七电容c7的另一端接地,第八电容c8与第七电容c7并联,第九电容c9与第八电容c8并联,第二二极管d2的正极接地。

41.其中,所述第七电容c7、第八电容c8和第九电容c9构成输出滤波电路,稳定输出的5v的第一电压vcc

‑

5v0。第二二极管d2为浪涌保护二极管,以防止第一电压的电源抖动,保护后级电路不会出现过压而损坏。

42.请一并参阅图3,所述响应模块200包括比较器芯片u2、第三二极管d3、第四二极管d4、第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、第十电容c10和第十一电容c11;所述第十电容c10的一端输入开断电信号mcu_pwm_off,第十电容c10的另一端连接第三二极管d3的负极和第四二极管d4的正极,第三二极管d3的正极接地;第四二极管d4的负极连接第八电阻r8的一端、第十一电容c11的一端和比较器芯片u2的in

‑

脚;第八电阻r8的另一端连接第十一电容c11的另一端和地,比较器芯片u2的vee脚接地,比较器芯片u2的in 脚连接第九电阻r9的一端和第十电阻r10的一端,第九电阻r9的另一端连接第一供电端,第十电阻r10的另一端接地,比较器芯片u2的vcc脚连接第一供电端和第十一电阻r11的一端,比较器芯片u2的out脚连接第十一电阻r11的另一端和电源管理模块300。

43.其中,所述开断电信号mcu_pwm_off是一种pwm信号,第三二极管d3、第四二极管d4、第八电阻r8、第十电容c10和第十一电容c11构成开断电信号的整流滤波电路;第三二极管d3为放电二极管,用于在开断电信号mcu_pwm_off的下降沿时快速释放掉第十电容c10上的电压。第四二极管d4用于整流,允许开断电信号mcu_pwm_off的上升沿通过,下降沿将截止。第八电阻r8和第十一电容c11组成rc滤波电路,将开断电信号mcu_pwm_off的脉冲信号滤波成稳定的电压;通过调整r8和c11的参数可以调整电路响应开断电信号mcu_pwm_off时的截止频率(本实施例为2khz)。第九电阻r9和第十电阻r10组成分压电路。

44.所述比较器芯片u2优选型号为tl331idbvr,通过比较in

‑

脚和in 脚的电压来从out脚输出对应的高低电平的电源使能信号ho_pwr_en。第十一电阻r11为输出的上拉电阻,正常时默认电源使能信号ho_pwr_en的电平为高电平。当开断电信号mcu_pwm_off是大于2khz的pwm信号输入时,in

‑

脚的电压高于in 脚,输出低电平的电源使能信号ho_pwr_en;当开断电信号mcu_pwm_off的信号频率小于2khz、或者输入持续的高电压或者低电压时,in

‑

脚的电压都会低于in 脚,输出高电平的电源使能信号ho_pwr_en。

45.优选地,所述响应模块200还包括第十二电容c12和第十三电容c13;所述第十二电容c12的一端连接比较器芯片u2的in 脚和第九电阻r9的一端,第十三电容c13的一端连接比较器芯片u2的vcc脚和第十一电阻r11的一端,第十二电容c12的另一端和第十三电容c13

的另一端均接地。

46.其中,第十二电容c12用于对r9和r10的分压电压进行滤波,使比较器芯片u2的比较结果更加准确。第十三电容c13为比较器芯片u2的电源输入的去耦电容。

47.请一并参阅图4,所述电源管理模块300包括电源管理芯片u3、第二电感l2、第三电感l3、第四电感l4、第五电感l5、第十二电阻r12、第十三电阻r13、第十四电阻r14、第十五电阻r15、第十六电阻r16、第十七电阻r17、第十八电阻r18、第十九电阻r19、第二十电阻r20、第十四电容c14、第十五电容c15、第十六电容c16、第十七电容c17、第十八电容c18、第十九电容c19、第二十电容c20和第二十一电容c21;所述电源管理芯片u3的vin1脚、vin2脚、vin3脚、vin4脚、vcc脚相互连接并均连接第一供电端;电源管理芯片u3的vcc脚连接第二十电阻r20的一端,电源管理芯片u3的en1脚、en2脚、en3脚、en4脚相互连接并均连接第二十电阻r20的另一端和比较器芯片u2的out脚。

48.所述电源管理芯片u3的lx1脚通过第二电感l2连接第十四电容c14的一端、第十二电阻r12的一端和第十五电容c15的一端;第十五电容c15的一端是第二供电端,连接主处理器;电源管理芯片u3的fb1脚连接第十四电容c14的另一端、第十二电阻r12的另一端和第十三电阻r13的一端;第十三电阻r13的另一端连接第十五电容c15的另一端和地。其中,第二电感l2为输出滤波电感,与第十五电容c15组成输出滤波电路。第十四电容c14、第十二电阻r12、第十三电阻r13构成输出电压反馈电路,用于调整输出电压。第十五电容c15的一端是第二供电端,l2、r12、r13、c14、c15构成1.1v dc

‑

dc电压输出电路,即第二供电端输出1.1v的第二电压vcc

‑

1v1给嵌入式处理器的内核供电(第二供电端连接嵌入式处理器的内核的供电端)。

49.所述电源管理芯片u3的lx2脚通过第三电感l3连接第十六电容c16的一端、第十四电阻r14的一端和第十七电容c17的一端;第十七电容c17的一端是第三供电端,连接主处理器;电源管理芯片u3的fb2脚连接第十六电容c16的另一端、第十四电阻r14的另一端和第十五电阻r15的一端;第十五电阻r15的另一端连接第十七电容c17的另一端和地。其中,第三电感l3为输出滤波电感,与第十七电容c17组成输出滤波电路。c16、r14、r15构成输出电压反馈电路,用于调整输出电压。第十七电容c17的一端是第三供电端,l3、r14、r15、c16、c17构成3.3v的dc

‑

dc电压输出电路,即第三供电端输出3.3v的第三电压vcc

‑

3v3给嵌入式处理器的i/o供电(第三供电端连接嵌入式处理器的i/o的供电端)。

50.所述电源管理芯片u3的lx3脚通过第四电感l4连接第十八电容c18的一端、第十六电阻r16的一端和第十九电容c19的一端;第十九电容c19的一端是第四供电端,连接主处理器;电源管理芯片u3的fb3脚连接第十八电容c18的另一端、第十六电阻r16的另一端和第十七电阻r17的一端;第十七电阻r17的另一端连接第十九电容c19的另一端和地。其中,第四电感l4为输出滤波电感,与第十九电容c19组成输出滤波电路。c18、r16、r17构成输出电压反馈电路,用于调整输出电压。第十九电容c19的一端是第四供电端,l4、r16、r17、c18、c19构成2.5v的dc

‑

dc电压输出电路,即第四供电端输出2.5v的第四电压vcc

‑

2v5给嵌入式处理器的ddr供电(即第四供电端连接嵌入式处理器的ddr的供电端)。

51.所述电源管理芯片u3的lx4脚通过第五电感l5连接第二十电容c20的一端、第十八电阻r18的一端和第二十一电容c21的一端;第二十一电容c21的一端是第五供电端,连接主处理器;电源管理芯片u3的fb4脚连接第二十电容c20的另一端、第十八电阻r18的另一端和

第十九电阻r19的一端;第十九电阻r19的另一端连接第二十一电容c21的另一端和地。其中,第五电感l5为输出滤波电感,与第二十一电容c21组成输出滤波电路。c20、r18、r19构成输出电压反馈电路,用于调整输出电压。

52.第二十一电容c21的一端是第五供电端,输出3.0v的第五电压vcc

‑

avcc给嵌入式处理器的模拟电路供电(第五供电端连接嵌入式处理器的模拟电路的供电端)。

53.优选地,还可在电源管理芯片u3的vin1脚、vin2脚、vin3脚、vin4脚、vcc脚上分别通过一电容接地。这些电容为输入滤波电容。

54.所述电源管理芯片u3优选型号为ea3059qdr的pmu芯片,其为多路合成的dc

‑

dc芯片,能将5v电压转换成嵌入式处理器所需的各种电压值;即上述的四路电压都是给嵌入式处理器的对应模块供电的,嵌入式处理器正常工作时四路电压都正常输出。

55.当mcu_pwm_off有大于2khz的pwm信号输入时,比较器芯片u2输出低电平的电源使能信号ho_pwr_en将电源管理芯片u3的使能脚拉低,电源管理芯片u3停止工作,即可关断嵌入式处理器的电源。

56.当mcu_pwm_off输出的信号频率小于2khz、或者输入持续的高电压或者低电压时,比较器芯片u2输出高电平的电源使能信号ho_pwr_en将电源管理芯片u3的使能脚拉高,电源管理芯片u3工作,从而为嵌入式处理器供电。

57.由于单片机在升级出现异常时都无法输出特定的pwm波形,所以当嵌入式处理器给单片机在线升级时,单片机不管处在何种异常状态都无法关断嵌入式处理器的电源,也就不会导致升级时异常断电而把车载设备的系统损坏。

58.综上所述,本实用新型提供的防止升级锁死的电路及车载设备,根据协处理器输出的具有预设波形的开断电信号来关断和打开主处理器电源,而协处理器在升级出现异常时无法输出预设波形,无论协处理器处在何种异常状态都无法关断主处理器的电源,这样既能保留协处理器的升级功能,支持远程给协处理器升级,又不会出现锁死导致异常断电、使协处理器程序不完整、影响车载设备不能正常工作,将车载设备的系统损坏的问题。同时,生产时协处理器可以保持空片,无需预先烧录程序,不需要先刷协处理器的程序后再刷主处理器的主程序,协处理器有无程序都不影响主处理器的系统运行;生产更为灵活,降低了生产成本。

59.以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。