1.本发明是有关于存储器,且特别是有关于一种安全存储器装置、安全存储器系统及管理篡改侦测的方法。

背景技术:

2.保护存储器装置或系统免受无意覆写、恶意攻击以及复制是重要的。存储器装置可包含特定特征以满足安全性要求。然而,若黑客(hacker)已对此类安全存储器装置进行实际存取,则其可直接篡改应用程序或以其自身函数置换函数调用。

技术实现要素:

3.本发明描述用于管理安全存储器装置(例如非易失性存储器装置)中的篡改侦测的系统及技术。

4.本发明的一个方面提供一种安全存储器装置,包含:存储单元阵列,具有多个存储单元;一或多个篡改侦测器,一或多个篡改侦测器中的每一者经组态以侦测安全存储器装置上的至少一部分的各别类型的篡改事件;以及篡改侦测状态缓存器,存储一或多个值,一或多个值中的各该值系指示由对应一或多个篡改侦测器侦测到的篡改侦测状态。

5.在一些实施方案中,一或多个篡改侦测器的各该篡改侦测器可耦合至篡改侦测状态缓存器且经组态以在篡改侦测器侦测对应篡改事件时更新篡改侦测状态缓存器中的对应值。一或多个篡改侦测器中的每一者可经组态以:侦测与安全存储器装置上的至少一部分相关联的对应参数的变化;判定对应参数的所侦测到的变化是否超出阈值;回应于判定对应参数的所侦测到的变化未超过阈值而保持侦测对应参数的变化;以及回应于判定对应参数的所侦测到的变化超出阈值而将命令传输至篡改侦测状态缓存器以更新篡改侦测状态缓存器中的对应值。

6.在一些实施方案中,对应值由篡改侦测状态缓存器中的对应位存储。当篡改侦测器侦测对应篡改事件时,对应位可经更新为逻辑1,对应位为逻辑0指示不存在由篡改侦测器侦测到的对应篡改事件。

7.在一些实施方案中,对应值存储于篡改侦测状态缓存器中的对应计数器,且当篡改侦测器侦测对应篡改事件时,对应值增加。当篡改侦测器侦测对应篡改事件时,对应值可能增加1。

8.在一些实施方案中,安全存储器装置包含命令接口,所述命令接口耦合至篡改侦测状态缓存器且经组态以输出存储于篡改侦测状态缓存器中的一或多个值。

9.在一些实施方案中,命令接口包含:命令译码器,经组态以译码传入命令;以及多任务器,耦合至存储单元阵列、篡改侦测状态缓存器以及命令译码器,其中多任务器基于译码所述传入命令而经控制以存取存储单元阵列及篡改侦测状态缓存器中的二者之一。

10.命令译码器可经组态以将传入命令译码为针对安全存储器装置中的至少一者的篡改侦测状态的读取命令,且多任务器可经控制以输出存储于篡改侦测状态缓存器中的一

或多个值。在一些实例中,传入命令包含下述的其中一者:特定命令码及特定信号。特定信号可包含预定信号,例如高电平电压信号或双态触变信号。

11.在一些实例中,命令译码器经组态以将传入命令译码为存储单元阵列上的操作命令,且多任务器经控制以实现对存储单元阵列的存取。操作命令可包含下述的至少一者:读取命令,用于读取存储于存储单元阵列中的数据;写入命令,用于将数据存储在存储单元阵列中;或擦除命令,用于将存储于存储单元阵列中的数据擦除。

12.在一些实施方案中,命令接口包含:第一接脚,经由第一缓冲器耦合至命令译码器;以及第二接脚,经由第二缓冲器耦合至多任务器。第一接脚可为串行输入接脚且第一缓冲器可为输入缓冲器。第二接脚可为串行输出接脚且第二缓冲器可为输出缓冲器。

13.在一些实施方案中,命令接口包含:多任务器,耦合至存储单元阵列及篡改侦测状态缓存器;以及接脚,耦合至多任务器,其中多任务器经组态以在通过特定命令驱动接脚时输出存储于篡改侦测状态缓存器中的一或多个值。接脚可为数据总线上的串行接脚或额外的接脚。

14.在一些实施方案中,安全存储器装置包含耦合至篡改侦测状态缓存器的输出接脚。安全存储器装置经组态以经由输出接脚来输出存储于篡改侦测状态缓存器中的一或多个值。安全存储器装置可经组态以在安全存储器装置通电后经由输出接脚自动地输出存储于篡改侦测状态缓存器中的一或多个值。安全存储器装置可更包含耦合于篡改侦测状态缓存器与输出接脚之间的输出缓冲器。输出接脚可为耦合至存储单元阵列的一或多个串行输出接脚的补充。

15.一或多个篡改侦测器可包含下述者中的至少一者:温度侦测器、电压侦测器、辐射侦测器或镭射直接建构(laser direct structuring;lds)电路。温度侦测器可经组态以侦测安全存储器装置上的至少一部分的操作温度的变化。电压侦测器可经组态以侦测安全存储器装置上的至少一部分的操作电压的变化。辐射侦测器可经组态以侦测安全存储器装置上的至少一部分的x射线或离子束。lds电路可包含:侵入侦测网格,围绕安全存储器装置上的至少一部分;以及传感器,经组态以监测侵入侦测网格的参数的变化,其中参数包含电容、电感或电阻。

16.篡改侦测状态缓存器可位于静态随机存取存储器(static random access memory;sram)中。安全存储器装置可包含用于一或多个篡改侦测器及篡改侦测状态缓存器的备份电池。

17.本发明的另一方面提供一种系统,包含:安全存储器装置及主机装置。安全存储器装置包含:存储单元阵列,具有多个存储单元;一或多个篡改侦测器,一或多个篡改侦测器中的每一者经组态以侦测安全存储器装置上的至少一部分的各别类型的篡改事件;以及篡改侦测状态缓存器,存储一或多个值,一或多个值中的各值系指示由对应一或多个篡改侦测器侦测到的篡改侦测状态。主机装置耦合至安全存储器装置且经组态以:自安全存储器装置获得存储于篡改侦测状态缓存器中的一或多个值,且基于所获得的一或多个值来判定安全存储器装置是否已经篡改。

18.在一些实施方案中,安全存储器装置包含:命令译码器,经组态以经由串行输入接脚自主机装置接收传入命令并译码传入命令;以及多任务器,耦合至存储单元阵列、篡改侦测状态缓存器以及命令译码器,多任务器基于译码传入命令而经控制以存取存储单元阵列

及篡改侦测状态缓存器中的二者之一。命令译码器可经组态以将传入命令译码为针对安全存储器装置的篡改侦测状态的读取命令,且多任务器可经控制以存取篡改侦测状态缓存器并经由串行输出接脚将存储于篡改侦测状态缓存器中的一或多个值输出至主机装置。

19.在一些实施方案中,安全存储器装置包含耦合至篡改侦测状态缓存器的输出接脚,所述输出接脚为耦合至存储单元阵列的一或多个串行接脚的补充。安全存储器装置可经组态以经由输出接脚来将存储于篡改侦测状态缓存器中的一或多个值自动地输出至主机装置。

20.主机装置可经组态以:响应于判定安全存储器装置已经篡改,在安全存储器装置上执行篡改响应。篡改回应可包含下述的至少一者:使安全存储器装置断电,停用安全存储器装置,将存储于安全存储器装置中的数据擦除,或实体地毁坏安全存储器装置。

21.本发明的另一方面提供一种管理安全存储器装置中的篡改侦测的方法。所述方法包含:经由输出接脚来接收存储于安全存储器装置中的篡改侦测状态缓存器中的一或多个值,安全存储器装置包含各自经组态以侦测安全存储器装置上的各别类型的篡改事件的一或多个篡改侦测器,一或多个值中的各该值系指示由对应一或多个篡改侦测器侦测到的篡改侦测状态;基于篡改侦测状态缓存器中的所接收的一或多个值来判定安全存储器装置是否已经篡改;以及响应于判定安全存储器装置已经篡改而在安全存储器装置上执行篡改响应。

22.所述方法可更包含:经由输入接脚将读取命令传输至安全存储器装置,所述读取命令用于读取安全存储器装置的篡改侦测状态。所述方法可更包含:判定是否在安全存储器装置上执行操作命令,以及响应于判定安全存储器装置上不存在操作命令而将读取命令传输至安全存储器装置。

23.本发明的第四方面提供一种安全存储器装置,包含:存储单元阵列,具有多个存储单元;多个篡改侦测器,多个篡改侦测器中的每一者经组态以侦测安全存储器装置上的至少一部分的各别类型的篡改事件;以及多个篡改侦测状态缓存器,篡改侦测状态缓存器中的每一者耦合至多个篡改侦测器中的不同对应篡改侦测器且存储指示由不同对应篡改侦测器侦测到的篡改侦测状态的各别值。

24.安全存储器装置可更包含多个输出接脚,多个输出接脚中的每一者耦合至多个篡改侦测状态缓存器中的不同的对应篡改侦测状态缓存器。安全存储器装置可经组态以经由多个输出接脚来输出存储于多个篡改侦测状态缓存器中的各别值。安全存储器装置可更包含耦合至存储单元阵列的多个串行接脚,且多个输出接脚为多个串行接脚的补充。

25.应注意,在本发明中术语「安全存储器装置」表示由篡改保护(例如由篡改侦测及/或篡改响应)保证安全的存储器装置(或存储器)。存储器装置(或存储器)自身可视情况为存储于存储器装置(或存储器)中的数据提供额外的安全性。术语「篡改状态」意谓安全存储器装置是否已经受窜改。应注意,术语「安全存储器装置的篡改状态」意谓安全存储器装置上的至少一部分(例如安全存储器装置的部分区域,诸如安全存储器装置的存储单元阵列)或安全存储器装置的篡改状态。类似地,术语「安全存储器装置上的篡改侦测」意谓安全存储器装置上的至少一部分(例如安全存储器装置的部分区域,诸如安全存储器装置的存储单元阵列)或安全存储器装置上的篡改侦测。术语「安全存储器装置的篡改侦测状态」意谓安全存储器装置上的至少一部分(例如安全存储器装置的部分区域,诸如安全存储器装置

的存储单元阵列)或安全存储器装置的篡改侦测状态。术语「安全存储器装置上的篡改事件」意谓安全存储器装置上的至少一部分(例如安全存储器装置的部分区域,诸如安全存储器装置的存储单元阵列)或安全存储器装置上的篡改事件。

26.上述技术的实施方案包含方法、系统、电路、计算机程序产品以及计算机可读媒体。在一个实例中,可在系统中执行一种方法且所述方法可包含上述动作,例如用于管理系统中的安全性装置中的篡改侦测的动作。在另一实例中,一种此类计算机程序产品适合实施于非暂时性机器可读媒体中,所述非暂时性机器可读媒体存储可由一或多个处理器执行的指令。指令经组态以使得一或多个处理器执行上述动作。一种此类计算机可读媒体存储指令,在所述指令由一或多个处理器执行时,所述指令经组态以使得一或多个处理器执行上述动作。

27.在随附附图及以下描述中阐述一或多个所公开实施方案的细节。其他特征、方面以及优点将自本说明书、附图及权利要求书变得显而易见。

附图说明

28.图1a说明根据本发明的一或多个实施方案的包含安全存储器装置的系统的实例。

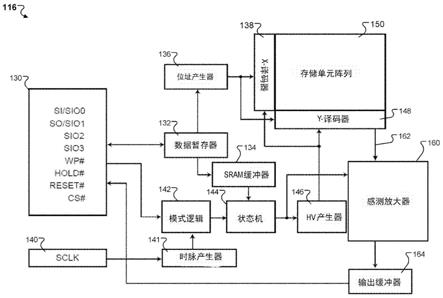

29.图1b说明根据本发明的一或多个实施方案的安全存储器装置的实例的方块图。

30.图2说明根据本发明的一或多个实施方案的具有篡改侦测及输出的安全存储器装置的实例的方块图。

31.图3说明根据本发明的一或多个实施方案的展示安全存储器装置的篡改侦测状态的读出的电路时序图。

32.图4说明根据本发明的一或多个实施方案的篡改侦测状态缓存器。

33.图5说明根据本发明的一或多个实施方案的用于管理安全存储器装置中的篡改侦测的方法的实例的流程图。

34.图6说明根据本发明的一或多个实施方案的具有篡改侦测及输出的安全存储器装置的另一实例的方块图。

35.图7说明根据本发明的一或多个实施方案的用于管理安全存储器装置中的篡改侦测的方法的另一实例的流程图。

36.【符号说明】

37.100:系统

38.110:装置

39.112:装置控制器

40.113:处理器

41.114:内部存储器

42.116、200、600:安全存储器装置

43.120:主机装置

44.130:存储器接口

45.132:数据缓存器

46.134:sram缓冲器

47.136:地址产生器

48.138:x-译码器

49.140:同步频率输入端

50.141:频率产生器

51.142:模式逻辑

52.144:状态机

53.146:高电压产生器

54.148:y-译码器

55.150、202、602:存储单元阵列

56.160、204、604:感测放大器

57.162:数据线

58.164、218、606、612:输出缓冲器

59.206:输入接脚

60.208、608、610:输出接脚

61.210:命令接口

62.212:命令译码器

63.214:数据多任务器

64.216:输入缓冲器

65.220-1、220-2、220-3、220-n、620-1、620-2、620-3、620-n:篡改侦测器

66.230、630:篡改侦测状态缓存器

67.300:电路时序图

68.302、304、306、308:列

69.500、700:方法

70.502、504、506、508、510、512、514、516、702、704、706:步骤

71.si、si/sio0、so、so/sio1、sio2、sio3、wp#、hold#、reset#、cs#:接脚

具体实施方式

72.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

73.有可能实体地篡改存储器装置,例如更改应用程序或置换函数调用。因此,期望开发用于有效地侦测安全存储器装置上的窜改尝试并输出篡改侦测的结果的技术。

74.本发明的实施方案提供一种具有篡改侦测及输出的安全存储器装置。安全存储器装置可包含:存储单元阵列;一或多个篡改侦测器(或篡改传感器),用于侦测安全存储器装置上的至少一部分(例如,存储单元阵列或安全存储器装置)的篡改状态;以及篡改侦测状态缓存器,存储一或多个值(例如,位),所述一或多个值各自指示由篡改侦测器中的对应一者侦测到的篡改侦测状态。每一篡改侦测器可彼此独立地起作用且经组态以侦测对应类型的篡改事件。在一些实例中,篡改侦测器包含下述者中的至少一者:温度传感器,用于侦测安全存储器装置上的至少一部分的操作温度的变化;电压传感器,用于侦测安全存储器装置上的至少一部分的操作电压的变化;辐射传感器,用于侦测安全存储器装置上的至少一部分的x射线及离子束;或镭射直接建构(lds)电路防护件,围绕安全存储器装置上的至少

一部分(例如包含存储单元阵列的关键硬件区)以用于侦测尝试侵入。

75.在一些实施方案中,若篡改侦测器侦测篡改事件,则可在任何适合的条件下,例如以正常操作模式或以低功率模式将缓存器中的对应位例如自逻辑0更新为逻辑1,所述低功率模式包含在提供电池备份(例如,内置电池)的情况下的关机。通过使用篡改侦测状态缓存器,可存储、更新以及同时输出由不同篡改侦测器侦测到的安全存储器装置上的至少一部分的篡改侦测状态,此可提高侦测速度、准确度以及效率。

76.可通过触发事件输出篡改侦测状态。在一些实例中,主机装置可向安全存储器装置发布针对篡改侦测状态的读取命令,且安全存储器装置可将存储于篡改侦测状态缓存器中的值输出至主机装置。读取命令可为信号(例如,高电压信号或双态触变信号)或特定命令码(例如,10101010)。可经由数据总线接脚,例如串行输入/输出(serial input/output;sio)接脚将读取命令递送至安全存储器装置。

77.在一些实例中,可扩展数据总线以添加耦合至篡改侦测状态缓存器的额外输出接脚。额外输出接脚亦可例如自动地输出存储于篡改侦测状态缓存器中的值,使得主机装置可保持监测安全存储器装置上的至少一部分(例如,存储单元阵列或安全存储器装置)的篡改侦测状态。举例而言,在安全存储器装置经通电后,安全存储器装置可经由额外输出接脚将存储于篡改侦测状态缓存器中的值自动地输出至主机装置。在一些实施方案中,可为篡改侦测器及篡改侦测状态缓存器提供内置电池。篡改侦测器及篡改侦测状态缓存器可甚至在安全存储器装置关机时保持起作用以更新篡改侦测状态。额外输出接脚的初始状态可为高阻抗(高z)、1或0。在一些实施方案中,安全存储器装置可包含一或多个额外输出接脚,所述一或多个额外输出接脚中的每一者可耦合至对应篡改侦测器以用于输出由篡改侦测器侦测到的篡改侦测状态或耦合至对应缓存器,所述对应缓存器存储指示由对应篡改侦测器侦测到的篡改侦测状态的值。

78.本发明公开的技术可有效地侦测安全存储器装置上的窜改尝试并输出篡改侦测的结果。可针对需要篡改侦测及/或输出的任何类型的电路、装置或系统实施所述技术。举例而言,除存储器系统以外,亦可将所述技术应用于利用安全引擎及/或包含篡改侦测及/或输出的任何其他存储装置。技术可应用于各种类型的易失性存储器装置或非易失性存储器装置,诸如nor闪存、nand闪存、电阻式随机存取存储器(resistive random-access memory;rram)、相变随机存取存储器(phase-change random-access memory;pcram)以及其他。所述技术可应用于各种存储器类型,诸如单层级单元(single-level cell;slc)装置、多层级单元(multi-level cell;mlc)装置(如2层级单元装置)、三层级单元(triple-level cell;tlc)装置、四层级单元(quad-level cell;qlc)装置或五层级单元(penta-level cell;plc)装置。另外或替代地,技术可应用于各种类型的装置及系统,诸如安全数字(secure digital;sd)卡、嵌入型多媒体卡(embedded multimedia cards;emmc)或固态驱动器(solid-state drives;ssd)、嵌入型系统以及其他。

79.图1a说明系统100的实例。系统100包含装置110及主机装置120。装置110可为包含装置控制器112及安全存储器装置116的存储器系统。装置控制器112包含处理器113及内部存储器114。

80.在一些实施方案中,装置110为存储装置。举例而言,装置110可为嵌入式多媒体卡(embedded multimedia card;emmc)、安全数字(sd)卡、固态驱动器(solid-state drive;

ssd)或某一其他适合的存储器。在一些实施方案中,装置110为智能型腕表、数字相机或媒体播放器。在一些实施方案中,装置110为耦合至主机装置120的客户端装置。举例而言,装置110为数字相机或媒体播放器中的sd卡,所述数字相机或媒体播放器为主机装置120。

81.装置控制器112为通用微处理器或特殊应用微控制器。在一些实施方案中,装置控制器112为用于装置110的存储器控制器。以下部分基于装置控制器112为存储器控制器的实施方案来描述各种技术。然而,描述于以下部分中的技术亦适用于装置控制器112为不同于存储器控制器的另一类型的控制器的实施方案中。

82.处理器113经组态以执行指令并处理数据。指令包含分别作为固件码及/或其他程序代码存储于辅助存储器中的固件指令及/或其他程序指令。数据报含对应于由处理器执行的固件及/或其他程序的程序数据,外加其他适合的数据。在一些实施方案中,处理器113为通用微处理器或特殊应用微控制器。处理器113亦称作中央处理单元(central processing unit;cpu)。

83.处理器113自内部存储器114存取指令及数据。在一些实施方案中,内部存储器114为静态随机存取存储器(sram)或动态随机存取存储器(dynamic random access memory;dram)。举例而言,在一些实施方案中,当装置110为emmc、sd卡或智能型腕表时,内部存储器114为sram。在一些实施方案中,当装置110为数字相机或媒体播放器时,内部存储器114为dram。

84.在一些实施方案中,内部存储器为包含于装置控制器112中的高速缓存,如图1a中所展示。内部存储器114存储对应于由处理器113执行的指令的脚本,及/或在运行时间期间由处理器113请求的数据。

85.装置控制器112将脚本及/或数据自安全存储器装置116转移至内部存储器114。在一些实施方案中,安全存储器装置116为经组态用于指令及/或数据的长期存储的非易失性存储器,例如nand或nor闪存装置,或某一其他适合的非易失性存储器装置。在安全存储器装置116为nand闪存的实施方案中,装置110为闪存装置,例如闪存卡,且装置控制器112为nand快闪控制器。举例而言,在一些实施方案中,当装置110为emmc或sd卡时,安全存储器装置116为nand闪存;在一些实施方案中,当装置110为数字相机时,安全存储器装置116为sd卡;且在一些实施方案中,当装置110为媒体播放器时,安全存储器装置116为硬盘。在安全存储器装置116为nor闪存的一些实施方案中,装置110可视情况包含装置控制器112。在一些情况下,装置110可不包含装置控制器且安全存储器装置116可与主机装置120直接通信。

86.图1b说明安全存储器装置116的实例组态。安全存储器装置116中的元件可经整合至板上,例如si类载体板上,且经封装。安全存储器装置116可具有存储单元阵列150,所述存储单元阵列150可包含多个存储单元。存储单元可经串联耦合至多个列字线及多个行位线。每一存储单元可包含存储器晶体管,所述存储器晶体管经组态为存储元件以存储数据。存储器晶体管可包含硅-氧化物-氮化物-氧化物-硅(silicon-oxide-nitride-oxide-silicon;sonos)晶体管、浮动栅极晶体管、氮化物只读存储器(nitride read only memory;nrom)晶体管或可存储电荷的任何适合的非易失性存储器mos装置。安全存储器装置116可包含x-译码器(或列译码器)138及y-译码器(或行译码器)148。每一存储单元可经由各别字元线耦合至x-译码器138且经由各别位线耦合至y-译码器148。因此,可通过x-译码器138及y-译码器148选择每一存储单元以经由各别字元线及各别位线进行读取操作或

写入操作。

87.安全存储器装置116可包含具有多个接脚的存储器接口130,所述多个接脚经组态以耦合至外部装置,例如装置控制器112及/或主机装置120。接脚可包含用于串行数据输入/串行数据输入及输出的si/sio0、用于串行数据输出/串行数据输入及输出的so/sio1、用于串行数据输入或输出的sio2、用于写入保护低态有效的wp#、用于保持信号输入的hold#、用于硬件重置接脚低态有效的reset#以及用于芯片选择的cs#。

88.安全存储器装置116可包含数据缓存器132、sram缓冲器134、地址产生器136、同步频率(synchronous clock;sclk)输入端140、频率产生器141、模式逻辑142、状态机144以及高电压(high voltage;hv)产生器146。sclk 140可经组态以接收同步频率输入且频率产生器141可经组态以基于同步频率输入而产生针对安全存储器装置116的频率信号。模式逻辑142可经组态以判定是否存在读取或写入操作并向状态机144提供判定的结果。安全存储器装置116亦可包含感测放大器160及输出缓冲器164,感测放大器160可通过数据线162连接至y-译码器148,输出缓冲器164用于将来自感测放大器160的输出信号缓冲至存储器接口130。感测放大器160可为在自安全存储器装置116读取数据时使用的读取电路的部分。感测放大器160可经组态以感测表示存储于存储单元中的数据位(1或0)的来自位线的低功率信号,且经组态以将小电压摆动放大至可辨识逻辑电平,因此数据可正确地加以解译。

89.主机装置120可产生命令,诸如可分别执行以自安全存储器装置116读取数据的读取命令、将数据写入至安全存储器装置116的写入命令及/或将安全存储器装置116中的数据擦除的擦除命令。可经由可为多位总线的数据总线(例如,系统总线)在安全存储器装置116与主机装置120及/或其他元件之间通信或传输写入至安全存储器装置116的数据或自安全存储器装置116读取的数据。

90.在一些实例中,在写入操作期间,安全存储器装置116可自主机装置120接收写入命令。数据缓存器132可登记来自存储器接口130的输入数据,且地址产生器136可产生对应实体地址以将输入数据存储于存储单元阵列150的特定存储单元中。可将地址产生器136连接至x-译码器138及y-译码器148,所述x-译码器138及y-译码器148经控制以经由对应字线及位线选择特定存储单元。只要供应功率,则sram缓冲器134可将来自数据缓存器132的输入数据保持在其存储器中。状态机144可处理来自sram缓冲器134的写入信号并将控制信号提供至hv产生器146,所述hv产生器146可产生写入电压并将写入电压提供至x-译码器138及y-译码器148。y-译码器148可经组态以将写入电压输出至用于将输入数据存储于特定存储单元中的位线。

91.在一些实例中,在读取操作期间,安全存储器装置116可经由存储器接口130自主机装置120接收读取命令。状态机144可将控制信号提供至hv产生器146及感测放大器160。hv产生器146可将电压提供至x-译码器138及y-译码器148以用于选择存储单元。感测放大器160可感测表示存储于选定存储单元中的数据位(1或0)的来自位线的小功率(电压或电流)信号,并将小功率信号摆动放大至可辨识逻辑电平,因此数据位可通过安全存储器装置116外部的逻辑正确地加以解译。输出缓冲器164可自感测放大器160接收经放大电压并经由存储器接口130将经放大功率信号输出至安全存储器装置116外部的逻辑。

92.在一些实施方案中,安全存储器装置116可为其中可安全地存储数据的安全存储器。如结合图2及图6中的其他细节所描述,安全存储器装置116可包含:一或多个篡改侦测

器,用于侦测安全存储器装置116的至少一部分(例如存储单元阵列150或安全存储器装置116)上的窜改事件(例如,篡改尝试或攻击);及篡改侦测状态缓存器,具有指示每一篡改侦测器的篡改侦测状态(亦即篡改侦测器是否已侦测到窜改)的位。篡改侦测状态缓存器可与存储单元阵列150分离。在一些情况下,篡改侦测状态缓存器可位于sram中。

93.当篡改侦测器侦测安全存储器装置116的至少一部分(例如存储单元阵列150或安全存储器装置116)上的篡改事件时,篡改侦测器可输出信号或命令以更新篡改侦测状态缓存器中的对应位,例如将逻辑电平自指示未篡改状态的初始值「0」改变为指示经篡改状态的新值「1」。因此,对应位指示由篡改侦测器侦测到的安全存储器装置116的至少一部分的篡改侦测状态。篡改侦测状态缓存器中的位可指示由安全存储器装置116中的篡改侦测器侦测到的安全存储器装置116的至少一部分的篡改侦测状态,如结合图4中的其他细节所说明及描述。

94.举例而言,如结合图2、图3以及图6中的其他细节所说明及描述,可同时读取篡改侦测状态缓存器中的位或将所述位输出至主机装置120。主机装置120可基于篡改侦测状态缓存器中所接收的位来判定安全存储器装置116是否已经受窜改,哪一篡改侦测器已侦测到篡改事件,已出现哪一(哪些)类型的篡改攻击或篡改尝试,及/或指示安全存储器装置116已经篡改的严重程度的严重性级别。举例而言,侦测篡改事件的篡改侦测器的数目愈大,严重性级别可能愈高。特定类型的篡改攻击(例如由镭射直接建构(lds)电路侦测到的实际损害)可能比另一类型的篡改攻击(例如由温度侦测器侦测到的温度变化)更严重。

95.主机装置120可基于由篡改侦测状态缓存器中存储的值所指示的篡改侦测状态来作出反应或执行篡改响应。举例而言,主机装置120可实现(例如发送命令)将安全存储器装置116及/或装置110断电(或关机),以停用安全存储器装置116、将安全存储器装置116中的数据擦除及/或实体地破坏安全存储器装置116。在一些情况下,主机装置120可基于安全存储器装置116的安全性级别及/或由安全存储器装置116中的篡改侦测器侦测到的篡改攻击或尝试的严重性级别来实现篡改响应。

96.图2说明根据本发明的一或多个实施方案的具有篡改侦测及输出的安全存储器装置200的实例。可将安全存储器装置200实施为图1a或图1b的安全存储器装置116。安全存储器装置200中的元件可经整合至板上,例如si类载体板上,且经封装。

97.安全存储器装置200可包含存储单元阵列202,例如图1b的存储单元阵列150,及感测放大器204,例如图1b的感测放大器160。安全存储器装置200可包含图1b的安全存储器装置116中的其他元件中的一或多者。仅出于说明的目的,其他元件并未呈现于图2中。存储单元阵列202可具有多个存储单元。每一存储单元可包含存储器晶体管,所述存储器晶体管经组态为存储元件以存储数据。在一些实施方案中,如图2中所说明,安全存储器装置200可包含多个篡改侦测器220-1、篡改侦测器220-2、篡改侦测器220-3、...、篡改侦测器220-n(整体称为篡改侦测器220且单独称为篡改侦测器220)。可将篡改侦测器220配置于所述板(如其他外围元件)上或配置于存储单元阵列202上。

98.每一篡改侦测器220可彼此独立地起作用且经组态以侦测对应类型的篡改事件。在一些情况下,篡改侦测器220中的每一者可彼此不同且经组态以侦测不同的对应类型的篡改事件。在一些情况下,两个或大于两个篡改侦测器220可经组态以侦测相同类型的篡改事件。可将两个或大于两个篡改侦测器220配置在存储单元阵列202或安全存储器装置200

周围或上。

99.在一些实例中,篡改侦测器220可为用于侦测存储单元阵列202或安全存储器装置200的操作温度变化的温度传感器。在一些实例中,篡改侦测器220可为用于侦测安全存储器装置200(例如,存储单元阵列202)的操作电压变化的电压传感器。在一些实例中,篡改侦测器220可为用于侦测安全存储器装置200(例如,存储单元阵列202)上的x射线及离子束的辐射传感器。在一些实例中,篡改侦测器220可为用于侦测尝试侵入的镭射直接建构(lds)电路。lds电路可包含围绕存储单元阵列202或安全存储器装置200的侵入侦测网格及经组态以监测侵入侦测网格的至少一个参数的变化的传感器。参数可包含阻抗,诸如电容、电感或电阻。

100.篡改侦测器220中的每一者可经组态以侦测(或监测)与安全存储器装置200的至少一部分(存储单元阵列202或安全存储器装置200)相关联的对应参数的变化,例如lds电路的操作温度、操作电压、x射线或离子束的强度或阻抗。篡改侦测器220可判定对应参数的所侦测到的变化是否超出阈值。若篡改侦测器220判定对应参数的所侦测到的变化未超过阈值,则篡改侦测器220可能保持侦测(或监测)对应参数的变化。若篡改侦测器220判定对应参数的所侦测到的变化超出阈值,则篡改侦测器220可判定侦测到对应篡改事件及/或安全存储器装置200的篡改侦测状态为篡改状态。

101.在一些实施方案中,如图2中所说明,安全存储器装置200可包含篡改侦测状态缓存器230。篡改侦测状态缓存器230可连同篡改侦测器220一起位于可整合于所述板上的sram中。篡改侦测状态缓存器230可经组态以存储多个值,且所述值中的每一者可指示由对应篡改侦测器220侦测到的篡改侦测状态。可例如经由导电线将篡改侦测器220中的每一者耦合至篡改侦测状态缓存器230。

102.在一些实施方案中,篡改侦测状态缓存器230可包含多个位。每一位可用于指示由对应篡改侦测器220侦测到的篡改侦测状态。在一个实例中,若位具有逻辑0的值,则位可指示不存在由对应篡改侦测器220侦测到的篡改事件且篡改侦测状态为未篡改状态。若位具有逻辑1的值,则位可指示篡改侦测器220已在安全存储器装置200上,例如存储单元阵列202上侦测到篡改事件,且篡改侦测状态为篡改状态。

103.当对应篡改事件已由篡改侦测器220侦测到时,篡改侦测器220可将命令发送至篡改侦测状态缓存器230以更新位的值。若位值指示无篡改事件,则位值经改变以指示窜改。另一方面,若位值已指示窜改,则位值不改变。继续先前实例,若前一位值为默认值0,则位值经改变为1。若前一位值为1,则位值仍然为1。因此,篡改侦测状态缓存器230中的位可指示由篡改侦测器220侦测到的篡改侦测状态。

104.篡改侦测状态缓存器230中的位可同时经读出例如至主机装置,诸如图1a的主机装置120。可例如在将位读出至主机装置后,将篡改侦测状态缓存器230中的位重置为默认值。篡改侦测状态缓存器230中的位的数目可能不低于篡改侦测状态缓存器230中的篡改侦测器220的数目。若位的数目大于篡改侦测器220的数目,则可将篡改侦测状态缓存器230中的额外位设定为默认值(例如0),以指示无篡改事件。

105.在一些实施方案中,篡改侦测状态缓存器230包含一或多个计数器。每一计数器存储指示对应篡改侦测器已侦测到篡改事件的次数的值。当篡改侦测器220已侦测到对应篡改事件时,每一计数器可将对应值增加1,例如篡改侦测器220可将命令发送至篡改侦测状

态缓存器230以更新计数器。因此,值可不仅指示篡改侦测器220是否已侦测到篡改事件,且亦指示篡改侦测器220已侦测到篡改事件多少次,此是因为值经重置为默认值,例如0。愈大值可指示安全存储器装置200已经篡改愈多次(或愈严重级别)。每一值可由篡改侦测状态缓存器230中的一或多个位或字节表示。

106.在一些实施方案中,安全存储器装置200可包含用于篡改侦测器220及篡改侦测状态缓存器230的备份电池,例如内置电池。当安全存储器装置200断电或关机时,备份电池可为篡改侦测器220及篡改侦测状态缓存器230提供电力,且篡改侦测器230可保持侦测安全存储器装置200的篡改状态且可更新篡改侦测状态缓存器230中的值。亦可在断电或关机模式下读出存储于篡改侦测状态缓存器230中的值。

107.在一些实施方案中,如图2中所说明,安全存储器装置200包含耦合至存储单元阵列202(经由感测放大器204)及篡改侦测状态缓存器230的命令接口210。命令接口210可经组态以例如自外部装置(诸如图1a的主机装置120)接收传入命令,且基于传入命令来实现对存储单元阵列202及篡改侦测状态缓存器230中的一者的存取。命令接口210可经组态以在命令接口210接收触发器时输出存储于篡改侦测状态缓存器230中的值。

108.在一些实例中,命令接口210可包含:命令译码器212,经组态以译码传入命令;及数据多任务器214,耦合至存储单元阵列202、篡改侦测状态缓存器230以及命令译码器212。可基于例如通过命令译码器212译码传入命令的结果来控制数据多任务器214以实现对存储单元阵列202及篡改侦测状态缓存器230中的一者的存取。

109.命令接口210可包含输入接脚206,例如串行输入(serial input;si)接脚,诸如图1b的存储器接口130的si/sio0、so/sio1、sio2或sio3,及输入缓冲器216。可经由输入接脚206及输入缓冲器216,例如图1b的sram缓冲器134将传入命令输入至命令译码器212。命令接口210亦可包含输出接脚208,例如串行输出(serial output;so)接脚,诸如图1b的存储器接口130的si/sio0、so/sio1、sio2或sio3。可经由输出缓冲器218,例如图1b的输出缓冲器164将数据多任务器214耦合至输出接脚208。

110.若命令译码器212将传入命令译码为存储单元阵列202上的操作命令,则数据多任务器214可由命令译码器212控制以实现对存储单元阵列202的存取。操作命令可为用于读取存储于存储单元阵列202中的数据的读取命令、用于将数据存储于存储单元阵列202中的写入命令或用于将存储于存储单元阵列202中的数据擦除的擦除命令。举例而言,在读取操作期间,数据多任务器214可经由输出接脚208将来自存储单元阵列202的读取数据输出至例如主机装置。

111.若命令译码器212将传入命令译码为针对安全存储器装置200(例如,存储单元阵列202)的篡改侦测状态的读取命令,则数据多任务器214可由命令译码器212控制以实现对篡改侦测状态缓存器230的存取并经由输出接脚208将存储于篡改侦测状态缓存器230中的值输出至例如主机装置。在一些实例中,读取命令可为特定命令码,例如10101010。在一些实例中,读取命令可为特定信号,例如高电压信号或双态触变信号。

112.图3是根据本发明的一或多个实施方案的展示安全存储器装置的篡改侦测状态的读出的电路时序图300。安全存储器装置可为图2的安全存储器装置200或图1a至图1b的安全存储器装置116。主机装置(例如图1a的主机装置120)可经由串行输入(si)接脚(例如图2的输入接脚206)将篡改侦测状态读取命令发布至安全存储器装置。存储于篡改侦测状态缓

存器(例如图2的篡改侦测状态缓存器230)中的位可指示由安全存储器装置的篡改侦测器(例如图2的篡改侦测器220)侦测到的篡改侦测状态。可经由串行输出(so)接脚(例如图2的输出接脚208)将位输出至主机装置。

113.列302展示芯片选择栏(chip select bar;csb)接脚(例如图1b的存储器接口130的cs#接脚)上确收的芯片选择信号。可通过施加高电平信号于csb接脚进而不选择安全存储器装置,且通过将所述芯片选择信号由高电平信号改变为低电平信号而选择安全存储器装置。

114.列304展示安全存储器装置中的频率(clk)信号。频率信号可在较高状态与较低状态之间振荡。频率信号可呈具有50%工作循环(例如具有固定恒定频率)的方波的形式。频率信号可通过安全存储器装置中的频率产生器(例如图1b的频率产生器141)产生。频率产生器可经组态以基于来自slck输入端(例如sclk 140)的同步频率输入而产生用于安全存储器装置的频率信号。

115.列306展示si接脚上确收的输入信号。si接脚可在不存在传入命令时保持空闲且在将读取命令输入于si接脚上时变为激活的,且安全存储器装置通过csb接脚上的芯片选择信号而经选择。读取命令可为可具有多个频率周期长度的篡改侦测状态读取命令,例如如图3中所说明,在第一频率周期的上升边缘处开始且在第八个频率周期的下降边缘处结束的8个频率周期。

116.列308展示so接脚上的输出信号。当不存在输出时,可将so接脚维持在高阻抗(或高z或浮动)状态下。亦即,并未通过输出电路将so接脚驱动至限定的逻辑电平,且亦未将输出信号驱动至逻辑高或低电平。当安全存储器装置接收针对篡改侦测状态的读取命令时,安全存储器装置可输出存储于篡改侦测状态缓存器中的位。将位存储为篡改侦测状态缓存器中的最高有效位(most significant bit;msb)。如图3中所说明,可存在存储于篡改侦测状态缓存器中的8个位。图4说明实例篡改侦测状态缓存器。每一位(位0、位1、...、位7)可指示由安全存储器装置中的对应篡改侦测器(传感器0、传感器1、...、传感器7)侦测到的篡改侦测状态。除非未通过csb接脚上的芯片选择信号来选择安全存储器装置,否则安全存储器装置可保持将篡改侦测状态缓存器中的位输出至主机装置。

117.图5说明根据本发明的一或多个实施方案的用于管理安全存储器装置中的篡改侦测的方法500的实例的流程图。方法500可通过主机装置,例如图1a的主机装置120执行。安全存储器装置可为图1a至图1b的安全存储器装置116或图2的安全存储器装置200。安全存储器装置可包含一或多个篡改侦测器(例如图2的篡改侦测器220)及篡改侦测状态缓存器(例如图2的篡改侦测状态缓存器230),所述篡改侦测状态缓存器包含各自指示由对应篡改侦测器侦测到的篡改侦测状态的一或多个值。

118.在502处,安全存储器装置为空闲的。举例而言,未通过主机装置选择安全存储器装置。在504处,例如通过安全存储器装置的csb接脚上的芯片选择信号来选择安全存储器装置,且主机装置可确收操作命令以存取安全存储器装置中的存储单元阵列,例如图2的存储单元阵列202。操作命令可为读取命令、写入命令及/或擦除命令。

119.在506处,主机装置读取操作命令的状态以判定是否已完成操作命令。在508处,主机装置判定状态是否是繁忙的。若状态是繁忙的,则主机装置判定未完成操作命令并返回以在506处读取状态。若状态不是繁忙的,则主机装置判定已完成操作命令。

120.在510处,响应于判定状态并不繁忙,主机装置读取安全存储器装置的篡改侦测状态,例如如图3中所说明。主机装置可经由si接脚将针对篡改侦测状态的读取命令传输至安全存储器装置并经由so接脚自安全存储器装置接收篡改侦测状态缓存器中的位的输出。

121.在512处,主机装置基于篡改侦测状态缓存器中所接收的位来判定安全存储器装置是否已经篡改。举例而言,若值中的任一者为1,则主机装置可判定安全存储器装置已经篡改。若所有值为0,则主机装置可判定安全存储器装置未经篡改。

122.在514处,若主机装置判定安全存储器装置未经篡改,则方法500结束。在516处,若主机装置判定安全存储器装置已经篡改,则主机装置可在安全存储器装置上执行篡改响应,例如实现将安全存储器装置断电。

123.图6说明根据本发明的一或多个实施方案的具有篡改侦测及输出的安全存储器装置600的另一实例的方块图。可将安全存储器装置600实施为图1a至图1b的安全存储器装置116。

124.如图6中所说明,安全存储器装置600可类似于图2的安全存储器装置200。安全存储器装置600可具有存储单元阵列602(例如图2的存储单元阵列202)、感测放大器604(例如图2的感测放大器204)、输出缓冲器606(例如图2的输出缓冲器218)以及串行输出(so)接脚608(例如图2的so接脚208)。安全存储器装置600亦可包含多个篡改侦测器620-1、篡改侦测器620-3、篡改侦测器620-3、...、篡改侦测器620-n(整体称为篡改侦测器620且单独称为篡改侦测器620)及篡改侦测状态缓存器630。篡改侦测器620可为图2的篡改侦测器220。篡改侦测状态缓存器630可为图2的篡改侦测状态缓存器230。篡改侦测状态缓存器630可存储多个值,所述多个值各自指示篡改侦测器620中的对应一者的篡改侦测状态。

125.相比于图2的安全存储器装置200,安全存储器装置600并不包含命令接口,如图2的命令接口210。亦即,安全存储器装置600并不包含如图2的命令译码器212的命令译码器及如图2的数据多任务器214的数据多任务器。实际上,安全存储器装置600包含额外输出接脚610作为耦合至篡改侦测状态缓存器630的篡改侦测接脚。额外输出接脚610可与存储器接口(例如图1b的存储器接口130)上的串行接脚不同。额外输出接脚610可为耦合至存储单元阵列602的串行接脚的补充。安全存储器装置600可包含耦合于篡改侦测状态缓存器630与额外输出接脚610之间的另一输出缓冲器612。

126.安全存储器装置600可经组态以经由额外输出接脚610输出存储于篡改侦测状态缓存器630中的值。举例而言,在通电序列后,安全存储器装置600经通电且可经由额外输出接脚610自动地输出所存储的值。举例而言,当主机装置(例如图1a的主机装置120)耦合至额外的输出接脚610时,主机装置可经由额外的输出接脚610,例如在无需确收读取命令的情况下自动地接收存储于篡改侦测状态缓存器630中的值。

127.在一些实施方案中,安全存储器装置可包含与存储器接口的串行输入/输出接脚不同的多个额外输出接脚。可将额外输出接脚中的每一者耦合至对应篡改侦测器。安全存储器装置可经由额外输出接脚输出由对应篡改侦测器侦测到的篡改侦测状态。安全存储器装置亦可包含多个篡改侦测状态缓存器。篡改侦测状态缓存器中的每一者可经耦合于不同的对应篡改侦测器与不同的对应额外输出接脚之间。篡改侦测状态缓存器可存储指示由不同的对应篡改侦测器侦测到的篡改侦测状态的值并经由不同的对应额外输出接脚将所存储值输出至例如主机装置。主机装置可经耦合至多个额外输出接脚且例如同时或并行地、

选择性地或单独地读取存储于多个篡改侦测状态缓存器中的值。

128.图7说明根据本发明的一或多个实施方案的用于管理安全存储器装置中的篡改侦测的方法700的另一实例的流程图。安全存储器装置可为图1a至图1b的安全存储器装置116、图2的安全存储器装置200或图6的安全存储器装置600。可通过耦合至安全存储器装置的主机装置(例如图1a的主机装置120)执行方法700。

129.安全存储器装置可包含存储单元阵列、一或多个篡改侦测器以及篡改侦测状态缓存器。存储单元阵列可为图1b的存储单元阵列150、图2的存储单元阵列202或图6的存储单元阵列602。篡改侦测器中的每一者可为图2的篡改侦测器220或图6的篡改侦测器620,且经组态以侦测安全存储器装置上的对应类型的篡改事件。篡改侦测状态缓存器可为图2的篡改侦测状态缓存器230或图6的篡改侦测状态缓存器630。篡改侦测状态缓存器可存储一或多个值,且所述值中的每一者可指示篡改侦测器中的对应一者的篡改侦测状态。

130.主机装置经由输出接脚获得存储于篡改侦测状态缓存器中的一或多个值(702)。

131.在一些实施方案中,安全存储器装置可包含命令接口,例如图2的命令接口210。命令接口可包含命令译码器(例如图2的命令译码器212)及多任务器(例如图2的数据多任务器214)。命令译码器可经组态以经由串行输入接脚(例如图2的si接脚206)自主机装置接收传入命令并译码传入命令。多任务器可耦合至存储单元阵列、篡改侦测状态缓存器以及命令译码器,且由译码传入命令的结果控制以实现对存储单元阵列及篡改侦测状态缓存器中的一者的存取。

132.若命令译码器将传入命令译码为存储单元阵列上的操作命令,则多任务器可经控制以实现对存储单元阵列的存取。若命令译码器将传入命令译码为针对安全存储器装置的篡改侦测状态的读取命令,则多任务器可经控制以存取篡改侦测状态缓存器并经由输出接脚将存储于篡改侦测状态缓存器中的一或多个值输出至主机装置。输出接脚可为至主机装置的串行输出接脚,例如图2的so接脚208。在一些情况下,如图5中所说明,主机装置可读取存储单元阵列的状态以判定是否在存储单元阵列上执行操作命令。若主机装置判定存在操作命令,则主机装置可保持读取状态。若主机装置判定不存在操作命令,则主机装置可将针对篡改侦测状态的读取命令传输至安全存储器装置。

133.在一些实施方案中,输出接脚可经耦合至篡改侦测状态缓存器。输出接脚可为与耦合至存储单元阵列的串行接脚不同的额外接脚,例如图6的额外输出接脚610。安全存储器装置可经组态以在主机装置耦合至输出接脚时将存储于篡改侦测状态缓存器中的值自动地输出至主机装置。若向篡改侦测器及篡改侦测状态缓存器提供备份电池,则安全存储器装置可在其处于通电模式或处于关机模式时自动地输出值。

134.在一些实施方案中,安全存储器装置可包含数据多任务器(例如图2的数据多任务器214)及接脚。接脚可为串行输入/输出(sio)接脚,诸如图1b的存储器接口130的si/sio0、so/sio1、sio2或sio3。接脚亦可为与sio接脚分离的额外接脚。数据多任务器可经耦合至存储单元阵列及篡改侦测状态缓存器。接脚可经耦合至数据多任务器。主机装置可先确收至数据多任务器的接脚上的特定命令码。数据多任务器可由特定命令码控制以实现对篡改侦测状态缓存器的存取并经由接脚将存储于篡改侦测状态缓存器中的值输出至主机装置。

135.主机装置基于所接收的值来判定安全存储器装置是否已经篡改(704)。举例而言,存储于篡改侦测状态缓存器中的逻辑0的值可指示安全存储器装置未经篡改;而存储于篡

改侦测状态缓存器中的逻辑1的值可指示安全存储器装置已经篡改。因此,若所接收的值皆为0,则主机装置可判定安全存储器装置未经篡改。若所接收的值中的任一者为1,则主机装置可判定安全存储器装置已经篡改。

136.响应于判定安全存储器装置未经篡改,主机装置可保持执行步骤702及步骤704。响应于判定安全存储器装置已经篡改,主机装置在安全存储器装置上执行篡改响应(706)。篡改回应可包含下述者中的至少一者:将安全存储器装置断电(关机),停用安全存储器装置,将存储于安全存储器装置中的数据擦除,或实体地毁坏安全存储器装置。在一些情况下,主机装置可基于安全存储器装置的安全性级别及/或由安全存储器装置中的篡改侦测器侦测到的篡改攻击或尝试的严重性级别来实现不同的篡改回应。

137.所公开及其他的实例可实施为一或多个计算机程序产品,例如在计算机可读媒体上编码以通过数据处理设备执行或控制数据处理设备的操作的计算机程序指令的一或多个模块模块。计算机可读媒体可为机器可读存储装置、机器可读存储基底、存储器装置或其中的一或多者的组合。术语「数据处理设备」涵盖用于处理数据的所有设备、装置以及机器,包含例如可编程处理器、计算机或多个处理器或计算机。设备可包含除了硬件之外的形成用于所讨论的计算机程序的执行环境的程序代码,例如构成处理器固件、协议堆叠、数据库管理系统、操作系统或其中的一或多者的组合的程序代码。

138.系统可涵盖用于处理数据的所有设备、装置以及机器,包含例如可编程处理器、计算机或多个处理器或计算机。系统可包含除了硬件之外的形成用于所讨论的计算机程序的执行环境的程序代码,例如构成处理器固件、协议堆叠、数据库管理系统、操作系统或其中的一或多者的组合的程序代码。

139.计算机程序(亦称为程序、软件、软件应用程序、脚本或程序代码)可以程序化语言的任何形式写入,包含编译或解译语言,且其可以任何形式部署,包含作为独立程序或作为模块、元件、子例程(subroutine)或适用于计算环境的其他单元。计算机程序未必对应于文件系统中的档案。程序可经存储于保持其他程序或数据(例如存储于标示语言文件中的一或多个脚本)的档案的一部分中,存储于专用于所讨论的程序的单个档案中,或存储于多个经协调档案(例如存储一或多个模块、子程序或部分程序代码的档案)中。计算机程序可经部署以在一个计算机上执行或在位于一个位点处或跨越多个位点分布且由通信网络互连的多个计算机上执行。

140.本发明中描述的方法及逻辑流程可由执行一或多个计算机程序的一或多个可编程处理器执行,从而执行本发明中所描述的功能。方法及逻辑流程亦可由专用逻辑电路执行,且设备亦可经实施为专用逻辑电路,所述专用逻辑电路例如场可编程门阵列(field programmable gate array;fpga)或特殊应用集成电路(application specific integrated circuit;asic)。

141.适用于执行计算机程序的处理器包含例如通用微处理器及专用微处理器两者,及任何种类的数字计算机的任何一或多个处理器。通常,处理器将自只读存储器或随机存取存储器或此两者接收指令及数据。计算机的基本元件可包含用于执行指令的处理器及用于存储指令及数据的一或多个存储器装置。通常,计算机亦可包含用于存储数据的一或多个大容量存储装置,例如磁盘、磁光盘或光盘,或可操作地耦合至所述一或多个大容量存储装置以自其接收数据,或将数据转移至所述一或多个大容量存储装置,或二者皆有。然而,计

算机无需具有此类装置。适用于存储计算机程序指令及数据的计算机可读媒体可包含所有形式的非易失性存储器、媒体以及存储器装置,包含例如半导体存储器装置,例如eprom、eeprom以及闪存装置;磁盘。处理器及存储器可由专用逻辑电路补充或并入于专用逻辑电路中。

142.虽然此文献可描述多种特性,但这些特性不应解释为对本发明的所主张或可主张的保护范围的限制,而是解释为对特定针对特定实施例的特征的描述。在独立实施例的情形下描述于此文献中的某些特征亦可在单一实施例中组合地实施。相反,描述于单个实施例的上下文中的各种特征亦可单独地或以任何适合的子组合在多个实施例中实施。此外,尽管上文可将特征描述为以某些组合起作用且甚至最初按此来主张,但来自所主张的组合的一或多个特征在一些情况下可自所述组合删除,且所主张的组合可针对子组合或子组合的变体。类似地,尽管在附图中以特定次序来描绘操作,但不应将此理解为需要以所展示的特定次序或以顺序次序执行这些操作,或执行所有所说明操作以达成合乎期望的结果。

143.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。