1.本公开涉及半导体器件组装,更具体地涉及到衬底的金属管芯附接。

背景技术:

2.封装的半导体器件通常包括集成电路(ic)管芯,该管芯通常是使用管芯附接粘合剂安装在诸如引线框架的工件的管芯焊盘上的硅管芯。其它工件包括中介层、印刷电路板(pcb)和另一个ic管芯。对于顶(有源)面朝上并且背面朝下组装的ic管芯,管芯附接粘合剂提供机械附接,并且通常还提供通向管芯焊盘的电和/或热通路。管芯附接粘合剂通常包括聚合物,诸如聚酰亚胺或环氧基粘合剂。通常以颗粒薄片形式添加银作为填料,以提高聚合物材料的导电性和导热性二者。

技术实现要素:

3.提供本发明内容从而以简化形式介绍所公开概念的简要选择,以下在包括所提供的附图的具体实施方式中进一步描述。本发明内容无意限制要求保护的主题的范围。

4.公开的方面认识到包括金属颗粒填充的聚合物的常规管芯附接解决方案具有显著的热阻性和电阻性。由于随着更紧凑和更高集成度的电子系统具有更小特征和以更高操作电流运行的趋势,热管理变得越来越重要,因此当使用与半导体管芯的背面电接触时,需要更高热导率的管芯附接布置,其还提供低电阻。众所周知,尽管与金属颗粒填充聚合物相比,焊料压模附接,诸如共晶金和锡(ausn)可以提供具有相对良好的热阻和电阻性能的与半导体管芯的背面电接触,但焊料压模附接相对昂贵,并且限于可焊接的管芯表面。此外,焊料压模附接过程涉及惰性回流过程,其温度可能会对半导体管芯的金属互连产生温度引起的应力。

5.公开的方面包括封装的半导体器件,其包括具有第一和第二通孔孔径的金属衬底,以及在金属衬底上的介电焊盘上围绕孔径的金属焊盘,通孔孔径各自具有外环。第一和第二半导体管芯顶面向上地安装在孔径的顶部部分上,在其底面上具有背面金属(bsm)层。金属管芯附接层位于bsm层和金属衬底的壁之间,该金属衬底的壁限定孔径,以为填充孔径底部部分的第一和第二半导体管芯提供管芯附接。引线接触金属焊盘,其中引线包括延伸超过金属衬底的远侧部分。键合线位于金属焊盘和第一和第二半导体管芯上的键合焊盘之间,并且模制化合物为封装的半导体器件提供器件封装。

附图说明

6.现在将参考附图,这些附图不一定按比例绘制,其中:

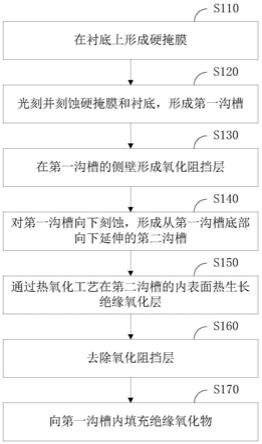

7.图1a至图1f示出了根据示例方面的所使用的部件和用于形成所公开的多芯片封装半导体器件的组装过程的组装过程进展过程,所公开的多芯片封装半导体器件在金属衬底上具有第一和第二半导体管芯,该金属衬底具有凸起的金属焊盘,该金属焊盘包括在金属衬底表面上的介电焊盘上的金属焊盘,其中每个具有bsm层的半导体管芯通过公开的电

镀(镀覆)金属管芯附接层直接附接到金属衬底上。

8.图2a示出了在切割(singulation),然后将相应半导体管芯上的键合焊盘引线键合到连接到引线的凸起金属焊盘,并且在相应的半导体管芯之间引线键合键合焊盘之后的示例带引线多芯片半导体器件,其在金属衬底上具有第一和第二半导体管芯。

9.图2b示出了模制后的图2a中所示的带引线多芯片封装半导体器件,其用来形成模制化合物以提供模制的带引线多芯片封装半导体器件。

具体实施方式

10.参考附图描述示例方面,其中相似的附图标记用于指示相似或等效的元件。动作或事件的图示顺序不应被视为限制,因为一些动作或事件可能以不同的顺序发生和/或与其它动作或事件同时发生。此外,根据本公开内容实施方法可能不需要某些图示的动作或事件。

11.所公开的方面包括多芯片半导体封装,其中第一和至少第二半导体管芯的管芯附接是通过镀覆金属层建立的,诸如包括铜、镍、钴或它们的合金,这与常规的焊接相反。因此,在公开的多芯片封装中消除了与sn

‑

cu金属间化合物形成相关的焊接管芯附接工艺的空洞问题。

12.图1a示出了用于覆盖金属衬底(参见图1b中的金属衬底120)以形成被覆盖的衬底叠层的示例介电盖130,其中介电盖130具有重复图案,每个图案包括凹槽对130a、130b,凹槽对包括第一凹槽130a和第二凹槽130b。被覆盖的衬底叠层被配置用于浸入下面相对于图1e所述的示出为150的提供电镀浴的镀覆容器中。

13.介电盖130可以包括塑料。第一凹槽130a用于覆盖第一半导体管芯,而第二凹槽130b用于覆盖第二半导体管芯,它们均例如被示出为矩形,其被成形为和尺寸被设定为匹配待覆盖的相应半导体管芯的尺寸。与第一和第二半导体管芯相比,凹槽130a、130b的面积略大以能够容纳相应的半导体管芯。尽管示出为相同的尺寸和形状,但是第一和第二凹槽130a和130b可以相对于彼此不同地设定尺寸和形状以匹配第一和第二半导体管芯的相应尺寸。

14.另选地,uv可固化电镀溶液抗性胶带可以用作介电盖130。在胶带代替介电盖的情况下,将不需要凹槽。第一和第二半导体管芯顶面上的介电盖可防止管芯在镀覆溶液中脱落。

15.图1b示出了示例金属衬底120,其中插图扩大了其一部分以示出凸起焊盘125的相应部件,每个部件包括在金属衬底120表面上的介电焊盘125a(例如,聚酰亚胺)上的金属焊盘125b。金属衬底120通常为衬底片/面板的形式,其具有多个双管芯位置通孔孔径,包括第一孔径120a和第二孔径120b,它们被配置为用于图1c中所示的第一和第二半导体管芯180a、180b,该第一和第二半导体管芯180a、180b顶面朝上定位在孔径120a、120b内。金属衬底片/面板可具有约50至1,000个双管芯位置。金属衬底120的厚度通常为约0.1mm(3.94密耳)至0.3mm(11.81密耳)。

16.金属衬底120可以包括铜,例如铜合金。用于金属衬底120的其它示例金属还可以包括镍、钴、锡或它们的合金。第一和第二孔径120a、120b呈重复图案,其位置与图1a所示的介电盖130的凹槽对130a、130b的(一个或多个)尺寸和重复图案相匹配。孔径120a和120b各

自具有用于坐置第一和第二半导体管芯的外环120a1和120b1,其中凸起焊盘125位于通常围绕通孔孔径120a和120b的侧面上。金属焊盘125b可印刷在介电焊盘125a上。印刷通常通过金属衬底120上的对准标记进行配准。

17.图1c示出了第一和第二半导体管芯180a和180b,其顶(有源)面朝上,背面朝下坐置在金属衬底120的孔径120a和120b内的外环120a1和120b1(图1b中所示)上。耦接到电路170a、170b中的节点的键合焊盘181被示出在半导体管芯180a和180b的有源顶面上。电路170a、170b包括形成在半导体层(体衬底上的外延层)中的电路元件(包括晶体管,并且通常包括二极管、电阻器、电容器等),它们被配置在一起以通常至少实现电路功能。示例电路功能包括模拟(例如放大器或电源转换器)、射频(rf)、数字或非易失性存储器功能。

18.第一和第二半导体管芯180a和180b具有bsm层186,例如包括铜。尽管未示出,但在bsm层186下方可以有任选的难熔金属阻挡层(例如tiw,tan或cr)。键合焊盘181可以在其上包括铜柱或焊接凸块。

19.图1d示出了在放置在半导体管芯180a、180b上方的金属衬底120上之后的介电盖130,其视图倒转以向下看金属衬底120的底部,显示孔径120a和120b的未被半导体管芯180a、180b占据的部分。bsm层186被示出在半导体管芯180a、180b的背面上。

20.图1e示出了将所公开的在其中具有第一和第二半导体管芯(未示出)的金属衬底120上包括介电盖130的被覆盖衬底叠层浸入在提供电镀浴的镀覆容器150内。这些部件被浸入镀覆溶液145中,该镀覆溶液145包括电解液,该电解液包含一种或多种溶解的金属盐,其包括电镀感兴趣的金属,以及溶液中允许电流流动的其它离子。

21.在介电盖的情况下,通常还存在密封剂,诸如在介电盖130和金属衬底120之间的电镀溶液抗性胶带,以避免在半导体管芯180a、180b的顶面上对镀覆金属管芯附接层进行镀覆。对于电镀,金属衬底120连接到电源190的负极端子(阴极),并且与金属衬底120间隔开的导电结构(诸如被示为与金属衬底120间隔开的阳极135的金属块)连接到电源190的正极端子(阳极)。

22.电镀通常在15℃至30℃的温度下进行,以避免引入温度引起的应力,诸如引入半导体管芯上的互连。在阴极,镀覆溶液145中溶解的金属离子(例如cu

2

)在溶液和阴极之间的界面处被还原,使得它们镀出到阴极上的零价态金属(例如cu金属)。电镀通常使用直流(dc)进行,但也可以作为脉冲电镀进行。

23.电镀沉积镀覆金属管芯附接层,其在本文示为包括在图1f中的187的单层(诸如包括铜),以填充半导体管芯180a和180b底面上的bsm层186和限定孔径120a、120b的金属衬底120的壁之间的体积以提供管芯附接。电镀工艺的时间可以通过将期望的金属管芯附接层187的厚度除以沉积速率来计算。镀覆金属管芯附接层187的厚度被设计成填充孔径120a、120b,诸如10到250μm厚,例如40到250μm厚。

24.图1f示出了孔径120a、120b未被半导体管芯180(管芯下方)占据的部分,现在填充有镀覆金属管芯附接层187,该层被沉积为金属衬底120的整个底面上的片。虽然镀覆金属管芯附接层187被显示为平面,但是当在相应的孔径120a、120b上方时通常存在轻微的凹陷。

25.即使与通过其它方法沉积的相同金属材料的其它层(诸如溅射金属层)相比,作为镀覆金属层的镀覆金属管芯附接层187也是独特的层。与溅射层不同,已知电沉积层填充视

线以外的区域。还已知电沉积层具有独特的微观结构,其包括初始沉积的能斯特扩散层,该扩散层的密度和微观结构与电沉积层的主体部分的密度和微观结构不同。

26.图2a示出了在从镀覆溶液145去除被覆盖的衬底叠层、去除介电盖130、切割金属衬底120并诸如通过焊接将引线126添加到凸起焊盘125的金属焊盘125b上之后的单个带引线多芯片半导体器件200。带引线多芯片半导体器件200可以被看作是18引线封装。引线126包括金属条(例如,与引线框架相同的金属),诸如可以商业获得或内部产生的铜、铜合金或镀锡引线126。例如,可以将金属片切割成用于引线126的金属条。

27.引线126具有至少一个弯曲部并且包括延伸超过金属衬底120的远侧部分。虽然未示出,但是引线126可以是鸥翼布置。引线126通常焊接到金属焊盘125b,但也可以经由焊接或通过导电粘合剂材料附接。所示的键合线133和134是在切割之前添加的,包括连接在凸起焊盘125的金属焊盘125b与半导体管芯180a、180b上的键合焊盘181之间的键合线133。还有任选的键合线134被示出为连接在相应半导体管芯180a、180b上的键合焊盘181之间。图2b示出了在形成为封装半导体器件提供封装的模制化合物290之后所公开的带引线多芯片封装半导体器件,现在示出为250。

28.所公开的方面可以集成到多种组装流程中以形成多种不同的多芯片半导体封装器件和相关产品。半导体管芯可包括其中的各种元件和/或其上的层,包括阻挡层、介电层、器件结构、有源元件和无源元件(包括源极区、漏极区、位线、基极、发射极、集电极、导线、导电通孔等)。此外,半导体管芯可以由多种工艺形成,包括双极型、绝缘栅双极型晶体管(igbt)、cmos、bicmos和mems。

29.本公开所涉及的本领域技术人员将理解,在要求保护的发明的范围内,所公开的方面的许多变化是可能的,并且在不偏离本公开的范围的情况下,可以对上述方面进行进一步的添加、删除、替换和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。