1.本发明涉及高速接收电路的差分输入阻抗校准技术领域,尤其涉及一种校准电路。

背景技术:

2.由于高速信号在传输过程中存在反射,高速接收电路的输入阻抗必须与外部传输线特征阻抗进行匹配。例如,当传输线特征阻抗为50ohm时,高速接收电路单端输入阻抗也需要位于50ohm左右,而差分输入阻抗则需要位于100ohm左右,以降低高速信号在传输过程中的反射,提高高速信号的质量。

3.但高速接收电路的输入阻抗一般由金属

‑

氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,mosfet)和电阻构成,但在芯片制作过程中,由于工艺误差的存在,并且mosfet的阻抗还会受到工作电压和共模电压的影响,导致芯片制作完成后高速接收电路的差分输入阻抗偏离100ohm,因此,需要差分输入阻抗校准电路进行校准,将高速接收电路的差分输入阻抗校准到100ohm附近。

4.图1为现有技术中高速接口的示意图。参照图1,图中包括直流耦合(dc coupling)方式连接的高速输出电路和高速接收电路,高速接收电路的差分输入阻抗为2

×

rtcoil rtt_d,其中rtcoil为变压器线圈(transformer coil,tcoil)的阻抗,rtt_d为由电阻和开关构成的目标阻抗单元,需要校准使得2

×

rtcoil rtt_d等于100ohm。

5.图2为现有技术中的差分输入阻抗校准电路的示意图。参照图2,图中包括比较器comparator、开关cal_diff_en、电阻rext、电阻r1、电阻r2、电阻r3、电阻r4以及目标阻抗单元rtt_d,电阻rext的一端接工作电压vdd,电阻rext的另一端接电阻r3,电阻r3的另一端接电阻r4,电阻r4的一端接目标阻抗单元rtt_d的一端,目标阻抗单元rtt_d的另一端接地vss,电阻r1的一端接工作电压vdd,电阻r1的另一端接电阻r2的一端,电阻r2的另一端接地vss,比较器的反相输入端接开关cal_diff_en的一端,开关cal_diff_en的另一端接电阻rext的另一端,比较器的正相输入端接电阻r1的另一端,其中,电阻rext的阻抗为100ohm,电阻r1的阻抗为10k ohm,电阻r2的阻抗为10k ohm,电阻r3的阻抗和电阻r4的阻抗均等于图1中tcoil的阻抗。闭合开关cal_diff_en,然后有小到大调节目标阻抗单元rtt_d的阻抗,当比较器的输出zcal_cmp_out由0到1翻转时,校准结束,即可以得到2

×

rtcoil rtt_d等于100ohm。

6.由图2的差分输入阻抗校准电路及校准过程可以得知,当校准完成时,电阻rext另一端处的电压为vdd/2,差分阻抗共模电压为vdd/4。而在高速输出电路和高速接收电路正常工作时,差分阻抗工模电压为vdd/2,并且差分阻抗中的开关阻抗易受工模电压的影像,不同共模电压使得开关阻抗不同,因此,通过图2所示现有技术中的差分输入阻抗校准电路校准的100ohm差分阻抗在直流耦合应用中会发生偏离,进而影响高速信号的质量。

7.因此,有必要提供一种新型的校准电以解决现有技术中存在的上述问题。

技术实现要素:

8.本发明的目的在于提供一种校准电路,提高差分输入阻抗校准的准确性。

9.为实现上述目的,本发明的所述校准电路,包括:

10.同相电压单元,包括第一调节电阻单元和第一开关单元,所述第一调节电阻单元与所述第一开关单元连接,所述第一调节电阻单元用于通过调节阻抗以向所述第一开关单元提供不同的电压;

11.反相电压单元,包括第二调节电阻单元、固定电阻单元和第二开关单元,所述第二调节电阻单元和所述固定电阻单元均与所述第二开关单元连接,所述第二调节电阻单元用于通过调节阻抗以向所述第二开关单元提供不同的电压,所述固定电阻单元用于向所述第二开关单元提供固定的电压;

12.目标阻抗调节单元,包括反向电压选择单元、第三调节电阻单元、第三开关单元和第四开关单元,所述反向电压选择单元与所述第三开关单元连接,所述第三调节电阻单元与所述第四开关单元连接,所述反向电压选择单元用于向所述第三开关单元提供至少两种电压,所述第三调节电阻单元用于根据所述第一调节电阻单元的阻抗调节信息和所述第二调节电阻单元的阻抗调节信息进行阻抗的调节,所述第三调节电阻单元还用于连接目标阻抗单元,并通过调节所述目标阻抗单元的阻抗以向所述第四开关单元提供不同的电压;

13.比较器单元,所述比较器单元的同相输入端与所述第一开关单元与所述第四开关单元连接,所述比较器单元的反相输入端与所述第二开关单元、所述第三开关单元连接,所述比较器单元用于同相输入端的电压和反相输入端的电压,以判断所述第一调节电阻单元的阻抗、所述第二调节电阻单元的阻抗、所述第三调节电阻单元的阻抗以及所述目标阻抗单元的阻抗是否调整完毕。

14.所述校准系统的有益效果在于:所述反向电压选择单元与所述第三开关单元连接,所述第三调节电阻单元与所述第四开关单元连接,所述反向电压选择单元用于向所述第三开关单元提供至少两种电压,所述第三调节电阻单元用于根据所述第一调节电阻单元调节后的阻抗和所述第二调节电阻单元调节后的阻抗进行阻抗的调节,所述第三调节电阻单元还用于连接目标阻抗单元,并通过调节所述目标阻抗单元的阻抗以向所述第四开关单元提供不同的电压,能够在不同的电压下对目标阻抗单元进行校准,使得目标阻抗单元的阻抗与所述第一调节电阻单元和所述第二调节电阻单元相关,提高了差分输入阻抗校准的准确性。

15.优选地,所述第一调节电阻单元包括第一调节电阻子单元、第二调节电阻子单元、第三调节电阻子单元、第一电阻、第二电阻和第三电阻,所述第一调节电阻子单元的一端和所述第二调节电阻子单元的一端接工作电压,所述第一调节电阻子单元的另一端连接所述第一电阻一端,所述第一电阻的另一端连接所述第三调节电阻子单元的一端和所述第三电阻的一端,所述第三调节电阻子单元的另一端接地,所述第二调节电阻子单元的另一端连接所述第二电阻的一端,所述第二电阻的另一端连接所述第三电阻的另一端。其有益效果在于:用于产生不同电压,并得到所述第一调节电阻子单元和所述第三调节电阻子单元的阻抗调节信息,便于后续对目标阻抗单元进行校准。

16.进一步优选地,所述第一开关单元包括第一开关和第二开关,所述第一开关的一端连接所述第二电阻的另一端,所述第二开关的一端连接所述第三电阻的一端,所述第一

开关的另一端和所述第二开关的另一端均连接所述比较器单元的正相输入端。其有益效果在于:便于通过第一开关的导通和关断、第二开关的导通和关断向比较器单元提供不同的电压。

17.优选地,所述第二调节电阻单元包括第四调节电阻子单元和第四电阻,所述第四电阻的一端接工作电压,所述第四电阻的另一端连接所述第四调节电阻子单元的一端,所述第四调节电阻子单元的另一端接地。其有益效果在于:用于产生不同电压。

18.进一步优选地,所述第二开关单元包括第三开关,所述第三开关的一端连接所述第四电阻的另一端,所述第三开关的另一端连接所述比较器单元的反相输入端。其有益效果在于:便于通过第三开关的导通和关断选择是否向比较器单元提供电压。

19.优选地,所述固定电阻单元包括第五电阻和第六电阻,所述第五电阻的一端接工作电压,所述第五电阻的另一端连接所述第六电阻的一端,所述第六电阻的另一端接地。其有益效果在于:便于提供固定电压。

20.进一步优选地,所述第二开关单元包括第四开关,所述第四开关的一端连接所述第五电阻的另一端,所述第四开关的另一端连接所述比较器单元的反相输入端。其有益效果在于:便于通过第四开关的导通和关断选择是否向比较器单元提供电压。

21.优选地,所述第三调节电阻单元包括第五调节电阻子单元和第六调节电阻子单元,所述第五调节电阻子单元的一端接工作电压,所述第五调节电阻子单元的另一端用于连接所述目标阻抗单元的一端,所述第六调节电阻子单元的一端接地,所述第六调节电阻子单元的另一端用于连接所述目标阻抗单元的另一端。其有益效果在于:便于根据所述第一调节电阻子单元和所述第三调节电阻子单元对目标阻抗单元进行校准,提高对目标阻抗单元校准的准确性。

22.进一步优选地,所述第四开关单元包括第五开关和第六开关,所述第五开关的一端连接所述第五调节电阻子单元的另一端,所述第六开关的一端连接所述第六调节电阻子单元的另一端,所述第五开关的另一端和所述第六开关的另一端均连接所述比较器单元的正相输入端。其有益效果在于:便于通过第五开关、第六开关的导通和关断,选择向比较器单元提供目标阻抗单元不同端的电压,便于在不同的共模电压下对目标阻抗单元进行校准。

23.优选地,所述反向电压选择单元包括第七电阻、第八电阻和第九电阻,所述第七电阻的一端接工作电压,所述第七电阻的另一端连接所述第八电阻的一端,所述第八电阻的另一端连接所述第九电阻的一端,所述第九电阻的一端接地。其有益效果在于:便于提供多种固定电压。

24.优选地,所述第三开关单元包括第七开关和第八开关,所述第七开关的一端连接所述第七电阻的另一端,所述第八开关的一端连接所述第八电阻的另一端,所述第七开关的另一端和所述第八开关的另一端均连接所述比较器单元的反相输入端。其有益效果在于:便于通过第七开关和第八开关的导通和关断选择向比较器单元提供不同的电压,便于在不同的共模电压下对目标阻抗单元进行校准。

附图说明

25.图1为现有技术中高速接口的示意图;

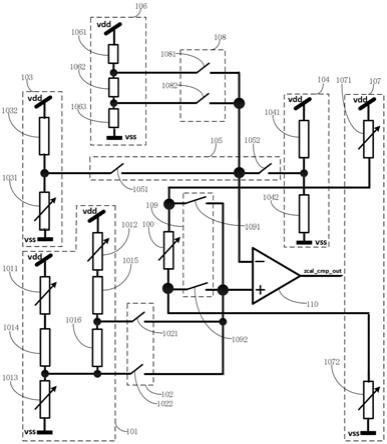

26.图2为现有技术中差分输入阻抗校准电路的示意图;

27.图3为本发明校准电路的示意图;

28.图4为本发明第一调节电阻子单元的电路示意图;

29.图5为本发明的第三调节电阻子单元的电路示意图;

30.图6为本发明目标阻抗单元的电路示意图;

31.图7为本发明校准电路在第一阶段所形成的电路示意图;

32.图8为本发明校准电路在第二阶段所形成的电路示意图;

33.图9为本发明校准电路在第三阶段所形成的电路示意图;

34.图10为本发明校准电路在第四阶段所形成的电路示意图。

具体实施方式

35.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

36.针对现有技术存在的问题,本发明的实施例提供了一种校准电路,应用于高速接口中高速接收电路中差分输入阻抗的调节。所述校准电路包括同相电压单元、反相电压单元、目标阻抗调节单元和比较器单元。

37.图3为本发明校准电路的示意图。参照图3,所述同相电压单元包括第一调节电阻单元101和第一开关单元102,所述第一调节电阻单元101与所述第一开关单元102连接,所述第一调节电阻单元101用于通过调节阻抗以向所述第一开关单元102提供不同的电压;所述反相电压单元包括第二调节电阻单元103、固定电阻单元104和第二开关单元105,所述第二调节电阻单元103和所述固定电阻单元104均与所述第二开关单元105连接,所述第二调节电阻单元103用于通过调节阻抗以向所述第二开关单元105提供不同的电压,所述固定电阻单元104用于向所述第二开关单元105提供固定的电压;所述目标阻抗调节单元包括反向电压选择单106元、第三调节电阻单元107、第三开关单元108和第四开关单元109,所述反向电压选择单元106与所述第三开关单元108连接,所述第三调节电阻单元107与所述第四开关单元109连接,所述反向电压选择单元106用于向所述第三开关单元108提供至少两种电压,所述第三调节电阻单元107用于根据所述第一调节电阻单元101的阻抗调节信息和所述第二调节电阻单元103的阻抗调节信息进行阻抗的调节,所述第三调节电阻单元107还用于连接目标阻抗单元,并通过调节所述目标阻抗单元100的阻抗以向所述第四开关单元109提供不同的电压;所述比较器单元110的同相输入端与所述第一开关单元102与所述第四开关单元109连接,所述比较器单元110的反相输入端与所述第二开关单元105、所述第三开关单元108连接,所述比较器单元用于同相输入端的电压和反相输入端的电压,以判断所述第一调节电阻单元101的阻抗、所述第二调节电阻单元103的阻抗、所述第三调节电阻单元107的阻抗以及所述目标阻抗单元100的阻抗是否调整完毕。其中,所述目标阻抗单元100即高速

接口中高速接收电路需要调节阻抗的器件。

38.参照图3,所述第一调节电阻单元101包括第一调节电阻子单元1011、第二调节电阻子单元1012、第三调节电阻子单元1013、第一电阻1014、第二电阻1015和第三电阻1016,所述第一调节电阻子单1011元的一端和所述第二调节电阻子单元1012的一端接工作电压vdd,所述第一调节电阻子单元1011的另一端连接所述第一电阻1014一端,所述第一电阻1014的另一端连接所述第三调节电阻子单元1013的一端和所述第三电阻1016的一端,所述第三调节电阻子单元1013的另一端接地vss,所述第二调节电阻子单元1012的另一端连接所述第二电阻1015的一端,所述第二电阻1015的另一端连接所述第三电阻1016的另一端。其中,所述第一调节电阻子单元1011、所述第二调节电阻子单元1012和所述第三调节电阻子单元1013的阻抗大小能够调节,所述第一电阻1014的阻抗与高速接收电路中的变压器线圈的阻抗rtcoil相同,所述第二电阻1015的阻抗为150ohm,所述第三电阻1016的阻抗为150ohm。

39.参照图3,所述第一开关单元102包括第一开关1021和第二开关1022,所述第一开关1021的一端连接所述第二电阻1015的另一端,所述第二开关1022的一端连接所述第三电阻1016的一端,所述第一开关1021的另一端和所述第二开关1022的另一端均连接所述比较器单元110的正相输入端。

40.参照图3,所述第二调节电阻单元103包括第四调节电阻子单元1031和第四电阻1032,所述第四电阻1032的一端接工作电压vdd,所述第四电阻1032的另一端连接所述第四调节电阻子单元1031的一端,所述第四调节电阻子单元1031的另一端接地vss。其中,所述第四调节电阻子单元1031的阻抗大小能够调节,所述第四电阻1032的阻抗为100ohm。

41.参照图3,所述固定电阻单元104包括第五电阻1041和第六电阻1042,所述第五电阻1041的一端接工作电压vdd,所述第五电阻1041的另一端连接所述第六电阻1042的一端,所述第六电阻1042的另一端接地vss。其中,所述第五电阻1041的阻抗为10k ohm,所述第六电阻1042的阻抗为10k ohm。

42.参照图3,所述第二开关单元105包括第三开关1051和第四开关1052,所述第三开关1051的一端连接所述第四电阻1032的另一端,所述第三开关1032的另一端连接所述比较器单元110的反相输入端,所述第四开关1052的一端连接所述第五电阻1041的另一端,所述第四开关1052的另一端连接所述比较器单元110的反相输入端。

43.参照图3,所述第三调节电阻单元107包括第五调节电阻子单元1071和第六调节电阻子单元1072,所述第五调节电阻子单元1071的一端接工作电压vdd,所述第五调节电阻子单元1071的另一端用于连接所述目标阻抗单元100的一端,所述第六调节电阻子单元1072的一端接地vss,所述第六调节电阻子单元1072的另一端用于连接所述目标阻抗单元100的另一端。

44.参照图3,所述第四开关单元109包括第五开关1091和第六开关1092,所述第五开关1091的一端连接所述第五调节电阻子单元1071的另一端,所述第六开关1092的一端连接所述第六调节电阻子单元1072的另一端,所述第五开关1091的另一端和所述第六开关1092的另一端均连接所述比较器单元110的正相输入端。

45.参照图3,所述反向电压选择单元106包括第七电阻1061、第八电阻1062和第九电阻1063,所述第七电阻1061的一端接工作电压vdd,所述第七电阻1061的另一端连接所述第

八电阻1062的一端,所述第八电阻1062的另一端连接所述第九电阻1063的一端,所述第九电阻1063的一端接地vss。其中,所述第七电阻1061的阻抗为10k ohm,所述第八电阻1062的阻抗为20k ohm,所述第九电阻1063的阻抗为10k ohm。

46.参照图3,所述第三开关单元108包括第七开关1081和第八开关1082,所述第七开关1081的一端连接所述第七电阻1061的另一端,所述第八开关1082的一端连接所述第八电阻1062的另一端,所述第七开关1081的另一端和所述第八开关1082的另一端均连接所述比较器单元110的反相输入端。

47.图4为本发明一些实施例中第一调节电阻子单元的电路示意图。所述第一调节电阻子单元、所述第二调节电阻子单元和所述第五调节电阻子单元的电路相同,以所述第一调节电阻子单元为例进行说明。参照图4,所述第一调节电阻子单元1011包括第一电阻通道单元、第二电阻通道单元和第三电阻通道单元和第四电阻通道单元。

48.参照图4,所述第一电阻通道单元包括第一pmos管10111、第二pmos管10112和第一选择电阻10113,所述第一pmos管10111的源极接工作电压vbb,所述第一pmos管10111的漏极连接所述第二pmos管10112的源极,所述第二pmos管10112的漏极连接所述第一选择电阻10113的一端,所述第一pmos管10111的栅极用于接收第四控制信号zcal_calp<3>,所述第二pmos管10112的栅极接地vss,当zcal_calp<3>=1,即向所述第一pmos管10111的栅极施加高电平,所述第一pmos管10111导通,当zcal_calp<3>=0,即向所述第一pmos管10111的栅极施加低电平,所述第一pmos管10111关断。

49.参照图4,所述第二电阻通道单元包括第三pmos管10114、第四pmos管10115和第二选择电阻10116,所述第三pmso管10114的源极接工作电压vbb,所述第三pmos管10114的漏极连接所述第四pmos管10115的源极,所述第四pmos管10115的漏极连接所述第二选择电阻10116的一端,所述第三pmos管10114的栅极用于接收第三控制信号zcal_calp<2>,所述第四pmos管10115的栅极接地vss,当zcal_calp<2>=1,即向所述第三pmos管10114的栅极施加高电平,所述第三pmos管10114导通,当zcal_calp<2>=0,即向所述第三pmos管10114的栅极施加低电平,所述第三pmos管10114关断。

50.参照图4,所述第三电阻通道单元包括第五pmos管10117、第六pmos管10118和第三选择电阻10119,所述第五pmso管10117的源极接工作电压vbb,所述第五pmos管10117的漏极连接所述第六pmos管10118的源极,所述第六pmos管10118的漏极连接所述第三选择电阻10119的一端,所述第五pmos管10117的栅极用于接收第二控制信号zcal_calp<1>,所述第六pmos管10118的栅极接地vss,当zcal_calp<1>=1,即向所述第五pmos管10117的栅极施加高电平,所述第五pmos管10117导通,当zcal_calp<1>=0,即向所述第五pmos管10117的栅极施加低电平,所述第五pmos管10117关断。

51.参照图4,所述第四电阻通道单元包括第七pmos管101110、第八pmos管101111和第四选择电阻101112,所述第七pmso管101110的源极接工作电压vbb,所述第七pmos管101110的漏极连接所述第八pmos管101111的源极,所述第八pmos管101111的漏极连接所述第四选择电阻101112的一端,所述第七pmos管101110的栅极用于接收第一控制信号zcal_calp<0>,所述第八pmos管101111的栅极接地vss,当zcal_calp<0>=1,即向所述第七pmos管101110的栅极施加高电平,所述第七pmos管101110导通,当zcal_calp<0>=0,即向所述第七pmos管101110的栅极施加低电平,所述第七pmos管101110关断。

52.一些实施例中,所述第一调节电阻子单元中所述第一选择电阻的另一端、所述第二选择电阻的另一端、所述第三选择电阻的另一端和所述第四选择电阻的另一端均连接所述第一电阻的一端;所述第二调节电阻子单元中所述第一选择电阻的另一端、所述第二选择电阻的另一端、所述第三选择电阻的另一端和所述第四选择电阻的另一端均连接所述第二电阻的一端;所述第五调节电阻子单元中所述第一选择电阻的另一端、所述第二选择电阻的另一端、所述第三选择电阻的另一端和所述第四选择电阻的另一端均连接所述第五开关的一端。

53.参照图4,所述第一选择电阻10113的阻抗、所述第二选择电阻10116的阻抗、所述第三选择电阻10119的阻抗和所述第四选择电阻101112的阻抗的比值为1:2:4:8。具体地,所述第一选择电阻10113的阻抗为50ohm,所述第二选择电阻10116的阻抗为100ohm,所述第三选择电阻10119的阻抗为200ohm,所述第四选择电阻101112的阻抗为400ohm。

54.一些实施例中,所述第一调节电阻子单元、所述第二调节电阻子单元和所述第五调节电阻子单元的控制信号格式相同,所述第一调节电阻子单元的控制信号为zcal_calp<3:0>,所述第二调节电阻子单元的控制信号为zcal_biasp<3:0>,所述第五调节电阻子单元的控制信号为tunep_diff<3:0>,以所述第一调节电阻子单元的控制信号zcal_calp<3:0>为例,zcal_calp<3:0>为4位数的二进制数值信号,所述第五控制信号、所述第六控制信号、所述第七控制信号和所述第八控制信号各对应zcal_calp<3:0>中的1位。例如,当zcal_calp<3:0>=0000,则zcal_calp<0>=0,zcal_calp<1>=0,zcal_calp<2>=0,zcal_calp<3>=0;当zcal_calp<3:0>=1111,则zcal_calp<0>=1,zcal_calp<1>=1,zcal_calp<2>=1,zcal_calp<3>=1;当zcal_calp<3:0>=0100,则zcal_calp<0>=0,zcal_calp<1>=0,zcal_calp<2>=1,zcal_calp<3>=0;当zcal_calp<3:0>=0110,则zcal_calp<0>=0,zcal_calp<1>=1,zcal_calp<2>=1,zcal_calp<3>=0。

55.图5为本发明一些实施例中第三调节电阻子单元的电路示意图。所述第三调节电阻子单元、所述第四调节电阻子单元和所述第六调节电阻子单元的电路相同,以所述第三调节电阻子单元为例进行说明。参照图5,所述第三调节电阻子单元包括第五电阻通道单元、第六电阻通道单元和第七电阻通道单元和第八电阻通道单元。

56.参照图5,所述第五电阻通道单元包括第一nmos管10131、第二nmos管10132和第五选择电阻10133,所述第一nmos管10131的源极接地vss,所述第一nmos管10131漏极连接所述第二nmos管10132的源极,所述第二nmos管10132的漏极连接所述第五选择电阻10133的一端,所述第一nmos管10131的栅极用于接收第八控制信号zcal_caln<3>,所述第二nmos管10132的栅极接工作电压vdd,当zcal_caln<3>=1,即向所述第一nmos管10131的栅极施加高电平,则所述第一nmos管10131导通,当zcal_caln<3>=0,即向所述第一nmos管10131的栅极施加低电平,则所述第一nmos管10131关断。

57.参照图5,所述第六电阻通道单元包括第三nmos管10134、第四nmos管10135和第六选择电阻10136,所述第三nmos管10134的源极接地vss,所述第三nmos管10134的漏极连接所述第四nmos管10135的源极,所述第四nmos管10135的漏极连接所述第六选择电阻10136的一端,所述第三nmos管10134的栅极用于接收第七控制信号zcal_caln<2>,所述第四nmos管10135的栅极接工作电压vdd,当zcal_caln<2>=1,即向所述第四nmos管10135的栅极施加高电平,则所述第三nmos管10134导通,当zcal_caln<2>=0,即向所述第四nmos管10135

的栅极施加低电平,则所述第三nmos管10134关断。

58.参照图5,所述第六电阻通道单元包括第五nmos管10137、第六nmos管10138和第七选择电阻10139,所述第五nmos管10137的源极接地vss,所述第五nmos管10137的漏极连接所述第六nmos管10138的源极,所述第六nmos管10138的漏极连接所述第七选择电阻10139的一端,所述第五nmos管10137的栅极用于接收第六控制信号zcal_caln<1>,所述第六nmos管10138的栅极接工作电压vdd,当zcal_caln<1>=1,即向所述第五nmos管10137的栅极施加高电平,则所述第五nmos管10137导通,当zcal_caln<1>=0,即向所述第五nmos管10137的栅极施加低电平,则所述第五nmos管10137关断。

59.参照图5,所述第六电阻通道单元包括第七nmos管101310、第八nmos管101311和第八选择电阻101312,所述第七nmos管101310的源极接地vss,所述第七nmos管101310的漏极连接所述第八nmos管101311的源极,所述第八nmos管101311的漏极连接所述第八选择电阻101312的一端,所述第七nmos管101310的栅极用于接收第五控制信号zcal_caln<0>,所述第八nmos管101312的栅极接工作电压vdd,当zcal_caln<0>=1,即向所述第七nmos管101310的栅极施加高电平,所述第七nmos管101310导通,当zcal_caln<0>=0,即向所述第七nmos管101310的栅极施加低电平,所述第七nmos管101310关断。

60.一些实施例中,所述第三调节电阻子单元中所述第五选择电阻的另一端、所述第六选择电阻的另一端、所述第七选择电阻的另一端和所述第八选择电阻的另一端均连接所述第一电阻的另一端;所述第四调节电阻子单元中所述第五选择电阻的另一端、所述第六选择电阻的另一端、所述第七选择电阻的另一端和所述第八选择电阻的另一端均连接所述第四电阻的另一端;所述第六调节电阻子单元中所述第五选择电阻的另一端、所述第六选择电阻的另一端、所述第七选择电阻的另一端和所述第八选择电阻的另一端均连接所述第六开关的一端。

61.参照图5,所述第五选择电阻10133的阻抗、所述第六选择电阻10136的阻抗、所述第七选择电阻10139的阻抗和所述第八选择电阻101312的阻抗的比值为1:2:4:8。具体地,所述第五选择电阻10133的阻抗为50ohm,所述第六选择电阻10136的阻抗为100ohm,所述第七选择电阻10139的阻抗为200ohm,所述第八选择电阻101312的阻抗为400ohm。

62.一些实施例中,所述第三调节电阻子单元、所述第四调节电阻子单元和所述第六调节电阻子单元的控制信号格式相同,所述第三调节电阻子单元的控制信号为zcal_caln<3:0>,所述第四调节电阻子单元的控制信号为zcal_baisn<3:0>,所述第六调节电阻子单元的控制信号为tunen_diff<3:0>,以所述第三调节电阻子单元的控制信号zcal_caln<3:0>为例,zcal_caln<3:0>为4位数的二进制数值信号,所述第五控制信号、所述第六控制信号、所述第七控制信号和所述第八控制信号各对应zcal_caln<3:0>中的1位。例如,当zcal_caln<3:0>=0000,则zcal_caln<0>=0,zcal_caln<1>=0,zcal_caln<2>=0,zcal_caln<3>=0;当zcal_caln<3:0>=1111,则zcal_caln<0>=1,zcal_caln<1>=1,zcal_caln<2>=1,zcal_caln<3>=1;当zcal_caln<3:0>=0100,则zcal_caln<0>=0,zcal_caln<1>=0,zcal_caln<2>=1,zcal_caln<3>=0;当zcal_caln<3:0>=0110,则zcal_caln<0>=0,zcal_caln<1>=1,zcal_caln<2>=1,zcal_caln<3>=0。

63.图6为目标阻抗单元的电路示意图。参照图6,所述目标阻抗单元100包括第一目标阻抗通道单元、第二目标阻抗通道单元、第三目标阻抗通道单元、第四目标阻抗通道单元、

第五目标阻抗通道单元以及第六目标阻抗通道单元。

64.参照图6,所述第一目标阻抗通道单元包括第一目标电阻1001、第一目标开关1002、第二目标开关1003以及第二目标电阻1004,所述第一目标电阻1002的一端连接所述第一目标开关1002的一端,所述第一目标开关1002的另一端连接所述第二目标开关1003的一端,所述第二目标开关1003的另一端连接所述第二目标电阻1004的一端,所述第一目标开关1001和所述第二目标开关1003的控制信号均为第六目标控制信号zcal_diff<5>,当zcal_diff<5>=1,所述第一目标开关1001和所述第二目标开关1003导通,当zcal_diff<5>=0,所述第一目标开关1001和所述第二目标开关1003关断。

65.参照图6,所述第一目标阻抗通道单元包括第三目标电阻1005、第三目标开关1006、第四目标开关1007以及第四目标电阻1008,所述第三目标电阻1005的一端连接所述第三目标开关1006的一端,所述第三目标开关1006的另一端连接所述第四目标开关1007的一端,所述第四目标开关1007的另一端连接所述第四目标电阻1008的一端,所述第三目标开关1006和所述第四目标开关1007的控制信号均为第五目标控制信号zcal_diff<4>,当zcal_diff<4>=1,所述第三目标开关1006和所述第四目标开关1007导通,当zcal_diff<4>=0,所述第三目标开关1006和所述第四目标开关1007关断。

66.参照图6,所述第一目标阻抗通道单元包括第五目标电阻1009、第五目标开关10010、第六目标开关10011以及第六目标电阻10012,所述第五目标电阻1009的一端连接所述第五目标开关10010的一端,所述第五目标开关10010的另一端连接所述第六目标开关10011的一端,所述第六目标开关10011的另一端连接所述第六目标电阻10012的一端,所述第五目标开关10010和所述第六目标开关10011的控制信号均为第四目标控制信号zcal_diff<3>,当zcal_diff<3>=1,所述第五目标开关10010和所述第六目标开关10011导通,当zcal_diff<3>=0,所述第五目标开关10010和所述第六目标开关10011关断。

67.参照图6,所述第一目标阻抗通道单元包括第七目标电阻10013、第七目标开关10014、第八目标开关10015以及第八目标电阻10016,所述第七目标电阻10013的一端连接所述第七目标开关10014的一端,所述第七目标开关10014的另一端连接所述第八目标开关10015的一端,所述第八目标开关10015的另一端连接所述第八目标电阻10016的一端,所述第七目标开关10014和所述第八目标开关10015的控制信号均为第三目标控制信号zcal_diff<2>,当zcal_diff<2>=1,所述第七目标开关10014和所述第八目标开关10015导通,当zcal_diff<2>=0,所述第七目标开关10014和所述第八目标开关10015关断。

68.参照图6,所述第一目标阻抗通道单元包括第九目标电阻10017、第九目标开关10018、第十目标开关10019以及第十目标电阻10020,所述第九目标电阻10017的一端连接所述第九目标开关10018的一端,所述第九目标开关10018的另一端连接所述第十目标开关10019的一端,所述第十目标开关10019的另一端连接所述第十目标电阻10020的一端,所述第九目标开关10018和所述第十目标开关10019的控制信号均为第二目标控制信号zcal_diff<1>,当zcal_diff<1>=1,所述第九目标开关10018和所述第十目标开关10019导通,所述第九目标开关10018和所述第十目标开关10019关断。

69.参照图6,所述第一目标阻抗通道单元包括第十一目标电阻10021、第十一目标开关10022、第十二目标开关10023以及第十二目标电阻10024,所述第十一目标电阻10021的一端连接所述第十一目标开关10022的一端,所述第十一目标开关10022的另一端连接所述

第十二目标开关10023的一端,所述第十二目标开关10023的另一端连接所述第十二目标电阻10024的一端,所述第十一目标开关10022和所述第十二目标开关10023的控制信号均为第一目标控制信号zcal_diff<0>,当zcal_diff<0>=1,所述第十一目标开关10022和所述第十二目标开关10023导通,当zcal_diff<0>=0,所述第十一目标开关10022和所述第十二目标开关10023关断。

70.参照图6,所述第一目标电阻1001、所述第三目标电阻1005、所述第五目标电阻1009、所述第七目标电阻10013、所述第九目标电阻10017和所述第十一目标电阻10021的阻抗比为1:2:4:8:16:32。

71.参照图6,所述第二目标电阻1004、所述第四目标电阻1008、所述第六目标电阻10012、所述第八目标电阻10016、所述第十目标电阻10020和所述第十二目标电阻10024的阻抗比为1:2:4:8:16:32。

72.参照图6,所述第一目标电阻1001和所述第二目标电阻1004的阻抗相同,所述第三目标电阻1005和所述第四目标电阻1008的阻抗相同,所述第五目标电阻1009和所述第六目标电阻10012的阻抗相同,所述第七目标电阻10013和所述第八目标电阻10016的阻抗相同,所述第九目标电阻10017和所述第十目标电阻10020的阻抗相同,所述第十一目标电阻10021和所述第十二目标电阻10024的阻抗相同。

73.参照图6,所述第一目标电阻1001和所述第二目标电阻1004的阻抗为50ohm,所述第三目标电阻1005和所述第四目标电阻1008的阻抗为100ohm,所述第五目标电阻1009和所述第六目标电阻10012的阻抗为200ohm,所述第七目标电阻10013和所述第八目标电阻10016的阻抗为400ohm,所述第九目标电阻10017和所述第十目标电阻10020的阻抗为800ohm,所述第十一目标电阻10021和所述第十二目标电阻10024的阻抗为1600ohm。

74.一些实施例中,所述目标阻抗单元的控制信号为zcal_diff<5:0>,zcal_diff<5:0>为6位数的二进制数值信号,所述第一目标控制信号、所述第二目标控制信号、所述第三目标控制信号、所述第四目标控制信号、所述第五目标控制信号和所述第六目标控制信号各对应zcal_diff<5:0>中的1位。例如,当zcal_diff<5:0>=000000,则zcal_diff<0>=0,zcal_diff<1>=0,zcal_diff<2>=0,zcal_diff<3>=0,zcal_diff<4>=0,zcal_diff<5>=0;当zcal_diff<5:0>=000001,则zcal_diff<0>=1,zcal_diff<1>=0,zcal_diff<2>=0,zcal_diff<3>=0,zcal_diff<4>=0,zcal_diff<5>=0;当zcal_diff<5:0>=001001,则zcal_diff<0>=1,zcal_diff<1>=0,zcal_diff<2>=0,zcal_diff<3>=1,zcal_diff<4>=0,zcal_diff<5>=0。

75.一些实施例中,所述比较器单元为电压比较器或电流比较器。

76.参照图3、图7~图10,所述校准电路进行校准包括第一阶段、第二阶段、第三阶段和第四阶段,具体过程如下:

77.图3中令所述第二开关1022和所述第三开关1051导通,同时另所述第一开关1021、所述第四开关1052、所述第七开关1081、所述第八开关1082、所述第五开关1091和所述第六开关1092关断,以形成如图8所示电路,所述校准电路进入校准的第一阶段;

78.令所述第四调节电阻子单元1031的控制信号zcal_biasn<3:0>与所述第三调节电阻子单元1013的控制信号zcal_caln<3:0>相同,均等于初始值,同时所述第二调节电阻子单元1012的控制信号zcal_biasp<3:0>=1111,所述第二调节电阻子单元1012偏置到关闭

状态,所述第六调节电阻子单元1072的控制信号tunen_diff<3:0>=0000,以将所述第六调节电阻子单元1072偏置到关闭状态,所述第五调节电阻子单元1071的控制信号tunep_diff<3:0>=1111,以将所述第五调节电阻子单元1071偏置到关闭状态,所述目标阻抗单元100的控制信号zcal_diff<5:0>=000000,以将所述目标阻抗单元100偏置到关闭状态;其中,所述初始值为在仿真下使所述第三调节电阻子单元和所述第四调节电阻子单元的电阻值均为300ohm的控制信号,由于生产工艺的差异,所述初始值存在一定的差异,例如,所述初始值可以为1000或0101。

79.令所述第一调节电阻子单元1011的控制信号zcal_calp<3:0>=1111,然后判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,如果判断所述比较器单元110输出的比较结果zcal_cmp_out不等于1,则将所述第一调节电阻子单元1011的控制信号zcal_calp<3:0>减1,然后重新判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,直至所述比较器单元110输出的比较结果zcal_cmp_out等于1,同时记录此时所述第一调节电阻子单元1011的控制信号zcal_calp<3:0>,例如此时的zcal_calp<3:0>=codep,所述校准电路进入校准的第一阶段结束;其中,将所述第一调节电阻子单元1011的控制信号zcal_calp<3:0>减1的具体过程,例如,当zcal_calp<3:0>=1111,则zcal_calp<3:0>

‑

1=1110,当zcal_calp<3:0>=1110,则zcal_calp<3:0>

‑

1=1101,当zcal_calp<3:0>=1101,则zcal_calp<3:0>

‑

1=1100。

80.图3中令所述第一开关1021和所述第四开关1052导通,同时令所述第二开关1022、所述第三开关1051、所述第七开关1081、所述第八开关1082、所述第五开关1091和所述第六开关1092关断,以形成如图9所示电路,所述校准电路进入校准的第二阶段;

81.令所述第二调节电阻子单元1012的控制信号zcal_biasp<3:0>=codep,同时所述第一调节电阻子单元1011的控制信号zcal_calp<3:0>=1111,以将所述第一调节电阻子单元1011偏置到关闭状态,所述第四调节电阻子单元1031的控制信号zcal_biasn<3:0>为0000,以将所述第四调节电阻子单元1031偏置到关闭状态,所述第六调节电阻子单元1072的控制信号tunen_diff<3:0>=0000,以将所述第六调节电阻子单元1072偏置到关闭状态,所述第五调节电阻子单元1071的控制信号tunep_diff<3:0>=1111,以将所述第五调节电阻子单元1071偏置到关闭状态,所述目标阻抗单元100的控制信号zcal_diff<5:0>=000000,以将所述目标阻抗单元100偏置到关闭状态;

82.令所述第三调节电阻子单元1013的控制信号zcal_caln<3:0>=1111,然后判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,如果判断所述比较器单元110输出的比较结果zcal_cmp_out不等于1,则将所述第三调节电阻子单元1013的控制信号zcal_caln<3:0>减1,然后重新判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,直至所述比较器单元110输出的比较结果zcal_cmp_out等于1,同时记录此时的zcal_caln<3:0>,例如此时所述第三调节电阻子单元1013的控制信号zcal_caln<3:0>=coden,所述校准电路进入校准的第二阶段结束;其中,将所述第三调节电阻子单元1013的控制信号zcal_caln<3:0>减1的具体过程,例如,当zcal_caln<3:0>=1111,则zcal_caln<3:0>

‑

1=1110,当zcal_caln<3:0>=1110,则zcal_caln<3:0>

‑

1=1101,当zcal_caln<3:0>=1101,则zcal_caln<3:0>

‑

1=1100。

83.图3中令所述第八开关1082和所述第六开关1092导通,同时令所述第二开关1022、

所述第三开关1051、所述第一开关1021、所述第四开关1052、所述第七开关1081和所述第五开关1091关断,以形成如图9所示电路,所述校准电路进入校准的第三阶段;

84.令1072的控制信号tunen_diff<3:0>=coden、1071的控制信号tunep_diff<3:0>=codep;

85.令所述目标阻抗单元的控制信号zcal_diff<5:0>=000000,然后判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,如果判断所述比较器单元110输出的比较结果zcal_cmp_out不等于1,则将所述目标阻抗单元100的控制信号zcal_diff<5:0>加1,然后重新判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,直至所述比较器单元110输出的比较结果zcal_cmp_out等于1,同时记录此时的zcal_diff<5:0>,例如此时的zcal_diff<5:0>=code_diff1,所述校准电路进入校准的第三阶段结束;其中,将所述目标阻抗单元的控制信号zcal_diff<5:0>加1的具体过程,例如,当zcal_diff<5:0>=000000,则zcal_diff<5:0> 1=000001,当zcal_diff<5:0>=000001,则zcal_diff<5:0> 1=000010,当zcal_diff<5:0>=000010,则zcal_diff<5:0> 1=000011。

86.图3中令所述第七开关1081和所述第五开关1091导通,同时令所述第二开关1022、所述第三开关1051、所述第一开关1021、所述第四开关1052、所述第八开关1082和所述第六开关1092关断,以形成如图10所示电路,所述校准电路进入校准的第四阶段;

87.令所述目标阻抗单元100的控制信号zcal_diff<5:0>=111111,然后判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,如果判断所述比较器单元110输出的比较结果zcal_cmp_out不等于1,则将所述目标阻抗单元100的控制信号zcal_diff<5:0>减1,然后重新判断所述比较器单元110输出的比较结果zcal_cmp_out是否等于1,直至所述比较器单元110输出的比较结果zcal_cmp_out等于1,同时记录此时的所述目标阻抗单元100的控制信号zcal_diff<5:0>,例如此时的zcal_diff<5:0>=code_diff2,所述校准电路进入校准的第四阶段结束;其中,将所述目标阻抗单元100的控制信号zcal_diff<5:0>减1的具体过程,例如,当zcal_diff<5:0>=111111,则zcal_diff<5:0>

‑

1=111110,当zcal_diff<5:0>=111110,则zcal_diff<5:0>

‑

1=111101,当zcal_diff<5:0>=111101,则zcal_diff<5:0>

‑

1=111100。

88.计算code_diff1和code_diff2的平均值,以得到所述目标阻抗单元100的控制信号zcal_diff<5:0>,若控制信号zcal_diff<5:0>的出现小数,则舍弃小数点之后的数;例如,若code_diff1=111001,code_diff2=110101,则zcal_diff<5:0>=110111,若code_diff1=111001,code_diff2=110100,则zcal_diff<5:0>=110110。

89.一些实施例中,在所述校准电路进入校准的第三阶段结束时,

90.rtt_d1=3*rtt_m

‑

rtt_p,

91.其中,rtt_m为所述第三调节电阻子单元1013的阻抗,rtt_p为所述第一调节电阻子单元1011的阻抗,rtt_d1为所述校准电路进入校准的第三阶段结束时所述目标阻抗单元差分阻抗;

92.在所述校准电路进入校准的第四阶段结束时,

93.rtt_d2=3*rtt_p

‑

rtt_m,

94.其中,rtt_m为所述第三调节电阻子单元1013的阻抗,rtt_p为所述第一调节电阻子单元1011的阻抗,rtt_d2为所述校准电路进入校准的第四阶段结束时所述目标阻抗单元差分阻抗;

95.计算rtt_d1和rtt_d2的平均可以得到:

96.rtt_d=(rtt_d1 rtt_d2)/2=rtt_p rtt_m,其中rtt_d为所述目标阻抗单元的阻抗;

97.由于rtt_m rtcoil=50ohm,rtt_p rtcoil=50ohm,所以高速接收电路的差分输入阻抗rtt=rtt_m rtt_p 2

×

rtcoil=100ohm。

98.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。