一种基于ddr sdram的sar成像数据转置处理系统

技术领域

1.本发明属于雷达成像信号技术领域,具体涉及一种基于ddr sdram的sar成像数据转置处理系统。

背景技术:

2.合成孔径雷达(synthetic aperture radar,sar)具有全天时,全天候的工作特点以及高分辨的成像精度,其已经在多云雾地区遥感测图、军事侦察、国民经济建设等方面发挥着巨大作用。近些年来,随着硬件制造水平的快速发展,sar实时成像系统设计收到越来越多的研究。而sar成像信号处理过程中涉及到大数据量的传输和存储,由于成像处理过程中数据的访问需要在距离维和方位维之间进行切换,因此转置效率的高低直接关系到sar成像信号处理的快慢。

3.目前ddr sdram(双倍速率同步动态随机存储器)由于存储量大,速度快,功耗低,成本低等优点在sar成像信号处理中得到越来越多的应用。在基于ddr sdram的sar成像处理系统中,在之前的研究中有两页式或三页式转置方法,该方法通过循环访问两片或者三片sdram来实现矩阵转置,实现较为简单,但是占用的外部存储资源较多,而且由于采用了多块sdram导致系统体积比较大,系统功耗比较高,不利于sar成像系统的小型化发展。南京电子技术研究所吴沁文发表的论文“基于fpga和ddr的高效率矩阵转置方法”将数据从行维上拆解,使原来的一行数据排成一个新的小矩阵以此来平衡读写效率,但是该方法中读写地址的计算方法依赖于矩阵规模以及ddr sdram行列长度,算法移植难度较大,而且在读写平衡之外,读访问效率的提高是以写访问效率的下降为代价的,同理若想提高写访问效率那么必然要降低读访问效率,无法做到同时提高读写效率,在读取数据时无法利用ddr sdram的突发传输技术。西安电子工程研究所刘晨等人发表的论文“基于ddr sdram的ctm算法与实现”提出最快列读取矩阵转置算法,首先接收两条方位向数据,将两条数据相间拼合写入到ddr sdram中,这种方法可以做到列数据顺序排列从而顺序读出,但是该算法与sar成像的距离向和方位向数据长度有关,算法的稳定性和可移植性较差。

技术实现要素:

4.为了克服现有技术中存在的缺陷,本发明提出了一种基于ddr sdram的sar成像数据转置处理系统,该系统通过使用fpga中的ram资源缓存多条行数据,然后利用ddr sdram的突发传输技术将数据写入到ddr sdram中。

5.本发明的技术方案如下:

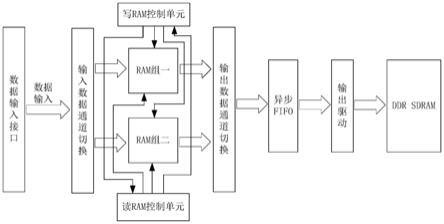

6.一种基于ddr sdram的sar成像数据转置处理系统,其特征在于,包括数据输入接口、输入数据通道切换模块、写ram控制单元、读ram控制单元、第一ram组、第二ram组、输出数据通道选择模块、异步fifo、输出驱动和ddr sdram;其中,所述第一ram组和第二ram组均具有n个独立的ram块,所有ram块的数据输入位宽相同,深度相同,每一个ram块都有独立的写使能信号输入端口、写地址信号输入端口、写数据输入总线、读使能信号输入端口、读地

址信号输入端口和读数据输出总线;所述写ram控制单元内部有两个计数器,分别是第一写计数器和第二写计数器,读ram控制单元内部有一个读计数器;

7.所述数据输入接口输出端接输入数据通道切换模块的输入端,第一ram组和第二ram组的写数据输入总线连接输入数据通道切换模块的输出端,第一ram组和第二ram的写使能端口连接写ram控制单元的使能信号输出端口,第一ram组和第二ram的写地址端口连接写ram控制单元的地址信号输出端口;第一ram组和第二ram组的读数据输出总线连接输出数据通道切换模块的输入端,第一ram组和第二ram的读使能端口连接读ram控制单元的使能信号输出端口,第一ram组和第二ram的读地址端口连接读ram控制单元的地址信号输出端口;写ram控制单元的ram组可读标志信号输出端口连接到读ram控制单元的可读标志信号输入端口;读ram控制单元的ram组可写标志信号输出端口连接到写ram控制单元的可写标志信号输入端口;输出数据通道切换模块的输出端接异步fifo的输入端;异步fifo的输出端连接到输出驱动的输入端,输出驱动的输出端连接到ddr sdram的用户接口;

8.所述输入数据切换通道用于数据输入到ram组之间的数据通路选择;输出数据切换通道用于ram组到异步fifo之间的数据通路选择;

9.写ram控制单元在第一写计数器和第二写计数器的控制下产生相应的写使能信号以及相应的写地址信号,从而将输入数据写入到第一ram组或第二ram组中,同时将当前写入的ram组可读标志信号置为0;第一写计数器每次自加步长为1,写地址信号每次自加1,第一写计数器达到设定的第一写上限值后,第一写计数器清零并重新开始计数,写地址信号清零并重新开始增加;第一写计数器每次达到设定的第一写上限值后,写ram控制单元产生写下一ram块的使能信号;第一写计数器每次达到设定的第一写上限值后,第二写计数器自加1,达到设定的第二写上限值后,第二写计数器清零并重新开始计数;第一写计数器达到设定的第一写上限值并且第二写计数器达到设定的第二写上限值后,写ram控制单元产生写另一ram组ram块1的使能信号,并将当前写入的ram组可读标志信号置为1;

10.读ram控制单元在读计数器的控制下产生相应的读使能信号以及相应的读地址信号,从而将指定的ram空间中的数据输出到输出数据通道切换模块,同时将当前ram组的可写标志信号置为0;读计数器每次自加步长为1,读地址信号每次自加1,读计数器达到设定的读上限值后,读计数器清零并重新开始计数,读地址信号清零并重新开始增加;读计数器每次达到设定的读上限值后,读ram控制单元产生读另一ram组的使能信号,并将当前ram组的可写标志信号置为1;

11.异步fifo用于跨时钟域的数据传输,其数据输入端位宽等于单个ram组中所有ram块的数据输出的位宽之和,数据输出端位宽等于单个ram块数据输出位宽的8倍;

12.输出驱动将从异步fifo中读出的数据写入到ddr sdram中,从两个ram组中读出的数据写入到ddr sdram的起始地址增加量等于每一ram组中ram块的个数;单个ram组中同一地址上的数据写入到ddr sdram中的相邻地址中,相邻地址上的数据写入到ddr sdram中的地址增加量等于输入数据的列长度。

13.进一步的,数据输入接口输入数据是按行顺序输入。

14.进一步的,所述第一ram组和第二ram组中ram块的个数为8的整数倍,每个ram块的数据输入位宽等于输入数据的位宽,深度等于输入数据的行长度。

15.进一步的,所述第一写上限值等于ram块的深度,第二写上限值等于每组ram中的

ram块数,读上限值等于ram块的深度。

16.本发明的有益效果为,可以利用ddr sdram的突发传输技术将数据写入到ddr sdram中,可以通过增加ram块的数量来提高行数据写入到ddr sdram中的效率,可以使得转置后列数据地址连续,因此可以以最快的速度读出转置后的列数据,并且该系统中访问ddr sdram的地址计算方式简单,具有很好的稳定性以及可移植性。

附图说明

17.图1是本发明一种基于ddr sdram的sar成像数据转置处理系统的实现框图;

18.图2是本发明中待转置的矩阵数据排布方式以及数据读取顺序;

19.图3是本发明中首次写入的待转置矩阵数据在两组ram中的数据排布方式;

20.图4是本发明中两组ram中的数据的读取顺序;

21.图5是本发明中转置后的数据在ddr sdram中的排布方式。

具体实施方式

22.下面结合附图,详细说明本发明的技术方案。

23.如图1所示,本发明提出的一种基于ddr sdram的sar成像数据转置处理系统包括数据输入接口、输入数据通道切换、写ram控制单元、读ram控制单元、第一ram组、第二ram组、输出数据通道选择、异步fifo、输出驱动以及ddr sdram。

24.除ddr sdram外,其余模块均在fpga上进行实现,fpga选用xilinx公司的xcku040

‑

ffva1156

‑2‑

e芯片。ddr sdram芯片型号为micron公司的mt40a256m16ha

‑

083e,是ddr4 sdram,突发传输长度设置为8。开发环境为xilinx的vivado 2018.3,ddr sdram读写接口使用vivado提供的mig核。

25.该具体实施方案中,待转置矩阵大小为4096 4096,设置两组ram,每组中有16个ram块,每个ram块的寻址空间大小为4096。

26.本发明的每个模块的作用以及工作原理为:

27.输入数据按行顺序通过输入数据通道切换模块送到到第一ram组上的所有ram块的输入数据总线上。

28.写ram控制单元将第一ram组的可读标志信号置为0,然后使能第一ram组中ram块1的写功能,每写入一个数据第一写计数器自加1,写地址信号自加1。当第一写计数器达到设定的第一写上限值也即是等于4096时,写ram控制单元关闭第一ram组中ram块1的写功能,打开第一ram组中ram块2的写功能,第一写计数器清零,写地址信号清零,将数据顺序写入到第一ram组的ram块2中。

29.依次将数据写入到第一ram组中的其它ram块中,每写满一个ram块第二写计数器自加1。直到写满第一ram组中的所有ram块,此时第一写计数器等于4096,第二写计数器等于16。此时将第一ram组的可读标志信号置为1。

30.写ram控制单元关闭第一ram组中ram块16的写功能,将第二ram组的可读标志信号置为0,打开第二ram组中ram块1的写功能,将数据顺序写入到第二ram组的ram块1中。按照写第一ram组的方法将数据写入到第二ram组中,直到第二ram组写满,此时将第二ram组的可读标志置为1。

31.读ram控制单元在写ram控制单元将第一ram组的可读标志信号置为1之后,将第一ram组的可写信号标志置为0,开始从第一ram组中顺序读取数据。

32.读ram控制单元使能第一ram组中全部ram块的读使能,通过连接到第一ram组中所有ram块的读地址信号,依次顺序将第一ram组中所有ram块同一地址上的数据读出。

33.首先读出第一ram组中16个ram块中地位为0的16个数据,写入ddr sdram的起始地址为0,16个数据在ddr sdram中地址连续。然后读出地址为1的16个数据,起始写入ddr sdram的地址增量等于输入数据行长度4096,16个数据在ddr sdram中地址连续。

34.每读出一次数据,读计数器自加1,读地址信号自加1。

35.当完成第一ram组所有数据的读取之后,此时读计数器达到设定的读上限值4096,读ram控制单元将第一ram组可写信号标志置为1。

36.读ram控制单元在写ram控制单元将第二ram组的可读标志信号置为1之后,将第二ram组的可写信号标志置为0,开始从第二ram组中顺序读取数据。

37.从第二ram组读取数据写入到ddr sdram的方法和从第一ram组读取数据写入到ddr sdram的方法相同,只是第二ram组中16个ram块地址为0的16个数据写入ddr sdram的起始地址相较于第一ram组而言增加一个固定值16,该值等于单个ram组中ram块的个数。

38.以上每完成两组ram的数据写入是一个写循环,每完成两组ram的数据读出是一个读循环,读写循环依序循环进行。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。