1.本公开涉及计算机技术领域,尤其是一种基于磁性缓存的存内计算电路、芯片和计算装置。

背景技术:

2.随着人工智能(artificial intelligent,ai)和物联网(internet of things,iot)应用的快速发展,中央处理器(cpu)和存储电路(memory)之间需要经由有限的总线带宽进行频繁且大量的数据传输,这也被公认为目前传统的冯诺依曼架构体系中的最大的瓶颈。深度神经网络作为目前在人工智能领域中应用于图像识别的最成功的算法之一,它需要对输入数据和权重数据做大量的读写,乘法和加法运算。这也意味着需要更大数目的数据传输和更多的能量消耗。值得注意的是,在不同的ai任务下,读写数据所消耗的能量远远大于计算数据的能量。

3.为了打破冯诺依曼架构中的这一瓶颈,存算一体架构被提出。这种系统架构不仅保留了存储电路本身所具有的存储和读写功能,同时可以支持不同的逻辑或者乘加运算,从而在很大程度上减少了中央处理器和存储器电路之间频繁的总线交互,也进一步降低了大量的数据搬移量,提升了系统的能耗效率。在目前的基于存算一体架构的深度神经网络处理器中,权重数据(weight)可以不经过读取就直接进行mac(乘加,multiplication and computation,mac)运算,并直接得出最终的乘加结果。

4.虽然可以避免权重数据的读取,但是输入和输出数据(input/output activation)仍旧需要对片上缓冲(buffer)进行访存。由于存内计算的计算特点,对于片上缓冲提出了多方面的需求:第一,为了避免频繁的片外(off

‑

chip)访存,通常需要设计足够容量的片上缓冲来存储activation数据;第二,片上缓冲需要提供足够高的访存带宽来匹配存内计算单元的计算吞吐;第三,片上缓冲需要尽量降低访存的能耗,从而提升存内计算的整体计算能效。

技术实现要素:

5.本公开的实施例提供了一种基于磁性缓存的存内计算电路,该电路包括:至少一个磁性缓存单元、至少一个存内计算单元、定时器;其中,至少一个磁性缓存单元中的磁性缓存单元,用于在对应的数据保持时间内,缓存对应的存内计算单元输出的数据作为待处理数据;定时器,用于对至少一个磁性缓存单元分别设定数据保持时间,其中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应的数据保持时间预先基于该磁性缓存单元对应的存内计算单元处理的待处理数据的数据量和该磁性缓存单元对应的存内计算单元的算力吞吐率得到;至少一个存内计算单元中的存内计算单元,用于从对应的磁性缓存单元提取待处理数据进行计算,并向其他磁性缓存单元输出计算后的数据。

6.在一些实施例中,定时器包括至少一个计数阈值寄存器和至少一个计数器,至少一个计数器、至少一个计数阈值寄存器、至少一个磁性缓存单元一一对应;对于至少一个计

数阈值寄存器中的计数阈值寄存器,该计数阈值寄存器用于存储预先设置的计数阈值,该计数阈值寄存器对应的计数器的计数值由初始计数值到计数阈值经过的时间为该计数阈值单元对应的磁性缓存单元的数据保持时间。

7.在一些实施例中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应于至少一个存内计算单元中的一个在先存内计算单元和一个在后存内计算单元,该磁性缓存单元用于存储在先存内输出的数据作为待处理数据,在后存内计算单元用于在对应的数据保持时间后,从该磁性缓存单元提取待处理数据并对待处理数据进行计算。

8.在一些实施例中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元用于存储在先存内计算单元输出的部分数据作为待处理数据,其中,该磁性缓存单元对应的数据保持时间基于在先存内计算单元输出的数据的数量和在先存内计算单元的算力吞吐率确定,部分数据根据在后存内计算单元进行计算所需要的数据量确定。

9.在一些实施例中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元用于存储第一存内计算单元输出的全部数据作为待处理数据,其中,该磁性缓存单元对应的数据保持时间基于在先存内计算单元输出的数据的数量和在先存内计算单元的算力吞吐率确定。

10.在一些实施例中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应于至少一个存内计算单元中的一个在先存内计算单元和预设数量个在后存内计算单元,该磁性缓存单元用于存储在先存内计算单元和预设数量个在后存内计算单元分别输出的数据作为待处理数据,其中,该磁性缓存单元对应的数据保持时间基于预设数量个在后存内计算单元分别对应的待处理数据的数量和算力吞吐率确定。

11.在一些实施例中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应的数据保持时间小于等于预先的建立的该磁性缓存单元对应的保守数据保持时间。

12.在一些实施例中,至少一个磁性缓存单元中的磁性缓存单元包括可靠区域和不可靠区域,可靠区域用于存储重要数据,不可靠数据用于存储非重要数据。

13.在一些实施例中,重要数据包括以下至少一种:多比特数据中的包括预设位数的高比特位上的数据,基于预先进行的数据重要性划分所确定的重要数据;非重要数据包括以下至少一种:多比特数据中的除预设位数的高比特位之外的低比特位上的数据,基于重要性划分所确定的非重要数据。

14.根据本公开实施例的另一个方面,提供了一种芯片,该芯片包括上述基于磁性缓存的存内计算电路。

15.根据本公开实施例的另一个方面,提供了一种计算装置,该计算装置包括上述芯片。

16.本公开上述实施例提供的基于磁性缓存的存内计算电路,通过设置至少一个磁性缓存单元、至少一个存内计算单元、定时器,利用定时器设定磁性缓存单元的数据保持时间,磁性缓存单元在对应的数据保持时间内,缓存对应的存内计算单元输出的数据作为待处理数据,存内计算单元提取待处理数据进行计算,并向其他磁性缓存单元输出计算后的数据。从而有效利用了磁性缓存单元相比静态随机存储器密度更高、容量更大的特点,提升了进行存内计算时芯片内部的数据存储量。此外,由于磁性缓存单元设定了数据保持时间,并且数据保持时间可以根据存内计算单元数据处理量来设定,因此,可以克服磁性缓存单

元写入延时长则写入功耗高的缺陷,有效利用磁性缓存单元写入延时短则写入功耗低的特点,灵活地调整各种存内计算场景下磁性缓存单元的数据保持时间,实现了较低功耗下为存内计算所需的数据提供较高容量的缓存。

17.下面通过附图和实施例,对本公开的技术方案做进一步的详细描述。

附图说明

18.通过结合附图对本公开实施例进行更详细的描述,本公开的上述以及其他目的、特征和优势将变得更加明显。附图用来提供对本公开实施例的进一步理解,并且构成说明书的一部分,与本公开实施例一起用于解释本公开,并不构成对本公开的限制。在附图中,相同的参考标号通常代表相同部件或步骤。

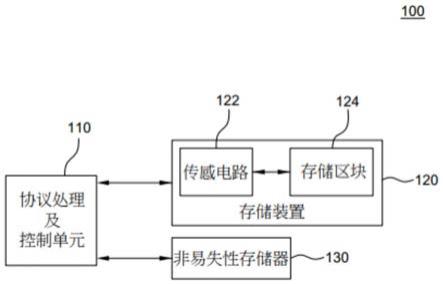

19.图1是本公开一示例性实施例提供的基于磁性缓存的存内计算电路的结构示意图。

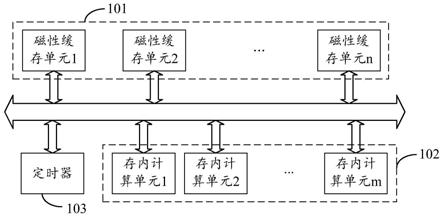

20.图2是本公开提供的基于磁性缓存的存内计算电路的定时器的结构示意图。

21.图3是本公开提供的基于磁性缓存的存内计算电路的一个数据存取过程的示意图。

22.图4是本公开提供的基于磁性缓存的存内计算电路的一个层间流水线式的数据处理方式下的存内计算单元读取的待处理数据的示意图。

23.图5是本公开提供的基于磁性缓存的存内计算电路的一个层间共享式的数据处理方式下的存内计算单元读取的待处理数据的示意图。

24.图6是本公开提供的基于磁性缓存的存内计算电路的另一个数据存取过程的示意图。

25.图7a是本公开提供的基于磁性缓存的存内计算电路的一个应用于resnet网络的示意图。

26.图7b是本公开提供的基于磁性缓存的存内计算电路的一个应用于fpn网络的示意图。

27.图8是本公开提供的基于磁性缓存的存内计算电路的向磁性缓存单元写入数据时的写入失败的分布情况的示意图。

具体实施方式

28.下面,将参考附图详细地描述根据本公开的示例实施例。显然,所描述的实施例仅仅是本公开的一部分实施例,而不是本公开的全部实施例,应理解,本公开不受这里描述的示例实施例的限制。

29.应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

30.本领域技术人员可以理解,本公开实施例中的“第一”、“第二”等术语仅用于区别不同步骤、设备或模块等,既不代表任何特定技术含义,也不表示它们之间的必然逻辑顺序。

31.还应理解,在本公开实施例中,“多个”可以指两个或两个以上,“至少一个”可以指一个、两个或两个以上。

32.还应理解,对于本公开实施例中提及的任一部件、数据或结构,在没有明确限定或者在前后文给出相反启示的情况下,一般可以理解为一个或多个。

33.另外,本公开中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本公开中字符“/”,一般表示前后关联对象是一种“或”的关系。

34.还应理解,本公开对各个实施例的描述着重强调各个实施例之间的不同之处,其相同或相似之处可以相互参考,为了简洁,不再一一赘述。

35.同时,应当明白,为了便于描述,附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。

36.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。

37.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。

38.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

39.申请概述

40.现有深度学习存内计算架构的缓存通常基于sram(静态随机存取存储器,static random

‑

access memory)器件设计。基于sram的缓存,一方面由于sram密度较低,导致容量受限,很难将全部激活的特征数据进行缓存,另一方面,由于sram的静态功耗较大,将影响存内计算架构的总体能效。

41.mram(磁性随机存储器,magnetoresistive random access memory)可以被用于构建存内计算架构中的非易失存储单元,利用其较长的保持时间来存储权重数据。现有存内计算架构中的mram,主要是利用其非易失特性来存储权重,如果用同样的设计来存储特征数据,会引入较大的性能和能耗开销,从而影响存内计算架构的整体能效。

42.现有主流的mram多采用自旋转移矩方式写入数据,其写入方式为电流通过磁隧道结(magnetic tunnel junction,mtj)改变mtj中自由层状态。通常来讲,存储器需要满足热稳定性来满足非易失存储器的要求,其存储数据保持时长可表示为:

[0043][0044]

期中δ表示热稳定性,当其大于60时,通常mram存储器数据可以保持10年以上,

[0045][0046]

其中v表示电压值,h

k

表示磁各向异性,m

s

表示饱和磁化强度,t表示温度。而对于mtj的写入关键电流来说,其与电流密度j

c0

和写入时间的关系如下公式所示:

[0047][0048]

虽然不同的mram设计,上述参数略有不用,但是都服从一个规律:写入延时长、写入功耗高,则数据保持时间长;反之,写入延时短、写入功耗低,则数据保持时间短。

[0049]

表1提供了一个不同场景的各项参数对比(注:不同的mram设计对应不同的数据)。

[0050]

表1mram不同保持时间对应的写入时间和写入能量示例(clk=1ns)

[0051] case1case2case3case4case5case6t

retention

25μs180μs1.3ms9.2ms60ms>1yeart

w

(ns)3.373.884.384.895.411.5t

w

(clk)4455612e

w

(nj)0.350.450.540.640.741.91

[0052]

根据表1给出的磁存储器件的写入延时、功耗、保持时间的关系,本公开实施例提供了支持“多保持时间”的mram缓存,即对于不同使用场景下的磁性缓存单元,设定不同的数据保持时间。

[0053]

示例性结构

[0054]

图1是本公开一示例性实施例提供的基于磁性缓存的存内计算电路的结构示意图。该电路包含的各个组成部分可以集成到一个芯片中,也可以设置到不同的芯片或电路板中,这些芯片或电路板之间建立数据通信的链路。

[0055]

如图1所示,该电路包括:至少一个磁性缓存单元101(包括磁性缓存单元1

‑

磁性缓存单元n)、至少一个存内计算单元102(包括存内计算单元1

‑

存内计算单元m)、定时器103。上述至少一个磁性缓存单元101、至少一个存内计算单元102和定时器103可以通过总线104连接。

[0056]

在本实施例中,至少一个磁性缓存单元101中的磁性缓存单元,用于在对应的数据保持时间内,缓存对应的存内计算单元输出的数据作为待处理数据。例如,当该电路应用于深度神经网络的数据运算时,至少一个磁性缓存单元101中的每个磁性缓存单元可以分别用于缓存一个卷积层的特征数据(feature map),缓存的特征数据通常为对应的存内计算单元经过计算输出的数据。磁性缓存单元可以为由上述mram构建的存储单元,通常,一个磁性缓存单元可以称为mram bank。每个磁性缓存单元中可以包括磁性存储阵列、数据读写接口等模块。

[0057]

在本实施例中,定时器103,用于对至少一个磁性缓存单元101分别设定数据保持时间。

[0058]

其中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应的数据保持时间预先基于该磁性缓存单元对应的存内计算单元处理的待处理数据的数据量和该磁性缓存单元对应的存内计算单元的算力吞吐率得到。

[0059]

作为示例,一个磁性缓存单元可以对应一个存内计算单元,磁性缓存单元存储一定量的待处理数据,待处理数据即为对应的存内计算单元输出的数据。通常,可以将这些待处理数据的数据量除以存内计算单元的算力吞吐率(即单位时间处理的数据的数量),得到的计算结果即为该存内计算单元处理数据所需的时间,同时,该时间即为磁性缓存单元保持这些待处理数据稳定存储在其内的最短时间。

[0060]

可选的,可以将上述计算结果确定为磁性缓存单元对应的数据保持时间。也可以通过查表的方法,从预先建立的包括多个设定的数据保持时间的表格(例如上述表1)中,查找与计算结果最接近的数据保持时间作为磁性缓存单元对应的数据保持时间。

[0061]

定时器103可以基于各种方式实现,例如实时时钟、晶振电路等。

[0062]

至少一个存内计算单元102中的存内计算单元,用于从对应的磁性缓存单元提取

待处理数据进行计算,并向其他磁性缓存单元输出计算后的数据。通常,一个存内计算单元可以对应至少两个磁性缓存单元,其中一个用于存储该存内计算单元所需的待处理数据,其他磁性缓存单元用于缓存存内计算单元输出的数据作为其他存内计算单元的待处理数据。或者说,一个磁性缓存单元可以对应至少两个存内计算单元,其中一个用于向磁性缓存单元输出数据作为其他存内计算单元的待处理数据。

[0063]

需要说明的是,存内计算单元可以是现有的任意架构的存内计算单元,关于存内计算单元的实现方式,本公开实施例不再赘述。在本实施例中,至少一个存内计算单元102包括的存内计算单元的数量与至少一个磁性缓存单元101包括的磁性缓存单元的数量可以相等,也可以不等,即图1中的磁性缓存单元的数量n与存内计算单元的数量m可以相同,也可以不同。

[0064]

本公开的上述实施例提供的电路,通过设置至少一个磁性缓存单元、至少一个存内计算单元、定时器,利用定时器设定磁性缓存单元的数据保持时间,磁性缓存单元在对应的数据保持时间内,缓存对应的存内计算单元输出的数据作为待处理数据,存内计算单元提取待处理数据进行计算,并向其他磁性缓存单元输出计算后的数据。从而有效利用了磁性缓存单元相比静态随机存储器密度更高、容量更大的特点,提升了进行存内计算时芯片内部的数据存储量。此外,由于磁性缓存单元设定了数据保持时间,并且数据保持时间可以根据存内计算单元数据处理量来设定,因此,可以克服磁性缓存单元写入延时长则写入功耗高的缺陷,有效利用磁性缓存单元写入延时短则写入功耗低的特点,灵活地调整各种存内计算场景下磁性缓存单元的数据保持时间,实现了较低功耗下为存内计算所需的数据提供较高容量的缓存。

[0065]

在一些可选的实现方式中,如图2所示,定时器103包括至少一个计数阈值寄存器1031和至少一个计数器1032,至少一个计数器1032、至少一个计数阈值寄存器1031、至少一个磁性缓存单元103一一对应。如图2所示,计数器1、计数阈值寄存器1、磁性缓存单元1相对应;计数器2、计数阈值寄存器2、磁性缓存单元2相对应;

……

;计数器n、计数阈值寄存器n、磁性缓存单元n相对应。

[0066]

对于至少一个计数阈值寄存器1031中的计数阈值寄存器,该计数阈值寄存器用于存储预先设置的计数阈值,该计数阈值寄存器对应的计数器的计数值由初始计数值到计数阈值经过的时间为该计数阈值单元对应的磁性缓存单元的数据保持时间。

[0067]

作为示例,某个计数阈值寄存器存储的计数阈值为4,对应的计数器的计数周期为1ns,初始计数值为0,则计数值从0到4计数,经过4个计数周期(即4ns),计数值清零,即该计数阈值寄存器和该计数器对应的磁性缓存单元的数据保持时间为4ns。

[0068]

需要说明的是,本技术实施例中描述的电路单元仅仅是示意性的,并不限定具体的结构。该电路包括的各个单元可以任意组合。例如,上述计数阈值寄存器可以设置在与各个磁性缓存单元和各个存计算单元分离的电路区域中,上述各个计数器可以分别与对应的磁性缓存单元设置在同一电路区域中。

[0069]

本实现方式通过计数器和计数阈值寄存器实现的定时器,在对应的存内计算单元进行数据处理时,无需精确地对数据保持时间进行计时,只需设置计数阈值即可,从而降低了对数据保持时间进行计时的难度,有助于提高存内计算的效率。

[0070]

在一些可选的实现方式中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁

性缓存单元对应于至少一个存内计算单元中的一个在先存内计算单元和一个在后存内计算单元,该磁性缓存单元用于存储在先存内输出的数据作为待处理数据,在后存内计算单元用于在对应的数据保持时间后,从该磁性缓存单元提取待处理数据并对待处理数据进行计算。

[0071]

如图3所示,第i个存内计算单元pe

i

、第i 1个存内计算单元pe

i 1

和第i个磁性缓存单元bank

i

通过总线连接。其中,pe

i

即为bank

i

的在先存内计算单元,pe

i 1

即为bank

i

的在后存内计算单元。pe

i

输出的数据作为待处理数据存储到bank

i

中,pe

i 1

在对应的数据保持时间后,从bank

i

中提取一定量的待处理数据进行计算。可选的,bank

i

中存储的待处理数据可以是pe

i

输出的全量数据,也可以是pe

i

输出的部分数据。

[0072]

本实现方式将两个相邻的存内计算单元之间设置一个磁性缓存单元作为该两个存内计算单元之间的数据缓存,可以将该实现方式应用到深度神经网络中的层间数据交换过程中。例如pe

i

处理网络的第i层,pe

i 1

处理网络的第i 1层,bank

i

缓存的待处理数据为第i 1层处理的特征数据,从而有助于利用该电路缓存数据量较大且功耗较小的特点,提高深度神经网络的性能。

[0073]

在一些可选的实现方式中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元用于存储在先存内计算单元输出的部分数据作为待处理数据,其中,该磁性缓存单元对应的数据保持时间基于在先存内计算单元输出的数据的数量和在先存内计算单元的算力吞吐率确定,部分数据根据在后存内计算单元进行计算所需要的数据量确定。在本实现方式中,当某个磁性缓存单元内存储的待处理数据达到一定量后,对应的在后存内计算单元即可从该磁性缓存单元中提取数据进行计算,即实现了流水线式的数据处理。

[0074]

作为示例,如图4所示,h

i 1

为深度神经网络的第i 1层计算的feature map的高度,k

i 1

为第i 1层的卷积核(高度与宽度相等)的尺寸,ch

i 1

表示第i 1层计算的feature map的通道数量。当上述bank

i

内缓存的待处理数据达到时(如图4中的feature map中填充的数据的数量),上述pe

i 1

即可开始进行数据计算,当本次计算完毕时,卷积核移动,第i层输出新的待处理数据并缓存至上述bank

i

,从而实现了深度神经网络的层间流水线式的数据处理。

[0075]

在该种实现方式下,bank

i

的数据保持时间t

retention

可以表示为:

[0076][0077]

其中,throughput

i

为上述pe

i

的算力吞吐率。通常,对于大部分深度神经网络,使用该实现方式时,t

retention

<25μs,因此通常选择表1中的case1,即第i个计数阈值寄存器的计数阈值设为4。

[0078]

本实现方式提供的流水线式的数据处理方式,相比于由磁性缓存单元缓存在先存内计算单元输出的全量数据,可以在缓存部分待处理数据后即可由在后存内计算单元进行数据处理,从而降低了对磁性缓存单元的体积的要求,有助于降低电路的成本和实现难度。此外,由于存内计算单元处理数据的数量减少,因此,可以相应地降低对应的磁性缓存单元的数据保持时间,有助于进一步降低磁性缓存单元的功耗。

[0079]

在一些可选的实现方式中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元用于存储第一存内计算单元输出的全部数据作为待处理数据。其中,该磁性缓

存单元对应的数据保持时间基于在先存内计算单元输出的数据的数量和在先存内计算单元的算力吞吐率确定。

[0080]

作为示例,如图5所示,h

i 1

和w

i 1

分别为深度神经网络的第i 1层计算的feature map的高度和宽度,ch

i 1

表示第i 1层计算的feature map的通道数量。上述bank

i

内缓存的待处理数据为(如图5中的feature map中的全部数据的数量),上述pe

i 1

提取第i层输出的全量数据进行计算,从而实现了深度神经网络的层间共享(非流水)方式的数据处理。

[0081]

在该种实现方式下,bank

i

的数据保持时间t

retention

可以表示为:

[0082][0083]

其中,throughput

i

为上述pe

i

的算力吞吐率。通常,对于大部分深度神经网络,使用该实现方式时,通常选择表1中的case1或case2,即第i个计数阈值寄存器的计数阈值设为4。

[0084]

本实现方式通过磁性缓存单元缓存对应的在先存内计算单元输出的全量数据,进一步丰富了存内计算过程中的数据缓存方式,扩大了该电路适用的应用场景的范围,相比于上述流水式的数据处理方式,其提取缓存的待处理数据时发生的时序错误的概率较小,从而有助于提高存内计算电路的计算准确性。

[0085]

在一些可选的实现方式中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应于至少一个存内计算单元中的一个在先存内计算单元和预设数量个在后存内计算单元,该磁性缓存单元用于存储在先存内计算单元和预设数量个在后存内计算单元分别输出的数据作为待处理数据,其中,该磁性缓存单元对应的数据保持时间基于预设数量个在后存内计算单元分别对应的待处理数据的数量和算力吞吐率确定。

[0086]

其中,上述预设数量个在后存内计算单元分别对应的待处理数据,即每个在后存内计算单元相邻的前一个存内计算单元输出的数据。上述目标存内计算单元通常为上述预设数量个在后存内计算单元中的最后一个。

[0087]

如图6所示,第i个存内计算单元pe

i

、第i 1个存内计算单元pe

i 1

、

……

、第i l个存内计算单元pe

i l

和第i个磁性缓存单元bank

i

通过总线连接。其中,pe

i

即为bank

i

的在先存内计算单元,pe

i 1

、

……

、pe

i l

即为bank

i

的在后存内计算单元。pe

i

、pe

i 1

、

……

、pe

i l

输出的数据均为待处理数据,其中,pe

i l

由于需要对pe

i

输出的待处理数据进行计算,因此,pe

i

输出的待处理数据需要保留到pe

i l

输出对应的待处理数据时,即在pe

i l

输出待处理数据后,pe

i

输出的待处理数据被其他计算模块从bank

i

中提取并处理。可选的,在本实现方式中,bank

i

中存储的待处理数据可以是各存内计算单元输出的全量数据(如上述图5对应实施例描述的方案),也可以是各存内计算单元输出的部分数据(如上述图4对应实施例描述的方案)。

[0088]

在该种实现方式下,bank

i

的数据保持时间t

retention

可以表示为:

[0089][0090]

其中,throughput

j

为对应的pe

j

的算力吞吐率。在得到t

retention

后,可以基于表一查找对应的数据保持时间。

[0091]

作为示例,如图7a所示,对于resnet网络,对于某个卷积层输出的feature map可以跨两层使用,即图7a中第i层输出的feature map会在第i 2层处理完数据后再次被使用,该应用场景下,磁性缓存单元的数据保持时间通常选择表1中case2或者case3。如图7b所示,对于检测任务常用的特征图金字塔网络(fpn,feature pyramid networks),对于某个卷积层输出的feature map会跨多层使用,即图7b中第i层输出的feature map会在第i 4层处理完数据后再次被第i 5层使用,该应用场景下,磁性缓存单元的数据保持时间通常选择表1中case5甚至case6以达到足够的保持时间。

[0092]

本实现方式通过将磁性缓存单元缓存的在先存内计算单元输出的数据保存至多个在后存内计算单元处理数据结束,从而可以将该电路应用到诸如resnet、fpn等类型的神经网络中,进一步丰富了存内计算过程中的数据缓存方式,扩大了该电路适用的应用场景的范围。

[0093]

在一些可选的实现方式中,对于至少一个磁性缓存单元中的磁性缓存单元,该磁性缓存单元对应的数据保持时间小于等于预先的建立的该磁性缓存单元对应的保守数据保持时间。

[0094]

其中,保守数据保持时间为根据不同的数据量所确定的、写入数据时的最小保持时间。作为示例,上述表一中的第二行(t

w

)对应的时间为保守数据保持时间。当数据写入的持续时间达到保守数据保持时间时,可以保证磁性缓存达到预期的较高可靠性。通常,在基于存内计算单元处理的待处理数据的数据量和算力吞吐率得到磁性缓存单元的数据保持时间后,可以将数据保持时间适当缩短,缩短的时间可以任意设置。

[0095]

通常,在设置实际的数据保持时间时,可以根据向磁性缓存单元内写入数据时的写入失败的分布情况确定。例如,写入失败与数据保持时间的对应关系如图8所示,其中的分布曲线由下式得到:

[0096][0097]

其中,p

usw

表示没有翻转(即写入失败)的概率密度,τ表示电流加载时间,δ表示磁性缓存单元的结构热力学稳定参数,i

c

表示关键电流值。如图8所示,,当确定磁性缓存单元符合表一中的case3时,保守数据保持时间为4.38ns,则可以将实际的数据保持时间设为4ns,从而预计有5%左右的数据不能达到足够的保持时间。

[0098]

本实现方式通过将磁性缓存单元的实际数据保持时间设定为小于保守数据保持时间,可以在使磁性缓存单元写入错误的概率达到容忍的范围内的情况下,降低磁性缓存单元的功耗并提升数据写入速度。

[0099]

在一些可选的实现方式中,至少一个磁性缓存单元中的磁性缓存单元包括可靠区域和不可靠区域,可靠区域用于存储重要数据,不可靠数据用于存储非重要数据。

[0100]

其中,磁性缓存单元的可靠区域和不可靠区域可以是通过现有的存储设备老化测试方法划定的。例如,对磁性缓存单元内的每个存储比特位的子单元按照目标写入时间进行数据写操作,这个操作可以重复数次,然后再读出数据,根据读出结果判断写入成功的子单元,然后划分可靠区域和不可靠区域。

[0101]

上述重要数据和非重要数据可以通过各种方式设定。具体请参考下述可选实现方式。

[0102]

本实现方式通过在磁性缓存单元中设置可靠区域和不可靠区域,并将重要数据存储到可靠区域,将非重要数据存储到不可靠区域,从而实现了在由于缩短数据保持时间导致磁性缓存单元的写入错误率提高的情况下,尽可能地降低重要数据发生写入错误的概率,在降低磁性缓存单元的功耗的基础上,提高数据缓存的可靠性。

[0103]

在一些可选的实现方式中,重要数据包括以下至少一种:多比特数据中的包括预设位数的高比特位上的数据,基于预先进行的数据重要性划分所确定的重要数据;非重要数据包括以下至少一种:多比特数据中的除预设位数的高比特位之外的低比特位上的数据,基于重要性划分所确定的非重要数据。

[0104]

具体地,上述预设位数可以根据不可靠区域占磁性缓存单元的总容量的比例确定。例如,如果不可靠区域占总容量比例<25%,对于8

‑

bit的数据,将高6

‑

bit存储到可靠区域,将低2

‑

bit存储到不可靠区域。从而使可靠区域存储高比特位,降低数据发生错误而变化的幅度。

[0105]

上述数据重要性划分方法可以采用现有方法。例如,当该电路应用到深度神经网络领域时,可以采用现有的关于算法可解释性的分析方法,确定神经网络中的每个通道包含的数据的重要性。

[0106]

本实现方式提供的重要数据和非重要数据的划分方案,可以实现使待存入磁性缓存单元中的数据有针对性地存入磁性缓存单元中的不同区域,进而有助于降低该电路进行存内计算时发生计算错误的概率。

[0107]

本公开的实施例还提供了一种芯片,芯片上集成了基于磁性缓存的存内计算电路,基于磁性缓存的存内计算电路的技术细节如图1

‑

图8和相关描述所示,此处不再展开描述。

[0108]

本公开的实施例还提供了一种计算装置,该计算装置包括上述实施例描述的芯片。此外,该计算装置还可以包括输入装置、输出装置以及必要的存储器等。其中,输入装置可以包括诸如鼠标、键盘、触控屏、通信网络连接器等,用于输入原始数组。输出装置可以包括诸如显示器、打印机、以及通信网络及其所连接的远程输出设备等等,用于输出上述实施例描述的第二预设表示方式的数据。存储器用于存储上述输入装置输入的数据,以及基于磁性缓存的存内计算电路运行过程中产生的数据。存储器可以包括易失性存储器和/或非易失性存储器。易失性存储器例如可以包括随机存取存储器(ram)和/或高速缓冲存储器(cache)等。非易失性存储器例如可以包括只读存储器(rom)、硬盘、闪存等。

[0109]

以上结合具体实施例描述了本公开的基本原理,但是,需要指出的是,在本公开中提及的优点、优势、效果等仅是示例而非限制,不能认为这些优点、优势、效果等是本公开的各个实施例必须具备的。另外,上述公开的具体细节仅是为了示例的作用和便于理解的作用,而非限制,上述细节并不限制本公开为必须采用上述具体的细节来实现。

[0110]

本说明书中各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似的部分相互参见即可。

[0111]

本公开中涉及的器件、装置、设备、系统的方框图仅作为例示性的例子并且不意图要求或暗示必须按照方框图示出的方式进行连接、布置、配置。如本领域技术人员将认识到的,可以按任意方式连接、布置、配置这些器件、装置、设备、系统。诸如“包括”、“包含”、“具有”等等的词语是开放性词汇,指“包括但不限于”,且可与其互换使用。这里所使用的词汇

“

或”和“和”指词汇“和/或”,且可与其互换使用,除非上下文明确指示不是如此。这里所使用的词汇“诸如”指词组“诸如但不限于”,且可与其互换使用。

[0112]

可能以许多方式来实现本公开的电路。例如,可通过软件、硬件、固件或者软件、硬件、固件的任何组合来实现本公开的电路。用于电路中的方法的步骤的上述顺序仅是为了进行说明,本公开的方法的步骤不限于以上具体描述的顺序,除非以其它方式特别说明。此外,在一些实施例中,还可将本公开实施为记录在记录介质中的程序,这些程序包括用于实现根据本公开的电路的功能的机器可读指令。因而,本公开还覆盖存储用于执行根据本公开的电路的功能的程序的记录介质。

[0113]

还需要指出的是,在本公开的电路中,各部件或各步骤是可以分解和/或重新组合的。这些分解和/或重新组合应视为本公开的等效方案。

[0114]

提供所公开的方面的以上描述以使本领域的任何技术人员能够做出或者使用本公开。对这些方面的各种修改对于本领域技术人员而言是非常显而易见的,并且在此定义的一般原理可以应用于其他方面而不脱离本公开的范围。因此,本公开不意图被限制到在此示出的方面,而是按照与在此公开的原理和新颖的特征一致的最宽范围。

[0115]

为了例示和描述的目的已经给出了以上描述。此外,此描述不意图将本公开的实施例限制到在此公开的形式。尽管以上已经讨论了多个示例方面和实施例,但是本领域技术人员将认识到其某些变型、修改、改变、添加和子组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。