存储器模块和堆叠的存储器装置

1.相关申请的交叉引用

2.本技术要求于2020年4月20日在韩国知识产权局提交的韩国专利申请no.10

‑

2020

‑

0047233的优先权,该申请的公开以引用方式全文并入本文中。

技术领域

3.示例性实施例涉及存储器装置,并且更具体地说,涉及存储器模块和堆叠的存储器装置。

背景技术:

4.在存储器装置中,动态随机存取存储器(dram)装置可通过将电荷存储至存储器单元的电容器来存储数据。由于电容器中的电荷随时间泄漏,dram装置可刷新存储器单元。存储器控制器可随机地访问dram装置的地址,并且具体地说,可频繁地或密集地访问特定地址。因为作为一种易失性存储器装置的动态随机存取存储器(dram)具有高访问速度,所以dram被广泛用作计算系统的工作存储器、缓冲器存储器、主存储器等。对于高容量,多个dram可按照存储器模块的形式设置。

技术实现要素:

5.一方面是提供一种能够分散由被密集地访问的地址导致的干扰的存储器模块。

6.另一方面是提供一种能够分散由被密集地访问的地址导致的干扰的堆叠的存储器装置。

7.根据示例性实施例的一方面,提供了一种存储器模块,该存储器模块包括安装在电路板上的多个半导体存储器装置和安装在电路板上的控制装置。多个半导体存储器装置中的每一个半导体存储器装置包括存储数据的存储器单元阵列。控制装置从外部装置接收命令和访问地址,并且将命令和访问地址提供至多个半导体存储器装置。多个半导体存储器装置中的每一个半导体存储器装置响应于通电信号或复位信号执行地址交换操作,以随机地交换访问地址的一部分比特,以产生交换后的地址,并且基于相同的访问地址启用半导体存储器装置的存储器单元阵列中的多条字线中的对应的目标字线,使得多个半导体存储器装置中的至少两个半导体存储器装置启用不同的目标字线。

8.根据示例性实施例的另一方面,提供了一种存储器模块,该存储器模块包括安装在电路板上的多个半导体存储器装置和安装在电路板上的控制装置。多个半导体存储器装置中的每一个半导体存储器装置包括存储数据的存储器单元阵列。控制装置从外部装置接收命令和访问地址,响应于通电信号或复位信号执行地址交换操作,以随机地交换访问地址的一部分比特,以产生交换后的地址,并且将命令和交换后的地址提供至多个半导体存储器装置。多个半导体存储器装置基于相同的访问地址启用存储器单元阵列中的多条字线中的对应的目标字线,使得多个半导体存储器装置中的至少两个半导体存储器装置启用不同的目标字线。

9.根据示例性实施例的另一方面,提供了一种堆叠的存储器装置,该堆叠的存储器装置包括缓冲器裸片、堆叠在缓冲器裸片上的多个存储器裸片和延伸穿过多个存储器裸片以连接至缓冲器裸片的多个硅穿通件(tsv)。缓冲器裸片从外部装置接收命令和访问地址。多个存储器裸片包括存储数据的存储器单元阵列。多个存储器裸片中的每一个存储器裸片通过tsv接收访问地址,响应于通电信号或复位信号执行地址交换操作,以随机地交换访问地址的一部分比特,以产生交换后的地址,并且基于相同的访问地址启用存储器单元阵列中的多条字线中的对应的目标字线,使得多个存储器裸片中的至少两个存储器裸片启用不同的目标字线。

附图说明

10.参照附图详细描述示例性实施例,将更加清楚地理解以上和其它方面,其中:

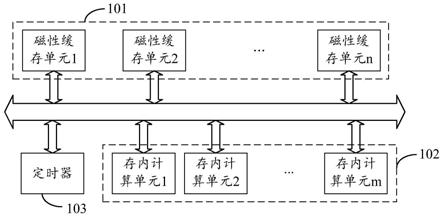

11.图1是示出根据各种示例性实施例的存储器系统的框图;

12.图2是根据示例性实施例的详细示出图1的存储器系统的存储器模块的框图;

13.图3是示出根据各种示例性实施例的图2的存储器模块中的半导体存储器装置之一的框图;

14.图4示出根据各种示例性实施例的图3的半导体存储器装置的第一存储体阵列;

15.图5是示出根据示例性实施例的图3的半导体存储器装置中的地址交换电路的框图;

16.图6是示出根据示例性实施例的图5的地址交换电路的示例的框图;

17.图7是根据示例性实施例的图6的地址交换电路中的物理不可克隆函数(puf)的示例;

18.图8是示出根据示例性实施例的图5的地址交换电路的地址交换器的电路图;

19.图9是示出根据示例性实施例的图5的地址交换电路的另一示例的框图;

20.图10示出根据示例性实施例的图2的存储器模块的地址交换操作的示例;

21.图11是根据示例性实施例的详细示出图1的存储器系统的存储器模块的另一示例的框图;

22.图12是示出根据示例性实施例的图11的存储器模块中的控制装置的示例的框图;

23.图13是示出根据示例性实施例的图12的控制装置中的地址交换电路块(asb)的示例的框图;

24.图14是示出根据示例性实施例的图13的asb的地址交换电路之一的框图;

25.图15是示出根据各种示例性实施例的图11的存储器模块中的半导体存储器装置之一的框图;

26.图16示出根据示例性实施例的图11的存储器模块的地址交换操作的示例;

27.图17a是示出根据示例性实施例的图1的存储器系统的存储器模块的另一示例的框图;

28.图17b是示出根据示例性实施例的图1的存储器系统的存储器模块的另一示例的框图;

29.图18是示出根据示例性实施例的堆叠的存储器装置的示例的框图;

30.图19示出根据示例性实施例的图18的堆叠的存储器装置的示例;

31.图20是示出根据示例性实施例的堆叠的存储器装置的另一示例的框图;

32.图21是示出根据示例性实施例的操作存储器模块的方法的流程图;

33.图22是示出根据示例性实施例的包括堆叠的存储器装置的半导体封装件的示图;

34.图23是示出根据示例性实施例的具有四列存储器模块的存储器系统的框图;以及

35.图24是示出根据示例性实施例的包括存储器模块的移动系统的框图。

具体实施方式

36.示例性实施例提供了一种能够对称地发送地址信号的存储器模块。

37.示例性实施例还提供了一种对能够对称地发送地址信号的存储器模块进行操作的方法。

38.根据各种示例性实施例,存储器模块包括多个半导体存储器装置和控制装置。半导体存储器装置或控制装置可基于访问地址中的行地址产生交换后的行地址。半导体存储器装置中的每一个半导体存储器装置中的行解码器响应于交换后的行地址启用不同的目标字线,使得半导体存储器装置中的至少两个半导体存储器装置相对于访问地址启用不同的目标字线。因此,半导体存储器装置可使受被密集地访问的地址干扰的受害字线分散,并且因此减小由于非法侵入导致故障的可能性。

39.下文中,将参照附图更完全地描述各种示例性实施例。在本技术中,相同的标号可指相同的元件。

40.图1是示出根据各种示例性实施例的存储器系统的框图。

41.参照图1,存储器系统10包括主机20和存储器模块100。主机20可包括存储器控制器25。

42.存储器模块100可包括控制装置500、多个半导体存储器装置(dram)200、串行存在检测(spd)芯片180、功率管理集成电路(pmic)185。在一些示例性实施例中,控制装置500可为注册时钟驱动程序(rcd)。

43.控制装置500可在存储器控制器25的控制下控制半导体存储器装置200和pmic 185。例如,控制装置500可从存储器控制器25接收地址addr、命令cmd、复位信号rst和时钟信号ck。响应于接收到的信号,控制装置500可通过第一控制信号ctl1控制半导体存储器装置200,并且可通过第二控制信号ctl2控制pmic 185。

44.响应于接收到的信号,控制装置500可控制半导体存储器装置200,使得通过数据信号dq和数据选通信号dqs接收到的数据被写入在半导体存储器装置200中,或者使得存储在半导体存储器装置200中的数据通过数据信号dq和数据选通信号dqs被输出。

45.例如,控制装置500可将地址addr、命令cmd、复位信号rst和时钟信号ck作为第一控制信号ctl1从存储器控制器25发送至半导体存储器装置200。

46.半导体存储器装置200可在控制装置500的控制下存储通过数据信号dq和数据选通信号dqs接收到的数据。可替换地,半导体存储器装置200可在控制装置500的控制下输出通过数据信号dq和数据选通信号dqs写入的数据。

47.例如,半导体存储器装置200可包括诸如动态随机存取存储器(dram)、静态ram(sram)或者同步dram(sdram)的易失性存储器装置。例如,半导体存储器装置200可为基于dram的易失性存储器装置。

48.spd芯片180可为可编程只读存储器(例如,eeprom)。spd芯片180可包括存储器模块100的初始信息或装置信息di。在各种示例性实施例中,spd芯片180可包括存储器模块100的诸如模型形式、模型配置、存储容量、模型类型、执行环境等的初始信息或装置信息di。

49.当包括存储器模块100的存储器系统10启动时,主机20可从spd芯片180中读取装置信息di,并且可基于装置信息di识别存储器模块100。主机20可基于来自spd芯片180的装置信息di控制存储器模块100。例如,主机20可基于来自spd芯片180的装置信息di识别存储器模块100中包括的半导体存储器装置200的类型。

50.在各种示例性实施例中,spd芯片180可通过串行总线与主机20通信。例如,主机20可通过串行总线与spd芯片180交换信号。spd芯片180还可通过串行总线与控制装置500通信。串行总线可包括诸如内集成电路(i2c)的2线(2

‑

line)串行总线、系统管理总线(smbus)、功率管理总线(pmbus)、智能平台管理界面(ipmi)、管理组件传输协议(mctp)等中的至少一个。

51.pmic 185接收输入电压vin,基于输入电压vin产生电源电压vdd,并且将电源电压vdd提供至半导体存储器装置200和/或控制装置500。半导体存储器装置200基于电源电压vdd操作。

52.图2是示出根据示例性实施例的图1的存储器系统的存储器模块的示例的框图。

53.参照图2,存储器模块100a包括设置(或者安装)在电路板101中的控制装置500a、多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e、多个数据缓冲器(db)141至145和151至155、模块电阻单元(mru)160和170、spd芯片180和pmic 185。

54.这里,电路板101(其为印刷电路板)可在第一边缘部分103与第二边缘部分105之间在垂直于第一方向d1的第二方向d2上延伸。第一边缘部分103和第二边缘部分105可在第一方向d1上延伸。

55.在一些示例性实施例中,控制装置500a可设置在电路板101的中心。多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e可在控制装置500a与第一边缘部分103之间按照多行排列并在控制装置500与第二边缘部分105之间按照多行排列。

56.在这种情况下,半导体存储器装置201a至201e和202a至202e可在控制装置500a与第一边缘部分103之间沿着多行排列。半导体存储器装置203a至203e和204a至204e可在控制装置500a与第二边缘部分105之间沿着多行排列。半导体存储器装置201a至201e和202a至202e的一部分可为错误校正码(ecc)存储器装置。ecc存储器装置可执行ecc编码操作,以产生关于将被写入在多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e的存储器单元的数据的奇偶校验位,并且执行ecc解码操作,以校正从存储器单元读取的数据中发生的错误。

57.多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置可通过用于接收/发送数据信号dq和数据选通信号dqs的数据传输线耦接至数据缓冲器(db)141至145和151至155中的对应的一个数据缓冲器。

58.控制装置500a可通过命令/地址传输线161将命令/地址信号(例如,ca)提供至半导体存储器装置201a至201e,并且可通过命令/地址传输线163将命令/地址信号提供至半导体存储器装置202a至202e。另外,控制装置500a可通过命令/地址传输线171将命令/地址

信号提供至半导体存储器装置203a至203e,并且可通过命令/地址传输线173将命令/地址信号提供至半导体存储器装置204a至204e。

59.命令/地址传输线161和命令/地址传输线163可共同连接至设置为邻近于第一边缘部分103的模块电阻单元(mru)160,并且命令/地址传输线171和命令/地址传输线173可共同连接至设置为邻近于第二边缘部分105的模块电阻单元(mru)170。模块电阻单元(mru)160和模块电阻单元(mru)170中的每一个模块电阻单元可包括连接至终端电压vtt的端接电阻器rtt/2。在这种情况下,模块电阻单元(mru)160和模块电阻单元(mru)170的排列可减少模块电阻单元的数量,并且因此减少设置端接电阻器的面积。

60.另外,所述多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置可为ddr5sdram。

61.spd芯片180可设置为邻近于控制装置500a,并且pmic 185可设置在半导体存储器装置203e与第二边缘部分105之间。pmic 185可基于输入电压vin产生电源电压vdd,并且可将电源电压vdd提供至半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e。

62.虽然图2示出pmic 185被设置为邻近于第二边缘部分105,但是示例性实施例不限于此,并且在一些示例性实施例中,pmic 185可设置在电路板101的中心部分,以邻近于控制装置500a。

63.半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置可包括地址交换电路,所述地址交换电路响应于通电信号或复位信号执行地址交换操作以随机地交换访问地址addr的一部分比特,以产生交换后的地址,并且基于相同的访问地址启用存储器单元阵列中的多条字线中的对应的目标字线,使得半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的至少两个半导体存储器装置启用不同的目标字线。

64.半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置通过半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的地址交换电路响应于通电信号和/或复位信号执行地址交换操作,以输出具有不同逻辑电平的随机选择信号,并且交换访问地址addr的一部分比特。

65.因此,当访问地址addr被密集地访问时,也就是说,当访问地址addr相对于参考访问次数更频繁地被访问时,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e可分散(即,区分)受访问地址addr干扰的受害字线。

66.这里,通电信号可为通过逻辑高电平启用的信号,并且当从主机20将功率施加至存储器模块100a时,在初始化操作中的通电序列期间,可响应于提供至所述多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个的电源电压vdd等于或大于参考电压被启用。复位信号可为在存储器模块100a的正常操作期间存储器控制器25施加至存储器模块100a的信号。存储器模块100a可响应于通过逻辑低电平启用的复位信号复位。

67.图3是示出根据各种示例性实施例的图2的存储器模块中的半导体存储器装置之一的框图。

68.参照图3,半导体存储器装置201a可包括控制逻辑电路210、地址寄存器220、存储体控制逻辑230、行地址多路复用器(ra mux)240、列地址(ca)锁存器250、行解码器260、列解码器270、存储器单元阵列300、读出放大器285、输入/输出门控电路(i/o门控电路)290、数据输入/输出(i/o)缓冲器295、通电信号产生器(pusg)225、刷新计数器245和ecc引擎297。

69.存储器单元阵列300可包括第一存储体阵列310至第八存储体阵列380。存储器单元阵列300可基于电源电压vdd操作。

70.行解码器260可包括分别耦接至第一存储体阵列310至第八存储体阵列380的第一行解码器260a至第八行解码器260h,列解码器270可包括分别耦接至第一存储体阵列310至第八存储体阵列380的第一列解码器270a至第八列解码器270h,并且读出放大器285可包括分别耦接至第一存储体阵列310至第八存储体阵列380的第一读出放大器285a至第八读出放大器285h。

71.第一存储体阵列310至第八存储体阵列380、第一行解码器260a至第八行解码器260h、第一列解码器270a至第八列解码器270h和第一读出放大器285a至第八读出放大器285h可形成第一存储体至第八存储体。第一存储体阵列310至第八存储体阵列380中的每一个存储体阵列可包括多条字线wl、多条位线btl和形成在字线wl与位线btl的交叉点处的多个存储器单元mc。

72.虽然半导体存储器装置201a在图3中示为包括八个存储体,但是半导体存储器装置201a可包括任何数量的存储体。

73.地址寄存器220可从控制装置500接收包括存储体地址bank_addr、行地址row_addr和列地址col_addr的地址addr。地址寄存器220可将接收到的存储体地址bank_addr提供至存储体控制逻辑230,可将接收到的行地址row_addr提供至行地址多路复用器240,并且可将接收到的列地址col_addr提供至列地址锁存器250。

74.地址寄存器220可包括地址交换电路(asc)400。

75.地址交换电路400可响应于通电信号pup或复位信号rst随机地交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addr。

76.存储体控制逻辑230可响应于存储体地址bank_addr产生存储体控制信号。第一行解码器260a至第八行解码器260h中的对应于存储体地址bank_addr的一个行解码器可响应于存储体控制信号被激活,并且第一列解码器270a至第八列解码器270h中的对应于存储体地址bank_addr的一个列解码器可响应于存储体控制信号被激活。

77.行地址多路复用器240可从地址寄存器220接收交换后的行地址s_row_addr,并且可从刷新计数器245接收刷新行地址ref_addr。行地址多路复用器240可选择性地输出交换后的行地址s_row_addr或者刷新行地址ref_addr,作为行地址ra。从行地址多路复用器240输出的行地址ra可应用于第一存储体行解码器260a至第八存储体行解码器260h。

78.第一行解码器260a至第八行解码器260h中被激活的一个可解码从行地址多路复用器240输出的行地址ra,并且可激活对应于行地址ra的字线wl。例如,被激活的存储体行解码器可基于电源电压vdd产生字线驱动电压,并且可将字线驱动电压应用于对应于行地址ra的字线wl。

79.列地址锁存器250可从地址寄存器220接收列地址col_addr,并且可临时存储接收

到的列地址col_addr。在各种示例性实施例中,在触发(burst)模式下,列地址锁存器250可产生相对于接收到的列地址col_addr增加的列地址。列地址锁存器250可将临时地存储的或者产生的列地址应用于第一存储体列解码器270a至第八存储体列解码器270h。

80.第一列解码器270a至第八列解码器270h中被激活的一个列解码器可解码从列地址锁存器250输出的列地址col_addr,并且可控制i/o门控电路290,以输出对应于列地址col_addr的数据。

81.i/o门控电路290可包括用于对输入/输出数据进行门控(gating)的电路。i/o门控电路290还可包括用于存储从第一存储体阵列310至第八存储体阵列380输出的数据的读取数据锁存器和用于将数据写入第一存储体阵列310至第八存储体阵列380的写入控制装置。

82.将从第一存储体阵列310至第八存储体阵列380之一被读取的数据可被读出放大器读出,并且可被存储在读取数据锁存器中,所述读出放大器耦接至数据将从中被读取的一个存储体阵列。

83.在ecc引擎297对数据(例如,码字cw)执行ecc解码之后,可经由数据i/o缓冲器295将存储在读取数据锁存器中的数据提供至存储器控制器25。将被写入第一存储体阵列310至第八存储体阵列380之一中的数据可从存储器控制器25被提供至数据i/o缓冲器295。ecc引擎297可对提供至数据i/o缓冲器295的数据执行ecc编码,并且ecc引擎297可将编码的数据(例如,码字cw)提供至i/o门控电路290。

84.在写入操作中,数据i/o缓冲器295将数据信号dq提供至ecc引擎297。在读取操作中,数据i/o缓冲器295从ecc引擎297接收数据信号dq,并且将数据信号dq和数据选通信号dqs提供至存储器控制器25。

85.通电信号产生器(pusg)225响应于来自pmic 185的电源电压vdd等于或大于参考电压产生通电信号pup。通电信号产生器225将通电信号pup提供至地址交换电路400。

86.通电信号产生器225可包括比较器。比较器将电源电压vdd与参考电压的电平进行比较,并且为地址交换电路400提供响应于电源电压vdd等于或大于参考电压而启用的通电信号pup。

87.当存储器模块100a启动,并且pmic 185从存储器控制器25接收输入电压vin时,pmic 185基于输入电压vin产生包括电源电压vdd的各种电压。半导体存储器装置201a基于电源电压vdd操作,并且当电源电压vdd等于或大于特定电压电平时正常操作。

88.通电信号产生器225可设置特定电压电平作为参考电压,并且为地址交换电路400提供响应于电源电压vdd等于或大于参考电压启用的通电信号pup,其中,半导体存储器装置201a在所述特定电压电平下正常操作。响应于接收通电信号pup,地址交换电路400将访问地址addr转换为交换后的地址,并且将交换后的地址提供至行解码器260。

89.控制逻辑电路210可控制半导体存储器装置201a的操作。例如,控制逻辑电路210可产生用于使存储器装置201a执行写入操作或者读取操作的控制信号。控制逻辑电路210可包括命令解码器211和模式寄存器212,其中,命令解码器211对通过控制装置500a从存储器控制器25接收的命令cmd进行解码,模式寄存器212设置半导体存储器装置201a的操作模式。

90.例如,命令解码器211可通过对写入使能信号、行地址选通信号、列地址选通信号、芯片选择信号等进行解码来产生对应于命令cmd的控制信号。

91.图4示出根据各种示例性实施例的图3的半导体存储器装置的第一存储体阵列。

92.参照图4,第一存储体阵列310包括多条字线wl1至wl2m(其中,m是大于二的自然数)、多条位线btl1至btl2n(其中,n是大于二的自然数)和设置在字线wl1至wl2m与位线btl1至btl2n之间的交叉点附近的多个存储器单元mc。在示例性实施例中,所述多个存储器单元mc中的每一个存储器单元可包括dram单元结构。多个存储器单元mc连接到的多条字线wl1至wl2m可被称作第一存储体阵列310的行,并且多个存储器单元mc连接到的多条位线btl1至btl2n可被称作第一存储体阵列310的列。

93.图5是示出根据示例性实施例的图3的半导体存储器装置中的地址交换电路的框图。

94.参照图5,地址交换电路(asc)400可包括随机选择信号产生器(rssg)410和地址交换器430。

95.随机选择信号产生器410可响应于通电信号pup或复位信号rst随机地产生随机选择信号rss。地址交换器430可响应于随机选择信号rss交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addr。

96.随机选择信号产生器410可包括诸如物理不可克隆函数(puf)、随机数产生器、反熔丝(anti

‑

fuse)电路或者熔丝(fuse)电路的电路元件,所述电路元件通过通电信号pup或者复位信号rst触发以随机地输出随机选择信号rss。

97.半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e的每一个中的随机选择信号产生器通过通电信号pup或者复位信号rst触发,并且可产生具有不同逻辑电平的随机选择信号rss,并且半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e的每一个半导体存储器装置中的地址交换器可响应于具有不同逻辑电平的随机选择信号rss将行地址row_addr转换为指示不同的存储器单元行的不同的交换后的行地址s_row_addr。

98.图6是示出根据示例性实施例的图5的地址交换电路的示例的框图。

99.参照图6,地址交换电路400a可包括随机选择信号产生器410a和地址交换器430。

100.地址交换电路400a可包括物理不可克隆函数(puf)410a,并且puf 410a可响应于通电信号pup或复位信号rst随机地产生随机选择信号rss。地址交换器430可响应于随机选择信号rss交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addr。

101.当图5中的随机选择信号产生器410由如图6中的puf 410a实施时,地址交换电路400a可执行地址交换操作,同时抵御存储器系统外部的非法侵入。

102.图7是根据示例性实施例的图6的地址交换电路中的物理不可克隆函数(puf)的示例。

103.在图7中,假设随机选择信号rss包括第一随机选择信号(比特)rss1和第二随机选择信号(比特)rss2,并且puf 410a可交换行地址row_addr的一部分比特ra0、ra1、ra2和ra3,以输出交换后的行地址s_row_addr的一部分比特sra0、sra1、sra2和sra3。

104.参照图7,当第一随机选择信号rss1和第二随机选择信号rss2对应于

‘

00’时,行地址row_addr的一部分比特ra0、ra1、ra2和ra3可分别交换为交换后的行地址s_row_addr的一部分比特sra0、sra1、sra2和sra3。当第一随机选择信号rss1和第二随机选择信号rss2对应于

‘

01’时,行地址row_addr的一部分比特ra0、ra1、ra2和ra3可分别交换为交换后的行地

址s_row_addr的一部分比特sra1、sra2、sra3和sra0。

105.当第一随机选择信号rss1和第二随机选择信号rss2对应于

‘

10’时,行地址row_addr的一部分比特ra0、ra1、ra2和ra3可分别交换为交换后的行地址s_row_addr的一部分比特sra2、sra3、sra0和sra1。当第一随机选择信号rss1和第二随机选择信号rss2对应于

‘

11’时,行地址row_addr的一部分比特ra0、ra1、ra2和ra3可分别交换为交换后的行地址s_row_addr的一部分比特sra3、sra0、sra1和sra2。

106.因此,当图5中的随机选择信号产生器410被通电信号pup或者复位信号rst触发,并且确定随机选择信号rss的逻辑电平时,地址交换器430可基于随机地确定的随机选择信号rss的逻辑电平随机地交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addr。

107.图8是示出根据示例性实施例的图5的地址交换电路的地址交换器的电路图。

108.在图8中,假设随机选择信号rss包括第一随机选择信号rss1和第二随机选择信号rss2,并且地址交换器430可响应于第一随机选择信号rss1和第二随机选择信号rss2交换行地址row_addr的一部分比特ra0、ra1、ra2和ra3,以输出交换后的行地址s_row_addr的一部分比特sra0、sra1、sra2和sra3。

109.参照图8,地址交换器430可包括多个多路复用器431、433、435和437。

110.多路复用器431、433、435和437中的每一个多路复用器接收行地址row_addr的一部分比特ra0、ra1、ra2和ra3中的对应一个,并且基于第一随机选择信号rss1和第二随机选择信号rss2的组合输出一部分比特ra0、ra1、ra2和ra3中的对应一个,作为交换后的行地址s_row_addr的一部分比特sra0、sra1、sra2和sra3中的对应一个。

111.如参照图7的描述,行地址row_addr的一部分比特ra0、ra1、ra2和ra3可交换为一部分比特(sra0、sra1、sra2和sra3)、一部分比特(sra1、sra2、sra3和sra0)、一部分比特(sra2、sra3、sra0和sra1)和一部分比特(sra3、sra0、sra1和sra2)之一。

112.图8中的地址交换器430中的多路复用器的数量可根据待交换的比特数变化。为了交换p个比特的行地址row_addr,地址交换器430可包括2p个多路复用器,并且随机选择信号rss包括p个比特。这里,p为自然数。

113.图9是示出根据示例性实施例的图5的地址交换电路的另一示例的框图。

114.参照图9,地址交换电路400b可包括反熔丝电路410b和地址交换器430。

115.第一随机选择信号rss1和第二随机选择信号rss2的逻辑电平可在反熔丝电路410b中被编程,并且反熔丝电路410b可响应于通电信号pup或者复位信号rst将第一随机选择信号rss1和第二随机选择信号rss2输出至地址交换器430。地址交换器430可响应于随机选择信号rss1和rss2交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addr。

116.第一随机选择信号rss1和第二随机选择信号rss2的逻辑电平可按照不同序列被编程在半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的反熔丝电路中。

117.第一随机选择信号rss1和第二随机选择信号rss2可按照

‘

00’的序列被编程在第一半导体存储器装置中的反熔丝电路中,可按照

‘

01’的序列被编程在第二半导体存储器装置中的反熔丝电路中,可按照

‘

10’的序列被编程在第三半导体存储器装置中的反熔丝电路

中,并且可按照

‘

11’的序列被编程在第四半导体存储器装置中的反熔丝电路中。

118.在一些示例性实施例中,随机选择信号产生器410可采用熔丝电路来替代反熔丝电路410b。

119.图10示出根据示例性实施例的图2的存储器模块的地址交换操作的示例。

120.在图10中,示出了半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的半导体存储器装置201a至201e和控制装置500a。将理解,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的其余的那些按照相似的方式操作,并且因此为了简明起见,省略了对它们的描述。

121.参照图10,控制装置500a接收命令cmd、访问地址addr和复位信号rst,并且将命令cmd和访问地址addr中继转发至半导体存储器装置201a至201e。另外,控制装置500a将复位信号rst中继转发至半导体存储器装置201a至201e。

122.半导体存储器装置201a包括存储器单元阵列300a,半导体存储器装置201b包括存储器单元阵列300b,半导体存储器装置201c包括存储器单元阵列300c,半导体存储器装置201d包括存储器单元阵列300d,并且半导体存储器装置201e包括存储器单元阵列300e。

123.半导体存储器装置201a中的地址交换电路将行地址转换为第一交换后的行地址,以启用存储器单元阵列300a的目标字线wla,半导体存储器装置201b中的地址交换电路将行地址转换为第二交换后的行地址,以启用存储器单元阵列300b的目标字线wlb,半导体存储器装置201c中的地址交换电路将行地址转换为第三交换后的行地址,以启用存储器单元阵列300c的目标字线wlc,半导体存储器装置201d中的地址交换电路将行地址转换为第四交换后的行地址,以启用存储器单元阵列300d的目标字线wld,并且半导体存储器装置201e中的地址交换电路将行地址转换为第五交换后的行地址,以启用存储器单元阵列300e的目标字线wle。

124.因此,半导体存储器装置201a至201e响应于访问地址addr分别启用不同的目标字线wla、wlb、wlc、wld和wle。另外,如果访问地址addr被密集地访问,则在半导体存储器装置201a至201e中分别由目标字线wla、wlb、wlc、wld和wle分散的受害字线wlf、wlg、wlh、wli和wlj是不同的。因此,半导体存储器装置201a至201e可分散受访问地址干扰addr的受害字线wlf、wlg、wlh、wli和wlj。

125.在图10中,awl指示对应于目标字线wla、wlb、wlc、wld和wle的侵略字线,并且vwl指示受害字线。

126.图11是详细示出根据示例性实施例的图1的存储器系统的存储器模块的另一示例的框图。

127.参照图11,存储器模块100b包括设置在(或者安装在)电路板101中的控制装置500b、多个半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e、多个数据缓冲器(db)141至145和151至155、模块电阻单元(mru)160和170、spd芯片180和pmic 185。

128.图11的存储器模块100b与图2的存储器模块100a不同之处在于:控制装置500b执行地址交换,并且将交换后的地址提供至半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e,以及控制装置500b接收电源电压vdd。

129.控制装置500b接收命令cmd、访问地址addr、时钟信号ck和复位信号rst,响应于复

位信号rst或通电信号随机地交换访问地址addr的一部分比特,以产生交换后的地址,以将交换后的地址分别提供至半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e。控制装置500b可包括与半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的相应的半导体存储器装置对应的多个地址交换电路。

130.半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的每一个半导体存储器装置接收交换后的地址中的对应的一个,并且启用与交换后的地址中的相应一个对应的目标字线,使得半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的两个或更多个半导体存储器装置相对于相同的访问地址addr启用不同的目标字线。

131.因此,当访问地址addr被密集地访问时,半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e可分散(即,区分)受访问地址addr干扰的受害字线。

132.图12是示出根据示例性实施例的图11的存储器模块中的控制装置的示例的框图。

133.参照图12,控制装置500b可包括存储器管理电路(mmu)510、地址交换电路块(asb)520。

134.mmu 510可将命令cmd和时钟信号ck中继转发至半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e,并且可将访问地址addr提供至asb 520。

135.mmu 510可包括控制电路511、命令缓冲器c_buf 513、时钟缓冲器ck_buf 515和地址缓冲器a_buf 517。控制电路511控制命令缓冲器、时钟缓冲器515和地址缓冲器517,以控制命令cmd、时钟信号ck和访问地址addr的缓冲时间。

136.asb 520可响应于基于电源电压vdd的复位信号rst或者通电信号随机地交换访问地址addr的一部分比特,以产生交换后的地址saddra至saddrk,以将交换后的地址saddra至saddrk分别提供至半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e。

137.控制电路511可控制提供交换后的地址saddra至saddrk的时序和提供命令cmd和时钟信号ck的时序。

138.图13是示出根据示例性实施例的图12的控制装置中的地址交换电路块(asb)的示例的框图。

139.参照图13,asb 520包括通电信号产生器pusg 530和多个地址交换电路asc1 540a至asck 540k。

140.通电信号产生器530产生响应于来自pmic 185的电源电压vdd等于或大于参考电压启用的通电信号pup。通电信号产生器530将通电信号pup提供至地址交换电路540a至540k。

141.地址交换电路540a至540k可响应于通电信号pup或复位信号rst随机地交换访问地址addr的一部分比特,以产生交换后的地址saddra至saddrk,并且可将交换后的地址saddra至saddrk分别提供至半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e。

142.地址交换电路540a至540k的数量可等于或小于半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e的数量。控制装置500b可控制地址交换电路540a至540k,以将交换后的地址saddra至saddrk分别提供至半导体存储器装置205a至205e、206a

至206e、207a至207e和208a至208e。

143.图14是示出根据示例性实施例的图13的地址交换电路块的地址交换电路之一的框图。

144.图14通过示图的方式示出地址交换电路540a的配置,并且将理解,地址交换电路540b至540k中的每一个地址交换电路的配置可与地址交换电路540a的配置实质上相同,并且因此为了简明起见,省略对其的重复描述。

145.参照图14,地址交换电路540a可包括随机选择信号产生器(rssg)541和地址交换器543。

146.随机选择信号产生器541可响应于通电信号pup或复位信号rst随机地产生随机选择信号rss。地址交换器543可响应于随机选择信号rss交换行地址row_addr的一部分比特,以输出交换后的行地址s_row_addra。

147.地址交换器543可包括通过通电信号pup或复位信号rst触发以随机地输出随机选择信号rss的电路元件,诸如物理不可克隆函数(puf)、随机数产生器、反熔丝电路或者熔丝电路。

148.地址交换电路540a至540k中的每一个地址交换电路中的随机选择信号产生器通过通电信号pup或复位信号rst被触发,并且可产生具有不同逻辑电平的随机选择信号rss,并且地址交换电路540a至540k中的每一个地址交换电路中的地址交换器可响应于具有不同逻辑电平的随机选择信号rss将行地址row_addr转换为指示不同的存储器单元行的不同的交换后的行地址s_row_addr。

149.图15是示出根据各种示例性实施例的图11的存储器模块中的半导体存储器装置之一的框图。

150.参照图15,半导体存储器装置205a可包括控制逻辑电路210、地址寄存器220a、存储体控制逻辑230、行地址多路复用器(ra mux)240、列地址(ca)锁存器250、行解码器260、列解码器270、存储器单元阵列300、读出放大器285、输入/输出门控电路(i/o门控电路)290、数据输入/输出(i/o)缓冲器295、刷新计数器245和ecc引擎297。

151.半导体存储器装置205a与半导体存储器装置201a不同之处在于:半导体存储器装置205a包括地址寄存器220a而不是地址寄存器220,并且不包括通电信号产生器225。

152.地址寄存器220a可从控制装置500b接收包括存储体地址bank_addr、交换后的行地址s_row_addr和列地址col_addr的交换后的地址saddra。地址寄存器220a可将接收到的存储体地址bank_addr提供至存储体控制逻辑230,并且可将接收到的交换后的行地址s_row_addr提供至行地址多路复用器240,并且可将接收到的列地址col_addr提供至列地址锁存器250。

153.地址寄存器220a不执行地址交换操作。

154.图16示出了根据示例性实施例的图11的存储器模块的地址交换操作的示例。

155.在图16中,示出了半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的半导体存储器装置205a至205e和控制装置500b。应该理解,半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的其余半导体存储器装置按照相似的方式操作,并且因此为了简明,省略了对它们的描述。

156.参照图16,控制装置500b接收命令cmd、访问地址addr和复位信号rst,从pmic 185

接收电源电压vdd,将命令cmd中继转发至半导体存储器装置205a至205e,并且将交换后的地址saddra至saddre分别提供至半导体存储器装置205a至205e。

157.半导体存储器装置205a包括存储器单元阵列300a,半导体存储器装置205b包括存储器单元阵列300b,半导体存储器装置205c包括存储器单元阵列300c,半导体存储器装置205d包括存储器单元阵列300d,并且半导体存储器装置205e包括存储器单元阵列300e。

158.半导体存储器装置205a的行解码器响应于交换后的地址saddra的第一交换行地址启用存储器单元阵列300a的目标字线wla1,并且半导体存储器装置205b的行解码器响应于交换后的地址saddrb的第二交换行地址启用存储器单元阵列300b的目标字线wlb1。

159.半导体存储器装置205c的行解码器响应于交换后的地址saddrc的第三交换行地址启用存储器单元阵列300c的目标字线wlc1,半导体存储器装置205d的行解码器响应于交换后的地址saddrd的第四交换行地址启用存储器单元阵列300d的目标字线wld1,并且半导体存储器装置205e的行解码器响应于交换后的地址saddre的第五交换行地址启用存储器单元阵列300e的目标字线wle1。

160.因此,当存储器控制器25提供访问地址addr时,半导体存储器装置205a至205e分别启用不同的目标字线wla1、wlb1、wlc1、wld1和wle1。另外,如果访问地址addr被密集地访问,则半导体存储器装置205a至205e中分别被目标字线wla1、wlb1、wlc1、wld1和wle1干扰的受害字线wlf1、wlg1、wlh1、wli1和wlj1是不同的。因此,半导体存储器装置205a至205e可分散受访问地址addr干扰的受害字线wlf1、wlg1、wlh1、wli1和wlj1。

161.在图16中,awl指示对应于目标字线wla1、wlb1、wlc1、wld1和wle1的侵略字线,并且vwl指示受害字线。

162.图17a是示出根据示例性实施例的图1的存储器系统的存储器模块的另一示例的框图。

163.图17a的存储器模块100c与图2的存储器模块100a的不同之处在于:存储器模块100c不包括从多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e接收数据信号dq和数据选通信号dqs/将数据信号dq和数据选通信号dqs发送至多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e的数据缓冲器(db)。存储器模块100c可通过控制装置500a从存储器控制器25接收数据信号dq和数据选通信号dqs/通过控制装置500a将数据信号dq和数据选通信号dqs发送至存储器控制器25。

164.如参照图2描述的,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置可包括地址交换电路,所述地址交换电路响应于通电信号或复位信号执行地址交换操作,以随机地交换访问地址addr的一部分比特,以产生交换后的地址,并且响应于交换后的地址启用存储器单元阵列中的多条字线中的对应的目标字线,使得半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的至少两个半导体存储器装置启用不同的目标字线。

165.图17b是示出根据示例性实施例的图1的存储器系统的存储器模块的另一示例的框图。

166.图17b的存储器模块100d与图11的存储器模块100b的不同之处在于:存储器模块100d不包括从多个半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e接收数据信号dq和数据选通信号dqs/将数据信号dq和数据选通信号dqs发送至多个半导体

存储器装置205a至205e、206a至206e、207a至207e和208a至208e的数据缓冲器(db)。存储器模块100d可通过控制装置500b从存储器控制器25接收数据信号dq和数据选通信号dqs/通过控制装置500b将数据信号dq和数据选通信号dqs发送至存储器控制器25。控制装置500b从存储器控制器25接收复位信号rst,并且从pmic185接收电源电压vdd。

167.如参照图11描述的,控制装置500b接收命令cmd、访问地址addr、时钟信号ck和复位信号rst,响应于复位信号rst或通电信号随机地交换访问地址addr的一部分比特,以产生交换后的地址,以将交换后的地址分别提供至图17b中的存储器模块100d中的半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e。控制装置500b可包括与半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的相应的半导体存储器装置对应的多个地址交换电路。

168.半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的每一个半导体存储器装置接收交换后的地址中的对应的一个交换后的地址,并且启用与对应的一个交换后的地址对应的目标字线,使得半导体存储器装置205a至205e、206a至206e、207a至207e和208a至208e中的两个或更多个相对于访问地址addr启用不同的目标字线。

169.图18是示出根据示例性实施例的堆叠的存储器装置的示例的框图。

170.参照图18,半导体存储器装置600a可包括提供堆叠的芯片结构的第一组裸片610和第二组裸片620。

171.第一组裸片610可包括至少一个缓冲器裸片611。第二组裸片620可包括堆叠在至少一个缓冲器裸片611上的多个存储器裸片620

‑

1至620

‑

s,并且通过多条衬底穿通件(或者,硅穿通件(tsv))线传递数据。这里,s是大于二的整数。

172.存储器裸片620

‑

1至620

‑

s中的每一个存储器裸片可包括具有用于存储数据的存储器单元阵列的单元核622、ecc引擎624和地址交换电路(asc)626。地址交换电路626可采用图5的地址交换电路400。因此,地址交换电路626可随机地交换行地址row_addr的一部分比特,以产生交换后的行地址,并且可将交换后的行地址提供至单元核中的行解码器。因此,存储器裸片620

‑

1至620

‑

s中的行解码器可相对于来自存储器控制器的相同的访问地址启用不同的目标字线。

173.存储器裸片620

‑

1至620

‑

s中的每一个存储器裸片可采用与图3的半导体存储器装置201a相似的配置。

174.缓冲器裸片611可包括具有ecc引擎614和mmu 616的接口电路ifc 612。

175.ecc引擎614可被称作穿通件ecc引擎,并且可校正从存储器裸片620

‑

1至620

‑

s中的至少一个存储器裸片提供的传输中的传输错误。

176.形成在一个存储器裸片620

‑

s的数据tsv线组632可包括多条tsv线l1至ls,并且奇偶校验tsv线组634可包括多条tsv线l10至lt。数据tsv线组632的tsv线l1至ls和奇偶校验tsv线组634的奇偶校验tsv线l10至lt可连接至对应地形成在存储器裸片620

‑

1至620

‑

s之间的微凸块mcb。

177.堆叠的存储器装置600a可具有三维(3d)芯片结构或者2.5d芯片结构,以通过数据总线b10与主机通信。缓冲器裸片611可通过数据总线b10与存储器控制器连接。

178.图19示出根据示例性实施例的图18的堆叠的存储器装置的示例。

179.参照图19,堆叠的存储器装置600a可包括缓冲器裸片611和对应于存储器裸片

620

‑

1至620

‑

s的多个存储器裸片620a、620b、620c和620d。

180.参照图19,缓冲器裸片611包括内部命令产生器icg 613和接口电路ifc 612。接口电路ifc 612包括mmu 616。来自内部命令产生器613的内部命令icmd通过针对每个沟道独立形成的命令硅穿通件tsv_c被提供至存储器裸片620a、620b、620c和620d。

181.接口电路612可在写入操作中通过针对存储器裸片620a、620b、620c和620d共同形成的数据硅穿通件tsv_d将数据dq和访问地址addr提供至对应的存储器裸片,并且可将来自对应的存储器裸片的数据提供至外部。

182.存储器裸片620a、620b、620c和620d可分别包括:命令解码器621a至621d,其通过解码内部命令输出内部控制信号;以及地址交换电路626a至626d,其随机地交换访问地址中的行地址的一部分比特以输出交换后的行地址。地址交换电路626a至626d中的每一个可采用图4的地址交换电路400,并且可包括随机选择信号产生器和地址交换器。

183.地址交换电路626a至626d可相对于相同的访问地址addr启用指示存储器裸片620a、620b、620c和620d中不同的存储器位置的不同的目标字线。

184.图20是示出根据示例性实施例的堆叠的存储器装置的另一示例的框图。

185.参照图20,半导体存储器装置600b可包括提供堆叠的芯片结构的第一组裸片610

‑

1和第二组裸片620

‑

1。

186.第一组裸片610

‑

1可包括至少一个缓冲器裸片611

‑

1。第二组裸片620

‑

1可包括堆叠在所述至少一个缓冲器裸片611

‑

1上的多个存储器裸片620a

‑

1至620a

‑

s,并且通过多条衬底穿通件(或者,硅穿通件(tsv))线传递数据。这里,s是大于二的整数。

187.存储器裸片620a

‑

1至620a

‑

s中的每一个存储器裸片可包括单元核622和ecc引擎624,所述单元核622包括用于存储数据的存储器单元阵列。

188.存储器裸片620a

‑

1至620a

‑

s中的每一个存储器裸片可采用与图15的半导体存储器装置205a的配置相似的配置。

189.缓冲器裸片611

‑

1可具有包括ecc引擎614和asb 617的接口电路ifc 612a。

190.asb 617可采用图13的asb 520。因此,asb 617可包括通电信号产生器和多个地址交换电路。

191.地址交换电路的数量可等于或小于存储器裸片620a

‑

1至620a

‑

s的数量。

192.通电信号产生器产生响应于电源电压等于或大于参考电压启用的通电信号。通电信号产生器将通电信号提供至地址交换电路。地址交换电路可响应于通电信号或复位信号rst随机地交换访问地址addr的一部分比特,以产生交换后的地址,并且可分别将交换后的地址提供至存储器裸片620a

‑

1至620a

‑

s。

193.存储器裸片620a

‑

1至620a

‑

s中的每一个存储器裸片中的地址寄存器接收交换后的地址的对应的交换后的地址,并且将交换后的地址提供至行解码器。行解码器可启用存储器单元阵列中的由交换后的地址指示的目标字线。

194.存储器裸片620a

‑

1至620a

‑

s可相对于相同的访问地址addr启用指示存储器裸片620a

‑

1至620a

‑

s中的不同存储器位置的不同的目标字线。

195.ecc引擎614可被称作穿通件ecc引擎,并且可校正从存储器裸片620a

‑

1至620a

‑

s中的至少一个提供的传输中的传输错误。

196.形成在一个存储器裸片620a

‑

s的数据tsv线组632可包括多条tsv线l1至ls,并且

奇偶校验tsv线组634可包括多条tsv线l10至lt。数据tsv线组632的tsv线l1至ls和奇偶校验tsv线组634的奇偶校验tsv线l10至lt可连接至存储器裸片620a

‑

1至620a

‑

s中对应地形成的微凸块mcb。

197.堆叠的存储器装置600b可具有三维(3d)芯片结构或者2.5d芯片结构,以通过数据总线b10与主机通信。缓冲器裸片611

‑

1可通过数据总线b10与存储器控制器连接。

198.图21是示出根据示例性实施例的操作存储器模块的方法的流程图。

199.参照图1至图17b和图21,提供了一种对包括安装在电路板上的控制装置500a和多个半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e的存储器模块500a进行操作的方法。

200.根据所述方法,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的地址交换电路400可基于来自控制装置500a的通电信号pup或复位信号rst随机地产生随机选择信号rss(s110)。半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的地址交换电路400可按照不同序列产生随机选择信号rss。

201.半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的地址交换电路400可将访问地址转换为交换后的地址(s130)。例如,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的地址交换电路400可响应于随机选择信号rss交换行地址row_addr的一部分比特,以产生交换后的行地址s_row_addr(s130)。

202.半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的行解码器260可响应于对应的交换后的地址启用不同的字线(s150)。例如,半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的每一个半导体存储器装置中的行解码器260可响应于交换后的行地址s_row_addr启用目标字线,使得半导体存储器装置201a至201e、202a至202e、203a至203e和204a至204e中的至少两个或更多个半导体存储器装置启用不同的目标字线。

203.因此,根据所述方法,如果访问地址addr被密集地访问,则半导体存储器装置201a至201e可分散受访问地址addr干扰的受害字线。

204.图22是示出根据示例性实施例的包括堆叠的存储器装置的半导体封装件的示图。

205.参照图22,半导体封装件700可包括一个或多个堆叠的存储器装置710和图形处理单元(gpu)720。

206.堆叠的存储器装置710和gpu 720可安装在中间件730上,并且安装有堆叠的存储器装置710和gpu 720的中间件可安装在封装件衬底740上。封装件衬底740安装在焊料球750上。gpu 720可与图1中的存储器控制器25执行相同的操作,或者可包括存储器控制器25。gpu 720可在堆叠的存储器装置710中存储图形处理中产生或使用的数据。

207.堆叠的存储器装置710可以以各种形式实施,并且堆叠的存储器装置710可为其中堆叠多层的高带宽存储器(hbm)形式的存储器装置。在一些示例性实施例中,堆叠的存储器装置710可采用根据图18或图20的堆叠的存储器装置。因此,堆叠的存储器装置710可包括缓冲器裸片和多个存储器裸片。缓冲器裸片可包括接口电路。

208.存储器裸片中的每一个存储器裸片可包括单元核、ecc引擎和地址交换电路,所述

单元核包括存储器单元阵列。

209.地址交换电路可采用图5的地址交换电路400。因此,地址交换电路可随机地交换行地址的一部分比特,以产生交换后的行地址,并且可将交换后的行地址提供至单元核中的行解码器。因此,存储器裸片中的行解码器可相对于来自存储器控制器的相同的访问地址启用不同的目标字线。

210.缓冲器裸片可包括asb。asb可采用图13的asb。因此,asb可包括通电信号产生器和多个地址交换电路。地址交换电路可响应于通电信号或复位信号随机地交换访问地址的一部分比特,以产生交换后的地址,并且可将交换后的地址分别提供至存储器裸片。

211.所述多个堆叠的存储器装置710可安装在中间件730上,并且gpu 720可与所述多个堆叠的存储器装置710通信。例如,堆叠的存储器装置710和gpu 720中的每一个可包括物理区,并且可通过物理区在堆叠的存储器装置710与gpu 720之间执行通信。

212.图23是示出根据示例性实施例的具有四列(quad

‑

rank)存储器模块的存储器系统的框图。

213.参照图23,存储器系统800可包括存储器控制器810以及一个或多个存储器模块820和830。图23中示出了两个存储器模块820和830,但这仅是示例。

214.存储器控制器810可控制一个或多个存储器模块820和830,以执行从处理器或主机供应的命令。存储器控制器810可实施在处理器或主机中,或者可使用应用处理器或者片上系统(soc)被实施。为了信号完整性,可使用存储器控制器810的总线840上的电阻器rtt来实现源端接。电阻器rtt可耦接至电源电压vddq。存储器控制器810可包括:发送器811,向一个或多个存储器模块820和830发送信号;以及接收器813,从一个或多个存储器模块820和830接收信号。

215.一个或多个存储器模块820和830可被称作第一存储器模块820和第二存储器模块830。第一存储器模块820和第二存储器模块830可通过总线840耦接至存储器控制器810。第一存储器模块820和第二存储器模块830中的每一个可对应于图2的存储器模块100或者图18的存储器模块100a。第一存储器模块820可包括一个或多个存储器列rk1和rk2,并且第二存储器模块830可包括一个或多个存储器列rk3和rk4。

216.第一存储器模块820和第二存储器模块830中的每一个存储器模块可包括设置在电路板的中心的控制装置、设置在控制装置与电路板的第一边缘部分之间的第一组半导体存储器装置和设置在控制装置与电路板的第二边缘部分之间的第二组半导体存储器装置。

217.在示例性实施例中,半导体存储器装置中的每一个半导体存储器装置可包括地址交换电路,并且地址交换电路交换行地址的一部分比特,以产生交换后的行地址,并且将交换后的行地址应用于行解码器。在示例性实施例中,控制装置可包括对应于半导体存储器装置的多个地址交换电路,地址交换电路交换行地址的一部分比特,以产生交换后的行地址,并且将交换后的行地址应用于半导体存储器装置。半导体存储器装置中的每一个半导体存储器装置中的行解码器可响应于对应的一个交换后的行地址启用不同的目标字线。

218.第一存储器模块820和第二存储器模块830中的半导体存储器装置可相对于相同的访问地址启用不同的目标字线,以分散受访问地址干扰的受害字线。

219.图24是示出根据示例性实施例的包括存储器模块的移动系统的框图。

220.参照图24,移动系统900可包括应用处理器(ap)910、连接模块920、存储器模块

(mm)950、非易失性存储器装置(nvm)940、用户接口930和电源970。应用处理器910可包括存储器控制器(mct)911。

221.应用处理器910可执行应用,诸如网络浏览器、游戏应用、视频播放器等。连接模块920可与外部装置执行有线或无线通信。

222.存储器模块950可存储通过应用处理器910处理的数据,或者作为工作存储器操作。存储器模块950可包括多个半导体存储器装置(md)951至95q(其中,q是大于三的自然数)和控制装置961。半导体存储器装置951至95q中的每一个半导体存储器装置可包括地址交换电路,并且地址交换电路可交换行地址的一部分比特,以产生交换后的行地址,并且将交换后的行地址应用于行解码器。在一些示例性实施例中,控制装置961可包括对应于半导体存储器装置951至95q的多个地址交换电路,地址交换电路可交换行地址的一部分比特,以产生交换后的行地址并将交换后的行地址应用于半导体存储器装置951至95q。半导体存储器装置951至95q中的每一个半导体存储器装置中的行解码器可响应于交换后的行地址中对应的一个交换后的行地址启用不同的目标字线。

223.因此,半导体存储器装置951至95q可相对于相同的访问地址启用不同的目标字线,以当访问地址被密集地访问时分散受访问地址干扰的受害字线。

224.非易失性存储器装置940可存储用于启动移动系统900的启动图像。用户接口30可包括诸如键盘、触摸屏等的至少一个输入装置以及诸如扬声器、显示装置等的至少一个输出装置。电源970可将操作电压供应至移动系统900。

225.在各种示例性实施例中,移动系统900和/或移动系统900的组件可按照各种形式被封装。

226.上述各种示例性实施例可应用于使用存储器模块或者堆叠的存储器装置的系统。

227.虽然上面已经示出和描述了各种示例性实施例,但是对于本领域的普通技术人员来说将显而易见的是,可在不脱离所附权利要求所述的本公开的精神和范围的情况下对其进行形式和细节上的修改和改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。