半导体存储装置

1.[相关申请]

[0002]

本技术享有以日本专利申请2020

‑

77416号(申请日:2020年4月24日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

实施方式涉及一种半导体存储装置。

背景技术:

[0004]

已知有nand(not and,与非)型闪速存储器作为能够非易失地存储数据的半导体存储装置。

技术实现要素:

[0005]

实施方式提供一种能够抑制写入动作的性能劣化且执行插入动作的半导体存储装置。

[0006]

实施方式的半导体存储装置具备:存储单元,连接于字线;以及控制电路,构成为执行反复进行编程循环的写入动作,所述编程循环包括将编程电压施加于所述字线的编程动作、及接在所述编程动作之后继续进行的验证动作。所述控制电路构成为,在所述写入动作中,每反复进行一次所述编程循环,便使所述编程电压上升第1量,在使所述写入动作中断的情况下,在重新开始所述写入动作后第n次(n为1以上的整数)为止的编程动作中,将所述第1量变更为第2量,所述第2量是小于所述第1量的正数。

附图说明

[0007]

图1是用来说明第1实施方式的存储器系统的构成的框图。

[0008]

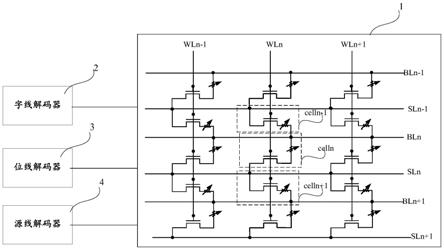

图2是用来说明第1实施方式的存储单元阵列的构成的电路图。

[0009]

图3是用来说明第1实施方式的存储单元晶体管的阈值电压分布的示意图。

[0010]

图4是用来说明第1实施方式的存储器系统中的写入动作的指令序列及时序图。

[0011]

图5是用来说明第1实施方式的存储器系统中的插入动作的指令序列及时序图。

[0012]

图6是用来说明第1实施方式的存储器系统中将中断考虑在内的写入动作的流程图。

[0013]

图7是用来说明第1实施方式的存储器系统中将中断考虑在内的写入动作的时序图。

[0014]

图8(a)~(c)是用来说明比较例的写入动作中的阈值电压分布变化的示意图。

[0015]

图9(a)~(c)是用来说明第1实施方式的写入动作中的阈值电压分布变化的示意图。

[0016]

图10是用来说明第2实施方式的存储器系统中将中断考虑在内的写入动作的流程图。

[0017]

图11是用来说明第2实施方式的第1例的存储器系统中将中断考虑在内的写入动作的流程图。

[0018]

图12(a)、(b)是用来说明第2实施方式的第1例的存储器系统中将中断考虑在内的写入动作的时序图。

[0019]

图13是用来说明第2实施方式的第2例的存储器系统中将中断考虑在内的写入动作的流程图。

[0020]

图14(a)、(b)是用来说明第2实施方式的第2例的存储器系统中将中断考虑在内的写入动作的时序图。

[0021]

图15是用来说明第2实施方式的第3例的存储器系统中将中断考虑在内的写入动作的流程图。

[0022]

图16是用来说明第2实施方式的第4例的存储器系统中将中断考虑在内的写入动作的流程图。

[0023]

图17是用来说明第3实施方式的存储器系统中将中断考虑在内的写入动作的流程图。

[0024]

图18是用来说明第3实施方式的存储器系统中将中断考虑在内的写入动作的时序图。

[0025]

图19是用来说明第4实施方式的存储器系统中将中断考虑在内的写入动作的流程图。

[0026]

图20是用来说明第4实施方式的存储器系统中将中断考虑在内的写入动作的时序图。

具体实施方式

[0027]

以下,参照附图对实施方式进行说明。此外,在以下说明中,对于具有同一功能及构成的构成要素标注共通的参照符号。另外,在对具有共通的参照符号的多个构成要素进行区分的情况下,对该共通的参照符号标注下标来进行区分。此外,在无需对多个构成要素特别进行区分的情况下,仅对该多个构成要素标注共通的参照符号,而不标注下标。

[0028]

1.第1实施方式

[0029]

对第1实施方式进行说明。以下,例举作为非易失性存储器的nand闪速存储器及具备该nand闪速存储器的存储器系统进行说明。

[0030]

1.1构成

[0031]

对第1实施方式的存储器系统的构成进行说明。

[0032]

1.1.1存储器系统

[0033]

首先,使用图1,对包含第1实施方式的存储器系统的构成的概要进行说明。

[0034]

如图1所示,存储器系统1具备半导体存储装置(nand闪速存储器)100及存储器控制器200。nand闪速存储器100与存储器控制器200例如可以通过它们的组合构成一个半导体装置,可以列举如sd

tm

卡的存储卡、或ssd(solid state drive,固态驱动器)等作为其示例。

[0035]

nand闪速存储器100具备多个存储单元,非易失地存储数据。存储器控制器200通过nand总线连接于nand闪速存储器100,并通过主机总线连接于主机装置300。而且,存储器

控制器200控制nand闪速存储器100,并且响应从主机装置300接收的命令,对nand闪速存储器100进行访问。主机装置300例如为数码相机或个人电脑等,主机总线例如是按照sd

tm

接口、sas(serial attached scsi(small computer system interface,小型计算机系统接口),串行连接scsi)、sata(serial ata(advanced technology attachment,高级技术附加装置),串行ata)、pcie(peripheral component interconnect express,外围部件互连标准)的总线。nand总线按照nand接口进行信号收发。

[0036]

nand接口的信号的具体例为芯片使能信号cen、指令锁存使能信号cle、地址锁存使能信号ale、写使能信号wen、读使能信号ren、就绪/忙碌信号rbn、及输入输出信号i/o。

[0037]

信号cen是用来启用nand闪速存储器100的信号,由“l(低(low))”电平断定。信号cle及ale是通知nand闪速存储器100输入到nand闪速存储器100的输入信号i/o分别为指令及地址的信号。信号ren由“l”电平断定,是用来从nand闪速存储器100读出输出信号i/o的信号。信号wen也由“l”电平断定,是用来将输入信号i/o擷取到nand闪速存储器100的信号。就绪/忙碌信号rbn是表示nand闪速存储器100处于就绪状态(能够从存储器控制器200接收命令的状态)还是忙碌状态(无法从存储器控制器200接收命令的状态)的信号,“l”电平表示忙碌状态。输入输出信号i/o是例如8比特的信号。而且,输入输出信号i/o是在nand闪速存储器100与存储器控制器200之间收发的数据的实体,也就是指令cmd、地址add、以及写入数据及读出数据等数据dat。

[0038]

1.1.2存储器控制器

[0039]

继续使用图1,对存储器控制器200的构成的详情进行说明。

[0040]

存储器控制器200例如为soc(system on a chip,片上系统),具备主机接口电路210、ram(random access memory,随机存取存储器)220、cpu(central processing unit,中央处理器)230、缓冲存储器240、nand接口电路250、及ecc(error check and correction,错误检查和校正)电路260。此外,以下所说明的存储器控制器200的各部210~260的功能通过硬件构成、或硬件资源与固件的组合构成的任意构成均能实现。

[0041]

主机接口电路210经由主机总线而与主机装置300连接,将从主机装置300接收的命令及数据分别传送到cpu230及缓冲存储器240。另外,响应cpu230的命令,将缓冲存储器240内的数据传送到主机装置300。

[0042]

ram220例如为dram(dynamic random access memory,动态随机存取存储器)等半导体存储器,用作cpu230的作业区域。而且,ram220保存用来管理nand闪速存储器100的固件或各种管理表等。

[0043]

cpu230控制存储器控制器200整体的动作。例如,cpu230从主机装置300接收到写入命令时,响应该写入命令,对nand接口电路250发布写入命令。进行读出动作及抹除动作时也一样。另外,cpu230执行用来管理nand闪速存储器100的各种处理。

[0044]

缓冲存储器240暂时保存写入数据或读出数据。

[0045]

nand接口电路250经由nand总线而与nand闪速存储器100连接,负责与nand闪速存储器100进行通信。而且,基于从cpu230接收的命令,将信号cen、ale、cle、wen及ren输出到nand闪速存储器100。另外,在写入动作时,将由cpu230发布的写入指令及缓冲存储器240内的写入数据作为输入输出信号i/o传送到nand闪速存储器100。进而,在读出动作时,将由cpu230发布的读出指令作为输入输出信号i/o传送到nand闪速存储器100,进而,接收作为

输入输出信号i/o的从nand闪速存储器100读出的数据,并将该数据传送到缓冲存储器240。

[0046]

ecc电路260进行与nand闪速存储器100中所存储的数据相关的错误检测及错误校正处理。也就是说,ecc电路260在写入数据时生成错误校正码,并对写入数据赋予该错误校正码,在读出数据时对其解码,检测有无错误位。而且,当检测到错误位时,特定出该错误位的位置,并校正错误。错误校正方法例如包括硬判定解码(hard bit decoding,硬位解码)处理及软判定解码(soft bit decoding,软位解码)处理。作为硬判定解码处理中所使用的硬判定解码编码,例如可以使用bch(bose

‑

chaudhuri

‑

hocquenghem)码或rs(reed

‑

solomon)码等,作为软判定解码处理中所使用的软判定解码编码,例如可以使用ldpc(low density parity check,低密度奇偶校验)码等。

[0047]

1.1.3nand闪速存储器

[0048]

其次,对nand闪速存储器100的构成进行说明。如图1所示,nand闪速存储器100具备存储单元阵列110、行解码器120、驱动器130、感测放大器140、地址寄存器150、指令寄存器160、定序器170及温度传感器180。

[0049]

存储单元阵列110具备多个区块blk,所述多个区块blk包含与行及列建立对应的多个非易失性存储单元。图1中图示出4个区块blk0~blk3作为一例。而且,存储单元阵列110存储从存储器控制器200获取的数据。

[0050]

行解码器120基于地址寄存器150内的区块地址ba选择区块blk0~blk3中的任一区块,进而在所选择的区块blk中选择字线。

[0051]

驱动器130基于地址寄存器150内的页地址pa,对所选择的区块blk经由行解码器120供给电压。

[0052]

感测放大器140在数据的读出动作时,感测存储单元阵列110内的存储单元晶体管的阈值电压,并读出数据。接着,将该数据dat输出到存储器控制器200。在数据的写入动作时,将从存储器控制器200接收的写入数据dat传送到存储单元阵列110。

[0053]

地址寄存器150保存从存储器控制器200接收的地址add。该地址add中包含上述区块地址ba及页地址pa。指令寄存器160保存从存储器控制器200接收的指令cmd。

[0054]

温度传感器180计测nand闪速存储器100的温度,并将与该所计测出的温度对应的温度信息发送到定序器170。温度传感器180可以配置在nand闪速存储器100内的任意位置,优选为主要能够生成与存储单元阵列110的温度对应的温度信息。

[0055]

定序器170基于指令寄存器160中所保存的指令cmd,控制nand闪速存储器100整体的动作。另外,定序器170包含计数器171。计数器171构成为,能够根据来自定序器170的指示在任意时间点开始或结束计测,且具有如下功能,即,基于计数所得的值计测各种处理所需时间。定序器170能够基于由计数器171计测出的时间,控制nand闪速存储器100的动作。另外,定序器170能够基于从温度传感器180获取的温度信息,控制nand闪速存储器100的动作。

[0056]

1.1.4存储单元阵列

[0057]

图2是用来说明第1实施方式的存储单元阵列的构成的电路图。图2中,示出存储单元阵列110所包含的多个区块blk中的1个区块blk。

[0058]

如图2所示,区块blk例如包含4个串单元su(su0~su3)。各串单元su包含分别与位线bl0~blm(m为1以上的整数)建立关联的多个nand串ns。各nand串ns例如包含8个存储单

元晶体管mt0~mt7、以及选择晶体管st1及st2。存储单元晶体管mt包含控制栅极及电荷储存层,非易失地存储与数据对应的电荷(电子)。选择晶体管st1及st2分别用于各种动作时的串单元su的选择。

[0059]

在各nand串ns中,存储单元晶体管mt0~mt7串联连接。选择晶体管st1的漏极连接于与其建立关联的位线bl,选择晶体管st1的源极连接于串联连接的存储单元晶体管mt0~mt7的一端。选择晶体管st2的漏极连接于串联连接的存储单元晶体管mt0~mt7的另一端。选择晶体管st2的源极连接于源极线sl。

[0060]

在同一区块blk中,存储单元晶体管mt0~mt7的控制栅极分别共通连接于字线wl0~wl7。串单元su0~su3内的选择晶体管st1的栅极分别共通连接于选择栅极线sgd0~sgd3。选择晶体管st2的栅极共通连接于选择栅极线sgs。

[0061]

也就是说,区块blk是共用同一字线wl0~wl7的多个串单元su的集合体。区块blk例如为数据的抹除单位。也就是说,同一区块blk内包含的存储单元晶体管mt中所保存的数据被一次抹除。

[0062]

串单元su是各自连接于不同位线bl且连接于同一选择栅极线sgd的多个nand串ns的集合体。也将串单元su中共通连接于同一字线wl的存储单元晶体管mt的集合体称为单元组件cu。例如,将单元组件cu内的多个存储单元晶体管mt内所存储的同位比特的集合定义为“1页”。单元组件cu根据存储单元晶体管mt存储的数据的比特数,能够具有2页数据以上的存储容量。

[0063]

此外,以上所说明的存储单元阵列110的电路构成并不限定于以上所说明的构成。例如,各nand串ns包含的存储单元晶体管mt以及选择晶体管st1及st2的个数可以分别设计为任意个数。各区块blk包含的串单元su的个数可以设计为任意个数。

[0064]

1.1.5存储单元晶体管的阈值电压分布

[0065]

其次,对存储单元晶体管mt的阈值电压分布进行说明。

[0066]

在本实施方式中,1个存储单元晶体管mt能够保存例如2比特数据。将该2比特数据从下位比特起分别称为下位(lower)比特及上位(upper)比特。而且,将属于同一单元组件cu的存储单元保存的下位比特的集合称为下位页,将上位比特的集合称为上位页。也就是说,对1个串单元su内的1条字线wl(1个单元组件cu)分配2页,包含8条字线wl的串单元su具有16页的容量。或者,换句话说,“页”也可以定义为单元组件cu中所形成的存储空间的一部分。数据抹除以区块blk为单位进行,另一方面,数据的写入动作及读出动作也可以针对该每一页每或每单元组件cu进行。

[0067]

图3是表示各存储单元晶体管mt所获取的数据与阈值电压分布的关系的图。

[0068]

如上所述,存储单元晶体管mt能够保存2比特数据。也就是说,存储单元晶体管mt根据阈值电压能够获取4个状态。将该4个状态按照阈值电压从低到高依次称为“er”状态(state)、“a”状态、“b”状态及“c”状态。

[0069]“er”状态的存储单元晶体管mt的阈值电压小于电压ar,相当于数据的抹除状态。“a”状态的存储单元晶体管mt的阈值电压为电压ar以上且小于电压br(>ar)。“b”状态的存储单元晶体管mt的阈值电压为电压br以上且小于电压cr(>br)。“c”状态的存储单元晶体管mt的阈值电压为电压cr以上且小于电压vread(>cr)。以此方式分布的4个状态中,“c”状态为阈值电压最高的状态。电压ar~cr也称为读出电压vcgr,在读出动作中使用。电压

vread例如是读出动作时施加于并非读出对象的字线wl的电压,且是无论保存数据如何均使存储单元晶体管mt接通的电压。

[0070]

阈值电压分布通过写入由上述下位比特及上位比特构成的2比特(2页)数据而实现。也就是说,所述“er”状态到“c”状态与下位比特及上位比特的关系如下。

[0071]“er”状态:“11”(以“上位/下位”的顺序表示)

[0072]“a”状态:“01”[0073]“b”状态:“00”[0074]“c”状态:“10”[0075]

这样一来,在与阈值电压分布中相邻的2个状态对应的数据间,2比特中仅1比特发生变化。

[0076]

因此,在读出下位比特时,只要使用相当于下位比特值(“0”或“1”)发生变化的边界的电压即可,对于上位比特也一样如此。

[0077]

也就是说,如图3所示,在读出下位页数据的情况下,使用区别“a”状态与“b”状态的电压br作为读出电压,由此,判定存储单元晶体管mt的阈值电压是否小于电压br(即电压br以上)。

[0078]

在读出上位页数据的情况下,使用区别“er”状态与“a”状态的电压ar、及区别“b”状态与“c”状态的电压cr作为读出电压。由此,判定存储单元晶体管mt的阈值电压是否小于电压ar或为电压cr以上(即ar以上、小于电压cr)。

[0079]

此外,将与“a”状态对应的电压av设定在电压ar及电压br之间,将与“b”状态对应的电压bv设定在电压br及电压cr之间,将与“c”状态对应的电压cv设定在电压cr及电压vread之间。电压av~cv也称为验证电压vcgv,在验证动作中使用。在写入动作中,半导体存储装置100使处于“a”状态~“c”状态的存储单元晶体管mt的阈值电压分别上升到超过验证电压av~cv。由此,能够使处于“a”状态~“c”状态的存储单元晶体管mt的阈值电压分别分布在高于读出电压ar~cr的区域中。

[0080]

1.2动作

[0081]

其次,对第1实施方式的存储器系统的动作进行说明。

[0082]

以下说明中,将连接于作为数据写入对象的存储单元晶体管mt的字线wl称为选择字线wl。

[0083]

1.2.1写入动作的概要

[0084]

图4是用来说明第1实施方式的存储器系统中的写入动作的概要的指令序列及时序图。图4中,以时间序列表示写入动作时与存储器控制器200之间进行通信的信号i/o及rbn、以及根据该通信执行的写入动作中施加于选择字线wl的电压。如图4所示,在写入动作前的状态下,例如信号rbn为“h”电平,对选择字线wl施加电压vss。电压vss是接地电压,例如为0v。

[0085]

首先,存储器控制器200将指令集cs1及cs2作为指示写入动作的指令集wcs依次发送到半导体存储装置100。指令集cs1包含指示下位页的写入动作的指令cmd及地址add、以及下位页数据dat。指令集cs2包含指示上位页的写入动作的指令cmd及地址add、以及上位页数据dat。

[0086]

半导体存储装置100当接收到指令集cs1时,暂时从就绪状态转换为忙碌状态,并

将下位页数据dat存储在感测放大器140内的锁存电路(未图示)中。

[0087]

当接收到指令集cs2时,半导体存储装置100从就绪状态转换为忙碌状态,并将上位页数据dat与下位页数据dat分开地存储在感测放大器140内另一锁存电路(未图示)中。接着,半导体存储装置100基于指令集cs1及cs2内的地址add、以及下位页数据及上位页数据(以下简称为写入数据dat)开始写入动作。在写入动作中,定序器170反复执行编程动作及验证动作组。以下说明中,也将反复进行的编程动作及接在该编程动作之后继续执行的验证动作组称为编程循环。

[0088]

编程动作是使存储单元晶体管mt的阈值电压上升的动作。在编程动作中,连接于选择字线wl的单元组件cu内的多个存储单元晶体管mt根据各自阈值电压的高低,容许或禁止阈值电压上升。也就是说,定序器170将阈值电压未达与写入数据dat对应的状态的验证电压的存储单元晶体管mt设定为编程对象,将达到该验证电压的存储单元晶体管mt设定为禁止编程。

[0089]

在编程动作中,将编程电压vpgm施加于选择字线wl。电压vpgm是能够使存储单元晶体管mt的阈值电压上升的程度的高电压。当将编程电压vpgm施加于选择字线wl时,连接于选择字线wl且被设定为编程对象的存储单元晶体管mt的阈值电压上升。另一方面,对于连接于选择字线wl且被设定为禁止编程的存储单元晶体管mt,例如通过将包含该存储单元晶体管mt的nand串ns控制在浮动状态,抑制其阈值电压上升。当编程动作结束时,定序器170随后移行到验证动作。

[0090]

验证动作是判定作为写入对象的存储单元晶体管mt的阈值电压是否达到与写入数据dat对应的状态的验证电压vcgv的处理。在验证动作中,可以根据因编程动作引起的阈值电压的上升,适当变更所要使用的验证电压vcgv。例如,在第1次编程循环中的验证动作中,使用验证电压av,判定被写入“a”状态的存储单元晶体管mt的阈值电压是否达到验证电压av。另外,在第2次以后的编程循环中的验证动作中,可以依次施加多个验证电压(例如av及bv)。

[0091]

将被判定为达到与写入数据dat对应的状态的验证电压vcgv的存储单元晶体管mt判定为通过验证动作。定序器170针对“a”状态~“c”状态的每个状态,对未通过验证动作(失败)的存储单元晶体管mt的数量进行计数,从而判定各状态的写入动作是否已完成。

[0092]

以上所说明的编程动作及验证动作组与1次编程循环对应。每反复进行一次编程循环,编程电压vpgm便上升指定的上升量dvpgm1。也就是说,施加于选择字线wl的编程电压vpgm根据所执行的编程循环的次数提高。

[0093]

每当反复进行编程循环时,定序器170便判定例如未通过验证动作的存储单元晶体管mt的数量是否低于指定的数量。如果检测到未通过验证动作的存储单元晶体管mt的数量低于指定的数量,定序器170便结束写入动作,使半导体存储装置100从忙碌状态转换为就绪状态。当写入动作结束时,对连接于选择字线wl的单元组件cu写入2页的数据。图示的期间tprog与执行写入动作的期间对应。期间tprog是表示写入动作完成速度的指标,优选为较短。

[0094]

1.2.2插入动作

[0095]

第1实施方式的半导体存储装置能够中断正在执行的写入动作并插入执行另一处理。以下说明中,将该另一处理称为“插入动作”。插入动作例如包括读出动作、及将1比特数

据写入到存储单元晶体管mt的写入动作等。

[0096]

图5是用来说明第1实施方式的插入动作的时序图。图5中,以时间序列表示在写入动作中执行插入动作的情况下的信号i/o及rbn的一例。此外,图5所示的状态sts示意性地表示在该时点正在执行的动作。例如,在图5中,正在执行编程动作的状态sts表示为“p”,正在执行验证动作的状态sts表示为“v”。

[0097]

如图5所示,存储器控制器200将指令集wcs发送到半导体存储装置100。当接收到指令集wcs时,半导体存储装置100从就绪状态转换为忙碌状态,开始写入动作。

[0098]

接着,存储器控制器200对正在执行写入动作而处于忙碌状态的半导体存储装置100发送暂停指令xxh。暂停指令xxh是指示暂时中断正在执行的处理的指令,可以在任意时间点发送到半导体存储装置100。当接收到暂停指令xxh时,半导体存储装置100中断写入动作,从忙碌状态转换为就绪状态。图5所示的期间tstoprst对应于半导体存储装置100接收到暂停指令xxh后使写入动作中断而转换为就绪状态为止的期间。期间tstoprst是表示使半导体存储装置100成为能够执行插入动作的状态的速度的指标,优选为较短。

[0099]

当检测到半导体存储装置100已转换为就绪状态时,存储器控制器200将插入动作的指令集ics发送到半导体存储装置100。指令集ics例如包含具体指示插入到写入动作中的处理的指令cmd及地址add。另外,在插入动作为写入动作的情况下,包含写入数据dat。当接收到指令集ics时,半导体存储装置100从就绪状态转换为忙碌状态,开始插入动作。当插入动作结束时,半导体存储装置100从忙碌状态转换为就绪状态,并通知存储器控制器200插入动作结束。

[0100]

当检测到半导体存储装置100已转换为就绪状态时,存储器控制器200对半导体存储装置100发送恢复指令yyh。恢复指令yyh是指示正在中断的处理开始的指令。当接收到恢复指令yyh时,半导体存储装置100从就绪状态转换为忙碌状态,重新开始写入动作。写入动作例如从本应在中断前完成的处理之后立刻执行的处理重新开始。在图5的示例中,写入动作在验证动作中途中断,因此在重新开始后,执行该编程循环中本应执行的验证动作中的中断前未执行部分。有时会省略恢复指令yyh。

[0101]

此外,在图5的示例中,示出将暂停指令xxh与指令集ics分开发送到半导体存储装置100的情况,但并不限于此。例如,指令集ics也可以包含暂停指令xxh(指示插入动作的指令也可以兼作暂停指令xxh)。在此情况下,存储器控制器200能够对忙碌状态的半导体存储装置100发送包含暂停指令xxh的指令集ics。半导体存储装置100也可以当接收到包含暂停指令xxh的指令集ics时,中断写入动作,执行插入动作。

[0102]

另外,在图5的示例中,示出针对1次暂停指令xxh执行1次插入动作的情况,但并不限于此。例如,存储器控制器200也可以在第1次插入动作结束后,发送用来执行另一插入动作的指令集ics而并非恢复指令yyh。

[0103]

1.2.3将中断考虑在内的写入动作

[0104]

在第1实施方式的半导体存储装置中的写入动作中,根据有无因上述插入动作引起的中断,将重新开始后的写入动作的编程动作中的电压vpgm的上升量从dvpgm1变更。以下,对于将因插入动作引起的中断考虑在内的写入动作进行说明。

[0105]

图6是用来说明第1实施方式的存储器系统中将中断考虑在内的写入动作的流程图。

[0106]

如图6所示,在步骤st10中,定序器170判定在写入动作中是否接收到暂停指令。如上所述,暂停指令可以是用来使正在执行的动作中断的固有指令xxh,也可以是同时能够中断正在执行的动作的读出指令之类的通用指令。在判定为接收到暂停指令的情况下(步骤st10;是(yes)),处理进入步骤st30,在判定为未接收到暂停指令的情况下(步骤st10;否(no)),处理继续执行写入动作。

[0107]

在步骤st30中,定序器170根据暂停指令,使写入动作中断。半导体存储装置100转换为就绪状态,处于能够执行插入动作的状态。

[0108]

在步骤st50中,定序器170执行插入动作。

[0109]

在步骤st70中,定序器170在插入动作结束后,重新开始写入动作。

[0110]

在步骤st90中,定序器170将写入动作重新开始后第n次为止的编程动作中的编程电压vpgm的上升量从dvpgm1变更为dvpgm2(数n为1以上的整数)。上升量dvpgm2是小于上升量dvpgm1的正量(0<dvpgm2<dvpgm1)。伴随于此,行解码器120在步骤st70中的写入动作重新开始后所执行的编程动作中最初的第n次为止的编程动作中,将上升量变更为dvpgm2所得的编程电压vpgm施加于选择字线wl。

[0111]

在重新开始写入动作后第(n 1)次以后的编程动作中,所述上升量的变更设定解除,上升量变成dvpgm1。此外,数n也可以设定为写入动作中的编程循环的上限值。在此情况下,一旦将上升量变更为dvpgm2,便维持该值直到写入动作结束为止。

[0112]

由上,将中断考虑在内的写入动作结束。

[0113]

图7是用来说明第1实施方式的存储器系统中将中断考虑在内的写入动作的时序图,与图6对应。图7中,示出在图中的第2次编程循环的验证动作中途(更具体来说,施加验证电压av的期间与施加验证电压bv的期间之间)执行插入动作的情况。另外,图7中,示出在图6的步骤st90中设定n=1的情况。此外,在以下说明中,为了便于说明,将“图中的第x次编程循环”简单记载为“第x次编程循环”。

[0114]

如图7所示,在写入动作中断前最后的编程动作中,编程电压vpgm从写入动作中断前最后第2个编程动作的编程电压vpgm以上升量dvpgm1上升。接着,当写入动作中断并执行插入动作时,定序器170将写入动作重新开始后最初的编程动作中的编程电压vpgm的上升量变更为dvpgm2。由此,写入动作重新开始后最初的编程动作的编程电压vpgm从写入动作中断前最后的编程动作的编程电压vpgm以上升量dvpgm2上升。此后,写入动作重新开始后最初第2个编程动作的编程电压vpgm从写入动作重新开始后最初的编程动作的编程电压vpgm以上升量dvpgm1上升。

[0115]

通过以如上方式动作,在重新开始后立刻进行的编程动作中,能够将编程电压vpgm的上升量抑制得低于通常的上升量dvpgm1。

[0116]

1.3本实施方式的效果

[0117]

根据第1实施方式,定序器170在写入动作中断的情况下,在重新开始后的编程动作中,将最初的第n次为止的编程电压的上升量从dvpgm1变更为dvpgm2,所述dvpgm2是小于dvpgm1的正数。由此,能够抑制写入动作劣化且执行插入动作。

[0118]

另外,存储单元晶体管mt的阈值电压因编程动作上升之后,存在经过某一段时间后下降的情况。

[0119]

图8是用来说明比较例的写入动作中的存储单元晶体管的阈值电压变化的示意

图。图9是用来说明第1实施方式的写入动作中的存储单元晶体管的阈值电压变化的示意图。在图8及图9的示例中,示出被写入“a”状态的预定的一群存储单元晶体管mt的阈值电压分布。在图8的示例中,示出无论写入动作有无中断,编程电压vpgm均以上升量dvpgm1升高的情况,在此方面与图9不同。

[0120]

如图8(a)所示,通过某编程循环中的编程动作,对选择字线wl施加基于上升量dvpgm1的编程电压vpgm。由此,该一群存储单元晶体管mt的阈值电压上升到超过验证电压av的程度。

[0121]

然而,定序器170如果在接在该编程动作之后继续执行的预定的验证动作开始前接收到暂停指令,便中断写入动作,执行插入动作。由此,执行验证动作之前会经过某一段时间,从而该一群存储单元晶体管mt的阈值电压会下降。因此,该一群存储单元晶体管mt中阈值电压相对较低部分的阈值电压会变得低于验证电压av。

[0122]

因此,如图8(b)所示,在插入动作结束后重新开始的写入动作中的验证动作中,将阈值电压处于低于验证电压av的阈值电压分布α中的存储单元晶体管mt判定为验证动作失败。

[0123]

伴随于此,如图8(c)所示,在上述验证动作之后继续的编程动作中,处于该阈值电压分布α中的存储单元晶体管mt被设定为编程对象。因此,处于阈值电压分布α中的存储单元晶体管mt使阈值电压基于上升量dvpgm1上升,形成新的阈值电压分布β。根据上升量dvpgm1的大小,阈值电压的上升量有可能变得过大,因此存在形成分散范围较窄的阈值电压分布的方面欠佳的情况。

[0124]

根据第1实施方式,如图9(a)及图9(b)所示,因伴随着插入动作的写入动作中断导致阈值电压下降,从而产生验证动作失败的存储单元晶体管mt,在此方面与比较例相同。然而,如图9(c)所示,在重新开始后的编程动作中,将编程电压vpgm的上升量变更为小于dvpgm1的dvpgm2。

[0125]

由此,处于阈值电压分布α中的存储单元晶体管mt的阈值电压的上升量比编程电压vpgm的上升量为dvpgm1的情况小。因此,由基于上升量dvpgm2的编程电压vpgm形成的新的阈值电压分布γ不会使阈值电压分布整体的分散范围增加。因此,能够形成分散范围更窄的阈值电压分布,从而能够降低之后要执行的读出动作中误读出的可能性。

[0126]

另外,基于上升量dvpgm2的编程动作虽然与基于上升量dvpgm1的编程动作相比阈值电压的上升量较小,但能够与上升量为0的编程动作相比使阈值电压上升。由此,能够与使阈值电压完全不上升的情况相比,缩短写入动作完成为止的时间(期间tprog)。

[0127]

2.第2实施方式

[0128]

其次,对第2实施方式进行说明。在第1实施方式中,对如下情况进行了说明:基于写入动作是否中断,判定是否需要执行针对编程动作后的阈值电压下降的应对方法。在第2实施方式中,对于如下情况进行说明:进一步基于中断中所执行的插入动作是否满足条件的判定结果,判定是否需要执行针对编程动作后的阈值电压下降的应对方法。以下,对于与第1实施方式同等的构成及动作省略其说明,主要对于与第1实施方式不同的构成及动作进行说明。

[0129]

2.1将中断考虑在内的写入动作

[0130]

图10是用来说明第2实施方式的存储器系统中将中断考虑在内的写入动作的流程

图,与第1实施方式中的图6对应。图10中,在图6中的步骤st70与步骤st90之间追加步骤st80。

[0131]

如图10所示,步骤st10~步骤st70中的处理与图6中的处理同等,因此省略说明。

[0132]

在步骤st80中,定序器170判定插入动作是否满足条件。在判定插入动作满足条件的情况下(步骤st80;是),处理进入步骤st90。在判定插入动作不满足条件的情况下(步骤st80;否),处理继续进行写入动作而不使编程动作的上升量从dvpgm1变更。

[0133]

在步骤st90中,定序器170使写入动作重新开始后第n次为止的编程动作中的编程电压vpgm的上升量从dvpgm1变更为dvpgm2。

[0134]

由上,将中断考虑在内的写入动作结束。

[0135]

此外,对于步骤st80中所判定的与插入动作相关的条件可以适用各种条件。以下,对其具体例进行叙述。

[0136]

2.1.1插入动作的实施时间点

[0137]

首先,参照图11所示的流程图,对于作为第1例的将插入动作的实施时间点作为条件的情况进行说明。在图11的示例中,示出步骤st81作为具体表示图10中的步骤st80的第1例。

[0138]

如步骤st81所示,定序器170判定插入动作是否在某编程循环中从编程动作结束到接在该编程动作之后继续进行的验证动作结束为止的期间d内中断。在写入动作在期间d内中断的情况下(步骤st81;是),处理进入步骤st90。在写入动作在期间d内未中断的情况下(步骤st81;否),处理继续执行写入动作而不使编程动作的上升量从dvpgm1变更。

[0139]

图12是用来说明第2实施方式的第1例的存储器系统中将中断考虑在内的写入动作的时序图。

[0140]

在图12(a)的示例中,插入动作在第2次编程循环中的所有验证动作结束后且第3次编程循环中的编程动作开始之前执行。也就是说,在图12(a)的示例中,在期间d外的期间内中断写入动作。在此情况下,第2次编程循环中的验证动作在紧邻的上一编程动作结束后,迅速执行。因此,因第2次编程循环中的编程动作上升的阈值电压下降的现象不会对接在该编程动作之后继续进行的验证动作产生影响。也就是说,第2次编程循环中的验证动作中应通过的存储单元晶体管mt不会发生随着时间的经过被判定为失败的现象。因此,第3次编程循环中的编程动作的编程电压vpgm的上升量不从dvpgm1变更。

[0141]

另一方面,图12(b)的示例中,在第2次编程循环的验证动作中,在施加验证电压av的期间与施加验证电压bv的期间之间执行插入动作。也就是说,在图12(b)的示例中,在期间d内中断写入动作。在此情况下,第2次编程循环中的验证动作在紧邻的上一编程动作结束后到插入动作结束为止不会执行。因此,因第2次编程循环中的编程动作上升的阈值电压下降的现象会对接在该编程动作之后继续进行的验证动作产生影响。也就是说,第2次编程循环中的验证动作中应通过的存储单元晶体管mt会发生随着时间的经过被判定为失败的现象。因此,第3次编程循环中的编程动作的编程电压vpgm的上升量从dvpgm1变更为dvpgm2。

[0142]

通过以如上方式动作,在写入动作伴随着插入动作的产生而中断的情况下,将执行该插入动作的时间点作为条件,能够判定是否应变更编程电压vpgm的上升量。

[0143]

2.1.2插入动作的期间长度

[0144]

其次,参照图13所示的流程图,对于作为第2例的将执行插入动作的期间长度作为条件的情况进行说明。在图13的示例中,示出步骤st81及st82作为具体表示图10中的步骤st80的第2例。

[0145]

步骤st81与图11中的该步骤同等,因此省略说明。

[0146]

如步骤st82所示,定序器170判定期间d(即,从插入动作紧邻的上一编程动作结束到插入动作紧邻的下一编程动作之前所执行的验证动作结束为止的期间)是否因包含插入动作而为阈值dth以上。具体来说,例如定序器170内的计数器171针对每个编程循环,对从编程动作结束到验证动作结束为止的期间d进行计数。定序器170将计数器171的计数值与指定的阈值dth进行比较,由此判定期间d的长度是否为阈值dth以上。阈值dth例如相当于因编程动作上升的存储单元晶体管mt的阈值电压随着时间的经过下降为止的期间。

[0147]

在期间d为阈值dth以上的情况下(步骤st82;是),处理进入步骤st90。在期间d小于阈值dth的情况下(步骤st82;否),处理继续执行写入动作而不使编程动作的上升量从dvpgm1变更。

[0148]

图14是用来说明第2实施方式的第2例的存储器系统中将中断考虑在内的写入动作的时序图。

[0149]

在图14(a)的示例中,在第2次编程循环中的验证动作中施加电压av的期间结束后且施加电压bv的期间开始前,执行1次插入动作。也就是说,在图14(a)的示例中,在期间d内,中断写入动作执行1次插入动作。在此情况下,期间d的长度小于阈值dth,从而判定因第2次编程循环中的编程动作上升的阈值电压下降的现象不会对接在该编程动作之后继续进行的验证动作(在施加电压bv的期间内也如此)产生影响。也就是说,第2次编程循环中的验证动作中应通过的存储单元晶体管mt不会发生随着时间的经过被判定为失败的现象。因此,第3次编程循环中的编程动作的编程电压vpgm的上升量不从dvpgm1变更。

[0150]

另一方面,图14(b)的示例中,在第2次编程循环的编程动作结束后到验证动作开始前,执行1次插入动作。进而,在第2次编程循环的验证动作中施加电压av的期间结束后且施加电压bv的期间开始前,再执行1次插入动作。也就是说,在期间d内执行2次插入动作。在此情况下,期间d的长度成为阈值dth以上,从而判定因第2次编程循环中的编程动作上升的阈值电压下降的现象会对接在该编程动作之后继续进行的验证动作(特别是施加电压bv的期间中)产生影响。也就是说,第2次编程循环中的验证动作中应通过的存储单元晶体管mt会发生随着时间的经过被判定为失败的现象。因此,第3次编程循环中的编程动作的编程电压vpgm的上升量从dvpgm1变更为dvpgm2。

[0151]

通过以如上方式动作,将会对验证动作的结果产生影响的期间中所执行的插入动作的长度作为条件,能够判定是否应变更编程电压vpgm的上升量。

[0152]

此外,在上述示例中,对于通过计数器171的计数值计测期间d的长度的情况进行了叙述,但并不限于此。例如,期间d的长度也可以通过插入动作在期间d内执行的次数来进行计测。在将该情况适用于图14的示例的情况下,阈值dth变成“2次”。

[0153]

2.1.3插入动作的种类

[0154]

其次,参照图15所示的流程图,对作为第3例的将插入动作的种类作为条件的情况进行说明。在图15的示例中,示出步骤st81及st83作为具体表示图10中的步骤st80的第3例。

[0155]

步骤st81与图11中的该步骤同等,因此省略说明。

[0156]

如步骤st83所示,定序器170判定是否基于从存储器控制器200发送的指令中的指定的指令执行插入动作。在基于指定的指令执行插入动作的情况下(步骤st83;是),处理进入步骤st90。在基于指定的指令以外的指令执行插入动作的情况下(步骤st83;否),处理继续执行写入动作而不使编程动作的上升量从dvpgm1变更。

[0157]

指定的指令例如包括指示执行新的写入动作来作为插入动作的指令、指示执行抹除动作来作为插入动作的指令、及指示执行多个使用读出电压的读出动作来作为插入动作的指令。作为多次使用读出电压的读出动作的示例,例如列举:对存储着2比特数据的存储单元晶体管mt的上位页读出动作、或用来掌握单元组件cu中的阈值电压分布的跟踪动作、基于第1次读出动作的结果决定第2次读出动作中的读出电压的读出动作等。此外,无需将多个使用读出电压的读出动作全部设定为上述指定的指令,可以将与这些读出动作中的任意动作对应的指令设定为指定的指令。

[0158]

通过以如上方式动作,在执行需要相对较长时间的插入动作,例如假定期间d为阈值dth以上的情况下,能够将编程电压vpgm的上升量变更为dvpgm2。另外,在执行仅需要相对较短时间的插入动作,例如假定期间d小于阈值dth的情况下,能够不使编程电压vpgm的上升量从dvpgm1变更。

[0159]

2.1.4插入动作执行过程中的温度

[0160]

其次,参照图16所示的流程图,对于作为第4例的将执行插入动作过程中的半导体存储装置100的温度作为条件的情况进行说明。在图16的示例中,示出步骤st81及st84作为具体表示图10中的步骤st80的第4例。

[0161]

步骤st81与图11中的该步骤同等,因此省略说明。

[0162]

如步骤st84所示,定序器170判定插入动作时半导体存储装置100的温度t是否为阈值tth以上。具体来说,例如温度传感器180计测执行插入动作过程中的半导体存储装置100的温度t,并将与该温度t对应的温度信息传输到定序器170。定序器170基于该温度信息,判定温度t是否为指定的阈值tth以上。阈值tth例如与因编程动作上升的存储单元晶体管mt的阈值电压下降为止的期间显著缩短的温度对应。在判定温度t为阈值tth以上的情况下(步骤st84;是),处理进入步骤st90。在判定温度t小于阈值tth的情况下(步骤st84;否),处理继续执行写入动作而不使编程动作的上升量从dvpgm1变更。

[0163]

通过以如上方式动作,能够考虑阈值电压下降的时间依赖温度t的情况。也就是说,在执行插入动作过程中的温度t为容易发生阈值电压下降的阈值tth以上的情况下,能够将编程电压vpgm的上升量变更为dvpgm2。另外,在执行插入动作过程中在温度t小于不易发生阈值电压下降的阈值tth的情况下,能够不使编程电压vpgm的上升量从dvpgm1变更。

[0164]

2.2本实施方式的效果

[0165]

根据第2实施方式,定序器170基于插入动作是否满足条件,判定是否将编程电压vpgm的上升量从dvpgm1变更为dvpgm2。由此,能够更详细地判定阈值电压下降的影响对重新开始后立刻进行的验证动作产生影响的情况及不产生影响的情况。因此,能够抑制步骤st90所执行的实例(即,编程电压vpgm的上升量变小的实例)增加。因而,能够抑制因编程动作产生的阈值电压的上升量下降,从而能够缩短编程动作的执行期间tprog。

[0166]

3.第3实施方式

[0167]

其次,对第3实施方式进行说明。在第2实施方式中,对于如下情况进行了说明,即,考虑伴随着满足条件的插入动作的写入动作的中断所造成的影响,使重新开始后至少最初的编程动作中的编程电压vpgm以更小的上升量上升,但并不限于此。在第3实施方式中,对于如下情况进行说明,即,考虑伴随着满足条件的插入动作的写入动作的中断所造成的影响,不使重新开始后最初的编程动作中的编程电压vpgm上升。以下,对于与第2实施方式同等的构成及动作省略其说明,主要对于与第2实施方式不同的构成及动作进行说明。

[0168]

3.1将中断考虑在内的写入动作

[0169]

图17是用来说明第3实施方式的存储器系统中将中断考虑在内的写入动作的流程图,与第2实施方式中的图10对应。图17中,执行步骤st91代替图10中的步骤st90。

[0170]

如图17所示,步骤st10~步骤st80中的处理与图10中的处理同等,因此省略说明。此外,对于步骤st80中所判定的适用于插入动作的条件,同样可以适用第2实施方式中所示的各种条件。

[0171]

在步骤st91中,定序器170不使写入动作重新开始后最初的编程动作中的编程电压vpgm从写入动作即将中断之前的编程动作中的编程电压vpgm上升。也就是说,定序器170使写入动作重新开始后最初的编程动作中的编程电压vpgm的上升量为0。

[0172]

此外,定序器170使写入动作重新开始后第2次以后的编程动作中的编程电压vpgm例如在每一编程循环中以上升量dvpgm1逐次上升。

[0173]

由上,将中断考虑在内的写入动作结束。

[0174]

图18是用来说明第3实施方式的存储器系统中将中断考虑在内的写入动作的时序图,与图17对应。在图18中,示出在第2次编程循环的验证动作中途执行满足条件的插入动作的情况。

[0175]

如图18所示,在写入动作中断前,定序器170设定上升量dvpgm1作为编程电压vpgm的上升量。当写入动作中断并执行满足条件的插入动作时,定序器170不使写入动作重新开始后最初的编程动作中的编程电压vpgm从即将中断之前的编程动作的编程电压vpgm上升。由此,在第3次编程循环中的编程动作中,将与第2次编程循环中的编程动作相同高低的编程电压vpgm施加于选择字线wl。此后,在第4次以后的编程循环中的编程动作中,将从第2次及第3次编程循环中的编程动作以上升量dvpgm1上升的编程电压vpgm施加于选择字线wl。

[0176]

3.2本实施方式的效果

[0177]

根据第3实施方式,定序器170基于插入动作是否满足条件,判定是否使重新开始后立刻进行的编程动作的编程电压vpgm上升。定序器170在预想到因写入动作中断导致存储单元晶体管mt的阈值电压下降的情况下,不使重新开始后立刻进行的编程动作的编程电压vpgm上升。由此,在重新开始后立刻进行的最初的编程动作中,能够使存储单元晶体管mt的阈值电压仅上升到与即将中断之前的编程动作相同的程度。也就是说,定序器170能够执行重新开始后立刻进行的最初的编程动作,作为用来使阈值电压恢复到即将中断之前的编程动作执行后的状态的编程动作。因此,通过重新开始后立刻进行的最初的编程动作,能够抑制阈值电压下降的存储单元晶体管mt的阈值电压过度上升。因此,能够抑制写入动作的性能劣化。

[0178]

另外,在插入动作不满足条件的情况下,定序器170在重新开始后立刻进行的最初的编程动作中,使编程电压vpgm以上升量dvpgm1上升。由此,在预想到插入动作无助于存储

单元晶体管mt的阈值电压下降的情况下,能够使存储单元晶体管mt的阈值电压从重新开始后立刻进行的最初的编程动作迅速上升。因此,能够抑制期间tprog的增加。

[0179]

4.第4实施方式

[0180]

其次,对第4实施方式进行说明。在第2实施方式及第3实施方式中,对于如下情况进行了说明,即,考虑伴随着满足条件的插入动作的写入动作的中断所造成的影响,使重新开始后至少最初的编程动作中的编程电压vpgm的上升量从dvpgm1变更,但并不限于此。在第4实施方式中,对于如下情况进行说明,即,考虑伴随着满足条件的插入动作的写入动作的中断所造成的影响,使重新开始后最初的验证动作中的验证电压vcgv下降。以下,对于与第2实施方式同等的构成及动作省略其说明,主要对于与第2实施方式不同的构成及动作进行说明。

[0181]

4.1将中断考虑在内的写入动作

[0182]

图19是用来说明第4实施方式的存储器系统中将中断考虑在内的写入动作的流程图,与第2实施方式中的图10对应。在图19中,执行步骤st92代替图10中的步骤st90。

[0183]

如图19所示,步骤st10~步骤st80中的处理与图10中的处理同等,因此省略说明。此外,对于步骤st80中所判定的适用于插入动作的条件,同样可以适用第2实施方式中所示的各种条件。

[0184]

在步骤st92中,行解码器120在写入动作重新开始后最初的验证动作中,将低于验证电压vcgv的验证电压vcgvm施加于选择字线wl(vcgvm<vcgv)。验证电压vcgvm是相对于验证电压av~cv的各电压设定的。也就是说,验证电压avm低于验证电压av。验证电压bvm低于验证电压bv且高于验证电压av(av<bvm<bv)。验证电压cvm低于验证电压cv且高于验证电压bv(bv<cvm<cv)。

[0185]

此外,行解码器120在写入动作重新开始后第2次以后的验证动作中,对选择字线wl施加验证电压vcgv。

[0186]

由上,将中断考虑在内的写入动作结束。

[0187]

图20是用来说明第4实施方式的存储器系统中将中断考虑在内的写入动作的时序图,与图19对应。图20中,在图中的所有编程循环中,判定被写入“a”状态及“b”状态的存储单元晶体管mt是否通过验证动作。另外,在图20中,示出在第2次编程循环的验证动作中途执行满足条件的插入动作的情况。

[0188]

如图20所示,在图中的第2次编程循环的验证动作中,在写入动作中断前,对选择字线wl施加电压av。由此,感测放大器140使用电压av(vcgv)判定被写入“a”状态的存储单元晶体管mt是否通过验证动作。

[0189]

另一方面,当写入动作中断并执行满足条件的插入动作时,对选择字线wl施加电压bvm。由此,感测放大器140使用电压bvm(vcgvm)判定被写入“b”状态的存储单元晶体管mt是否通过验证动作。

[0190]

这样一来,在同一编程循环中的验证动作中途写入动作中断的情况下,当插入动作满足条件时,在重新开始后立刻进行的验证动作中,也对选择字线wl施加验证电压vcgvm。

[0191]

接着,在重新开始后第2次以后的验证动作中,对选择字线wl施加验证电压vcgv。

[0192]

4.2本实施方式的效果

[0193]

根据第4实施方式,定序器170基于插入动作是否满足条件,判定是否使重新开始后立刻进行的验证动作的验证电压从vcgv下降。行解码器120在预想到因写入动作中断导致存储单元晶体管mt的阈值电压下降的情况下,在重新开始后立刻进行的最初的验证动作中,施加低于验证电压vcgv的vcgvm。由此,感测放大器140能够判定阈值电压下降的存储单元晶体管mt也通过验证动作。因此,定序器170能够判定为,无需使在写入动作即将中断前阈值电压上升到通过验证动作的程度且到执行验证电压之前阈值电压下降的存储单元晶体管mt的阈值电压在重新开始后立刻进行的编程动作中进一步上升。因此,能够抑制因重新开始后立刻进行的最初的编程动作,使阈值电压下降的存储单元晶体管mt的阈值电压过度上升。因此,能够抑制写入动作的性能劣化。

[0194]

另外,在插入动作不满足条件的情况下,定序器170在重新开始后立刻进行的最初的验证动作中,将验证电压vcgv施加于选择字线wl。由此,在预想到插入动作无助于存储单元晶体管mt的阈值电压下降的情况下,通过通常的验证电压vcgv,即可判定存储单元晶体管mt的阈值电压是否达到所需状态。

[0195]

5.变化例等

[0196]

此外,上述第1实施方式至第4实施方式可以进行各种变化。

[0197]

例如,在上述第2实施方式及第3实施方式中,对于如下情况进行了说明,即,基于是否满足1个条件,判定是否将编程电压vpgm的上升量从dvpgm1变更为另一上升量(dvpgm2或0),但并不限于此。例如,编程电压vpgm的上升量也可以基于多个条件,从dvpgm1变更为多个上升量中的任一个。具体来说,例如定序器170也可以在插入动作满足第1个条件及第2个条件中的任一条件的情况下,判定将编程电压vpgm的上升量从dvpgm1变更为0,在插入动作满足第1个条件且不满足第2个条件的情况下,判定将编程电压vpgm的上升量从dvpgm1变更为dvpgm2,在插入动作既不满足第1个条件又不满足第2个条件的情况下,判定不将编程电压vpgm的上升量从dvpgm1变更。对于第4实施方式中的验证电压vcgv的下降量,也可以适用与上述编程电压vpgm的上升量同等的变化。由此,能够根据存储单元晶体管mt的阈值电压下降的程度,更精密地控制阈值电压分布的形状。

[0198]

在此情况下,第2个条件也可以是第1个条件所包含的更严格的条件。例如,定序器170也可以适用“期间d为阈值dth以上”作为第1个条件,适用“期间d为阈值dth2(>dth)以上”作为第2个条件。另外,例如定序器170也可以适用“温度t为阈值tth以上”作为第1个条件,适用“温度t为阈值tth2(>tth)以上”作为第2个条件。

[0199]

另外,在上述第2实施方式中,对于预先规定了重新开始后将编程电压vgpm的上升量从dvpgm1变更为dvpgm2的编程动作的次数n的情况进行了说明,但并不限于此。例如,次数n也可以根据多个条件阶段性地决定。

[0200]

例如,定序器170也可以在满足“期间d为阈值dth以上且小于阈值dth2(>dth)”的情况下,适用次数n1,在满足“期间d为阈值dth2以上”的情况下,适用次数n2(>n1)。另外,例如定序器170也可以在满足“温度t为阈值tth以上且小于阈值tth2(>tth)”的情况下,适用次数n1,在满足“温度t为阈值tth2以上”的情况下,适用次数n2。

[0201]

此外,所述实施方式的一部分例如可以如以下附记那样记载,但并不限于以下。

[0202]

[附记1]

[0203]

一种半导体存储装置,其具备:

[0204]

存储单元,连接于字线;以及

[0205]

控制电路,构成为执行反复进行编程循环的写入动作,所述编程循环包括编程动作、及接在所述编程动作之后继续进行的验证动作;且

[0206]

所述控制电路构成为,在所述写入动作中,

[0207]

在使所述写入动作中断时执行第1动作且所述第1动作不满足条件的情况下,在使所述写入动作重新开始后立刻进行的验证动作中,对所述字线施加第1电压,

[0208]

在所述第1动作满足所述条件的情况下,在使所述写入动作重新开始后立刻进行的验证动作中,对所述字线施加低于所述第1电压的第2电压。

[0209]

[附记2]

[0210]

根据附记1所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括在所述编程循环中从所述编程动作结束到所述验证动作结束为止的第1期间内执行所述第1动作。

[0211]

[附记3]

[0212]

根据附记2所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括所述第1期间的长度超过第1阈值。

[0213]

[附记4]

[0214]

根据附记1所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括执行所述第1动作的第2期间的长度超过第2阈值。

[0215]

[附记5]

[0216]

根据附记1所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括在所述编程循环中从所述编程动作结束到所述验证动作结束为止的第1期间内执行的所述第1动作的次数超过第3阈值。

[0217]

[附记6]

[0218]

根据附记1所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括基于来自存储器控制器的指定的指令执行所述第1动作。

[0219]

[附记7]

[0220]

根据附记1所述的半导体存储装置,其中所谓所述第1动作满足所述条件,包括执行所述第1动作期间的温度超过第4阈值。

[0221]

对本发明的若干实施方式进行了说明,但这些实施方式是作为示例提出的,并非意图限定发明范围。这些实施方式可以通过其他各种方式实施,可以在不脱离发明主旨的范围内,进行各种省略、置换、变更。这些实施方式或其变化包含在发明范围或主旨中,且同样包含在权利要求书所记载的发明及其均等的范围内。

[0222]

[符号的说明]

[0223]1ꢀꢀꢀꢀꢀꢀꢀꢀ

存储器系统

[0224]

100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nand闪速存储器

[0225]

110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储单元阵列

[0226]

120

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

行解码器

[0227]

130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

驱动器

[0228]

140

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

感测放大器

[0229]

150

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

地址寄存器

[0230]

160

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

指令寄存器

[0231]

170

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

定序器

[0232]

171

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

计数器

[0233]

180

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

温度传感器

[0234]

200

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储器控制器

[0235]

210

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机接口电路

[0236]

220

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

ram

[0237]

230

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

cpu

[0238]

240

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

缓冲存储器

[0239]

250

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

nand接口电路

[0240]

260

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

ecc电路

[0241]

300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

主机装置。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。