1.本发明涉及存储器技术领域,特别涉及一种磁性随机存储器及其读写方法。

背景技术:

2.磁性随机存储器(magnetic random access memory,mram)是一种新的内存和存储技术,可以像sram/dram一样快速随机读写,还可以像flash闪存一样在断电后永久保留数据。

3.请参考图6,现有的常规磁性随机存储器包括:主要由多个存储单元cell排列成的存储阵列1,一字线解码器2,用以设定所述字线wl上的电位;一位线解码器3,用以设定所述位线bl上的电位;一源线解码器4,用以设定所述源线sl上的电位。其中,所述存储阵列1由多条字线wl、多条位线bl以及多条源线sl控制,每个存储单元cell由一个磁性隧道结mjt和一个mos管组成。每一个存储单元需要连接三根线:mos管的栅极连接到芯片的字线wl,负责接通或切断这个单元;mos管的一极(源极或漏极)连在源线sl上,mos管的另一极(漏极或源极)和磁性隧道结的一极相连,磁性隧道结的另一极连在位线bl上。具体地,所述存储阵列1中,连续三条字线标记为wln-1、wln、wln 1,连续三条位线标记为bln-1、bln、bln 1,连续三条源线线标记为sln-1、sln、sln 1。从图6中可以看出,上下相邻的存储单元共享同一字线wl,但不共享同一源线sl和同一位线bl,即上下相邻的两存储单元的源线sl和位线bl均相互隔离开。

4.请继续参考图6,该磁性随机存储器的读写方法是在需要读或写的存储单元所连接的所述字线、位线和源线上施加相应的电位,例如假设字线wln、位线bln和源线sln三条线确定的存储单元为需要读或写的存储单元,定义为celln,则在所连接的字线wln、位线bln和源线sln上施加相应的电位。

5.上述这种磁性随机存储器,由于上下相邻的存储单元不共享位线和源线,单个mram存储单元的面积较大,无法满足高存储密度的mram的需求。

6.另外,随着mram技术不断进步,出现了一些高存储密度的mram,但这些高存储密度的mram在读写过程中存在误读写的问题。

7.因此,如何将mram存储单元进一步做小,以提高mram的密度,并防止高存储密度的mram的误读写,已经成为本领域技术人员亟待解决的技术问题之一。

技术实现要素:

8.本发明的目的在于提供一种磁性随机存储器及其读写方法,将mram存储单元进一步做小,以提高mram的密度,并防止高存储密度的mram的误读写。

9.为解决上述技术问题,本发明提供一种磁性随机存储器,包括:主要由多个存储单元排列成的存储阵列,所述存储阵列由多条字线、多条位线以及多条源线控制,每个存储单元均具有磁性隧道结;所述磁性随机存储器在进行读或写操作时,所述存储阵列中与需要读或写的存储单元相邻的非读写存储单元所连接的源线和位线等电位。

10.可选地,与所述需要读或写的存储单元相邻的非读写存储单元包括:与所述需要读或写的存储单元共享同一字线。

11.可选地,一部分所述非读写存储单元的位线和源线等电位且与所述需要读或写的存储单元的位线的电位相等;另一部分所述非读写存储单元的位线和源线等电位且与所述需要读或写的存储单元的源线的电位相等。

12.可选地,所述磁性随机存储器包括:

13.半导体衬底,所述半导体衬底中设置有呈条状且沿第一方向和第二方向排列的多个有源区,每个所述有源区沿第三方向延伸,所述第二方向和所述第一方向垂直,所述第三方向与所述第一方向和第二方向均相交;

14.所有的所述字线沿第一方向排布在所述半导体衬底上,且每条所述字线沿第二方向延伸并跨设在多个所述有源区上,每条所述字线将相应的所述有源区分为源极区和漏极区;

15.每条所述源线通过第一金属层形成并连接相应的所述源极区;

16.每个所述磁性隧道结底部通过相应的第二金属层连接相应的所述漏极区,顶部连接第三金属层,所述第三金属层用于形成相应的所述位线;

17.其中,每个所述有源区和设置在所述有源区上方的所述字线形成相应的mos管,所述有源区处形成的相应的mos管和所述漏极区上方相应的所述磁性隧道结组成一个存储单元。

18.可选地,所述磁性随机存储器包括:

19.半导体衬底,所述半导体衬底中设置有多个沿第一方向延伸呈条状并沿第二方向排列的有源区;

20.所有的所述字线沿第一方向排布在所述半导体衬底上,且每条所述字线沿第二方向延伸并跨设在多个所述有源区上,每条所述字线将相应的所述有源区分为源极区和漏极区;

21.每条所述源线通过第一金属层形成并连接相应的所述源极区;

22.每个所述磁性隧道结底部通过相应的第二金属层连接相应的所述漏极区,顶部连接第三金属层,所述第三金属层用于形成相应的位线;

23.其中,每个所述有源区和设置在所述有源区上方的所述字线形成相应的mos管,所述有源区处形成的相应的mos管和所述漏极区上方相应的所述磁性隧道结组成一个存储单元。

24.可选地,每个所述存储单元最少仅具有一个mos管。

25.可选地,除所述磁性随机存储器的阵列边界上所述存储单元以外的每个存储单元的mos管的源极区和漏极区与周围相邻的存储单元共享,每个所述存储单元的面积为4f2,其中,f是特征尺寸。

26.可选地,所述第一方向和所述第三方向的夹角包括但不仅限于45度。

27.可选地,所述磁性随机存储器还包括:一字线解码器,用以设定所述字线上的电位;一位线解码器,用以设定所述位线上的电位;一源线解码器,用以设定所述源线上的电位。

28.基于同一发明构思,本发明还提供一种磁性随机存储器的读写方法,包括:

29.设定需要读或写的存储单元所连接的所述字线、位线和源线上的电位;

30.确定与所述需要读或写的存储单元相邻的非读写存储单元,并将所述非读写存储单元所连接的源线或位线的电位设定为与所述读或写的存储单元所连接的源线或位线的电位相等;

31.对所述需要读或写的存储单元进行读或者写操作。

32.与现有技术相比,本发明的磁性随机存储器及其读写方法,具有以下有益效果:

33.1、所述磁性随机存储器在进行读或写操作时,所述存储阵列中与需要读或写的存储单元相邻的非读写存储单元所连接的源线和位线等电位,由此,就算相应的字线将与需要读或写的存储单元相邻的非读写存储单元的mos管开启,由于非读写存储单元的mos管的源极区与漏极区等电位,该mos管也不会有电流流过,所以不会有误读与误写的问题。

34.2、所述磁性随机存储器中的有源区为在一个方向上连续延伸为条状的结构,且在字线延伸方向上共享同一字线的相邻两个存储单元可以进一步共享同一源线或同一条位线,因此在占用相同衬底面积前提下,能够有效利用衬底面积空间,实现更小的存储单元的特征尺寸和更高的存储密度,芯片成本更低。

35.3、可以实现单元面积为4f2(f为特征尺寸)的密堆积存储阵列,提高存储密度和器件集成度。

附图说明

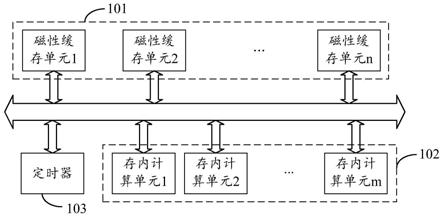

36.图1是本发明一实施例的磁性随机存储器的等效电路结构示意图;

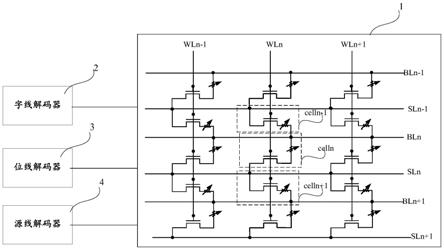

37.图2是本发明一实施例的磁性随机存储器的版图结构的一种示例示意图;

38.图3是沿图2所示的磁性随机存储器中的xx’线的一种剖面结构示意图(省略了层间介质层等结构,且源线和位线平行且在纵向上不发生重叠);

39.图4是沿图2所示的磁性随机存储器中的xx’线的另一种剖面结构示意图(省略了层间介质层等结构,且源线和位线在纵向上有重叠,且可以是异面相交的);

40.图5a~图5c是本发明一实施例的磁性随机存储器的版图结构的另外三种示例示意图;

41.图6是现有的一种典型的磁性随机存储器的等效电路结构示意图。

具体实施方式

42.以下结合附图和具体实施例对本发明提出的技术方案作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。本文中“和/或”的含义是二选一或二者兼具。

43.请参考图1,本发明一实施例提供一种磁性随机存储器,包括:主要由多个存储单元cell排列成的存储阵列1,所述存储阵列1由多条字线wl、多条位线bl以及多条源线sl控制,每个存储单元cell由一个磁性隧道结mjt和一个mos管组成,每一个存储单元cell需要连接三根线:mos管的栅极连接到芯片的字线wl,负责接通或切断这个单元;mos管的一极(源极或漏极)连在源线sl上,mos管的另一极(漏极或源极)和磁性隧道结的一极相连,磁性隧道结的另一极连在位线bl上。

44.所述磁性随机存储器在进行读或写操作时,所述存储阵列中与需要读或写的存储单元相邻的非读写存储单元所连接的源线sl和位线bl等电位,其中,与需要读或写的存储单元相邻的非读写存储单元为与需要读或写的存储单元共享同一字线wl的所有存储单元,也可以说是与需要读或写的存储单元共享同一字线wl的一串存储单元。需要说明的,图1所示的所述存储阵列1中,虽然仅仅示出了连续三条字线wln-1、wln、wln 1、连续三条位线bln-1、bln、bln 1、连续三条源线线sln-1、sln、sln 1及其连接的mos晶圆管和磁隧道结,但是本领域技术人员能够预料到本实施例的存储阵列1应该是沿图1的上下左右四个方向进行相应的有规律的延展。

45.本实施例中,所述磁性随机存储器还包括:一字线解码器2,用以设定所述字线wl上的电位;一位线解码器3,用以设定所述位线bl上的电位;一源线解码器4,用以设定所述源线sl上的电位。

46.请参考图1,本实施例的磁性随机存储器的读写方法,包括:

47.首先,设定需要读或写的存储单元所连接的所述字线、位线和源线上的电位。

48.接着,确定与所述需要读或写的存储单元相邻的非读写存储单元。具体地,存储阵列中的存储单元被分为三类:(1)需要读或写的存储单元;(2)与需要读或写的存储单元相邻的非读写存储单元,即与需要读或写的存储单元共享同一字线的那些存储单元;(3)其他无关的存储单元,即与需要读或写的存储单元不共享同一字线的那些存储单元。例如假设字线wln、位线bln和源线sln三条线确定的存储单元为需要读或写的存储单元,定义为celln,则与存储单元celln共享同一条字线wln的所有存储单元均为与需要读或写的存储单元celln相邻的非读写存储单元,这些非读写存储单元中包括字线wln、位线bln和源线sln-1三条线确定的存储单元(定义为celln-1),以及,字线wln、位线bln 1和源线sln确定的存储单元(定义为celln 1),其中,与需要读或写的存储单元celln与非读写存储单元celln-1不仅共享同一字线wln,还进一步共享同一位线bln,与需要读或写的存储单元celln与非读写存储单元celln 1不仅共享同一字线wln,还进一步共享同一源线sln。

49.然后,将每个所述非读写存储单元所连接的源线和位线设定为等电位。具体地,继续以上述的字线wln、位线bln和源线sln三条线确定的存储单元为需要读或写的存储单元celln,并假设存储阵列1具有m条字线wl0~wlm-1、k条位线bl0~blk-1以及k条源线sl0~slk-1,0≤n≤m-1且0≤n≤k-1,m、n、k均为大于1的整数,则将与需要读或写的存储单元celln共享同一字线wln的所有存储单元的位线和源线均设为等电位,此时,源线sl0~sln-1以及位线bl0~bln-1的电位均等于位线bln的电位,源线sln 1~slk-1以及位线bln 1~blk-1的电位均等于源线sln的电位。也就是说,与需要读或写的存储单元celln相邻的所有非读写存储单元(即与需要读或写的存储单元celln共享同一字线wln的所有存储单元)中,一部分所述非读写存储单元(即在图1中沿着wln且布设在位线bln以上的存储单元)的位线和源线等电位且与所述需要读或写的存储单元celln的位线bln的电位相等;另一部分所述非读写存储单元即在图1中沿着wln且布设在源线sln以下的存储单元)的位线和源线等电位且与所述需要读或写的存储单元celln的源线sln的电位相等。具体地,在图1中,由wln、位线bln和源线sln-1三条线确定的存储单元celln-1所连接的位线bln和源线sln-1设为等电位,将字线wln、位线bln 1和源线sln确定的存储单元celln 1所连接的位线bln 1和源线sln设为等电位。其中,位线bln和源线sln的电位不同。

50.之后,按照上述设定来对所述需要读或写的存储单元进行读或者写操作。

51.由于在需要读或写的存储单元celln进行读或写时,即使其所连接的字线wln将与其共享该字线wln的各个与需要读或写的存储单元相邻的非读写存储单元的mos管开启,但是由于这些非读写存储单元所连接的位线bl和源线sl为等电位,即使得这些非读写存储单元的mos管的源极区和漏极区等电位,因此这些与需要读或写的存储单元相邻的非读写存储单元mos管中均不会有电流流过,即对需要读写的存储单元celln进行读或写时,不会造成对与之相邻且共享同一字线的非读写存储单元的误读写。请参考图1,存储单元celln读或写时,存储单元celln-1和存储单元celln 1的mos管开启,但是由于存储单元celln-1所连接位线bln和源线sln-1等电位,存储单元celln 1所连接位线bln 1和源线sln等电位,使得存储单元celln-1的mos管的源极区和漏极区等电位,存储单元celln 1的mos管的源极区和漏极区等电位,因此存储单元celln-1的mos管和存储单元celln 1的mos管中均不会有电流流过,存储单元celln-1和存储单元celln 1不会发生被误读写的问题。

52.基于本实施例的磁性随机存储器的电路及其读写方法能够实现更小的存储单元版图设计,以实现更高存储密度,例如将存储单元面积实现为4f2(f为特征尺寸)。下面结合附图2至图5c来详细说明本发明的具有4f2存储单元面积的磁性随机存储器的版图设计。

53.请参考图2,作为一种示例,本实施例的磁性随机存储器的版图结构具体包括:半导体衬底100、若干条字线wl、若干条源线sl、若干个磁性隧道结106以及若干条位线bl。图2中虽然仅仅示出了字线wln-2~wln 1、源线sln-1~sln 1以及位线bln~bln 1所限定的区域,但是本领域技术人员能够预料到本实施例的版图结构应该是沿图2的上下左右四个方向进行相应的有规律的延展而得到的版图结构。

54.其中,半导体衬底100可以是硅衬底、锗衬底、硅-锗衬底、绝缘体上硅(soi)衬底、绝缘体上锗(goi)衬底等。半导体衬底100中可以被注入有杂质,以形成有源区101,杂质可以包括例如磷、砷等的n型杂质,或者例如硼、镓等的p型杂质。相邻有源区101之间的间隔为场区(未图示),场区可以通过浅沟槽隔离(sti)工艺或局部场氧化隔离(locos)工艺形成。

55.本实施例中,半导体衬底100中形成有多个有源区101,所有的有源区101均呈条状,可以沿相互垂直的第一方向和第二方向排列,且有源区101的长度沿第三方向延伸,第三方向与第一方向和第二方向均相交,第三方向和第一方向之间的夹角包括但不限于45度,即也可以为45度,也可以不为45度。所有的有源区101排列为阵列,其中每条有源区101可以在第三方向上连续延伸至相应的半导体衬底100的整个第三方向长度,也可以在某些区域断开,由此形成在第一方向上和第二方向上对齐的多个有源区101块。

56.若干条字线wl沿第一方向排布且形成在所述半导体衬底100上,且每条所述字线wl沿第二方向延伸并跨设在多个所述有源区101上,所述第二方向与所述第一方向相垂直。每条所述字线wl将相应的所述有源区101分为源极区101a和漏极区101b。每个所述有源区101和设置在所述有源区101上方的相应的所述字线wl形成相应的mos管,即字线wl作为mos管的栅极,字线wl两侧的有源区101分别为mos管的源极区101a和漏极区101b,字线wl覆盖的有源区101为mos管的沟道区。字线wl的材质可以是多晶硅或金属栅极材质,字线wl和半导体衬底100之间还有栅介质层(未图示),字线wl的侧壁上还可能形成有侧墙(sidewall或者spacer,未图示)。字线wl的线宽可以等于或小于源极接触插塞和漏极接触插塞形成的插塞阵列的列间距,以避免字线wl与其他的有源区101重叠而造成存储单元之间的干扰,影响

器件性能。

57.若干条源线sl通过第一金属层103形成,并通过相应的源极接触插塞102连接相应的所述源极区101a。

58.各个磁性隧道结(mtj)106的底部通过相应的第二金属层105及第二金属层105下方的漏极接触插塞104连接相应的所述漏极区101b,各个磁性隧道结106的顶部连接第三金属层107,所述第三金属层107用于形成相应的位线bl。其中,每个有源区101处形成的所述mos管和所述有源区101上方的所述磁性隧道结106组成一个存储单元cell,每个存储单元cell的面积为2f*2f=4f2。共享同一条字线wl的相邻存储单元还可以进一步共享同一位线bl或同一源线sl。源极接触插塞102、漏极接触插塞104、第一金属层103、第二金属层105、第三金属层107均可以包括金属和/或金属氮化物。所有的源极接触插塞102和漏极接触插塞104按照行和列排列成插塞阵列,插塞阵列的行方向为垂直于第二方向的第一方向,插塞阵列的列方向为第二方向,由此使得磁性隧道结106按照插塞阵列的布局排列成相应的阵列。

59.各个磁性隧道结106可以包括依次形成在第二金属层105上的势垒层(未示出)、钉扎层、下铁磁层、反铁磁耦合间隔物层和上铁磁层等,势垒层可以减少或避免钉扎层、下铁磁层、铁磁耦合间隔物层和上铁磁层等中的金属异常生长,势垒层可以包括非晶的金属或金属氮化物,例如钽、钽氮化物、钛、钛氮化物等。钉扎层可以包括例如femn、irmn、ptmn、mno、mns、mnte、mnf2、fef2、fecl2、feo、cocl2、coo、nicl2、nio、cr等。下铁磁层和上铁磁层可以包括例如fe、ni、co等。反铁磁耦合间隔物层可以包括例如ru、ir、rh等。下铁磁层可以具有固定或“钉扎”磁取向,而上铁磁层具有可变或“自由”磁取向且可以在两个或多个不同的磁极性之间切换,每个磁极性表示不同的数据状态,诸如不同的二进制状态。然而,在其它实施方式中,mtj 106可以垂直“翻转”,从而使得下铁磁层具有“自由”磁取向,而上铁磁层具有“固定”磁取向。

60.请参考图2和图3,本实施例中,所述位线bl和所述源线sl平行设置,所述位线bl和所述源线sl所在的金属层完全没有重叠,所述位线bl依次通过磁隧道结106、第二金属层105以及漏极接触插塞104与漏极区相接触,所述源线sl通过源极接触插塞102与源极区相接触。所有的漏极接触插塞104和源极接触插塞102沿第一方向和第二方向排列成插塞阵列,请参考图2,在俯视角度下,所述插塞阵列的行方向为所述第一方向,所述插塞阵列的列方向为所述第二方向,相邻两行所述漏极接触插塞104对齐,相邻两列所述漏极接触插塞104对齐,相邻两行所述源极接触插塞102对齐,相邻两列所述源极接触插塞102对齐,且相邻两行所述漏极接触插塞104之间夹设一行所述源极接触插塞102。且所述位线bl与所述字线wl相交且垂直(即位线bl与字线wl在半导体衬底100表面上的投影相交且垂直,实际上位线bl与字线wl是异面垂直相交的)。此时,本实施例中,共享同一字线wl的相邻两个所述存储单元cell可以进一步共享同一位线bl或同一源线sl。图3所示的这种源线sl和位线bl结构,一方面,可以降低相邻存储单元之间的干扰,提高器件性能;另一方面能够相对增大两条相邻的位线bl上的相邻两个接触插塞之间的间距,降低接触插塞的制作难度,避免出现桥接等问题,提高器件性能。此时,每条字线wl与每条位线bl的交叉点连接部位对应一存储单元cell,每个存储单元cell可以为1晶体管(t)1磁性隧道结(mtj)结构,每个存储单元cell的面积为2f*2f=4f2。其中f为特征尺寸,每个存储单元cell在垂直于第二方向的方向上的长度为2f,在第二方向上的长度为2f。

61.此外,相邻字线wl之间、相邻位线bl之间、相邻源线sl之间、相邻磁隧道结106之间、相邻接触插塞之间、字线wl和位线bl之间、字线wl与源线sl之间、字线wl与磁隧道结106之间、源线sl与磁隧道结106之间、源线sl与位线之间、相邻存储单元cell的第二金属层105之间均通过相应的绝缘介质层(未图示)绝缘隔离开来。

62.另外需要说明的是,本发明的技术方案中,有源区和字线的布局在俯视角度上并不仅仅限于图2所示的版图布局结构,位线bl和源线sl的布局在俯视角度上并不仅仅限于图2所示的版图布局结构,在剖视角度上也不仅仅限于图3所示的布局结构,可以是其他任意合适的布局方式。具体地,例如,请参考图4,在本发明的其他实施例中,所述位线bl和所述源线sl也可以上下异面相交设置,请参考图4所示,所述位线bl和所述源线sl所在的金属层部分重叠,位线bl依次通过磁隧道结106、第二金属层105以及漏极接触插塞104’与所述源线sl所在的金属层103的部分金属层103’接触,金属层103’通过漏极接触插塞104与漏极区相接触,所述源线sl通过源极接触插塞102与源极区相接触。所述位线bl还与字线wl垂直。

63.再例如,请参考图5a,在本发明的其他实施例中,还可以在图2的字线wl和有源区101的版图布局基础上,使得:所述位线bl和所述源线sl平行设置,且所述位线bl与所述字线wl异面相交但不垂直(即位线bl与字线wl在半导体衬底100表面上的投影相交且夹角不为90度),可选地,所述位线bl和所述源线sl沿所述第三方向布设。此时,相邻两行所述存储单元还可以进一步共享同一条位线bl或同一条源线sl,即共享同一条字线wl的相邻存储单元还可以进一步共享同一位线bl或同一源线sl。同样地,图5a中虽然仅仅示出了字线wln-2~wln 1、源线sln-2~sln 1以及位线bln-1~bln 2所限定的区域,但是本领域技术人员能够预料到本实施例的版图结构应该是沿图5a的上下左右四个方向进行相应的有规律的延展而得到的版图结构。

64.又例如,请参考图5b,在本发明的其他实施例中,采用字线wl和有源区101相互垂直的布局方式。具体地,该实施例的磁性随机存储器的版图结构具体包括:半导体衬底100、若干条字线wl、若干条源线sl、若干个磁性隧道结106以及若干条位线bl。该示例中的共享同一字线wl的相邻两存储单元还可以进一步共享同一源线sl或同一位线bl。同样地,图5b中虽然仅仅示出了字线wln-1~wln 1、源线sln-1~sln 1以及位线bln-2~bln 1所限定的区域,但是本领域技术人员能够预料到本实施例的版图结构应该是沿图5b的上下左右四个方向进行相应的有规律的延展而得到的版图结构。

65.在该实施例中,半导体衬底100中形成有多个有源区101,每个有源区101沿第一方向延伸呈连续条状,所有的有源区101沿第二方向平行排布。其中每条有源区101可以在第一方向上连续延伸至相应的半导体衬底100的整个存储阵列区域的长度。有源区阵列所定义出的存储阵列中的每个存储单元cell在第一方向上的尺寸为2f,在第二方向上的尺寸为2f,每个存储单元cell的面积为2f*2f=4f2,其中,f为此磁性随机存储阵列作为半导体集成电路芯片的一部分或者大部分而被进行工艺制造时所对应的最小尺寸,也经常被称之为特征尺寸(feature size)。

66.若干条字线wl沿第一方向排布且形成在所述半导体衬底100上,且每条所述字线wl沿第二方向延伸并跨设在多个所述有源区101上,所述第二方向与所述第一方向相垂直。每条所述字线wl将相应的所述有源区分为源极区101a和漏极区101b。每个所述有源区101

和设置在所述有源区101上方的所述字线wl形成相应的mos管,即字线wl作为mos管的栅极,字线wl两侧的有源区101分别为mos管的源极区101a和漏极区101b,字线wl覆盖的有源区101为mos管的沟道区。字线wl和半导体衬底100之间还有栅介质层(未图示),字线wl的侧壁上还可能形成有侧墙(sidewall或者spacer,未图示)。字线wl的线宽可以等于或小于源极接触插塞和漏极接触插塞形成的插塞阵列的列间距,以避免存储单元之间的干扰,影响器件性能。

67.若干条源线sl通过第一金属层103形成,并通过相应的源极接触插塞102连接相应的所述源极区101a。

68.各个磁性隧道结(mtj)106的底部通过相应的第二金属层105及第二金属层105下方的漏极接触插塞104连接相应的所述漏极区101b,各个磁性隧道结106的顶部连接第三金属层107,所述第三金属层107用于形成相应的位线bl。其中,mtj 106只做在连接位线bl的mos管的漏极区上,每个有源区101处形成的相应的所述mos管和所述mos管的漏极区有源区101b上方的所述磁性隧道结106组成一个存储单元。

69.请结合图3和图5b,在该实施例中,所述位线bl和所述源线sl平行设置,所述位线bl和所述源线sl所在的金属层完全没有重叠,所述位线bl依次通过磁隧道结106、第二金属层105以及漏极接触插塞104与漏极区相接触,所述源线sl通过源极接触插塞102与源极区相接触。所有的漏极接触插塞104和源极接触插塞102按行和列排列成插塞阵列。请继续参考图5b,在俯视角度下,每行插塞中,漏极接触插塞104和源极接触插塞102交替排列,每列插塞中,漏极接触插塞104和源极接触插塞102也交替排列,相邻两行漏极接触插塞104交错不对齐,相邻两行源极接触插塞102交错不对齐,相邻两列漏极接触插塞104交错不对齐,相邻两列源极接触插塞102交错不对齐。且所述位线bl与所述字线wl相交且不垂直(即位线bl与字线wl在半导体衬底100表面上的投影相交且不垂直,实际上位线bl与字线wl是异面相交的),例如,所述位线bl与所述字线wl之间的夹角可以为45度,但不仅仅限于45度。

70.再例如,请结合图4和图5b,在本发明的其他实施例中,还可以在图5b的字线wl和有源区101的版图布局基础上,使得:所述位线bl和所述源线sl上下异面相交设置且均与字线wl垂直,请参考图4所示,所述位线bl和所述源线sl所在的金属层部分重叠,位线bl依次通过磁隧道结106、第二金属层105以及漏极接触插塞104’与所述源线sl所在的金属层103的部分金属层103’接触,金属层103’通过漏极接触插塞104与漏极区相接触,所述源线sl通过源极接触插塞102与源极区相接触。所述位线bl还与字线wl垂直。

71.又例如,请参考图5c,在本发明的其他实施例中,还可以在图5b的字线wl和有源区101的版图布局基础上,使得:所述位线bl和所述源线sl平行设置,且所述位线bl与所述字线wl异面垂直相交(即位线bl与字线wl在半导体衬底100表面上的投影相交且垂直,实际上位线bl与字线wl是异面垂直的),此时,相邻两行所述存储单元还可以进一步共享同一条位线bl或同一条源线sl,即共享同一条字线wl的相邻存储单元还可以进一步共享同一位线bl或同一源线sl。同样地,图5c中虽然仅仅示出了字线wln-1~wln 1、源线sln~sln 1以及位线bln-1~bln 1所限定的区域,但是本领域技术人员能够预料到本实施例的版图结构应该是沿图5c的上下左右四个方向进行相应的有规律的延展而得到的版图结构。

72.综上所述,本发明的磁性随机存储器,在占用相同衬底面积前提下,通过连条状延伸的有源区与多条字线相交的布局方式,能够有效利用衬底面积空间,实现更小的存储单

元的特征尺寸和更高的存储密度,芯片成本更低。进一步地,可以实现单元面积为4f2(f为特征尺寸)的密堆积存储阵列,提高存储密度和器件集成度。更重要的是,所述磁性随机存储器在进行读或写操作时,所述存储阵列中与需要读或写的存储单元相邻的非读写存储单元所连接的源线和位线等电位,由此,就算相应的字线将与需要读或写的存储单元相邻的非读写存储单元的mos管开启,由于非读写存储单元的mos管的源极区与漏极区等电位,该mos管也不会有电流流过,所以不会有误读与误写的问题。

73.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。