1.本发明与一存储单元、一存储装置及一识别标签相关,尤其是与接收及/或传送识别信息的存储单元、存储装置及识别标签相关。

背景技术:

2.现今,各个产业中皆应用了无线射频识别(radio

‑

frequency identification,简称rfid),来借着无线射频(radio

‑

frequency,简称rf)接口形成的电磁场自动识别及追踪附加在物件上的rfid标签(rfid tag),而无须机械或光电接触。rfid标签经编程化后可感应或回应一专属装置的特定频率,并可在感知由无线射频识别读写器(rfid reader)产生的预定频率的电磁讯问脉冲(interrogation pulse)之后,传送包括标签的协议(protocol)、rfid管理机构、资产信息及识别码(identification serial number)的rf讯号。然而,由于rfid标签需要花费许多时间与能量存取其非易失性存储器(non

‑

volatile memory),如:内嵌的电可擦写可编程只读存储器(electrically

‑

erasable programmable read

‑

only memory,简称eeprom)中所存储的信息,使得总能量消耗及总处理时间(transaction time)甚大。更甚者,在典型的rfid标签中,只有使用96位元的非易失性存储器来存储识别码,却需要消耗相对较大的面积及能量配置如:电荷泵(charge pump)等周边读取/写入电路。如此限制了rfid标签的成本及敏感度。

3.考量到信息真实性及安全性,由于部分的rfid标签可被耦接于一可编程逻辑控制器(programmable logic controller,简称plc)或一计算机的rfid收发器(rfid transceiver)重新编程化而重新写入,因此目前的rfid标签可能尚有缺陷存在。非易失性存储器在高温或辐射环境是脆弱的,而影响存储在此种rfid标签的信息可信赖度。

技术实现要素:

4.在发明内容部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

5.依据本发明的一面向提供一存储单元、一存储装置及一识别标签,以接收及/或传送识别信息。本发明的一实施例提供保持识别信息的一存储装置,其存储单元以电连接于专属闩锁(latch)的至少一可编程化熔丝(programmable fuses)构成,存储单元依据可编程化熔丝被编程化的方式来展现一电气特性。相对来说,存储单元的尺寸小以及对电气特性的传感时间较短。其次,尚可改善极端环境下的信息可信赖度。可藉激光或布局断线的方式编程化可编程化熔丝来不可逆转地写入识别信息,较佳地,可在半导体制造设备中的晶圆级测试程序(wafer level testing process)进行,且因此可改善信息真实性、信息安全性及写入生产量。

6.依据本发明之一面向,一实施例之一存储单元包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁由一第一基准电压及与第一基准电压不同的一第二基准电压

提供电力,并具有一第一连接端及一第二连接端。第一可编程化熔丝具有耦接于第一连接端的一第一端及耦接于第二基准电压的一第二端,且第二可编程化熔丝具有耦接于第二连接端的一第一端及耦接于第二基准电压的一第二端。

7.示例性地,所述第一基准电压及所述第二基准电压之其一是一电源电压,且所述第一基准电压及所述第二基准电压之另一是一接地电压。

8.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝是激光可编程化熔丝。

9.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝之其一已经预先编程化。

10.示例性地,所述存储单元更包括:一第一限制电路,依据一第一控制讯号将所述第一可编程化熔丝的所述第二端耦接至所述第二基准电压;及一第二限制电路,依据一第二控制讯号将所述第二可编程化熔丝的所述第二端耦接至所述基准电压。

11.示例性地,所述第一控制讯号及所述第二控制讯号是所述第一基准电压。

12.示例性地,所述第一控制讯号及所述第二控制讯号是所述第二基准电压。

13.示例性地,所述第一控制讯号是所述第一基准电压,且所述第二控制讯号是所述第二基准电压。

14.示例性地,所述第一限制电路包括:一第一晶体管,具有一第一连接端、一第二连接端及一控制端,所述第一连接端耦接于所述第一可编程化熔丝的所述第二端,所述第二连接端耦接于所述第二基准电压,且所述控制端耦接于所述第一控制讯号;及所述第二限制电路包括:一第二晶体管,具有一第一连接端、一第二连接端及一控制端,所述第一连接端耦接于所述第一可编程化熔丝的所述第二端,所述第二连接端耦接于所述第二基准电压,且所述控制端耦接于所述第二控制讯号。

15.示例性地,第一晶体管及所述第二晶体管是金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect晶体管,简称mosfet),且所述第一控制讯号及所述第二控制讯号是所述第一基准电压。

16.示例性地,第一晶体管及所述第二晶体管是原生型mosfet(native mosfet),且所述第一控制讯号及所述第二控制讯号是所述第二基准电压。

17.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝之其一经可编程化以形成一开路。

18.示例性地,所述第一控制讯号及所述第二控制讯号之其一是一电源电压,所述电源电压在读取所述存储单元时是开启的。

19.依据本发明之另一面向,一实施例之一存储单元包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁由一第一基准电压及与第一基准电压不同的一第二基准电压提供电力,并具有一连接端。第一可编程化熔丝具有耦接于连接端的一第一端及耦接于第一基准电压的一第二端,且第二可编程化熔丝具有耦接于连接端的一第一端及耦接于第二基准电压的一第二端。

20.示例性地,所述第一基准电压及所述第二基准电压之其一是一电源电压,且所述第一基准电压及所述第二基准电压之另一是一接地电压。

21.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝之其一已经预先编程

化。

22.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝是激光可编程化熔丝。

23.示例性地,所述存储单元更包括:一第一限制电路,依据一第一控制讯号将所述第一可编程化熔丝的所述第二端耦接于所述第一基准电压;及一第二限制电路,依据一第二控制讯号将所述第二可编程化熔丝的所述第二端耦接于所述第二基准电压。

24.示例性地,所述第一控制讯号是所述第二基准电压,且所述第二控制讯号是所述第一基准电压。

25.示例性地,所述第一限制电路包括:一第一晶体管,具有一第一连接端、一第二连接端及一控制端,所述第一连接端耦接于所述第一可编程化熔丝的所述第二端,所述第二连接端耦接于所述第一基准电压,且所述控制端耦接于所述第一控制讯号;及所述第二限制电路包括:一第二晶体管,具有一第一连接端、一第二连接端及一控制端,所述第一连接端耦接于所述第一可编程化熔丝的所述第二端,所述第二连接端耦接于所述第二基准电压,且所述控制端耦接于所述第二控制讯号;其中,所述第一控制讯号是所述第二基准电压,且所述第二控制讯号是所述第一基准电压。

26.示例性地,所述第一晶体管是一p型mosfet,及所述第二晶体管是一n型mosfet。

27.示例性地,所述第一可编程化熔丝及所述第二可编程化熔丝之其一经编程化以形成一开路。

28.示例性地,所述第一控制讯号及所述第二控制讯号之其一是一电源电压,所述电源电压在读取所述存储单元时是开启的。

29.依据本发明之另一面向,一实施例之一识别标签包括保持识别信息的一存储装置。存储装置包括一存储区块,存储区块包括多个存储单元。至少一存储单元包括包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁由一第一基准电压及与第一基准电压不同的一第二基准电压提供电力,并具有一第一连接端及一第二连接端。第一可编程化熔丝具有耦接于第一连接端的一第一端及耦接于第二基准电压的一第二端,且第二可编程化熔丝具有耦接于第二连接端的一第一端及耦接于第二基准电压的一第二端。第一可编程化熔丝及第二可编程化熔丝之其一经编程化以形成一开路。

30.依据本发明之另一面向,一实施例之保持识别信息之一存储装置包括一存储区块及一传感电路。存储区块包括多个存储单元,其中每个存储单元具有一闩锁及多个可编程化熔丝,此些可编程化熔丝电连接于闩锁,以依据可编程化熔丝被编程化的方式来展现一电气特性。传感电路电连接于存储区块,以传感存储单元的电气特性,且存储单元的电气特性共同代表识别信息。

31.示例性地,所述电气特性是电压电平。

32.示例性地,在所述些存储单元的至少一存储单元中,所述可编程化熔丝形成一可编程化熔丝对。

33.示例性地,在所述些存储单元的至少一存储单元中,所述闩锁包括两反向栅,且所述可编程化熔丝对的所述些可编程化熔丝分别电连接所述些反向栅之其一的一连接端及所述些反向栅之另一的一连接端。

34.示例性地,在所述些存储单元的至少一存储单元中,所述闩锁包括两反向栅,且所

述可编程化熔丝对中的所述些可编程化熔丝同时电连接所述些反向栅之其一的一连接端及所述些反向栅之另一的一连接端。

35.示例性地,在所述些存储单元的至少一存储单元中,一可编程化熔丝对经编程化。

36.示例性地,在所述些存储单元的至少一存储单元中,所述第一可编程化熔丝及所述第二可编程化熔丝之其一已经预先编程化。

附图说明

37.本发明的下列附图在此作为本发明的一部分用于理解本发明。附图中示出了本发明的实施例及其描述,用来解释本发明的原理。

38.附图中:

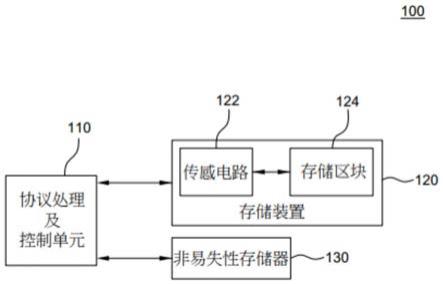

39.图1显示依据本发明一第一实施例之一识别标签的例示功能方块图;

40.图2显示依据本发明第一实施例之一协议处理及控制单元的例示功能方块图;

41.图3显示依据本发明第一实施例之一识别标签之传感电路的例示功能方块图;

42.图4显示依据本发明第一实施例之一存储单元的五种例示电路架构;

43.图5显示依据本发明第一实施例之一可编程化熔丝的一例示电路架构;

44.图6至图9显示依据本发明第二、第三、第四及第五实施例之一存储单元的例示电路架构;及

45.图10显示依据本发明第一实施例以可编程化熔丝被炸除的情形代表信息之一例示表。

具体实施方式

46.在下文的描述中,给出了大量具体的细节以便提供对本发明更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本发明可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本发明发生混淆,对于本领域公知的一些技术特征未进行描述。

47.为了彻底理解本发明,将在下列的描述中提出详细的描述,以说明本发明的存储单元、存储装置及相关识别标签的装置与方法。显然,本发明的施行并不限于半导体领域技术人员所熟习的特殊细节。本发明的较佳实施例详细描述如下,然而除了这些详细描述外,本发明还可以具有其他实施方式。

48.应予以注意的是,这里所使用的术语仅是为了描述具体实施例,而非意图限制根据本发明的示例性实施例。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式。此外,还应当理解的是,当在本说明书中使用术语“包含”和/或“包括”时,其指明存在所述特征、整体、步骤、操作、元件和/或组件,但不排除存在或附加一个或多个其他特征、整体、步骤、操作、元件、组件和/或它们的组合。

49.现在,将参照附图更详细地描述根据本发明的示例性实施例。然而,这些示例性实施例可以多种不同的形式来实施,并且不应当被解释为只限于这里所阐述的实施例。应当理解的是,提供这些实施例是为了使得本发明的公开彻底且完整,并且将这些示例性实施例的构思充分传达给本领域普通技术人员。在附图中,为了清楚起见,使用相同的附图标记表示相同的元件,因而将省略对它们的描述。

50.本技术提供一存储单元、保持识别信息之一存储装置及一识别标签之示例。一存储单元之一实施例可包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁可由一第一基准电压及与第一基准电压不同的一第二基准电压提供电力,并具有一第一连接端及一第二连接端。第一可编程化熔丝可具有耦接于第一连接端的一第一端及耦接于第二基准电压的一第二端,且第二可编程化熔丝可具有耦接于第二连接端的一第一端及耦接于第二基准电压的一第二端。

51.一存储单元之一实施例可包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁可由一第一基准电压及与第一基准电压不同的一第二基准电压提供电力,并具有一连接端。第一可编程化熔丝可具有耦接于连接端的一第一端及耦接于第一基准电压的一第二端,且第二可编程化熔丝可具有耦接于连接端的一第一端及耦接于第二基准电压的一第二端。

52.一识别标签之一实施例可包括保持识别信息的一存储装置。存储装置可包括一存储区块,存储区块可包括多个存储单元。至少一存储单元可包括包括一闩锁、一第一可编程化熔丝及一第二可编程化熔丝。闩锁可由一第一基准电压及与第一基准电压不同的一第二基准电压提供电力,并具有一第一连接端及一第二连接端。第一可编程化熔丝可具有耦接于第一连接端的一第一端及耦接于第二基准电压的一第二端,且第二可编程化熔丝可具有耦接于第二连接端的一第一端及耦接于第二基准电压的一第二端。第一可编程化熔丝及第二可编程化熔丝之其一可经编程化以形成一开路。

53.保持识别信息之一存储装置之一实施例可包括一存储区块及一传感电路。存储区块可包括多个存储单元,其中每个存储单元可具有一闩锁及多个可编程化熔丝,此些可编程化熔丝可电连接于闩锁,以依据可编程化熔丝被编程化的方式来展现一电气特性。传感电路可电连接于存储区块,以传感存储单元的电气特性,且存储单元的电气特性可共同代表识别信息。

54.请参考图1至图5及图10。图1显示依据本发明一第一实施例之一识别标签的例示功能方块图,图2显示依据本发明第一实施例之一协议处理及控制单元的例示功能方块图,图3显示依据本发明第一实施例之一识别标签之传感电路的例示功能方块图,图4显示依据本发明第一实施例之一存储单元的五种例示电路架构,图5显示依据本发明第一实施例之一可编程化熔丝的一例示电路架构,图10显示依据本发明第一实施例以可编程化熔丝被炸除(blasted)的情形代表信息之一例示表。

55.如图1所示,本发明之一识别标签100可包括一协议处理及控制单元110,一存储装置120及一非易失性存储器(non

‑

volatile memory)130。协议处理及控制单元110电连接于存储装置120及非易失性存储器130,且可依从一通讯标准传送包括存储在存储装置120的识别信息的讯号至一识别读写器(identification reader)(图中未示)。在本实施例中,可以无线射频(radio

‑

frequency,简称rf)接口实施通讯标准,并且在此情形时,识别读写器可为一无线射频识别读写器(radio

‑

frequency identification reader,简称rfid reader),而识别标签100可用以取代一rfid标签来实施无线射频识别。前述讯号可为无线射频讯号。当协议处理及控制单元110使用一预定频率及数据包协议与识别读写器完成一握手程序(hand

‑

shaking process)时,其可输出包括识别信息的另一讯号至识别读写器。如图2所示,示例的协议处理及控制单元110可包括一控制逻辑111、一解调器

(demodulator)112、一整流器(rectifier)113、一调节器(regulator)114、一基准电压产生器115、一调变器(modulator)116及一天线117。控制逻辑111可控制存储装置120及非易失性存储器130的操作。调变器116可在天线117无线发射讯号之前调变讯号。接收自天线117的讯号可经下列两种方式之其一处理,其一是经解调器112解调并接着传送至控制逻辑111,另一是经整流器113整流、在超出一预定限制值时经截断直流(dc)电压并经自基准电压产生器115接收至少一固定电压的调节器114调节来产生至少一基准电压。此基准电压举例为v

dd

,其可接着被传送到控制逻辑111。

56.存储装置120可包括一传感电路122及一存储区块124。如图3所示,传感电路122电连接于存储区块124可以实施但不限于一传感放大器(sense amplifier),其由三个正通道金属氧化物半导体(positive channel metal oxide semiconductor,简称pmos)p1、p2、p3及三个负通道金属氧化物半导体(negative channel metal oxide semiconductor,简称nmos)n1、n2、n3构成。传感电路122可经复用设计以传感多个位元,或者固定传感保持在存储区块124的识别信息的一特定位元,在后者情况时可缩短传感时间。

57.存储区块124可包括多个存储单元,其中的每一个存储单元可具有一闩锁及多个可编程化熔丝电连接于闩锁。存储单元的数量可以根据需求变化,但本实施例所应用的rfid标签的内文(context)为96位元,藉此存储一rfid序列号码(rfid serial number)。图示显示示例的存储单元126。由两个基准电压v

dd

及v

ss

提供电力的闩锁是由彼此反向电连接或交叉耦合(cross

‑

coupled)的两个反向栅(inverting gates)所构成,其中一个反向栅包括一个nmos m1及一个pmos m3,另一个反向栅包括一个nmos m2及一个pmos m4。在此,v

dd

是一电源电压,而v

s

是一接地电压。较佳地,可即时控制v

dd

而仅在读取存储单元126时开启v

dd

。反向栅可为not栅、nand栅、nor栅等,在此以两反向栅都是not栅为例。提供两个连接端o1、o2,not栅的其一连接端o1/o2所输出的一输出电压电平可以是在一连接端i1/i2从高电平基准电压v

dd

经反相处理得到的讯号。举例来说,将在连接端i1输入的高电压电平反相处理,可产生在连接端o1输出的低电压电平。

58.如图5显示,可编程化熔丝f1,f2可以是激光可编程化熔丝,即,可被激光炸除(blasted)或打开以形成一开路。特定地说,每一可编程化熔丝f1、f2可以一可编程化部分127及其两端构成,可编程化部分127可被激光炸除,而可编程化部分127的两端可形成工连接的导电穿孔128。较佳地,前述可编程化部分127其中构成可编程化部分127的材料皆被激光炸除后,可在其上形成一编程化窗口(或称一暴露开口)129。激光光束可通过编程化窗口129炸除可编程化部分127以形成两个穿孔128之间的开路。如图4显示,两个可编程化熔丝f1、f2组成一可编程化熔丝对,其中各可编程化熔丝分别电连接到反向栅之一的连接端i1/i2及另一反向栅的连接端o2/o1。可编程化熔丝f1、f2的另一端f1t2、f2t2是分别电连接到一限制装置l1/l2,如以一晶体管实施的一电流限制装置,晶体管可为金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect晶体管,简称mosfet)、nmos等。特定地说,可编程化熔丝f1可具有耦接于连接端o1的一端f1t1及透过限制装置l1耦接于基准电压v

s

的另一端f1t2,且可编程化熔丝f2可具有耦接于连接端o2的一端f2t1及透过限制装置l2耦接于基准电压v

s

的另一端f2t2。限制装置l1/l2可提供耦接于可编程化熔丝f1/f2的f1t2/f2t2端的一连接端l1t1/l2t1、耦接于基准电压v

ss

的另一连接端l1t2/l2t2、及耦接于一控制讯号v

dd

的一控制端l1t3/l2t3,因此可安排限制装置l1、l2来依据控制讯号v

dd

,将可

编程化熔丝f1、f2的f1t2端、f2t2端耦接于基准电压v

s

。在此举例控制讯号v

dd

是与基准电压v

dd

相同。较佳地,可在尺寸远小于其中具有习知非挥发存储单元的非易失性存储器的一半导体晶片中实施可编程化熔丝f1、f2。可借着激光编程化可编程化熔丝f1、f2,将识别信息写入每个存储单元126的可编程化熔丝。可借着可编程化熔丝f1、f2被编程化的方式来影响连接端o2所展现的电气特性,此电气特性可由传感电路122传感。在本实施例中,电气特性可为电压电平。可在半导体制造设备中的晶圆级测试程序(wafer level testing process)进行写入程序,以改善写入生产量。在激光一次性地写入之后,仅能读取存储单元。换句话说,因为识别信息固定为已写入存储单元的内容而无法变更,如此可提供健全的信息真实性及安全性。

59.请参考图10,其显示依据可编程化熔丝被编程化的方式来展现位元值的示例。当可编程化熔丝f1由激光光束而编程化,但可编程化熔丝f2并未被编程化时,在连接端o1可传感到高电压电平,因此从存储单元126读取到1的位元值。相对地,当可编程化熔丝f1并未被编程化,而可编程化熔丝f2被编程化时,在连接端o1可传感到低电压电平,因此从存储单元126读取到0的位元值。传感位元值只需要非常低的上电(power

‑

up)能量,无须特别的上电程序,而可简化传感电路122的电路设计并加速传感时间。其次,限制装置l1及/或限制装置l2可为一可选用装置。在其他实施例中,f1t2端及/或f2t2端可直接连接基准电压v

ss

。

60.非易失性存储器130可存储配置信息(configuration information),如:与晶体管门槛(threshold)/漏电流(leakage)或电阻的薄膜电阻值(sheet resistance)相关的制程设定,此制程设定可与剪切(trimming)相关。在本发明一些实施例中,一识别标签中可不存在一非易失性存储器。

61.图6至图9显示一存储单元的各种例示设计。在每个例示的存储单元中,存在一闩锁,由两个基准电压,v

dd

及v

ss

提供电力,且存在电连接于闩锁的多个可编程化熔丝。较佳地,两个可编程化熔丝f1、f2组成一可编程化熔丝对。可在尺寸远小于其中具有习知非挥发存储单元的非易失性存储器的一半导体晶片中实施可编程化熔丝f1、f2。可借着激光编程化可编程化熔丝f1、f2,将识别信息写入每个存储单元126的可编程化熔丝。可借着可编程化熔丝f1、f2被编程化的方式来影响连接端o2所展现的电气特性,此电气特性可由传感电路122传感。在本实施例中,电气特性可为电压电平。可在半导体制造设备中的晶圆级测试程序进行写入程序,以改善写入生产量。在激光一次性地写入之后,仅能读取存储单元。换句话说,因为识别信息固定为已写入存储单元的内容而无法变更,如此可提供健全的信息真实性及安全性。

62.图6显示在本发明一第二实施例对一存储单元126的设计。与图4类似地,一闩锁是由彼此反向电连接的两个反向栅所构成,其中一个反向栅包括一nmos m1及一pmos m3,而另一个反向栅包括一nmos m2及一pmos m4。在not栅的一连接端o1/o2所呈现的一输出电压电平可以是在一连接端i1/i2从高电平基准电压v

dd

经反相处理得到的讯号。举例来说,将在连接端i1输入的高电压电平反相处理,可产生在连接端o1输出的低电压电平。可编程化熔丝f1、f2分别电连接到反向栅之一的连接端i1/i2及另一反向栅的连接端o2/o1。可编程化熔丝f1、f2的另一端f1t2、f2t2是分别透过一限制装置l3/l4耦接于基准电压v

s

。限制装置l3、l4举例可为以一晶体管实施的一零阈值电压装置(zero

‑

v

t device),在此以原生型mosfet(native mosfet)为例,可提供耦接于可编程化熔丝f1/f2的f1t2/f2t2端的一连接

端l3t1/l4t1、耦接于基准电压v

ss

的另一连接端l3t2/l4t2及耦接于一控制讯号v

ss

的一控制端l3t3/l4t3,因此可设置限制装置l3、l4来依据控制讯号v

ss

使可编程化熔丝f1、f2的f1t2、f2t2端耦接于基准电压v

s

,控制讯号v

ss

举例是与基准电压v

s

相同。

63.在本实施例中,当可编程化熔丝f1被编程化,而可编程化熔丝f2并未被编程化时,在连接端o1可传感到高电压电平,因此从存储单元126读取到1的位元值。相对地,当可编程化熔丝f1并未被编程化,而可编程化熔丝f2被编程化时,在连接端o1可传感到低电压电平,因此从存储单元126读取到0的位元值。传感位元值只需要非常低的上电能量,无须特别的上电程序,而可简化传感电路122的电路设计并加速传感时间。其次,限制装置l3及/或限制装置l4可为一可选用装置。在其他实施例中,f1t2端及/或f2t2端可直接连接基准电压v

ss

。

64.图7显示在本发明一第三实施例对一存储单元126的设计。与图4类似地,由两个基准电压,v

dd

及v

ss

提供电力的一闩锁,是由彼此反向电连接的两个反向栅所构成,其中一个反向栅包括一nmos m1及一pmos m3,而另一个反向栅包括一nmos m2及一pmos m4。在反向栅的一连接端o1/o2所呈现的一输出电压电平可以是在一连接端i1/i2从高电平基准电压v

dd

经反相处理得到的讯号。举例来说,将在连接端i1输入的高电压电平反相处理,可产生在连接端o1输出的低电压电平。可编程化熔丝f1、f2皆电连接到包括nmos m1及pmos m3的反向栅的连接端i1及包括nmos m2及pmos m4的另一反向栅的连接端o2。可编程化熔丝f1、f2的另一端f1t2、f2t2是分别透过一限制装置l5/l6耦接于基准电压v

dd

/v

s

。限制装置l5、l6举例可以一晶体管实施,在此以nmos及pmos为例,可提供耦接于可编程化熔丝f1/f2的f1t2/f2t2端的一连接端l5t1/l6t1、耦接于基准电压v

dd

/v

ss

的另一连接端l5t2/l6t2及耦接于一控制讯号v

ss

/v

dd

的一控制端l5t3/l6t3,因此可设置限制装置l5、l6来依据控制讯号v

ss

/v

dd

使可编程化熔丝f1、f2的f1t2、f2t2端耦接于基准电压v

dd

/v

s

,控制讯号v

ss

/v

dd

举例是与基准电压v

ss

/v

dd

相同。

65.在本实施例中,当可编程化熔丝f1被编程化,而可编程化熔丝f2并未被编程化时,在连接端o1可传感到高电压电平,因此从存储单元126读取到1的位元值。相对地,当可编程化熔丝f1并未被编程化,而可编程化熔丝f2被编程化时,在连接端o1可传感到低电压电平,因此从存储单元126读取到0的位元值。传感位元值只需要非常低的上电能量,无须特别的上电程序,而可简化传感电路122的电路设计并加速传感时间。其次,限制装置l5及/或限制装置l6可为一可选用装置。在其他实施例中,f1t2端及/或f2t2端可直接连接基准电压v

ss

。

66.图8显示在本发明一第四实施例对一存储单元126的设计。与图4类似地,以两个基准电压,v

dd

及v

ss

提供电力的一闩锁,是由彼此反向电连接的两个反向栅所构成,其中一个反向栅包括一nmos m1及一pmos m3,而另一个反向栅包括一nmos m2及一pmos m4。在not栅的一连接端o1/o2所呈现的一输出电压电平可以是在一连接端i1/i2从高电平基准电压v

dd

经反相处理得到的讯号。举例来说,将在连接端i1输入的高电压电平反相处理,可产生在连接端o1输出的低电压电平。可编程化熔丝f1、f2皆电连接到包括nmos m1及pmos m3的反向栅的连接端i1及包括nmos m2及pmos m4的另一反向栅的连接端o2。可编程化熔丝f1、f2的另一端f1t2、f2t2是分别透过一限制装置l7/l8耦接于基准电压v

dd

/v

s

。限制装置l7、l8举例可以是由一晶体管实施的电流限制装置或零阈值电压装置,在此以耗尽模式(depletion mode)nmos及pmos为例,可提供耦接于可编程化熔丝f1/f2的f1t2/f2t2端的一连接端l7t1/l8t1、耦接于基准电压v

dd

/v

ss

的另一连接端l7t2/l8t2及耦接于一控制讯号v

ss

/v

dd

的一控制

端l7t3/l8t3,因此可设置限制装置l7、l8来依据控制讯号v

ss

/v

dd

使可编程化熔丝f1、f2的f1t2、f2t2端耦接于基准电压v

dd

/v

s

,控制讯号v

ss

/v

dd

举例是与基准电压v

ss

/v

dd

相同。

67.在本实施例中,当可编程化熔丝f1被编程化,而可编程化熔丝f2并未被编程化时,在连接端o1可传感到高电压电平,因此从存储单元126读取到1的位元值。相对地,当可编程化熔丝f1并未被编程化,而可编程化熔丝f2被编程化时,在连接端o1可传感到低电压电平,因此从存储单元126读取到0的位元值。传感位元值只需要非常低的上电能量,无须特别的上电程序,而可简化传感电路122的电路设计并加速传感时间。其次,限制装置l7及/或限制装置l8可为一可选用装置。在其他实施例中,f1t2端及/或f2t2端可直接连接基准电压v

ss

。

68.图9显示在本发明一第五实施例对一存储单元126的设计。与图4类似地,由两个基准电压,v

dd

及v

ss

提供电力的一闩锁,是由彼此反向电连接的两个反向栅所构成,其中一个反向栅包括一nmos m1及一pmos m3,而另一个反向栅包括一nmos m2及一pmos m4。在反向栅的一连接端o1/o2所呈现的一输出电压电平可以是在一连接端i1/i2从高电平基准电压v

dd

经反相处理得到的讯号。举例来说,将在连接端i1输入的高电压电平反相处理,可产生在连接端o1输出的低电压电平。可编程化熔丝f1、f2分别电连接到其一反向栅的连接端i1/i2及另一反向栅的连接端o2/o2。可编程化熔丝f1、f2的另一端f1t2、f2t2是分别透过一限制装置l9/l10耦接于基准电压v

dd

。限制装置l9、l10举例可以是由一晶体管实施的电流限制装置,在此以pmos为例,可提供耦接于可编程化熔丝f1/f2的f1t2/f2t2端的一连接端l9t1/l10t1、耦接于基准电压v

dd

的另一连接端l9t2/l10t2及耦接于一控制讯号v

ss

的一控制端l9t3/l10t3,因此可设置限制装置l9、l10来依据控制讯号v

ss

使可编程化熔丝f1、f2的f1t2、f2t2端耦接于基准电压v

dd

,控制讯号v

ss

举例是与基准电压v

ss

相同。

69.在本实施例中,当可编程化熔丝f1被编程化,而可编程化熔丝f2并未被编程化时,在连接端o2可传感到高电压电平,因此从存储单元126读取到1的位元值。相对地,当可编程化熔丝f1并未被编程化,而可编程化熔丝f2被编程化时,在连接端o2可传感到低电压电平,因此从存储单元126读取到0的位元值。传感位元值只需要非常低的上电能量,无须特别的上电程序,而可简化传感电路122的电路设计并加速传感时间。其次,限制装置l9及/或限制装置l10可为一可选用装置。在其他实施例中,f1t2端及/或f2t2端可直接连接基准电压v

dd

。

70.依据本发明一第六实施例所设计的存储单元126是显示在图4及图6

‑

10之其一。在一存储单元126中,可藉设计断路的布线来预先编程化可编程化熔丝f1、f2之一者,即,制造可编程化熔丝f1、f2之其一是断开的。较佳地,光罩中的一些裸芯片(dice)可经预先编程化来降低编程化的时间,但在其他裸芯片中可未经预先编程化的。特定地说,可经预先编程化的裸芯片可以渐递增加序列号码,每次增加1。接着,光罩中只有大部分裸芯片的共同位元需要藉激光来编程化。

71.依据本发明,限制装置l1

‑

l10中,晶体管的閾值电压不限于图4及图6

‑

9所显示者,可设计晶体管的閾值电压为多个客制化的閾值电压来使各个存储单元的表现为最佳。

72.如前所述,在本发明之实施例中,接收及/或传送识别信息的一存储装置、一识别标签及一识别信息接收及传送系统是将识别信息存储在经良好设计且新颖的存储单元中,每个存储单元至少是由可编程化熔丝形成,可编程化熔丝电连接于一闩锁,并依据可编程化熔丝被编程化的方式来展现一电气特性。相对习知来说,存储单元的尺寸比较小且传感电气特性的时间也比较短。其次,尚可改善极端环境下的信息可信赖度。可藉激光或布局断

线的方式编程化可编程化熔丝来不可逆转地写入识别信息,较佳地,可在半导体制造设备中的晶圆级测试程序(wafer level testing process)进行,且因此可改善信息真实性、信息安全性及写入生产量。

73.本发明已经通过上述实施例进行了说明,但应当理解的是,上述实施例只是用于举例和说明的目的,而非意在将本发明限制于所描述的实施例范围内。此外本领域技术人员可以理解的是,本发明并不局限于上述实施例,根据本发明的教导还可以做出更多种的变型和修改,这些变型和修改均落在本发明所要求保护的范围以内。本发明的保护范围由附属的权利要求书及其等效范围所界定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。