1.本揭示文件是关于一种集成电路,特别是一种包含电子熔丝单元的集成电路。

背景技术:

2.将非挥发性记忆体(non

‑

volatile memory;nvm)提供于集成电路(integrated circuit;ic)中。nvm能够在关断ic后保留数据。一些nvm利用包含例如电子熔丝(electrical fuse;efuse)的技术实施对ic重新程序化。

技术实现要素:

3.本揭示文件的一些实施例提供一种集成电路。集成电路包括晶体管、第一熔丝元件及第二熔丝元件。晶体管形成于第一导电层中。第一熔丝元件形成于设置于第一导电层上方的第二导电层中。第二熔丝元件形成于第二导电层中且耦接至第一熔丝元件。晶体管经由第一熔丝元件耦接至用于接收第一数据信号的第一数据线,且晶体管经由第二熔丝元件耦接至用于接收第二数据信号的第二数据线。

4.本揭示文件的一些实施例亦提供一种集成电路。集成电路包括电子熔丝单元阵列。电子熔丝单元阵列包括按多个行及多个列配置的多个电子熔丝单元。电子熔丝单元包括第一导电区段、第一晶体管及一对第一熔丝元件。第一晶体管形成于第一导电层中。此对第一熔丝元件形成于设置于第一导电层上方的第二导电层中。此对第一熔丝元件耦接在一起,且经由第一导电区段耦接至第一晶体管。第一晶体管经由此对第一熔丝元件中的一者耦接至用于接收第一数据信号的第一数据线,且第一晶体管经由此对第一熔丝元件中的另一者耦接至用于接收第二数据信号的第二数据线。

5.本揭示文件的一些实施例亦提供一种制造集成电路的方法。方法包括以下步骤:在集成电路中的第一导电层中形成第一熔丝元件;在集成电路中的第一导电层中形成耦接至第一熔丝元件的第二熔丝元件;在集成电路中的设置于第一导电层下方的第二导电层中形成晶体管;及经由第一熔丝元件将晶体管耦接至用于接收第一数据电压的第一数据线,及经由第二熔丝元件将晶体管耦接至用于接收第二数据电压的第二数据线。

附图说明

6.当通过附图阅读时,自以下详细描述,最佳地理解本揭示内容的一些实施例的态样。注意,根据此行业中的标准实务,各种特征未按比例绘制。事实上,为了论述的清晰起见,可任意地增大或减小各种特征的尺寸。

7.图1为根据本揭示内容的一些实施例的一电路的电路示意图;

8.图2为根据本揭示内容的一些实施例的对应于图1中展示的电子熔丝(electrical fuse;efuse)电路的一efuse电路的电路示意图;

9.图3a为根据本揭示内容的一些实施例的对应于图2中展示的efuse单元(efuse cell)中的一者的efuse单元的电路示意图;

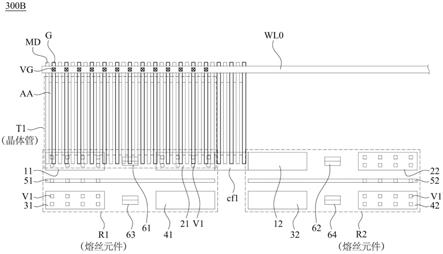

10.图3b为根据本揭示内容的一些实施例的对应于图3a中展示的efuse单元的efuse单元的布局结构;

11.图4a为根据本揭示内容的一些实施例的对应于图2中展示的efuse单元的efuse单元的电路示意图;

12.图4b为根据本揭示内容的一些实施例的对应于图4a中展示的efuse单元的efuse单元的布局结构;

13.图4c为根据本揭示内容的一些实施例的对应于图4b中展示的efuse单元的efuse单元的横截面示意图;

14.图5a为根据本揭示内容的一些实施例的对应于图4a中展示的efuse单元的efuse单元的布局结构;

15.图5b为根据本揭示内容的一些实施例的对应于图5a中展示的efuse单元的efuse单元的横截面示意图;

16.图6a为根据本揭示内容的一些实施例的对应于图2中展示的efuse单元的efuse单元的电路示意图;

17.图6b为根据本揭示内容的一些实施例的对应于图6a中展示的efuse单元的efuse单元的布局结构;

18.图7为根据本揭示内容的一些实施例的用于对应于图2中展示的efuse单元的efuse单元的电路路径的示意图;

19.图8a为根据本揭示内容的一些实施例的用于产生包含efuse单元的集成电路(integrated circuit;ic)布局图的方法的流程图;

20.图8b为根据本揭示内容的一些实施例的用于产生包含efuse单元的集成电路(integrated circuit;ic)的方法的流程图;

21.图9为根据本揭示内容的一些实施例的用于设计ic布局设计的系统的方块图;

22.图10为根据一些实施例的ic制造系统及与其相关联的ic制造流程的方块图。

23.【符号说明】

24.11、12、13、14、21、22、23、24、31、32、41、42:熔丝区段

25.51、52、53、54:熔丝线

26.61、62、63、64、65、66:熔丝壁

27.100:记忆体电路

28.110:程序选择单元

29.120:读取选择单元

30.130:感测放大器

31.140:参考电路

32.220、230、240、250、260、270、280、290:电子熔丝(efuse)单元

33.221、222、241、242、261、262、281、282:efuse元件

34.223、243、263、283:晶体管元件

35.300a、400a、600a:efuse单元

36.300b、400b、500a、600b:布局结构

37.500b:示意图

38.800a、800b:方法

39.900:电子设计自动化系统

40.910:输入/输出接口

41.920:处理器

42.930:网络接口

43.940:网络

44.950:总线

45.960:储存媒体

46.961:计算机程序码(指令)

47.962:程序库

48.963:使用者界面

49.970:制造工具

50.1000:集成电路(ic)制造系统

51.1020:设计室

52.1022:ic设计布局图

53.1030:光罩室

54.1032:光罩数据准备

55.1044:光罩制造

56.1045:光罩

57.1050:ic晶圆厂

58.1052:晶圆制造

59.1053:半导体晶圆

60.1060:ic元件

61.s810a

‑

s840a、s810b

‑

s840 b:操作

62.aa:主动区

63.bl0

‑

bl3:位元线

64.cf1、cf2:熔丝导电区段

65.cg:栅极区段

66.cs1、cs2:导电区段

67.fa:电子熔丝(efuse)电路

68.g:栅极

69.md:连接结构

70.p1:程序路径、电力开关

71.p2:读取路径、程序选择晶体管

72.r1

‑

r8:熔丝元件、熔丝

73.rdrop、rfuse、rdrain、rvss:电阻

74.rref、rvqps:电阻器

75.rvq_ypass:电阻、电阻器

76.t1

‑

t5:晶体管

77.v1、vg:导通孔

78.vdd:读取电压

79.vddq:程序电压

80.vq:节点

81.vqps:电源供应器

82.wl0

‑

wl4:字元线

83.线1、线2:线

具体实施方式

84.以下揭露内容提供许多不同实施例或实例,用于实施提供的标的的不同特征。以下描述元件及布置的具体实例以简化本揭示内容的一些实施例。当然,这些仅为实例,且并不意欲为限制性。举例而言,在接下来的描述中,第一特征在第二特征上方或上的形成可包含第一与第二特征直接接触地形成的实施例,且亦可包含额外特征可形成于第一与第二特征之间使得第一与第二特征可不直接接触的实施例。此外,在各种实例中,本揭示内容的一些实施例可重复参考数字及/或字母。此重复是为了简单且清晰的目的,且自身并不规定论述的各种实施例及/或组态之间的关系。

85.在本说明书中使用的术语通常具有其在此项技术中及在使用各术语的具体上下文中的普通意义。在本说明书中的实例(包含本文中论述的任何术语的实例)的使用是说明性的,且决不限制本揭示内容的一些实施例或任一举例说明的术语的范畴及意义。同样地,本揭示内容的一些实施例不限于在本说明书中给出的各种实施例。

86.虽然术语“第一”、“第二”等可在本文中用以描述各种元件,但这些元件不应受到这些术语限制。这些术语用以将一个元件与另一元件区分。举例而言,在不脱离实施例的范畴的情况下,第一元件可被称为第二元件,且类似地,第二元件可被称为第一元件。如本文中所使用,术语“及/或”包含相关联的列出项目中的一或多者的任何及所有组合。

87.在本文中,术语“耦接”亦可被称为“电耦接”,且术语“连接”可被称为“电连接”。“耦接”及“连接”亦可用来指示两个或更多个元件相互合作或互动。

88.此外,为了易于理解,诸如“下伏(underlying)”、“在

……

下方(below)”、“下部(lower)”、“上覆(overlying)”、“上部(upper)”及类似者的空间相对术语可贯穿此描述用以描述如在图中图示的一个元件或特征与另一(另外)元件或特征的关系。除了图中描绘的定向之外,这些空间相对术语意欲亦涵盖在使用或操作中的元件的不同定向。可将结构以其他方式定向(例如,旋转90度或以其他定向),且同样地可将本文中使用的空间相对描述词相应地作出解释。

89.如本文中所使用,“大约”、“约”、“大致”或“实质上”应大体指一给定值或范围的任一近似值,其中其取决于其属的各种技术而变化,且其范畴应与由熟悉其属的此项技术者理解的最宽泛解释一致,以便涵盖所有这些修改及类似结构。在一些实施例,其应大体意谓在一给定值或范围的20%内,较佳地10%内,且更佳地5%内。本文中给出的数值量为近似,意谓术语“大约”、“约”、“大致”或“实质上”若未明确地陈述,则可加以推断,或意谓其他近似值。

90.现在对图1进行参看。图1为根据本揭示内容的一些实施例的记忆体电路100的电

路示意图。在一些实施例中,记忆体电路100亦指非挥发性记忆体(non

‑

volatile memory;nvm)电路。

91.对于图1中的图示,记忆体电路100包含程序选择单元(program selection unit)110、读取选择单元(read selection unit)120、感测放大器(sense amplifier)130、参考电路140及电子熔丝(electrical fuse;efuse)电路fa。程序选择单元110耦接至efuse电路fa,且用以接收包含例如程序电压vddq的程序信号。读取选择单元120耦接于感测放大器130与efuse电路fa之间,且用以接收自感测放大器130耦接的读取信号,包含例如,读取电压vdd。感测放大器130耦接至读取选择单元120,且用以接收读取信号。efuse电路fa在节点vq处耦接至程序选择单元110及读取选择单元120两者。参考电路140耦接至感测放大器130。

92.继续参看图1,亦图示程序路径p1及读取路径p2,分别用于程序化及读取efuse电路fa。

93.程序路径p1包含将程序信号耦接至节点vq的程序选择单元110。在一些实施例中,程序选择单元110包含选择晶体管t1。选择晶体管t1在一些实施例为p型金属氧化物半导体(pmos)晶体管。

94.读取路径p2包含读取选择单元120及感测放大器130的部分(亦即,图1中展示的晶体管t3)。在一些实施例中,读取选择单元120包含选择晶体管t2。选择晶体管t2在一些实施例为n型金属氧化物半导体(nmos)晶体管。读取选择单元120将读取电压信号耦接至节点vq。在一些实施例中,感测放大器130包含晶体管t3及t4。晶体管t3及t4在一些实施例中为pmos。晶体管t3及t4形成电流镜,且将读取路径p2耦接至参考电路140。在一些实施例中,参考电路140包含电阻器rref及晶体管t5。

95.基于记忆体电路100在程序操作或读取操作中,程序路径p1及读取路径p2由程序选择单元110及读取选择单元120选择性地耦接至节点vq。

96.在程序操作中,程序选择单元110及读取选择单元120断开连接读取路径p2,且将节点vq耦接至程序电压vddq。程序电压vddq足够大,因此程序信号提供经由efuse电路fa的程序电流,以使efuse电路fa中的某一个efuse被烧毁。

97.在读取操作中,程序选择单元110及读取选择单元120断开连接程序路径p1,且将节点vq耦接至感测放大器130。感测放大器130基于经由efuse电路fa的电流判定逻辑高(h)或逻辑低(l)电压存在于节点vq处。若已烧毁efuse电路fa中的一个efuse,则efuse的电阻将为大,且在节点vq处的电压将为高(亦即,h)。若尚未烧毁efuse电路fa中的一个efuse,则在节点vq处的电压将为低(亦即,l)。

98.如上图示的记忆体电路100的组态是为了说明性目的而给出。记忆体电路100的各种组态在本揭示内容的一些实施例的预料范畴内。举例而言,在各种实施例中,程序选择单元110由nmos晶体管实施,且读取选择单元120由一pmos晶体管实施。

99.现在对图2进行参看。图2为根据本揭示内容的一些实施例的对应于图1中展示的efuse电路fa的efuse电路fa的电路示意图。

100.对于图2中的图示,efuse电路fa经配置为阵列,且按多个行及多个列配置。将阵列图示为具有两列及四行efuse单元。efuse单元中的每一行耦接至对应的字元线,包含例如耦接于efuse单元220的字元线wl0,且efuse单元的每一列耦接至各别两个位元线,包含例

如耦接于efuse单元220的位元线bl0及bl1。每一efuse单元可经由字元线与位元线组合个别存取。

101.图2中展示的efuse电路fa中包含的efuse单元标示为220、230、240、250、260、270、280及290。efuse单元220、240、260及280配置于连接至位元线bl0及位元线bl1的一个列中。efuse单元230、250、270及290配置于连接至位元线bl2及位元线bl3的另一列中。efuse单元220及230配置于连接至字元线wl0的一个行中。类似地,efuse单元240及250配置于连接至字元线wl1的同一行中,efuse单元260及270配置于连接至字元线wl2的同一行中,且efuse单元280及290配置于连接至字元线wl3的同一行中。

102.每一efuse单元220至290包含两个efuse元件及一个晶体管元件,且efuse单元220至290中的每一者的组态亦指示为“1t2r”。参看图2,举例而言,efuse单元220包含efuse元件221及222,及晶体管元件223。efuse元件221及222分别耦接至位元线bl0及位元线bl1。晶体管元件223耦接于efuse元件221与222之间,且进一步耦接至字元线wl0。类似地,efuse单元240包含efuse元件241及242,及晶体管元件243。efuse元件241及242分别耦接至位元线bl0及位元线bl1。晶体管元件243耦接于efuse元件241与242之间,且进一步耦接至字元线wl1。efuse单元260包含efuse元件261及262,及晶体管元件263。efuse元件261及262分别耦接至位元线bl0及位元线bl1。晶体管元件263耦接于efuse元件261与262之间,且进一步耦接至字元线wl2。efuse单元280包含efuse元件281及282,及晶体管元件283。efuse元件281及282分别耦接至位元线bl0及位元线bl1。晶体管元件283耦接于efuse元件281与282之间,且进一步耦接至字元线wl3。

103.如上图示的efuse电路fa的组态是为了说明性目的而给出。efuse电路fa的各种组态在本揭示内容的一些实施例的预料范畴内。举例而言,在各种实施例中,字元线wl0、wl1、wl2、wl3及wl4配置成列,且位元线bl0、bl1、bl2及bl3配置成行。

104.现在对图3a进行参看。图3a为根据本揭示内容的一些实施例的对应于efuse单元(包含例如图2中展示的efuse单元220)中的一者的efuse单元300a的电路示意图。

105.对于图3a中的图示,efuse单元300a包含耦接至位元线bl0的熔丝r1、耦接至位元线bl1的熔丝r2及耦接至字元线wl0的晶体管t1。由于一个晶体管(亦即,晶体管t1)耦接至一个efuse单元(亦即,efuse单元300a)中包含的两个熔丝(亦即,熔丝r1及r2),因此此efuse单元的组态亦指示为“1t2r”。换言之,对于作为1t2r的efuse单元,一个字元线(例如,wl0)及两个位元线(例如,bl0及bl1)包含于一个单元中,以便在由一个字元线及两个位元线控制的程序操作中操作两个位元。在一些实施例中,熔丝r1对应于图2中展示的efuse元件221,熔丝r2对应于图2中展示的efuse元件222,且晶体管t1对应于图2中展示的晶体管元件223。换言之,efuse单元300a图示efuse单元220的等效电路。

106.熔丝r1与熔丝r2耦接在一起,且熔丝r1及熔丝r2中的每一者耦接至晶体管t1。在一些实施例中,晶体管t1为nmos。换言之,晶体管t1经由熔丝r1耦接至位元线bl0,用于接收自位元线bl0传输的数据信号。晶体管t1亦经由熔丝r2耦接至位元线bl1,用于接收自位元线bl1传输的数据信号。此外,晶体管t1耦接至字元线wl0,用于由字元线wl0控制。

107.efuse单元300a的以上实施是为了说明性目的而提供。efuse单元300a的各种实施在本揭示内容的一些实施例的预料范畴内。举例而言,除了晶体管t1之外,efuse单元300a包含两个晶体管(未展示)。在一些实施例中,此两个晶体管为分别耦接至熔丝r1及熔丝r2

的nmos。换言之,一个晶体管耦接于熔丝r1与位元线bl0之间,用于由位元线bl0控制。另一晶体管耦接于熔丝r2与位元线bl1之间,用于由位元线bl1控制。换个方式解释,以上论述的晶体管指示为位元线选择器晶体管。

108.现在对图3b进行参看。图3b为根据本揭示内容的一些实施例的对应于图3a中展示的efuse单元300a的efuse单元的布局结构300b。对于图3b中的图示,布局结构300b包含晶体管t1、熔丝元件r1及熔丝元件r2。在布局图中,熔丝元件r1紧靠熔丝元件r2设置。在一些实施例中,熔丝元件r1与熔丝元件r2按熔丝导电区段cf1的宽度间隔开。在一些实施例中,将熔丝元件r1与熔丝元件r2指示为一对熔丝元件。对于图3b中的图示,在布局图中,将熔丝元件r1及熔丝元件r2两者配置于晶体管t1下方。在各种实施例中,在布局图中,晶体管t1与熔丝元件r1部分重叠。为了图示的简单起见,图3b仅展示布局结构300b的一部分。布局结构300b的其他元件在本揭示内容的一些实施例的预料范畴内。

109.在一些实施例中,晶体管t1亦指至少一个选择晶体管,包含例如nmos晶体管,用于由字元线wl0(其亦展示于图3a中)控制。在一些实施例中,晶体管t1对应于图3a中展示的晶体管t1。

110.在一些实施例中,熔丝元件r1及熔丝元件r2亦指efuse,且耦接在一起,用于由同一晶体管(亦即,晶体管t1)控制,且亦由包含例如bl0及bl1(其展示于图3a或图6b中)的各别位元线控制。在一些实施例中,熔丝元件r1对应于图3a中展示的熔丝r1。在其他一些实施例中,熔丝元件r2对应于图3a中展示的熔丝r2。在各种实施例中,熔丝元件r1及熔丝元件r2经由导电区段(亦即,以下参看图5a及图5b论述的导电区段cs1)耦接至晶体管t1。

111.继续参看图3b,晶体管t1包含主动区aa、多个栅极g及多个连接结构md。栅极g设置于主动区aa上方,且栅极g延伸以跨越主动区aa。栅极g单独地配置。连接结构md设置于主动区aa上方,且连接结构md延伸以跨越主动区aa。连接结构md与栅极g相互分开来配置,且按交替次序配置。

112.栅极g及连接结构md设置于字元线wl0下方。导通孔vg直接设置于栅极g上方,且将栅极g耦接至字元线wl0。栅极g经由导通孔vg耦接至字元线wl0,且用以接收自字元线wl0传输的数据信号。在一些实施例中,参看图3b,在布局图中,字元线wl0配置于晶体管t1上方。在一些其他实施例中,在布局图中,字元线wl0配置于晶体管t1下方。在各种实施例中,导通孔vg设置于连接结构md上方,且将连接结构md耦接至字元线wl0。

113.在一些实施例中,栅极g为多晶硅栅极。主动区aa由掺杂区域/区实施,以便形成包含于efuse单元300a中的晶体管t1,如在图3a中展示。在一些实施例中,主动区域aa由p型掺杂材料制成。在一些其他实施例中,主动区域aa由n型掺杂材料制成。在一些实施例中,主动区域aa经组态用于形成晶体管的通道。在替代实施例中,为了形成鳍式场效晶体管(fin field

‑

effect transistor;finfet),主动区域aa经组态用于形成鳍结构。

114.此些鳍可通过任一合适方法图案化。举例而言,此些鳍可使用一或多个光微影制程来图案化,包含双图案化或多图案化制程。通常,双图案化或多图案化制程组合光微影及自对准的制程,从而允许创造具有例如小于另外可使用单一直接光微影制程获得的图案间距小的间距的图案。举例而言,在一个实施例中,牺牲层形成于基板上,且使用光微影制程来图案化。使用自对准的制程在经图案化的牺牲层旁形成间隔物。接着移除牺牲层,且剩余间隔物可接着用以将鳍图案化。

115.在一些实施例中,在finfet中,连接结构md亦被称作鳍连接结构或鳍连接层。为了图示简单起见,晶体管t1中图示少数布局结构,包含例如栅极g及连接结构md。晶体管t1中的各种布局结构在本揭示内容的一些实施例的预料范畴内。

116.继续参看图3b,熔丝元件r1包含熔丝区段11、21、31及41、熔丝线51及熔丝壁61及63。熔丝区段11、21、31及41、熔丝线51及熔丝壁61及63中的所有者设置于晶体管t1上方的同一金属层(亦即,图5b中展示的第二金属层m2,其在下文参看图5a及图5b论述)中。在一些实施例中,参看图3b,在布局图中,熔丝区段11及21及熔丝壁61与栅极g及连接结构md部分重叠。

117.熔丝区段11、21、31及41相互分开来配置,且配置于熔丝线51的侧上。熔丝壁61及63相互分开来配置,且配置于熔丝线51的侧上。在一些实施例中,熔丝区段11及31被称作一对熔丝区段,且配置于熔丝线51的一个端的相对侧上。又,熔丝区段21及41被称作一对熔丝区段,且配置于熔丝线51的另一端的相对侧上。此外,熔丝壁61及63被称作一对熔丝壁,且配置于熔丝线51的中间的相对侧上。

118.在程序操作中,在一些实施例中,熔丝线51经烧毁,且熔丝壁61及63阻挡来自烧毁的熔丝线51的残渣(包含例如金属或氧化物),用于避免残渣干涉efuse单元的其他元件。

119.在一些实施例中,熔丝元件r1经由多个导通孔v1耦接至设置于熔丝元件r1上方的另一金属层(亦即,以下参看图6b论述的第三金属层m3)中的位元线bl0(其展示于图3a或图6b中)。在一些实施例中,参看图3b,导通孔v1配置于熔丝区段11及31及熔丝线51的部分中,用于经由导通孔v1将熔丝元件r1耦接至位元线bl0。换言之,晶体管t1经由熔丝元件r1耦接至导通孔v1,且至位元线bl0。

120.继续参看图3b,熔丝元件r2包含熔丝区段12、22、32及42、熔丝线52及熔丝壁62及64。类似于熔丝元件r1,熔丝区段12、22、32及42、熔丝线52及熔丝壁62及64中的所有者设置于设置熔丝元件r1的同一金属层中。参看图3b,熔丝导电区段cf1配置于熔丝区段21与熔丝区段12之间,用于将熔丝元件r1与熔丝元件r2相互耦接。在一些实施例中,熔丝导电区段cf1直接邻接于熔丝区段21与熔丝区段12之间配置。在一些实施例中,熔丝导电区段cf1设置于设置熔丝元件r1至r2的同一金属层中。因此,熔丝区段12经由熔丝导电区段cf1耦接至熔丝区段21。换言之,熔丝元件r1经由熔丝导电区段cf1耦接至熔丝元件r2。

121.类似于熔丝元件r1,熔丝区段12、22、32及42相互分开来配置,且配置于熔丝线52的侧上。熔丝壁62及64相互分开来配置,且配置于熔丝线52的侧上。在一些实施例中,熔丝区段12及32被称作一对熔丝区段,且配置于熔丝线52的一个端的相对侧上。又,熔丝区段22及42被称作一对熔丝区段,且配置于熔丝线52的另一端的相对侧上。此外,熔丝壁62及64被称作一对熔丝壁,且配置于熔丝线52的中间的相对侧上。

122.在程序操作中,在一些实施例中,熔丝线52经烧毁,且熔丝壁62及64阻挡来自烧毁的熔丝线52的残渣(包含例如金属或氧化物),用于避免残渣干涉efuse单元的其他元件。

123.在一些实施例中,熔丝元件r2经由导通孔v1耦接至设置于设置位元线bl0的同一金属层中的位元线bl1(其展示于图3a或图6b中)。在一些实施例中,参看图3b,导通孔v1配置于熔丝区段22及42及熔丝线52的部分中,用于经由导通孔v1将熔丝元件r2耦接至位元线bl1。换言之,晶体管t1经由熔丝元件r2耦接至导通孔v1,且至位元线bl1。

124.在一些方法中,对应于例如图3a中展示的efuse单元300a的efuse单元包含耦接至

一个位元线的一个熔丝及耦接至一个字元线的一个晶体管。efuse单元亦指示为“1t1r”。efuse单元的布局结构的大小限于金属间距规则及栅极间距。程序路径(以下参看图7论述)指在程序操作中的efuse单元的等效电路路径,且程序路径的长度对应于布局结构的大小。程序路径的长度由efuse单元的布局结构的大小实现。对应于efuse单元的程序路径的电阻随程序路径的长度愈长而增大,且其将造成efuse单元的不良效能。

125.与以上方法相比,在本揭示内容的实施例中,例如参看图3a至图3b,指示为“1t2r”的efuse单元可透过共用一个晶体管的两个熔丝来减小对应的布局结构的大小。因此,可减小程序操作中对应于efuse单元的程序路径的电阻,且可增强efuse单元的效能。

126.现在对图4a进行参看。图4a为根据本揭示内容的一些实施例的对应于efuse单元(包含例如图2中展示的efuse单元220及240)的efuse单元400a的电路示意图。

127.对于图4a中的图示,efuse单元400a包含熔丝r1、熔丝r2、熔丝r3、熔丝r4、晶体管t1及晶体管t2。由于两个晶体管(亦即,晶体管t1及t2)耦接至一个efuse单元(亦即,efuse单元400a)中包含的四个熔丝(亦即,熔丝r1至r4),因此此efuse单元的组态亦指示为“2t4r”。换言之,对于作为2t4r的efuse单元,两个字元线(例如,wl0及wl1)及两个位元线(例如,bl0及bl1)包含于一个单元中,以便在由个字元线及两个位元线控制的程序操作中操作四个位元。在一些实施例中,熔丝r1及r2及晶体管t1与在图3a中展示的efuse单元300a的彼等者相同。因此,其不在本文中作进一步详述。

128.与efuse单元300a相比,efuse单元400a进一步包含耦接至位元线bl0的熔丝r3、耦接至位元线bl1的熔丝r4及耦接至字元线wl1的晶体管t2。在一些实施例中,熔丝r3对应于图2中展示的efuse元件241,熔丝r4对应于图2中展示的efuse元件242,且晶体管t2对应于图2中展示的晶体管元件243。换言之,efuse单元400a图示efuse单元220及240的一等效电路。

129.类似于熔丝r1及r2,熔丝r3与熔丝r4耦接在一起,且熔丝r3及熔丝r4中的每一者耦接至晶体管t2。在一些实施例中,晶体管t2为nmos。换言之,晶体管t2经由熔丝r3耦接至位元线bl0用于接收自位元线bl0传输的数据信号,且晶体管t2亦经由熔丝r4耦接至位元线bl1用于接收自位元线bl1传输的数据信号。此外,晶体管t2耦接至字元线wl1,用于由字元线wl1控制。在一些实施例中,晶体管t1与t2具有相同组态或结构,且熔丝r1至r4具有相同组态或结构。

130.efuse单元400a的以上实施是为了说明性目的而提供。efuse单元400a的各种实施在本揭示内容的一些实施例的预料范畴内。举例而言,晶体管t1及t2由pmos实施。

131.现在对图4b进行参看。图4b为根据本揭示内容的一些实施例的对应于图4a中展示的efuse单元400a的efuse单元的布局结构400b。对于图4b中的图示,布局结构400b包含晶体管t1、熔丝元件r1、熔丝元件r2、晶体管t2、熔丝元件r3及熔丝元件r4。在一些实施例中,在布局图中,布局结构400b在水平方向上对称。在一些实施例中,熔丝元件r1及r2及晶体管t1与在图3b中展示的布局结构300b的彼等者相同。在一些实施例中,晶体管t2具有与晶体管t1相同的结构。因此,其不在本文中作进一步详述。

132.图4c为图示根据本揭示内容的一些实施例的横截面图的示意图400c,此横截面图是在图4b中展示的晶体管t1的栅极g中的一者的交叉线线1处检视。为了易于理解,参看图4b论述关于图4c的实施例。

133.在布局结构400b的布局图中,栅极g设置于主动区aa上方且跨越主动区aa,以及在图4c中展示。在一些实施例中,在布局结构400b的布局图中,导通孔vg设置于栅极g上方,且重叠栅极g,以及在图4c中展示。因此,在图4c中,为了图示的简单起见,示意图400c仅图示设置于主动区aa上方的两个栅极g及对应的两个导通孔vg。在一些实施例中,为了简单起见,在仅在图4c中展示且未在图4b中展示的布局图中,栅极区段cg设置于栅极g上方且重叠栅极g。在各种实施例中,栅极区段cg用以经由导通孔vg将栅极g耦接至字元线wl0或wl1。然而,本揭示内容的一些实施例不限于图4b至图4c的实施例。导通孔vg的各种位置或数目在本揭示内容的一些实施例的预料范畴内。

134.在布局结构400b的布局图中,字元线wl0及wl1设置于栅极g及连接结构md上方且跨越栅极g及连接结构md,以及在图4c中展示。在一些实施例中,字元线wl0及wl1形成于金属零(m0)层中。此m0层设置于栅极g、连接结构md及主动区aa上方。在一些实施例中,字元线wl0及wl1经由导通孔vg耦接至栅极g或连接结构md。举例而言,参看图4c,字元线wl0用以经由导通孔vg耦接至晶体管t1的栅极g(其展示于图4b中),且字元线wl1用以经由导通孔vg耦接至晶体管t2的栅极g(其展示于图4b中)。

135.与布局结构300b相比,布局结构400b进一步包含晶体管t2、熔丝元件r3及熔丝元件r4。在布局图中,晶体管t2紧靠晶体管t1配置。在布局图中,晶体管t2与熔丝元件r3及r4分开来配置。

136.在布局图中,熔丝元件r3紧靠熔丝元件r4配置。在一些实施例中,熔丝元件r3与熔丝元件r4按熔丝导电区段cf2的宽度间隔开。在一些实施例中,将熔丝元件r3与熔丝元件r4指示为与包含熔丝元件r1至r2的另一对熔丝元件不同的一对熔丝元件。对于图3b中的图示,在布局图中,将元件r3及熔丝元件r4两者配置于晶体管t1及t2下方。换言之,在布局图中,将熔丝元件r3及熔丝元件r4两者与晶体管t1及t2分开来配置。换个方式解释,将所有熔丝元件r1至r4配置为一阵列,且在布局图中,配置于晶体管t1及t2下方。为了图示的简单起见,图4b仅展示布局结构400b的一部分。布局结构400b的其他元件在本揭示内容的一些实施例的预料范畴内。

137.在一些实施例中,晶体管t2具有与晶体管t1类似的功能,且亦指用于由字元线wl1控制的至少一个选择晶体管,包含例如nmos晶体管。在一些实施例中,晶体管t2对应于图4a中展示的晶体管t2。

138.在一些实施例中,熔丝元件r3及r4具有与熔丝元件r1及r2类似的功能。熔丝元件r3及熔丝元件r4亦指efuse,且耦接在一起,用于由同一晶体管(例如,晶体管t2)控制,且亦分别由包含例如bl0及bl1(其展示于图4a中)的位元线控制。在一些实施例中,熔丝元件r3对应于图3a中展示的熔丝r3。在其他一些实施例中,熔丝元件r4对应于图3a中展示的熔丝r4。在各种实施例中,熔丝元件r3及熔丝元件r4经由导电区段(亦即,以下参看图5a及图5b论述的导电区段cs2)耦接至晶体管t2。

139.继续参看图4b,晶体管t2的栅极g经由导通孔vg耦接至字元线wl1,且用以接收自字元线wl1传输的数据信号。在一些实施例中,参看图4b,字元线wl1紧靠字元线wl0配置,且字元线wl0及wl1在布局图中配置于晶体管t1及t2上方。在各种实施例中,在布局图中,字元线wl0及wl1配置于晶体管t1及t2下方。在一些实施例中,参看图4b,在布局图中,晶体管t2的栅极g及连接结构md与熔丝区段12及22及熔丝壁62部分重叠。

140.继续参看图4b,熔丝元件r3包含熔丝区段13、23、31及41、熔丝线53及熔丝壁63及65。熔丝元件r3及熔丝元件r1共用邻近熔丝区段或邻近熔丝壁中的至少一者,包含例如熔丝区段31及41及熔丝壁63。类似于熔丝元件r1至r2,熔丝区段13、23、31及41、熔丝线53及熔丝壁63及65中的所有者设置于设置熔丝元件r1及r2的同一金属层中。

141.类似于熔丝元件r1至r2,熔丝区段13、23、31及41相互分开来配置,且配置于熔丝线53的侧上。熔丝壁63及65相互分开来配置,且配置于熔丝线53的侧上。在一些实施例中,熔丝区段31及13被称作一对熔丝区段,且配置于熔丝线53的一个端的相对侧上。又,熔丝区段41及23被称作一对熔丝区段,且配置于熔丝线53的另一端的相对侧上。此外,熔丝壁63及65被称作一对熔丝壁,且配置于熔丝线53的中间的相对侧上。

142.在程序操作中,在一些实施例中,熔丝线53经烧毁,且熔丝壁63及65阻挡来自烧毁的熔丝线53的残渣(包含例如金属或氧化物),用于避免残渣干涉efuse单元的其他元件(包含例如熔丝元件r1)。

143.在一些实施例中,熔丝元件r3经由导通孔v1耦接至设置于设置位元线bl0的同一金属层中的位元线bl0(其展示于图4a中)。在一些实施例中,参看图4b,导通孔v1配置于熔丝区段13及31及熔丝线53的部分中,用于经由导通孔v1将熔丝元件r3耦接至位元线bl0。换言之,晶体管t2经由熔丝元件r3耦接至导通孔v1,且至位元线bl0。

144.继续参看图4b,熔丝元件r4包含熔丝区段14、24、32及42、熔丝线54及熔丝壁64及66。熔丝元件r4及熔丝元件r2共用邻近熔丝区段或邻近熔丝壁中的至少一者,包含例如熔丝区段32及42及熔丝壁64。类似于熔丝元件r1至r3,熔丝区段14、24、32及42、熔丝线54及熔丝壁64及66中的所有者设置于设置熔丝元件r1至r3的同一金属层中。参看图4b,熔丝导电区段cf2配置于熔丝区段23与熔丝区段14之间,用于将熔丝元件r3与熔丝元件r4相互耦接。在一些实施例中,熔丝导电区段cf2直接邻接于熔丝区段23与熔丝区段14之间配置。在一些实施例中,熔丝导电区段cf2设置于设置熔丝元件r1至r4的同一金属层中。因此,熔丝区段23经由熔丝导电区段cf2耦接至熔丝区段14。换言之,熔丝元件r3经由熔丝导电区段cf2耦接至熔丝元件r4。在一些实施例中,导电区段cf1与导电区段cf2具有相同布局结构。

145.类似于熔丝元件r1至r3,熔丝区段14、24、32及42相互分开来配置,且配置于熔丝线54的侧上。熔丝壁64及66相互分开来配置,且配置于熔丝线54的侧上。在一些实施例中,熔丝区段32及14被称作一对熔丝区段,且配置于熔丝线54的一个端的相对侧上。又,熔丝区段42及24被称作一对熔丝区段,且配置于熔丝线54的另一端的相对侧上。此外,熔丝壁64及66被称作一对熔丝壁,且配置于熔丝线54的中间的相对侧上。

146.在程序操作中,在一些实施例中,熔丝线54经烧毁,且熔丝壁64及66阻挡来自烧毁的熔丝线54的残渣(包含例如金属或氧化物),用于避免残渣干涉efuse单元的其他元件(包含例如熔丝元件r2)。

147.在一些实施例中,熔丝元件r4经由导通孔v1耦接至设置于设置位元线bl0的同一金属层中的位元线bl1(其展示于图4a中)。在一些实施例中,参看图4b,导通孔v1配置于熔丝区段24及42及熔丝线54的部分中,用于经由导通孔v1将熔丝元件r4耦接至位元线bl1。换言之,晶体管t2经由熔丝元件r4耦接至导通孔v1,且至位元线bl1。

148.现在对图5a进行参看。图5a为根据本揭示内容的一些实施例的对应于图4a中展示的efuse单元400a的efuse单元的布局结构500a。在一些实施例中,熔丝元件r1至r4及晶体

管t1至t2与在图4b中展示的布局结构400b的彼等者相同。因此,其不在本文中作进一步详述。

149.图5b为图示根据本揭示内容的一些实施例的横截面图的示意图500b。此横截面图是在图5a中展示的晶体管t1的连接结构md中的一者的交叉线线2处检视。为了易于理解,参看图5a论述关于图5b的实施例。

150.与布局结构400b相比,布局结构500a进一步包含导电区段cs1及导电区段cs2。

151.在布局结构500a的布局图中,连接结构md设置于主动区aa上方且跨越主动区aa,以及在图5b中展示。在一些实施例中,导通孔vd设置于连接结构md上方且重叠连接结构md,为了简单起见,其仅展示于图5b中且未展示于图5a中。因此,在图5b中,为了图示的简单起见,示意图500b仅图示设置于主动区aa上方的两个连接结构md及对应的两个导通孔vd。然而,本揭示内容的一些实施例不限于图5a至图5b的实施例。导通孔vg的各种位置或数目在本揭示内容的一些实施例的预料范畴内。

152.在布局结构500a的布局图中,字元线wl0及wl1设置于栅极g及连接结构md上方且跨越栅极g及连接结构md,以及在图5b中展示。在一些实施例中,字元线wl0及wl1形成于金属零(m0)层中。此m0层设置于栅极g、连接结构md及主动区aa上方。在一些实施例中,字元线wl0及wl1经由导通孔vd耦接至连接结构md。举例而言,参看图5b,字元线wl0用以经由导通孔vd耦接至晶体管t1的连接结构md(其展示于图5a中),且字元线wl1用以经由导通孔vd耦接至晶体管t2的连接结构md(其展示于图5a中)。

153.对于图5a中的图示,在布局结构500a的布局图中,导电区段cs1设置于晶体管t1的栅极g及连接结构md的部分上方且跨越栅极g及连接结构md的部分,以及在图5b中展示。在一些实施例中,导电区段cs1形成于设置于m0层上方的第一金属(m1)层中。在一些实施例中,导电区段cs1经由导通孔v0(图5a中未展示)耦接至字元线wl0,且经由导通孔vd耦接至晶体管t1的连接结构md。换言之,晶体管t1经由导通孔vd耦接至字元线wl0,且经由导通孔v0连接至导电区段cs1。

154.此外,在布局结构500a的布局图中,导电区段cs1亦设置于熔丝元件r1上方且与熔丝元件r1部分重叠,以及在图5b中展示。具体言之,导电区段cs1与熔丝元件r1的熔丝区段21重叠。在一些实施例中,熔丝元件r1形成于设置于m1层上方的第二金属(m2)层中。在一些实施例中,导电区段cs1经由导通孔v1耦接至熔丝元件r1。换言之,熔丝元件r1经由导通孔v1耦接至导电区段cs1。

155.因此,熔丝元件r1经由导通孔v1耦接至导电区段cs1,经由导通孔v0耦接至字元线wl0,且经由导通孔vd耦接至晶体管t1的连接结构md。换言之,晶体管t1经由导通孔vd耦接至字元线wl0,经由导通孔v0耦接至导电区段cs1,且经由导通孔v1连接至熔丝元件r1。基于以上论述,由于熔丝元件r1耦接至熔丝元件r2,因此晶体管t1亦由与耦接至熔丝元件r1的相同路径耦接至熔丝元件r2。

156.继续参看图5a,在布局结构500a的布局图中,导电区段cs2设置于晶体管t2的栅极g及连接结构md的部分上方且跨越栅极g及连接结构md的部分,以及在图5b中展示。在一些实施例中,导电区段cs2形成于m1层中。在一些实施例中,导电区段cs1经由导通孔v0(图5a中未展示)耦接至字元线wl1,且经由导通孔vd耦接至晶体管t2的连接结构md。换言之,晶体管t2经由导通孔vd耦接至字元线wl1,且经由导通孔v0连接至导电区段cs2。

157.此外,在布局结构500a的布局图中,导电区段cs2亦设置于熔丝元件r2及r4上方且与熔丝元件r2及r4部分重叠,以及在图5b中展示。具体言之,导电区段cs2与熔丝元件r2的熔丝区段12及32及熔丝线52的部分重叠,且亦与熔丝元件r4的熔丝区段14及32及熔丝线54的部分重叠。在一些实施例中,熔丝元件r1至r4形成于m2层中。在一些实施例中,导电区段cs2经由导通孔v1耦接至熔丝元件r4。换言之,熔丝元件r4经由导通孔v1耦接至导电区段cs2。

158.因此,熔丝元件r4经由导通孔v1耦接至导电区段cs2,经由导通孔v0耦接至字元线wl1,且经由导通孔vd耦接至晶体管t2的连接结构md。换言之,晶体管t2经由导通孔vd耦接至字元线wl1,经由导通孔v0耦接至导电区段cs2,且经由导通孔v1连接至熔丝元件r4。基于以上论述,由于熔丝元件r4耦接至熔丝元件r3,因此晶体管t2亦由与耦接至熔丝元件r2的相同路径耦接至熔丝元件r3。

159.在一些实施例中,导电区段cs1的长度与导电区段cs2的长度不同。在一些实施例中,继续参看图5a,导电区段cs1的长度比导电区段cs2的长度短。在一些其他实施例中,导电区段cs1的宽度与导电区段cs2的宽度不同。在一些实施例中,继续参看图5a,导电区段cs1的宽度等于导电区段cs2的宽度。

160.在一些实施例中,导电区段cs1与cs2形成于同一金属层中,例如,参看图5b,形成于m1层中。在一些其他实施例中,导电区段cs1与cs2形成于不同金属层中,例如,导电区段cs1形成于m1层中,且导电区段cs2形成于m2层中。在各种实施例中,晶体管t1耦接至无导电区段cs1的熔丝元件r1及r2,且晶体管t2耦接至无导电区段cs2的熔丝元件r3及r4。

161.在一些方法中,对应于例如图4a中展示的efuse单元400a的efuse单元包含分别耦接至两个位元线的两个熔丝及分别耦接至两个字元线的两个晶体管。此些晶体管中的每一者耦接至一个熔丝,且此efuse单元亦指示为“2t2r”。efuse单元的布局结构的大小亦限于设计规则,包含例如熔丝的金属间距规则及晶体管的栅极间隙,且其导致程序路径的长度(以下参看图7论述)。自此,对应于efuse单元的程序路径的电阻增大,且其将造成efuse单元的不良效能。

162.与以上方法相比,在本揭示内容的实施例中,例如参看图4a至图5b,指示为“2t4r”的efuse单元可对应地按共用两个晶体管的四个熔丝且按双字元线配置来减小对应的布局结构的大小。因此,布局结构的组态经最佳化以实施efuse单元,且程序操作中对应于efuse单元的程序路径的电阻可通过efuse单元大小的减小而减小,且可进一步增强efuse单元的效能。

163.现在对图6a进行参看。图6a为根据本揭示内容的一些实施例的对应于efuse单元(包含例如图2中展示的efuse单元220、240、260及280)的efuse单元600a的电路示意图。

164.对于图6a中的图示,efuse单元600a包含熔丝r1至r8及晶体管t1至t4。由于四个晶体管(亦即,晶体管t1至t4)耦接至一个efuse单元(亦即,efuse单元600a)中包含的八个熔丝(亦即,熔丝r1至r8),因此efuse单元600a的组态亦指示为“4t8r”。换言之,对于作为4t8r的efuse单元,四个字元线(例如,wl0至wl3)及两个位元线(例如,bl0及bl1)包含于一个单元中,以便在由四个字元线及两个位元线控制的程序操作中操作八个位元。在一些实施例中,熔丝r1至r4及晶体管t1至t2与在图4a中展示的efuse单元400a的彼等者相同。因此,其不在本文中作进一步详述。

165.与efuse单元400a相比,efuse单元600a进一步包含耦接至位元线bl0的熔丝r5、耦接至位元线bl1的熔丝r6及耦接至字元线wl2的晶体管t3。此外,efuse单元600a进一步包含耦接至位元线bl0的熔丝r7、耦接至位元线bl1的熔丝r8及耦接至字元线wl3的晶体管t4。在一些实施例中,熔丝r5对应于图2中展示的efuse元件261,熔丝r6对应于图2中展示的efuse元件262,且晶体管t3对应于图2中展示的晶体管元件263。在一些实施例中,熔丝r7对应于图2中展示的efuse元件281,熔丝r8对应于图2中展示的efuse元件282,且晶体管t4对应于图2中展示的晶体管元件283。换言之,efuse单元600a图示efuse单元220、240、260及280的一等效电路。

166.类似于以上论述的efuse单元400a,一个晶体管耦接至两个熔丝,例如,熔丝r5与r6耦接在一起,且其中的每一者耦接至晶体管t3。在一些实施例中,晶体管t3为nmos。熔丝r7与r8耦接在一起,且其中的每一者耦接至晶体管t4。在一些实施例中,晶体管t4为nmos。换言之,晶体管t3经由熔丝r5耦接至位元线bl0,且晶体管t3亦经由熔丝r6耦接至位元线bl1。此外,晶体管t3耦接至字元线wl2。晶体管t4经由熔丝r7耦接至位元线bl0,且晶体管t4亦经由熔丝r8耦接至位元线bl1。此外,晶体管t4耦接至字元线wl3。

167.efuse单元600a的以上实施是为了说明性目的而提供。efuse单元600a的各种实施在本揭示内容的一些实施例的预料范畴内。举例而言,晶体管t1至t4由pmos实施。

168.现在对图6b进行参看。图6b为根据本揭示内容的一些实施例的对应于图6a中展示的efuse单元600a的efuse单元的布局结构600b。对于图6b中的图示,布局结构600b包含晶体管t1至t4、熔丝元件r1至r8。在一些实施例中,熔丝元件r1及r2及晶体管t1与在图3b中展示的布局结构300b的彼等者相同,且亦与在图4b中展示的布局结构400b或在图5a中展示的布局结构500a的彼等者相同。在一些实施例中,熔丝元件r3及r4及晶体管t2与在图4b中展示的布局结构400b或在图5a中展示的布局结构500a的彼等者相同。在一些实施例中,晶体管t1至t4具有与以上所论述相同的结构,且熔丝元件r1至r8亦具有与以上所论述相同的结构。因此,其不在本文中作进一步详述。

169.与布局结构500a相比,布局结构600b进一步包含晶体管t3至t4及熔丝元件r5至r8。在布局图中,晶体管t3至t4与晶体管t1至t2及熔丝元件r1至r5分开来配置。晶体管t3紧靠熔丝元件r7配置,且晶体管t4紧靠熔丝元件r8配置。

170.在布局图中,熔丝元件r5紧靠熔丝元件r6配置。在一些实施例中,熔丝元件r5与熔丝元件r6按熔丝导电区段(其在以上参看图3b、图4b或图5a论述)的宽度间隔开。在一些实施例中,将熔丝元件r5与熔丝元件r6指示为一对熔丝元件。对于图6b中的图示,熔丝元件r5配置于熔丝元件r3与熔丝元件r7之间,且熔丝元件r6配置于熔丝元件r4与熔丝元件r8之间。此外,在布局图中,元件r5及r6配置于晶体管t1及t2下方,且配置于晶体管t3及t4上方。换言之,在布局图中,将元件r5及熔丝元件r6两者与晶体管t1至t4分开来配置。

171.在布局图中,熔丝元件r7紧靠熔丝元件r8配置。在一些实施例中,熔丝元件r7与熔丝元件r8按熔丝导电区段(其在以上参看图3b、图4b或图5a论述)的宽度间隔开。在一些实施例中,将熔丝元件r7与熔丝元件r8指示为一对熔丝元件。对于图6b中的图示,熔丝元件r7紧靠晶体管t3配置,且熔丝元件r8紧靠晶体管t4配置。此外,在布局图中,熔丝元件r5及r6配置于晶体管t1及t2下方,且配置于晶体管t3及t4上方。换言之,在布局图中,将熔丝元件r5及熔丝元件r6两者与晶体管t1至t4分开来配置。换个方式解释,将所有熔丝元件r1至r8

配置为一阵列,且在布局图中,由晶体管t1至t4包围。为了图示的简单起见,图6b仅展示布局结构600b的一部分。布局结构600b的其他元件在本揭示内容的一些实施例的预料范畴内。

172.在一些实施例中,参看图6b,布局结构600b相对于线a上对称,但设置于字元线wl0至wl3中的一些导通孔vg除外。

173.在一些方法中,对应于例如图6a中展示的efuse单元600a的efuse单元包含分别耦接至四个位元线的四个熔丝及分别耦接至四个字元线的四个晶体管。此些晶体管中的每一者耦接至一个熔丝,且此efuse单元亦指示为“4t4r”。如上参考其他一些方法论述,程序操作中的efuse单元的电阻增大,且efuse单元的效能因此降低。

174.与以上方法相比,在本揭示内容的实施例中,例如参看图6a至图6b,指示为“4t8r”的efuse单元可对应地按共用四个晶体管的八个熔丝且按双字元线配置来减小对应的布局结构的大小。此外,对于一个efuse单元,其可一次程序化八个位元。因此,布局结构的组态经最佳化以实施efuse单元,且程序操作中对应于efuse单元的程序路径的电阻可减小,且可进一步增强efuse单元的效能。

175.现在对图7进行参看。图7为根据本揭示内容的一些实施例的用于对应于图2中展示的efuse单元中的至少一个的efuse单元的电路路径的示意图。对于图7中的图示,用于efuse单元的程序路径包含例如图3a中展示的efuse单元300a、图4a中展示的efuse单元400a或图6a中展示的efuse单元600a。将程序路径图示为图7的左侧中的实体布局,且亦图示为由图7的右侧中的等效电路路径表示。作为实体布局的程序路径对应于作为具有用于图示的相同参考编号的等效电路路径的程序路径。

176.对于图7中的图示,程序路径在电源供应器vqps与接地之间延伸。电阻器rvqps耦接于电源供应器vqps与电力开关p1(其在一些实施例中为pmos开关)之间,且电阻器rvqps与电源供应器vqps至电力开关晶体管p1的连接相关联。在pmos电力开关晶体管p1的漏极处提供电压vddq(其亦展示于图1中)。

177.程序路径进一步沿着y方向延伸至程序选择晶体管p2(在一些实施例中,其为pmos)。在一些实施例中,程序选择晶体管p2对应于图1中的读取选择单元120。在程序选择晶体管p2与电力开关晶体管p1之间的程序路径的电阻经识别为rvq_ypass,且亦指示为电阻器rvq_ypass。

178.程序路径进一步自程序选择晶体管p2延伸至efuse单元,且将其间的电阻识别为rdrop。将efuse单元的电阻识别为rfuse。此外,程序路径自efuse单元延伸至程序晶体管(例如,在图6a至图6b中展示的晶体管t1至t4中的至少一者),且将其间的电阻识别为rdrain。程序路径进一步延伸穿过选择晶体管p3(其在一些实施例中为nmos)至接地,且将其间的电阻识别为rvss。

179.下表根据以上结合图3a至图6b描述的本揭示内容的一些实施例,比较当将1t1r布局结构用于efuse单元中的每一者(其在表中指示为1t1r)时与当将改良的1t2r布局结构用于efuse单元中的每一者(其在表中指示为1t2r)时,用于5nm产生的参数。

180.参数(欧姆)1t1r1t2rrvq_ypass41.9530.83rdrop62.0642.31

共计235.55206.68

181.在一些实施例中,电阻rvq_ypass由1t2r布局结构自约41.95欧姆减小至约30.83欧姆,且电阻rdrop由此布局结构自约62.06欧姆减小至约42.31欧姆。程序路径的总电阻由1t2r布局结构自约235.55欧姆减小至约206.68欧姆。因此,在程序操作期间,efuse单元的电阻减小约15%至30%,且电流(未展示)增大约10%至20%。

182.图8a为根据本揭示内容的一些实施例的包含efuse单元的集成电路(integrated circuit;ic)布局图(包含例如图3b中展示的布局结构300b、图4b中展示的布局结构400b、图5a中展示的布局结构500a或图6b中展示的布局结构600b)的方法800a的流程图。对于图8a中的图示,方法800a包含操作s810a、s820a、s830a及s840a。参考图3a至图6b中的efuse单元及其布局结构的图8a中的方法800a的以下图示包含例示性操作。然而,图8a中的操作未必是按展示的次序执行。换言之,根据本揭示内容的各种实施例的精神及范畴,可将操作适当地添加、替换、改变次序及/或消除。

183.在操作s810a中,配置形成于第一导电层中的第一熔丝元件。在一些实施例中,第一熔丝元件对应于包含例如图2中展示的efuse元件221、图3a至图6b中展示的efuse元件r1的efuse元件。在一些实施例中,第一导电层对应于参看图5a至图5b论述的m2层。

184.在操作s820a中,配置形成于第一导电层中的第二熔丝元件,及配置耦接至第一熔丝元件的第二熔丝元件。在一些实施例中,第二熔丝元件对应于包含例如图2中展示的efuse元件222、图3a至图6b中展示的efuse元件r2的efuse元件。

185.在一些实施例中,操作s810a或操作s820a中的至少一者进一步包含如下的其他操作。配置形成于第一导电层中的熔丝线。配置设置于形成于第一导电层中的熔丝线的相对侧上的一对熔丝区段。配置设置于此对熔丝区段中的一者与另一熔丝元件(例如,若在此操作中配置第一熔丝元件,则为第二熔丝元件)之间的熔丝导电区段经配置,以将此对熔丝区段中的一者耦接至另一熔丝元件(例如,第二熔丝元件)。

186.在一些实施例中,熔丝线对应于包含例如图3b、图4b、图5a及图6b中展示的熔丝线51的熔丝线。在一些实施例中,对熔丝区段对应于包含例如图3b、图4b、图5a及图6b中展示的熔丝区段11及31的熔丝区段。在一些实施例中,熔丝导电区段对应于包含例如图3b、图4b、图5a及图6b中展示的熔丝导电区段cf1的熔丝导电区段。

187.在操作s830a中,形成于设置于第一导电层下方的第二导电层中的晶体管经配置,以经由第一熔丝元件耦接至用于接收第一数据电压的第一数据线,且经由第二熔丝元件耦接至用于接收第二数据电压的第二数据线。在一些实施例中,晶体管对应于包含例如图2中展示的晶体管元件223、图3a至图6b中展示的晶体管t1的晶体管。在一些实施例中,第二导电层对应于参看图5a至图5b论述的主动区域aa。在一些实施例中,第一数据线对应于图2至图6b中展示的位元线bl0,且第二数据线对应于图2至图6b中展示的位元线bl1。

188.在操作s840a中,产生包含第一熔丝元件、第二熔丝元件及晶体管的ic布局图。在一些实施例中,ic布局图对应于包含例如图3b中展示的布局结构300b、图4b中展示的布局结构400b、图5a中展示的布局结构500a及图6b中展示的布局结构600b的布局图。在一些实施例中,如上论述的包含efuse单元的集成电路是基于在操作s840a中产生的ic布局图来制造。

189.图8b为根据本揭示内容的一些实施例的用于制造包含efuse单元(包含例如图3a

中展示的efuse单元300a、图4a中展示的efuse单元400a或图6a中展示的efuse单元600a)的集成电路(integrated circuit;ic)的方法800b的流程图。对于图8b中的图示,方法800b包含操作s810b、s820b、s830b及s840b。

190.参看图8b,在操作s810b中,第一熔丝元件形成于第一导电层中。在一些实施例中,第一熔丝元件对应于包含例如图2中展示的efuse元件221或图3a、图4a或图6a中展示的efuse元件r1的efuse元件。在一些实施例中,第一导电层对应于如上参看图5a至图5b论述的m2层。

191.在操作s820b中,耦接至第一熔丝元件的第二熔丝元件形成于第一导电层中。在一些实施例中,第二熔丝元件对应于包含例如图2中展示的efuse元件222或图3a、图4a或图6a中展示的efuse元件r2的efuse元件。

192.在一些实施例中,操作s810b或操作s820b中的至少一者包含如下的操作。熔丝线形成于第一导电层中。设置于熔丝线的相对侧上的一对熔丝区段形成于第一导电层中。形成设置于此对熔丝区段中的一者与另一熔丝元件(例如,若在此操作中形成第一熔丝元件,则为第二熔丝元件)之间的熔丝导电区段。此熔丝导电区段经由此对熔丝区段中的一者耦接至另一熔丝区段(例如,第二熔丝元件)。

193.在操作s830b中,晶体管形成于设置于第一导电层下方的第二导电层中。在一些实施例中,晶体管对应于包含例如图2中展示的晶体管元件223、图3a、图4a或图6a中展示的晶体管t1的晶体管。在一些实施例中,第二导电层对应于参看图5a至图5b论述的主动区域aa。

194.在操作s840b中,晶体管经由第一熔丝元件耦接至用于接收第一数据电压的第一数据线,且经由第二熔丝元件耦接至用于接收第二数据电压的第二数据线。在一些实施例中,第一数据线对应于图2、图3a、图4a或图6a中展示的位元线bl0,且第二数据线对应于图2、图3a、图4a或图6a中展示的位元线bl1。

195.基于以上操作,产生包含第一熔丝元件、第二熔丝元件及晶体管的ic。在一些实施例中,ic对应于包含例如图3a中展示的efuse单元300a、图4a中展示的efuse单元400a或图6a中展示的efuse单元600a的元件。

196.参考图3a至图6b中的efuse单元及其布局结构的图8b中的方法800b的以下图示包含例示性操作。然而,图8b中的操作未必是按展示的次序执行。换言之,根据本揭示内容的各种实施例的精神及范畴,可将操作适当地添加、替换、改变次序及/或消除。

197.现在对图9进行参看。图9为根据本揭示内容的一些实施例的用于设计集成电路布局设计的电子设计自动化(electronic design automation;eda)系统900的方块图。eda系统900用以实施在图8a中揭露的方法800a或在图8b中揭露的方法800b的一或多个操作,且进一步结合图3a至图6b解释。在一些实施例中,eda系统900包含apr系统。

198.在一些实施例中,eda系统900为通用计算元件,其包含硬件处理器920及非暂时性计算机可读储存媒体960。储存媒体(即,记忆体)960尤其编码有(亦即,储存)计算机程序码(指令)961,亦即,可执行指令集合。由硬件处理器920进行的指令961的执行表示(至少部分)一eda工具,其实施例如方法800a或800b的一部分或所有。

199.处理器920经由总线950电耦接至计算机可读储存媒体960。处理器920亦由总线950电耦接至输入/输出(i/o)接口910及制造工具970。网络接口930亦经由总线950电连接至处理器920。网络接口930连接至网络940,使得处理器920及计算机可读储存媒体960能够

经由网络940连接至外部元件。处理器920用以执行在计算机可读储存媒体960中编码的计算机程序码961,以便使eda系统900可用于执行指出的处理程序及/或方法的一部分或所有。在一或多个实施例中,处理器920为中央处理单元(central processing unit;cpu)、多处理器、分散式处理系统、特殊应用集成电路(application specific integrated circuit;asic)及/或合适的处理单元。

200.在一或多个实施例中,计算机可读储存媒体960为电子、磁性、光学、电磁、红外线及/或半导体系统(或设备或元件)。举例而言,计算机可读储存媒体960包含半导体或固态记忆体、磁带、可移除式计算机磁盘、随机存取记忆体(random access memory;ram)、只读记忆体(read

‑

only memory;rom)、刚性磁盘及/或光盘。在使用光盘的一或多个实施例中,计算机可读储存媒体960包含紧密光盘只读记忆体(compact disk

‑

read only memory;cd

‑

rom)、紧密光盘读/写(compact disk

‑

read/write;cd

‑

r/w)及/或数字视频盘(digital video disc;dvd)。

201.在一或多个实施例中,储存媒体960储存用以使eda系统900(其中此执行表示(至少部分)eda工具)可用于执行指出的处理程序及/或方法的一部分或所有的计算机程序码961。在一或多个实施例中,储存媒体960亦储存有助于执行指出的处理程序及/或方法的一部分或所有的信息。在一或多个实施例中,储存媒体960储存包含如本文中揭露的这些标准单元(例如,包含在以上关于图3a至图3b论述的晶体管t1的efuse单元,或包含在以上关于图4a至图5b论述的晶体管t1至t2的efuse单元,或包含在以上关于图6a至图6b论述的晶体管t1至t4的efuse单元)的标准单元的程序库962。

202.eda系统900包含i/o接口910。i/o接口910耦接至外部电路系统。在一或多个实施例中,i/o接口910包含键盘、小键盘、鼠标、轨迹球、轨迹垫、触控式屏幕及/或游标方向键,用于将信息及命令传达给处理器920。

203.eda系统900亦包含耦接至处理器920的网络接口930。网络接口930允许eda系统900与一或多个其他计算机系统连接至的网络940通讯。网络接口930包含无线网络接口,诸如,bluetooth、wifi、wimax、gprs或wcdma;或有线网络接口,诸如,ethernet、usb或ieee

‑

1364。在一或多个实施例中,指出的处理程序及/或方法的一部分或所有实施于两个或更多个eda系统900中。

204.eda系统900亦包含耦接至处理器920的制造工具970。制造工具970用以基于由处理器920处理的设计文件及/或如上所论述的ic布局设计制造集成电路,包含例如图1中图示的集成电路100。

205.eda系统900用以经由i/o接口910接收信息。经由i/o接口910接收的信息包含指令、数据、设计规则、标准晶胞的程序库及/或其他参数中的一或多者,用于由处理器920处理。经由总线950将信息传送至处理器920。eda系统900用以经由i/o接口910接收与ui有关的信息。此信息储存于计算机可读媒体960中,作为使用者界面(user interface;ui)963。

206.在一些实施例中,指出的处理程序及/或方法的一部分或所有经实施为一单独软件应用程序,用于由一处理器执行。在一些实施例中,指出的处理程序及/或方法的一部分或所有经实施为是一额外软件应用程序的一部分的一软件应用程序。在一些实施例中,指出的处理程序及/或方法的一部分或所有经实施为至一软件应用程序的一外挂程序。在一些实施例中,指出的处理程序及/或方法中的至少一者经实施为是eda工具的一部分的一软

件应用程序。在一些实施例中,指出的处理程序及/或方法的一部分或所有经实施为由eda系统900使用的软件应用程序。在一些实施例中,使用诸如可购自cadence design systems公司的或另一合适布局产生工具产生包含标准晶胞的一布局图。

207.在一些实施例中,此些处理程序经实现为储存于非暂时性计算机可读记录媒体中的程序的函数。非暂时性计算机可读记录媒体的实例包含但不限于,外部/可移除式及/或内部/内建式储存或记忆体单元,例如,光盘(诸如,dvd)、磁盘(诸如,硬盘)、半导体记忆体(诸如,rom、ram)、记忆卡及类似者中的一或多者。

208.图10为根据一些实施例的ic制造系统1000及与其相关联的ic制造流程的方块图。在一些实施例中,基于布局图,(a)一或多个半导体光罩或(b)在半导体集成电路的一层中的至少一个元件中的至少一者是使用ic制造系统1000制造。

209.在图10中,ic制造系统1000包含在与制造ic元件1060有关的设计、开发及制造循环及/或服务中相互互动的实体,诸如,设计室1020、光罩室1030及ic制造商/制造厂(“晶圆厂”)1050。ic制造系统1000中的此些实体由通讯网络连接。在一些实施例中,通讯网络为单一网络。在一些实施例中,通讯网络为多种不同网络,诸如,企业内部网络或网际网络。此些通讯网络包含有线及/或无线通讯通道。每一实体与其他实体中的一或多者互动,且将服务提供至其他实体中的一或多者及/或接收来自其他实体中的一或多者的服务。在一些实施例中,设计室1020、光罩室1030及ic晶圆厂1050中的两个或更多个由单一较大型公司拥有。在一些实施例中,设计室1020、光罩室1030及ic晶圆厂1050中的两个或更多个共存于共同设施中,且使用共同资源。

210.设计室(或设计团队)1020产生ic设计布局图1022。ic设计布局图1022包含针对ic元件1060(例如,以上关于图1、图3a、图4a及/或图6a论述的记忆体电路100、efuse单元300a、400a及600a)设计的各种几何图案(例如,在图3b、图4b、图5a及/或图6a中描绘的布局结构)。此些几何图案对应于组成待制造的ic元件1060的各种元件的金属、氧化物或半导体层的图案。各种层组合以形成各种ic特征。举例而言,ic设计布局图1022的一部分包含待在一半导体基板(诸如,硅晶圆)及设置于此半导体基板上的各种金属层中形成的各种ic特征,诸如,主动区、栅极电极、源极及漏极、导电区段或层间互连的导通孔。设计室1020实施恰当设计程序以形成ic设计布局图1022。此设计程序包含逻辑设计、实体设计或处所及路线中的一或多者。ic设计布局图1022呈现于具有几何图案的信息的一或多个数据文件中。举例而言,ic设计布局图1022可按gdsii文件格式或dfii文件格式来表达。

211.光罩室1030包含光罩数据准备1032及光罩制造1044。光罩室1030使用ic设计布局图1022制造待用于根据ic设计布局图1022制造ic元件1060的各种层的一或多个光罩1045。光罩室1030执行光罩数据准备1032,其中ic设计布局图1022经转译成一代表性数据文件(“rdf”)。光罩数据准备1032将rdf提供至光罩制造1044。光罩制造1044包含光罩写入器。光罩写入器将rdf转换至在诸如光罩(mask)(光罩(reticle))1045或半导体晶圆1053的基板上的影像。设计布局图1022由光罩数据准备1032制造以遵照光罩写入器的特定特性及/或ic晶圆厂1050的要求。在图10中,将数据准备1032及光罩制造1044图示为分开的构件。在一些实施例中,数据准备1032与光罩制造1044可共同地被称作光罩数据准备。

212.在一些实施例中,数据准备1032包含光学接近性校正(optical proximity correction;opc),其使用微影增强技术来补偿影像误差,诸如,可自绕射、干涉、其他制程

效应及类似者引起的误差。opc调整ic设计布局图1022。在一些实施例中,数据准备1032包含另外解析度增强技术(resolution enhancement technique;ret),诸如,偏轴照射、子解析度辅助特征、相转移光罩、其他合适技术及类似者或其组合。在一些实施例中,亦使用反向微影技术(inverse lithography technology;ilt),其将opc作为一反向成像问题来处理。

213.在一些实施例中,数据准备1032包含光罩规则检查器(mask rule checker;mrc),其通过一组光罩建立规则检查已经历opc中的处理程序的ic设计布局图1022,此些光罩建立规则含有某些几何及/或连接性限制以确保充分裕度,以考量半导体制造制程中的可变性,及类似者。在一些实施例中,mrc修改ic设计布局图1022以补偿在光罩制造1044期间的限制,此可取消通过opc执行的修改的部分以便符合光罩建立规则。

214.在一些实施例中,数据准备1032包含微影制程检查(lithography process checking;lpc),其模拟将由ic晶圆厂1050实施以制造ic元件1060的处理。lpc基于ic设计布局图1022模拟此处理,以创造经模拟的制造的元件,诸如,ic元件1060。lpc模拟中的处理参数可包含与ic制造循环的各种制程相关联的参数、与用于制造ic的工具相关联的参数及/或制造制程的其他态样。lpc考量各种因素,诸如,航空影像对比度、焦点深度(depth of focus;dof)、光罩误差增强因数(mask error enhancement factor;meef)、其他合适因数及类似者或其组合。在一些实施例中,在一经模拟的制造的元件已通过lpc创造后,若经模拟的元件在形状上并不足够靠近满足设计规则,则重复opc及/或mrc以进一步改进ic设计布局图1022。

215.应理解,已为了清晰起见而简化了光罩数据准备1032的以上描述。在一些实施例中,数据准备1032包含诸如逻辑运算(logic operation;lop)的额外特征以根据制造规则修改ic设计布局图1022。另外,在数据准备1032期间应用于ic设计布局图1022的处理程序可按多种不同次序执行。

216.在数据准备1032后且在光罩制造1044期间,基于修改的ic设计布局图1022制造光罩1045或群光罩1045。在一些实施例中,光罩制造1044包含基于ic设计布局图1022执行一或多个微影曝露。在一些实施例中,使用一电子束(e束)或多个电子束的一机构来基于修改的ic设计布局图1022在光罩(mask)(光罩(photomask)或光罩(reticle))1045上形成图案。光罩1045可按各种技术形成。在一些实施例中,光罩1045是使用二进位技术形成。在一些实施例中,光罩图案包含不透明区及透明区。用以曝露已涂布于晶圆上的影像敏感性材料层(例如,光阻)的诸如紫外线(ultraviolet;uv)束的辐射束受到不透明区域阻挡,且经由透明区域透射。在一个实例中,光罩1045的二进位光罩型式包含透明基板(例如,熔融石英),及涂布于二进位光罩的不透明区中的不透明材料(例如,铬)。在另一实例中,光罩1045是使用相转移技术形成。在光罩1045的相转移光罩(phase shift mask;psm)型式中,形成于相转移光罩上的图案中的各种特征用以具有恰当相位差以增强解析度及成像品质。在各种实例中,相转移光罩可为衰减的psm或交变psm。由光罩制造1044产生的光罩用于多种制程中。举例而言,此(等)光罩用于离子植入制程中以形成半导体晶圆1053中的各种掺杂的区,用于蚀刻制程中以形成半导体晶圆1053中的各种蚀刻区,及/或用于其他合适制程中。

217.ic晶圆厂1050包含晶圆制造1052。ic晶圆厂1050为ic制造企业,其包含用于多种不同ic产品的制造的一或多个制造设施。在一些实施例中,ic晶圆厂1050为半导体铸造厂。

举例而言,可存在用于多个ic产品的前端制造的一制造设施(前段制程(front

‑

end

‑

of

‑

line;feol)制造),而第二制造设施可提供用于ic产品的互连及封装的后端制造(后段制程(back

‑

end

‑

of

‑

line;beol)制造),且第三制造设施可提供用于铸造厂企业的其他服务。

218.ic晶圆厂1050使用由光罩室1030制造的光罩1045来制造ic元件1060。因此,ic晶圆厂1050至少间接地使用ic设计布局图1022来制造ic元件1060。在一些实施例中,半导体晶圆1053是由ic晶圆厂1050使用光罩1045形成ic元件1060来制造。在一些实施例中,ic制造包含至少间接地基于ic设计布局图1022来执行一或多个微影曝露。半导体晶圆1053包含一硅基板或具有形成于其上的材料层的其他恰当基板。半导体晶圆1053进一步包含各种掺杂的区、介电特征、多级互连及类似者(在后续制造步骤形成)中的一或多者。

219.此外,实施前述实施例中的晶体管的各种电路或元件在本揭示内容的一些实施例的预期范畴内。

220.此外,在本文的一些实施例中,此些晶体管中的至少一者实施有至少一个金属氧化物半导体(metal oxide semiconductor;mos)晶体管、至少一个双极接面晶体管(bipolar junction transistor;bjt)等或其组合。实施前述实施例中的晶体管的各种电路或元件在本揭示内容的一些实施例的预期范畴内。

221.在一些实施例中,揭露一种集成电路。集成电路包含晶体管、第一熔丝元件及第二熔丝元件。此晶体管形成于第一导电层中。此第一熔丝元件形成于设置于此第一导电层上方的第二导电层中。此第二熔丝元件形成于此第二导电层中且耦接至此第一熔丝元件。此晶体管经由此第一熔丝元件耦接至用于接收第一数据信号的第一数据线,且此晶体管经由此第二熔丝元件耦接至用于接收第二数据信号的第二数据线。

222.在一些实施例中,集成电路进一步包含熔丝导电区段。此熔丝导电区段形成于此第二导电层中。此熔丝导电区段邻接于此第一熔丝元件与此第二熔丝元件之间,且将此第一熔丝元件耦接至此第二熔丝元件。

223.在一些实施例中,集成电路进一步包含导电区段。此导电区段形成于设置于此第一导电层与此第二导电层之间的第三导电层中。此导电区段、此第一熔丝元件的部分及此晶体管的部分在布局图中重叠,且此第一熔丝元件经由此导电区段耦接至此晶体管。

224.在一些实施例中,此第一熔丝元件包含熔丝线及对熔丝区段。此对熔丝区段设置于此熔丝线的相对侧上。此对熔丝区段中的一者经由形成于此第二导电层中的熔丝导电区段耦接至此第二熔丝元件。

225.在一些实施例中,此第一熔丝元件包含第一熔丝线及一对第一熔丝区段。此对第一熔丝区段设置于此第一熔丝线的一端的相对侧上。此第二熔丝元件包含第二熔丝线及一对第二熔丝区段。此对第二熔丝区段设置于此第二熔丝线的一端的相对侧上。此对此些第一熔丝区段中的一者经由形成于此第二导电层中的熔丝导电区段耦接至此对第二熔丝元件中的一者。

226.在一些实施例中,耦接至此对第二熔丝元件中的一者的此对第一熔丝区段中的一者经由形成于设置于此第一导电层与此第二导电层之间的第三导电层中的导电区段进一步耦接至此晶体管。

227.在一些实施例中,揭露一种集成电路。此集成电路包含电子熔丝单元阵列。此电子熔丝单元阵列包含按多个行及多个列配置的多个电子熔丝单元。此些电子熔丝单元包含第

一导电区段、第一晶体管及一对第一熔丝区段。此第一晶体管形成于第一导电层中。此对第一熔丝元件形成于设置于此第一导电层上方的第二导电层中。此对第一熔丝元件耦接在一起,且经由此第一导电区段耦接至此第一晶体管。此第一晶体管经由此对第一熔丝元件中的一者耦接至用于接收第一数据信号的第一数据线,且此第一晶体管经由此对第一熔丝元件中的另一者耦接至用于接收第二数据信号的第二数据线。

228.在一些实施例中,此些电子熔丝单元进一步包含第二晶体管、第一程序线及第二程序线。此第二晶体管形成于此第一导电层中且紧靠此第一晶体管设置。此第一程序线形成于设置于此第一导电层与此第二导电层之间的第三导电层中。此第一晶体管耦接至此第一程序线。此第二程序线形成于此第三导电层中且紧靠此第一程序线设置。此第二晶体管耦接至此第二程序线。在布局图中,此第一程序线及此第二程序线两者皆设置于此第一晶体管、此第二晶体管及此对第一熔丝元件中的所有者上方或下方。

229.在一些实施例中,集成电路进一步包含第三导电层。此第三导电层设置于此第一导电层与此第二导电层之间。此第一导电区段形成于此第三导电层中,且在布局图中,与此第一晶体管及此对第一熔丝元件中的一者部分重叠。

230.在一些实施例中,此对第一熔丝元件中的一者包含熔丝线、第一对熔丝区段及第二对熔丝区段。此第一对熔丝区段设置于此熔丝线的第一端的相对侧上。此第二对熔丝区段设置于此熔丝线的第二端的相对侧上。此第一端与此第二端彼此相对。在布局图中,此第一对熔丝区段中的一者与此第一导电区段重叠。在一布局图中,此第二对熔丝区段及此熔丝线的部分与此第一数据线重叠。

231.在一些实施例中,此对第一熔丝元件中的一者包含第一熔丝线及一对第一熔丝区段。此对第一熔丝区段设置于此第一熔丝线的一端的相对侧上。此对第一熔丝元件中的另一者包含第二熔丝线及一对第二熔丝区段。此对第二熔丝区段设置于此第二熔丝线的一端的相对侧上。此对第一熔丝区段中的一者经由形成于此第二导电层中的熔丝导电区段耦接至此对第二熔丝元件中的一者,且在布局图中,与此第一导电区段重叠。

232.在一些实施例中,集成电路进一步包含第一程序线及第二程序线。此第一程序线形成于设置于此第一导电层与此第二导电层之间的第三导电层中。此第一晶体管耦接至此第一程序线。此第二程序线形成于此第三导电层中且紧靠此第一程序线设置。在布局图中,此第一程序线及此第二程序线两者皆设置于此些电子熔丝单元上方或下方。此些电子熔丝单元进一步包含第二晶体管及一对第二熔丝区段。此第二晶体管形成于此第一导电层中且紧靠此第一晶体管设置。此第二晶体管耦接至此第二程序线。此对第二熔丝元件形成于此第二导电层中且由熔丝导电区段耦接在一起。在布局图中,此对第一熔丝元件设置于此对第二熔丝元件与此第二晶体管之间。此第二晶体管经由此对第二熔丝元件中的一者耦接至用于接收此第一数据信号的此第一数据线,且此第二晶体管经由此对第二熔丝元件中的另一者耦接至用于接收此第二数据信号的此第二数据线。

233.在一些实施例中,此些电子熔丝单元进一步包含第二导电区段。此第二导电区段紧靠此第一导电区段设置。此对第二熔丝元件经由此第二导电区段耦接至此第二晶体管。此第一导电区段及此第二导电区段形成于设置于此第二导电层与此第三导电层之间的第四导电层中。此第二导电区段与此第一导电区段具有不同长度。

234.在一些实施例中,集成电路进一步包含第三程序线及第四程序线。此第三程序线

形成于此第三导电层中且远离此第一程序线及此第二程序线两者设置。此第四程序线形成于此第三导电层中且紧靠此第三程序线设置。在布局图中,此第三程序线及此第四程序线两者皆设置于此些电子熔丝单元上方或下方。此些电子熔丝单元进一步包含第三晶体管、第四晶体管、一对第三熔丝元件及一对第四熔丝元件。此第三晶体管形成于此第一导电层中。此第三晶体管耦接至此第三程序线。此第四晶体管形成于此第一导电层中且紧靠此第三晶体管设置。此第四晶体管耦接至此第四程序线。此对第三熔丝元件形成于此第二导电层中且耦接在一起。此对第二熔丝元件设置于此对第一熔丝元件与此对第三熔丝元件之间。此对第四熔丝元件形成于此第二导电层中且耦接在一起。此对第三熔丝元件设置于此对第二熔丝元件与此对第四熔丝元件之间。此第三晶体管经由此对第三熔丝元件中的一者耦接至用于接收此第一数据信号的此第一数据线,且此第二晶体管经由此对第二熔丝元件中的另一者耦接至用于接收此第二数据信号的此第二数据线。

235.在一些实施例中,揭露一种制造集成电路(integrated circuit;ic)的方法。此方法包含以下操作:在此集成电路中的第一导电层中形成第一熔丝元件;在此集成电路中的此第一导电层中形成耦接至此第一熔丝元件的第二熔丝元件;在此集成电路中的设置于此第一导电层下方的第二导电层中形成晶体管;及经由此第一熔丝元件将此晶体管耦接至用于接收第一数据电压的第一数据线,及经由此第二熔丝元件将此晶体管耦接至用于接收第二数据电压的第二数据线。

236.在一些实施例中,方法进一步包含以下操作:在此第一导电层中形成熔丝导电区段;及经由此熔丝导电区段将此第一熔丝元件耦接至此第二熔丝元件。

237.在一些实施例中,方法进一步包含以下操作:在设置于此第一导电层与此第二导电层之间的第三导电层中形成导电区段;及经由此导电区段将此第一熔丝元件耦接至此晶体管。

238.在一些实施例中,方法进一步包含以下操作:在此第二导电层中形成邻接于此第一熔丝元件与此第二熔丝元件之间的熔丝导电区段;在设置于此第一导电层与此第二导电层之间的第三导电层中形成导电区段;及经由此导电区段将此第一熔丝元件耦接至此晶体管。

239.在一些实施例中,形成此第一熔丝元件的操作进一步包含以下操作:形成熔丝线;形成设置于此熔丝线的相对侧上的一对熔丝区段;形成设置于此第二熔丝元件与此对熔丝区段中的一者之间的熔丝导电区段;及经由此对熔丝区段中的一者将此熔丝导电区段耦接至此第二熔丝元件。

240.在一些实施例中,方法进一步包含以下操作:在设置于此第一导电层与此第二导电层之间的第三导电层中形成耦接于此第一熔丝元件与此晶体管之间的导电区段。

241.前文概括了若干实施例的特征,使得熟悉此项技术者可更好地理解本揭示内容的一些实施例的态样。熟悉此项技术者应了解,其可易于将本揭示内容的一些实施例用作用于设计或修改其他处理程序及结构以用于实行相同目的及/或达成本文中介绍的实施例的相同优势的基础。熟悉此项技术者亦应认识到,这些等效构造不脱离本揭示内容的一些实施例的精神及范畴,且在不脱离本揭示内容的一些实施例的精神及范畴的情况下,其可进行各种改变、取代及更改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。