1.本发明涉及一种半导体封装技术,尤其涉及一种硅穿孔结构、及硅穿孔结构的制作方法。

背景技术:

2.随着目前晶圆市场需求的急速多样化发展,积体电路(integrated circuit,ic)尺寸的微缩技术演进已迈入数十奈米之极小尺度。因此晶圆模块必须具备有轻薄短小、低成本、低耗电量、高传输效率、高度多功能异质整合(hetero-integration)、以及实时上市的需求。则不仅在晶圆层级的制造技术必须加速提升,且在晶圆模块封装层级的封装技术(package technology)上更是将面临到严峻的挑战。由于晶圆的整合变得相当复杂,封装技术也因此随着产品需求而有所改变。目前高阶产品常见的覆晶接合封装(flip chip)虽然可以解决短连线的晶圆封装问题,却只能进行单层的晶圆封装,且随着晶体管数目与信号接脚数量(i/o)遽增,覆晶接合封装亦逐渐无法应付凸块间隙小于150μm的封装需求。

3.又如所谓的多晶圆封装(multi-chip package,mcp)、pop(package on package)、pip(package in package)等类型的系统级封装技术(system in package,sip)为例,封装布局必须由二维延伸至三维,大幅增加封装技术的难度。因此,所谓的三维积体电路硅穿孔(3d integrated circuits through silicon via,3d ic tsv)技术正是可以解决上述问题的关键性技术,其可使晶圆由二维平面布局演进至三维垂直堆叠布局。其是利用三维硅穿孔的立体互连技术具有更短的导线互连路径、更低的电阻与电感、更有效率地传递讯号、电力及热能等优势。

4.三维硅穿孔的制程步骤主要依序为:(1)硅穿孔蚀刻、(2)硅穿孔填充、(3)载板接合、(4)晶圆薄化、及(5)载板脱离等等。仰赖的技术涵盖包括:硅穿孔成形技术、晶圆操纵技术、晶圆薄化技术、接合组装技术、及晶圆测试技术。此些技术涉及的制程工序繁琐,例如需要蚀刻掩膜的干蚀刻(dry etching)、及需要昂贵原料或设备的化学气相沉积(chemical vapor deposition,cvd)、化学机械平坦化(chemical-mechanical planarization,cmp),导致制造成本难以下修。而于硅穿孔蚀刻、载板接合、晶圆薄化等之步骤,常会面临加工的风险,晶圆的支撑强度若是不够,则难以防止晶圆的破裂损伤,而使良率不佳,且所付出的原料成本会居高不下。

技术实现要素:

5.解决上述的问题,本发明之主要目的在提供一种具有硅穿孔结构的半导体组件,利用三维硅穿孔的立体互连技术具有更短的导线互连路径、更低的电阻与电感、更有效率地传递讯号、电力及热能等优势。

6.根据本发明的实施方式,具有硅穿孔结构的半导体组件包括:衬底,具有第一表面、及与第一表面相对的第二表面,并设置有多个孔洞贯穿过衬底的第一表面及第二表面;穿通电极,设置于衬底的每一个孔洞内,穿通电极具有第一端面及与第一端面相对的第二

端面,第一端面位于衬底的第一表面的一侧,第二端面位于衬底的第二表面的一侧;衬层,设置于每一个孔洞的内壁,从衬底的第一表面的一侧延伸至第二表面的一侧;多个焊垫,每一个焊垫对应并覆盖穿通电极的第一端面、及位于衬底的第一表面的一侧的衬层;第一绝缘层,设置于衬底的第一表面上,并使得每个焊垫的部分表面暴露出来;多个第一导电组件,覆盖所暴露的每个焊垫及部分的第一绝缘层;第二绝缘层,覆盖衬底的第二表面、及位于衬底的第二表面的一侧的衬层;以及多个第二导电组件,覆盖每个穿通电极的第二端面,并延伸到部分的第二绝缘层上。

7.本发明之另一目的在提供一种具有硅穿孔结构的半导体组件的制作方法,将导电组件与穿通电极电性接触的面积建构得大,电连接性得以增强。

8.根据本发明的实施方式,具有硅穿孔结构的半导体组件的制作方法包括:提供衬底,衬底具有第一表面、及与第一表面相对的第二表面;在衬底内形成多个贯穿衬底的第一表面及第二表面的孔洞;形成衬层在衬底内的每一个孔洞的内壁上;在每一个孔洞内形成金属以形成穿通电极,其中穿通电极具有第一端面及与第一端面相对的第二端面,第一端面位于衬底的第一表面的一侧,第二端面位于衬底的第二表面的一侧;形成多个焊垫以覆盖穿通电极的第一端面;形成第一绝缘层在衬底的第一表面并暴露每一个焊垫的部分表面;形成第一导电组件在每一个焊垫上,且每一个焊垫与第一导电组件电性连接;对衬底相对于第一表面的一侧执行薄形化制程,使衬层暴露出衬底的第二表面;形成第二绝缘层在衬底的第二表面上;移除部分的第二绝缘层及衬层,以暴露穿通电极的第二端面;以及形成多个第二导电组件,且每一个第二导电组件覆盖穿通电极的第二端面,并延伸到部分的第二绝缘层上。

9.本发明之又一目的在提供一种具有硅穿孔结构的半导体组件的制作方法,将导电组件与硅穿孔结构的接触面积设计增大,使接合度增强,提升产品可靠度。

10.根据本发明的实施方式,具有硅穿孔结构的半导体组件的制作方法包括:提供衬底,衬底具有第一表面、及与第一表面相对的第二表面;在衬底内形成多个贯穿衬底的第一表面及第二表面的孔洞;形成衬层在衬底内的每一个孔洞的内壁上;在每个孔洞内形成金属以形成穿通电极,其中穿通电极具有第一端面及与第一端面相对的第二端面,第一端面位于衬底的第一表面的一侧,第二端面位于衬底的第二表面的一侧;形成多个焊垫以覆盖穿通电极的第一端面;形成第一绝缘层在衬底的第一表面并暴露每一个焊垫的部分表面;形成第一导电组件在每一个焊垫上,且每一个焊垫与第一导电组件电性连接;对衬底相对于第一表面的一侧执行薄形化制程,使穿通电极突出于衬底的第二表面;形成第二绝缘层以覆盖衬底的第二表面及突出的穿通电极;移除部分的第二绝缘层及衬层,以暴露穿通电极的部分的第二端面;以及形成多个第二导电组件,且每一个第二导电组件覆盖穿通电极的部分的第二端面,并延伸到部分的第二绝缘层上。

11.本发明所披露的具有硅穿孔结构的半导体组件具有良好的电连接性及电绝缘性;于另一实施例中,由于第二导电组件与硅穿孔结构的接触面积增大,使接合度增强并牢固半导体组件的支撑强度,以提升产品可靠度,使原料成本免于耗费高涨。于制作方法中,衬层与第二绝缘层的部分移除可于同一个蚀刻步骤完成,可节省制作流程的耗时与工耗。

附图说明

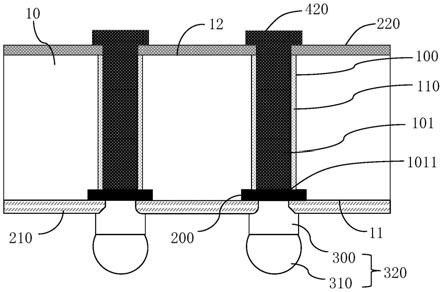

12.图1为根据本发明的第一实施态样,表示具有硅穿孔结构的半导体组件的侧视图。

13.图2a至图2h为根据本发明的第一实施态样,表示具有硅穿孔结构的半导体组件的制作方法的侧视图。

14.图3为根据本发明的第二实施态样,表示具有硅穿孔结构的半导体组件的侧视图。

15.图4a至图4h为根据本发明的第二实施态样,表示具有硅穿孔结构的半导体组件的制作方法的侧视图。

具体实施方式

16.以下详细讨论本发明的第一实施态样及第二实施态样的半导体组件结构及制作方法。应当理解的是无论如何,示出的实施态样提供了在广泛多种场景中实施的适用的发明构思。所讨论的特定的实施态样仅是制造和使用本发明的特定方式,并不是对本发明的范围的限制。

17.本发明在特定的环境中将参考示出的实施态样进行描述,也就是使用硅穿孔技术将一个半导体组件接合到另一个半导体组件上,或是将一个半导体组件接合到玻璃上。然而,本发明也可以应用到其他接合封装制程。

18.首先,参考图1说明本发明第一实施态样的具有硅穿孔结构的半导体组件,如图1所示,具有硅穿孔结构的半导体组件包括衬底10、垂直地贯穿于衬底10的穿通电极101、与穿通电极101电性连接的正面凸块320及背面凸块420。衬底10的第一表面11是位于正面侧,而衬底10的第二表面12是位于与正面侧对应的背面侧。衬底10可包括硅晶圆并且具有彼此相反的正面侧和背面侧。衬底10可以是在制造半导体内存组件、半导体逻辑组件、光电组件、显示单元等的过程中使用的衬底。正面侧可对应于与其中形成例如场效应晶体管、仿真积体电路等有源组件或电阻器、电容器、连接器等无源组件的有源区相邻的一侧,背面侧可对应于与正面侧相反的另一侧。正面凸块320设置在衬底10的第一表面11上,背面凸块420设置在衬底10的第二表面12上并与正面凸块320相对。

19.孔洞100从第一表面11贯穿衬底10直至第二表面12,利用金属填充孔洞100以形成穿通电极101,穿通电极101的金属可包括铜、银或锡。硅穿孔结构(图未示)包括穿通电极101及包围穿通电极101的内壁的衬层110。因此,衬层110设置在穿通电极101和衬底10之间,衬层110的材料为氧化物,优选为二氧化硅,衬层110从衬底10的正面侧延伸至背面侧,基本上可以防止穿通电极101中的金属原子或金属离子扩散到衬底10中。

20.穿通电极101具有第一端面1011及与第一端面1011相对的第二端面1012,穿通电极101的第一端面1011位于衬底10的正面侧,穿通电极101的第二端面1012位于衬底10的背面侧。穿通电极101的第一端面1011可与电路图案接触,使得穿通电极101电性连接到电路图案。此外,穿通电极101的第一端面1011上设置焊垫200,多个焊垫200还覆盖位于衬底10的正面侧的衬层110,由于覆盖电路图案的第一绝缘层210是位于衬底10的第一表面11,而同样位于衬底10的第一表面11的焊垫200则需要被暴露得以电性连接到电路图案,以电性连接到衬底的外部电路(图未示)。

21.用以覆盖电路图案的第一绝缘层210是形成于衬底10的第一表面11上,第一绝缘层210经图案化以使每一个焊垫200的部分表面暴露出来。第一绝缘层210的材料优选为可

被图案化的聚合物或光硬化树脂,其中以聚酰亚胺的耐热性最为优异。

22.为了与穿通电极101电性连接,正面凸块320附接到焊垫200被暴露的部分表面。正面凸块320包括设置于焊垫200上的金属层300(under bump metallurgy,ubm)、及设置在金属层300的与焊垫200相反的表面上的焊球310。金属层300优选的形状为圆柱形状,金属层300可以由至少三层导电材料形成,例如:一层镍、一层锡银合金、及一层铜,可选择在铜层的上方具有合金层而顶层为镍;焊球310可以由至少两层导电材料形成,例如一层锡银合金、及一层铜,可选择在铜层的顶层的上方具有合金层。在一实施例中,一旦在金属层300上已经形成锡层,优选为进行回流以使锡层形成期望的球点形状。另外还有其他本领域熟知的导电材料,例如钛/钛钨/铜的排列、铜/镍/金的排列或是铜/铬铜的排列,因此不限于此。

23.再者,于衬底10的背面侧,第二绝缘层220设置于衬底10的第二表面12,第二绝缘层220的材料优选为绝缘性、耐溶剂性、及耐热性良好的聚酰亚胺,第二绝缘层220可以经图案化后仅覆盖位于衬底10的背面侧且位于内壁上的衬层110,而使穿通电极101的第二端面1012暴露出来。且背面凸块420覆盖穿通电极101暴露出的完整第二端面1012,并横向延伸到部分的第二绝缘层220上。背面凸块420可以由至少三层导电材料形成,例如一层金、一层镍、及一层铜,可选择在铜层的上方具有镍层而顶层为金;也可以是由一层或两层导电材料所形成,优选的导电材料为铜、镍、锡、银、金或彼等的合金。背面凸块420与穿通电极101电性接触的面积较大,电连接性较强。此外,背面凸块420与衬底10的第二表面12之间隔着第二绝缘层220,背面凸块420与硅穿孔结构的内壁隔着衬层110,可发挥电绝缘性的效果。

24.接着,参考图2a至图2h说明本发明第一实施态样的制作方法流程。首先,如图2a所示,提供衬底10,对衬底10执行沟槽化,优选为采用蚀刻或雷射鑽孔方式在衬底10内形成多个贯穿衬底10的孔洞100,孔洞100具有从正面侧朝向背面侧延伸预定的深度。然后采用例如物理气相沉积方式(pvd)在衬底10内的每一个孔洞100的内壁上形成衬层110;且对每一个孔洞100内填充金属以形成彼此分隔开预定距离的穿通电极101,则穿通电极101具有位于衬底10的正面侧的第一端面1011、及位于衬底10的背面侧的第二端面1012。然后采用溅镀或电镀的方式对每一个穿通电极101形成多个焊垫200以覆盖穿通电极101的第一端面1011,焊垫200并未覆盖衬底10的整个第一表面11。焊垫200的材料优选为铝。

25.接着,如图2b所示,在衬底10的第一表面11涂布聚酰亚胺,聚酰亚胺经过照光或加热而硬化而形成第一绝缘层210在衬底10的第一表面11。接着对第一绝缘层210执行蚀刻,以形成图案化的第一绝缘层210,以暴露出每一个焊垫200的部分表面。

26.接着,如图2c所示,在每一个焊垫200上形成正面凸块320,包含先采用例如等离子体增强化学气相沉积(pecvd)方式在每一个焊垫200上形成金属层300,再采用溅镀、电镀、印刷、焊料迁移、或植球等方式于圆柱形状的金属层300上形成焊球310,并采用回流方式以使焊球310形成期望的球点形状。金属层300堆栈在每一个焊垫200上并覆盖部分的第一绝缘层210,以使正面凸块320通过焊垫200与穿通电极101电性连接。

27.接着,如图2d所示,翻转衬底10将背面侧朝上,以便对衬底10的背面侧执行薄形化,优选为采用研磨滚轮400研磨衬底10的背面侧,直至衬层110从衬底10的第二表面12暴露出来则停止研磨。

28.接着,如图2e所示,在衬底10的第二表面12涂布聚酰亚胺,聚酰亚胺经过照光或加热而硬化,以在衬底10的第二表面12上形成第二绝缘层220。

29.接着,如图2f及图2g所示,采用等离子体轰击等干蚀刻方式及蚀刻掩膜500对第二绝缘层220执行蚀刻,对应于穿通电极101的第二端面1012上方的第二绝缘层220及衬层110由于没有蚀刻掩膜500遮住而被去除,以形成图案化的第二绝缘层220,使穿通电极101的第二端面1012暴露出来。

30.接着,如图2h所示,采用溅镀、电镀、印刷、焊料迁移、或植球等方式于衬底10的背面侧对应穿通电极101的第二端面1012的位置形成背面凸块420。背面凸块420堆栈在每个穿通电极101的第二端面1012上并延伸覆盖到部分的第二绝缘层220上,使得背面凸块420与穿通电极101电性连接。

31.接着,参考图3说明本发明第二实施态样的具有硅穿孔结构的半导体组件,如图3所示并配合图1,于第二实施态样,衬底10的正面侧的结构配置与第一实施态样相同,于此不再赘述。不同的是衬底10的背面侧,穿通电极101的第二端面1012、及包围穿通电极101的第二端面1012的部分衬层110从衬底10的第二表面12突出。也就是说,穿通电极101的第二端面1012高于衬底10的第二表面12,则硅穿孔结构突出到衬底10的第二表面12上方。

32.第二绝缘层220设置于衬底10的第二表面12,并覆盖突出的硅穿孔结构的一端。第二绝缘层220可以经图案化后覆盖位于内壁上的衬层110、及位于穿通电极101的第二端面1012上的部分衬层110,而使穿通电极101的部分第二端面1012暴露出来。详细来说,第二绝缘层220覆盖突出的硅穿孔结构的一端,包括覆盖突出于衬底10的第二表面12的衬层110、及设置于穿通电极101部分的第二端面1012上的衬层110,但没有超过衬层110延伸覆盖到穿通电极101的整个第二端面1012。

33.背面凸块420覆盖穿通电极101暴露出的部分第二端面1012,与位于穿通电极101的第二端面1012上的部分衬层110接触,并横向延伸到部分的第二绝缘层220上。详细来说,背面凸块420包括依序堆栈在穿通电极101的部分第二端面1012上、及包围衬层110的部分第二绝缘层220上,而与位于穿通电极101的第二端面1012上的部分衬层110、及第二绝缘层220的侧壁接触。在第二实施态样中,背面凸块420覆盖突出的硅穿孔结构的一端,且背面凸块420从突出的硅穿孔结构的内壁横向延伸并覆盖于部分第二绝缘层220上。相比于只接触穿通电极101的第二端面1012(即第一实施态样)的背面凸块420,第二实施态样具有良好的电连接性及电绝缘性,此外由于背面凸块420与硅穿孔结构的接触面积增大,使接合度增强,提升产品可靠度。

34.接着,参考图4a至图4h说明本发明第二实施态样的制作方法流程。首先,如图4a所示,提供衬底10,对衬底10执行沟槽化,优选为采用蚀刻或雷射鑽孔方式在衬底10内形成多个贯穿衬底10的孔洞100,孔洞100具有从正面侧朝向背面侧延伸预定的深度。然后采用例如物理气相沉积方式在衬底10内的每一个孔洞100的内壁上形成衬层110;且对每一个孔洞100内填充金属以形成彼此分隔开预定距离的穿通电极101,则穿通电极101具有位于衬底10的正面侧的第一端面1011、及位于衬底10的背面侧的第二端面1012。然后采用溅镀或电镀的方式对每一个穿通电极101形成多个焊垫200以覆盖穿通电极101的第一端面1011,焊垫200并未覆盖衬底10的整个第一表面11。焊垫200的材料优选为铝。

35.接着,如图4b所示,在衬底10的第一表面11涂布聚酰亚胺,聚酰亚胺经过照光或加热而硬化而形成第一绝缘层210在衬底10的第一表面11。接着对第一绝缘层210执行蚀刻,以形成图案化的第一绝缘层210,使每个焊垫200的部分表面暴露出来。

36.接着,如图4c所示,在每一个焊垫200上形成正面凸块320,包含先采用例如等离子体增强化学气相沉积方式在每一个焊垫200上形成金属层300,再采用溅镀、电镀、印刷、焊料迁移、或植球等方式于圆柱形状的金属层300上形成焊球310,并采用回流方式以使焊球310形成期望的球点形状。金属层300堆栈在每一个焊垫200上并覆盖部分的第一绝缘层210,以使正面凸块320通过焊垫200与穿通电极101电性连接。

37.接着,如图4d所示,翻转衬底10将背面侧朝上,以便对衬底10的背面侧执行薄形化,优选为采用研磨滚轮400研磨衬底10的背面侧,使衬底10的第二表面12向内凹进,直至硅穿孔结构(包含衬层110及穿通电极101)从衬底10的第二表面12突出预定的高度则停止研磨。

38.接着,如图4e所示,在衬底10的背面侧涂布聚酰亚胺,聚酰亚胺经过照光或加热而硬化,以在衬底10的第二表面12上形成第二绝缘层220。第二绝缘层220覆盖于突出的硅穿孔结构的一端、及衬底10凹进的第二表面12。

39.接着,如图4f及图4g所示,使用等离子体轰击等干蚀刻方式及蚀刻掩膜500对第二绝缘层220执行蚀刻,对应于穿通电极101的第二端面1012上方的第二绝缘层220及衬层110由于没有蚀刻掩膜500遮住而被去除,以形成图案化的第二绝缘层220,使穿通电极101的部分第二端面1012暴露出来,而通电极101的第二端面1012的另一部分的上方仍覆设有第二绝缘层220及衬层110。详细来说,图案化的第二绝缘层220覆盖突出的硅穿孔结构的一端,包括覆盖突出于衬底10的第二表面12的衬层110、及设置于穿通电极101部分的第二端面1012上的衬层110,但没有超过衬层110延伸覆盖到穿通电极101的整个第二端面1012。

40.接着,如图4g所示,采用溅镀、电镀、印刷、焊料迁移、或植球等方式于衬底10的背面侧对应穿通电极101的第二端面1012的位置形成背面凸块420。背面凸块420堆栈在每个穿通电极101的第二端面1012上并延伸覆盖到部分的第二绝缘层220上,使得背面凸块420与穿通电极101电性连接。

41.以上所述仅为本发明优选的实施方式,并非用以限定本发明权利的范围;同时以上的描述,对于相关技术领域中具有通常知识者应可明了并据以实施,因此其他未脱离本发明所披露概念下所完成之等效改变或修饰,应均包含于申请专利范围中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。