基于ate设备自检的方法和系统

技术领域

1.本发明涉及ate设备领域,尤其涉及了基于ate设备自检的方法和系统。

背景技术:

2.对于ate(automatic test equipment,自动测试设备):集成了大量的硬件组件,tmu组件可以代替示波器,pmu组件可以代替万用表等;兼容一种高等语言,可以通过编程实现自动化控制;可以轻易的发送任何想要的激励。

3.在ate数字设备中,多通道任意数字波形发生器(dio)是一个核心的功能模块。此模块可通过软件进行任意通道选择,数字通道个数、组合形式多种多样。各通道根据测试向量集,可独立发送符合芯片测试需求的任意数字波形。并接收存储设备外部芯片的任意响应波形,作为鉴别被测芯片达标与否的依据。

4.例如专利名称,一种ate数字测试系统及其自检方法,专利申请号:201610867908.1,申请日期:2016

‑

09

‑

29,一种ate数字测试系统及其自检方法,该ate数字测试系统,包括地址发生器、图形存储器、指令存储器、自检存储器以及驱动器,地址发生器与图形存储器、指令存储器和自检存储器均连接,自检存储器与总线相连,图形存储器与驱动器相连。

5.现有技术不能很好地验证ate设备自身产生的任意形状的数字波形功能正确与否,不能对ate设备外部延时特性存在的差异进行自适应校准,不能动态调整验证的通道组合;对产生波形的vector正确与否;从而影响了设备功能、性能,测试自动化率。

技术实现要素:

6.本发明针对现有技术不能很好地验证ate设备自身产生的任意形状的数字波形功能正确与否,性能是否达标;从而影响了设备功能、性能测试自动化率,以及测试效率缺点,提供了基于ate设备自检的方法和系统。

7.为了解决上述技术问题,本发明通过下述技术方案得以解决:

8.基于ate设备自检的方法,包括pc端和待测设备端,其方法包括,

9.测试文件的生成,pc端生成测试文件;

10.测试执行,pc端对待测设备端依据测试用例表进行测试的执行;

11.测试校验,pc端对待测设备端测试的相关信息进行校验;

12.测试结果判断,pc端对校验后的测试结果进行判断,测试结果通过则进行测试用例判断,否则测试失败;

13.测试用例判断,pc端对待测设备端的测试用例完成则测试成功,否则重新进行待测设备端的测试校验。

14.通过对ate设备进行自检,其能够保证输出波形的正确性,性能符合测试的需求;这样有利于提高ate设备功能、性能测试自动化率以及测试效率。

15.作为优选,测试执行前需进行通道延时;pc端对待测设备端的通道延时进行测量,

从而保证待测设备端通道的同步性。通过在待测设备端的通道进行延时,从而保证数据传输过程的同步性。

16.作为优选,待测设备端的通道包括接收通道和发送通道。

17.作为优选,通道延时,pc端测量设备测试端的发送通道和接收通道进行延时,接收通道预留测量阈值不做电平比较,设备测试端测试结束时,发送通道预留同样的测量阈值不做电平比较,测量阈值为delayvalue/t,其中,delayvalue延时值,t波形周期。

18.作为优选,测试的相关信息包括测试的数据、测试的波形数量和预期错误波形。

19.作为优选,测试结果判断包括执行结果判断、运行判断和失败判断,

20.执行结果判断,设备的采样数据通道采集到实际波形数据,与期望的波形数据进行逐条对比判断;

21.运行判断,设备实际运行的vector条数与期望的vector条数对比判断;

22.失败判断,设备实际运行的失败的vector条数和期望的vctor失败条数对比判断。

23.作为优选,测试文件包括管脚资源映射文件、待测信号组文件、波形定义文件。

24.基于ate设备自检的系统,包括pc端和待测设备端,还包括测试文件生成模块、测试执行模块、测试校验模块、测试结果判断模块和测试用例判断模块;

25.测试文件生成模块,用于生成测试文件通过pc端;

26.测试执行模块,用于对待测设备端依据测试用例表进行测试的执行通过pc端;

27.测试校验模块,用于对待测设备端测试的相关信息进行校验通过pc端;

28.测试结果判断模块,用于对校验后的测试结果进行判断通过pc端,测试结果通过则进行测试用例判断,否则测试失败;

29.测试用例判断,对待测设备端的测试用例完成则测试成功,否则重新进行待测设备端的测试校验。

30.作为优选,还包括通道延时模块;用于对待测设备端的通道延时进行测量pc端,从而保证待测设备端通道的同步性。

31.本发明由于采用了以上技术方案,具有显著的技术效果:

32.通过对ate设备进行自检,其能够保证输出波形的正确性,性能符合测试的需求;这样有利于提高ate设备功能、性能、设备稳定性以及测试效率。

33.本发明通过对待测设备端的接收通道延时进行调整,从而保证数据收发过程的同步性。

附图说明

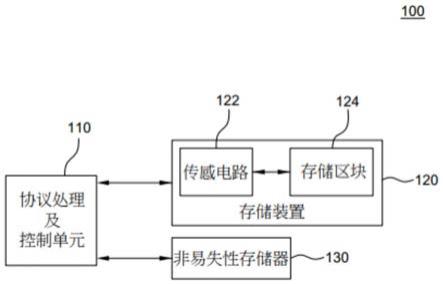

34.图1是本发明的系统图。

35.图2是本发明的通道延时图。

36.图3是本发明的流程图。

37.图4是本发明的波形发生器各要素图。

具体实施方式

38.下面结合附图1至附图3与实施例对本发明作进一步详细描述。

39.实施例1

40.基于ate设备自检的方法,包括pc端和待测设备端,其方法包括,测试文件的生成,pc端生成测试文件;测试执行,pc端对待测设备端依据测试用例表进行测试的执行;测试校验,pc端对待测设备端测试的相关信息进行校验;测试结果判断,pc端对校验后的测试结果进行判断,测试结果通过则进行测试用例判断,否则测试失败;测试用例判断,pc端对待测设备端的测试用例完成则测试成功,否则重新进行待测设备端的测试校验。

41.通过对ate设备进行自检,其能够保证输出波形的正确性,性能符合测试的需求;这样有利于提高ate设备功能、性能测试自动化率以及测试效率。

42.测试的相关信息包括测试的数据、测试的波形数量和预期错误波形。

43.测试结果判断包括执行结果判断、运行判断和失败判断,执行结果判断,设备的采样数据通道采集到实际波形数据,与期望的波形数据进行逐条对比判断;运行判断,设备实际运行的vector条数与期望的vector条数对比判断;失败判断,设备实际运行的失败的vector条数和期望的vctor失败条数对比判断。

44.测试文件包括管脚资源映射文件、待测信号组文件、波形定义文件。

45.实施例2

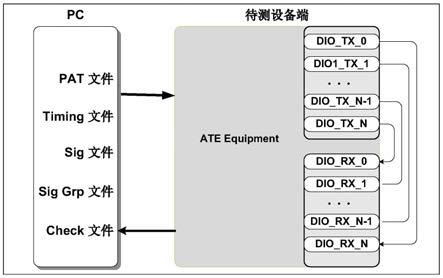

46.在实施例1基础上,本实施例测试执行前需进行通道延时;pc端对待测设备端的通道延时进行测量,从而保证待测设备端通道的同步性。通过在待测设备端的通道进行延时,从而保证数据传输过程的同步性。

47.待测设备端的通道包括接收通道和发送通道。通道延时,pc端测量设备测试端的发送通道和接收通道进行延时,接收通道预留测量阈值不做电平比较,设备测试端测试结束时,发送通道预留同样的测量阈值不做电平比较,测量阈值为delayvalue/t,其中,delayvalue延时值,t波形周期。

48.实施例3

49.基于ate设备自检的系统,包括pc端和待测设备端,还包括测试文件生成模块、测试执行模块、测试校验模块、测试结果判断模块和测试用例判断模块;

50.测试文件生成模块,用于生成测试文件通过pc端;

51.测试执行模块,用于对待测设备端依据测试用例表进行测试的执行通过pc端;

52.测试校验模块,用于对待测设备端测试的相关信息进行校验通过pc端;

53.测试结果判断模块,用于对校验后的测试结果进行判断通过pc端,测试结果通过则进行测试用例判断,否则测试失败;

54.测试用例判断,对待测设备端的测试用例完成则测试成功,否则重新进行待测设备端的测试校验。

55.通道延时模块;用于对待测设备端的通道延时进行测量pc端,从而保证待测设备端通道的同步性。

56.实施例4

57.在上述实施例基础上,制作引脚定义文件表pins.sig,此文件将板卡上所有的dio资源映射到此文件。制作资源组文件chmap.grp。此文件可将特定的一些资源绑定成一组;

58.制作波形时序文件timing.tim,测试图形对应的时序文件timing.sig;对于测试的波形由多个同一/或者不同的wavetiming组成;制作测试用例文件pat.csv,此文件定义需要发送的数字波形和期望采集到的波形;

59.制作测试用例文件表test_case.csv,此文件表需设置期望运行的pat相关文件,以及期望得到的采样失败/成功的pat个数。测试工具生成测试case的同时,同步生成理论上期望的各个case执行vctor条数,期望的失败的vctor条数,期望的波形数据。设备的采样数据通道采集到实际波形数据,与期望的波形数据进行逐条,确认执行结果正确性;设备实际运行的vector条数与期望的vector条数比对;设备实际运行的失败的vector条数和期望的vctor失败条数比对;期望的各个case执行vctor条数,期望的失败的vctor条数,期望的波形数据均符合条件则测试项通过,否则测试不通过。

60.依据附图3可知,real tx表示ate设备发送通道输出的数字波形;

‘

0/1’表示发送的高低电平。

61.exprx表示ate设备接收通道期望收到的数字波形;

‘

x’表示不关注接收的电平。

‘

h’表示期望是高电平,

‘

l’表示期望是低电平。

62.real rx表示ate设备接收通道实际收到的数字波形;

‘

x’表示不关注接收的电平。

‘

h’表示接收到高电平,

‘

l’表示接收到低电平。

63.dealy表示ate设备发送通道至接收通道存在的物理延时。设备发送数字波形和接收电平同时启动,因发送和接收直接存在时延,故接收端预留一定计算好的数字波形个数不做电平比较,同理结束时发送端的最后波形也不做电平比较。

64.具体延时值delayvalue由pcb版图得到,并且根据发送端波形周期t,得到前期不予比较的波形个数为delayvalue/t。

65.err表示ate设备接收通道收到的数字信号与期望的不符;当存在接收与预期不符时fail cnt加1。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。