1.各种实施方式总体上涉及半导体存储器装置,具体地,涉及一种包括页缓冲器的半导体存储器装置。

背景技术:

2.易失性存储器装置具有较高的写速度和读速度,但是如果其电源中断则可能丢失存储在其中的数据。非易失性存储器装置具有相对低的写速度和读速度,但是即使其电源中断也可保持存储在其中的数据。因此,为了存储无论电源如何均应该保持的数据,使用非易失性存储器装置。

3.在非易失性存储器装置当中,nand闪存装置广泛用作数据存储装置。nand闪存装置可使用多个页缓冲器来执行读取和输出存储在存储器单元中的数据所需的操作。

技术实现要素:

4.各种实施方式涉及能够减小页缓冲器的尺寸的措施。

5.在实施方式中,一种半导体存储器装置可包括:存储器单元;以及页缓冲器,其包括通过位线联接到存储器单元的感测电路。该页缓冲器可包括:包括在感测电路中的第一晶体管;以及不包括在感测电路中的第二晶体管。联接到第一晶体管的第一触点的横截面尺寸和联接到第二晶体管的第二触点的横截面尺寸可彼此不同。第二触点的横截面尺寸可小于第一触点的横截面尺寸。

6.在实施方式中,一种半导体存储器装置可包括:存储器单元阵列,该存储器单元阵列限定在层叠在逻辑结构上的存储器结构中;以及页缓冲器,该页缓冲器限定在逻辑结构中,该页缓冲器包括读取存储在存储器单元阵列中的数据的感测电路。该页缓冲器可包括:第一晶体管,该第一晶体管被包括在感测电路中;以及第二晶体管,该第二晶体管不被包括在感测电路中。联接到第一晶体管的第一触点的横截面尺寸和联接到第二晶体管的第二触点的横截面尺寸可彼此不同。

7.在实施方式中,一种半导体存储器装置可包括:存储器单元阵列,该存储器单元阵列限定在单元晶圆中;以及页缓冲器,该页缓冲器限定在结合到单元晶圆上的外围晶圆中,该页缓冲器包括读取存储在存储器单元阵列中的数据的感测电路。该页缓冲器可包括:第一晶体管,该第一晶体管被包括在感测电路中;以及第二晶体管,该第二晶体管不被包括在感测电路中。联接到第一晶体管的结区域的第一触点的横截面尺寸和联接到第二晶体管的结区域的第二触点的横截面尺寸可彼此不同。

附图说明

8.图1是示出根据本公开的实施方式的半导体存储器装置的表示的框图。

9.图2是示出图1所示的存储块之一的表示的等效电路图。

10.图3是示出图1所示的页缓冲器的表示的电路图。

11.图4是示出根据本公开的实施方式的页缓冲器的表示的电路图。

12.图5是示出配置页缓冲器的晶体管的表示的示意性横截面图。

13.图6是示出根据本公开的实施方式的配置页缓冲器的晶体管的表示的俯视图。

14.图7是沿着图6的线a-a’和b-b’截取的横截面图。

15.图8是示出根据本公开的实施方式的半导体存储器装置的表示的横截面图。

16.图9是示出根据本公开的另一实施方式的半导体存储器装置的表示的横截面图。

17.图10是示意性地示出包括根据本公开的实施方式的半导体存储器装置的存储器系统的框图。

18.图11是示意性地示出包括根据本公开的实施方式的半导体存储器装置的计算系统的框图。

具体实施方式

19.本公开的优点和特征以及实现它们的方法将从以下参照附图描述的示例性实施方式的描述而变得显而易见。然而,本公开不限于本文所公开的示例性实施方式,而是可按照各种不同的方式实现。本公开的示例性实施方式向本领域技术人员传达本公开的范围。

20.描述本公开的实施方式的附图中给出的元件的图形、尺寸、比例、角度、数量仅仅是例示性的,因此本公开不限于所示的内容。贯穿说明书,相似的标号表示相似的组件。在描述本公开时,当确定现有技术的详细描述可能使本公开的主旨或清晰度模糊时,将省略其详细描述。将理解,除非另外具体地说明,否则说明书和权利要求中所使用的术语“包括”、“具有”、“包含”等不应被解释为限于之后列出的手段。在涉及单数名词时使用不定冠词或定冠词(例如,“一个”、“一种”或“该”)的情况下,除非另外具体地说明,否则这可包括该名词的复数。

21.即使没有明确说明,本公开的实施方式中的元件也应该被解释为包括误差容限。

22.另外,在描述本公开的组件时,可使用诸如第一、第二、a、b、(a)和(b)的术语。这些仅是为了将一个组件与另一组件相区别,而非限制组件的实质、次序、顺序或数量。另外,本公开的实施方式中的组件不受这些术语限制。这些术语仅用于将一个组件与另一组件相区分。因此,如本文所使用的,在本公开的技术精神内,第一组件可以是第二组件。

23.如果组件被描述为“连接”、“联接”或“链接”到另一组件,则可意指该组件不仅可直接“连接”、“联接”或“链接”,而且可经由第三组件间接“连接”、“联接”或“链接”。在描述位置关系时,例如“在元件b上的元件a”、“在元件b上方的元件a”、“在元件b下方的元件a”以及“在元件b旁边的元件a”,除非明确地使用术语“直接”或“紧挨”,否则另一元件c可设置在元件a和元件b之间。

24.本公开的各种示例性实施方式的特征可部分或全部联接、组合或分离。技术上,各种交互和操作是可能的。各种示例性实施方式可单独地实践或组合实践。

25.以下,将参照附图详细描述本公开的实施方式的各种示例。

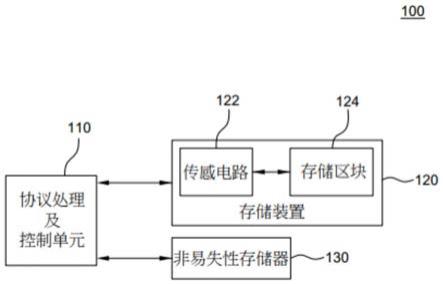

26.图1是示出根据本公开的实施方式的半导体存储器装置的表示的框图。

27.参照图1,根据本公开的实施方式的半导体存储器装置100可包括存储器单元阵列110、行解码器(x-dec)121、页缓冲器电路122和外围电路(peri电路)123。

28.存储器单元阵列110可包括多个存储块blk。尽管未示出,各个存储块blk可包括多

个存储器单元。各个存储器单元可以是易失性存储器单元,或者可以是非易失性存储器单元。尽管本文的实施方式描述了作为垂直nand闪存装置的半导体存储器装置,但是将理解,本公开的技术精神不限于此。

29.存储器单元阵列110可通过行线rl联接到行解码器121。行解码器121可响应于从外围电路123提供的行地址x_a而在存储器单元阵列110中所包括的存储块blk当中选择任一个存储块。行解码器121可将从外围电路123提供的操作电压x_v传送至与在存储器单元阵列110中所包括的存储块blk当中选择的存储块blk联接的行线rl。

30.存储器单元阵列110可通过位线bl联接到页缓冲器电路122。页缓冲器电路122可包括分别联接到位线bl的多个页缓冲器pb。页缓冲器电路122可从外围电路123接收页缓冲器控制信号pb_c,并且可向外围电路123发送数据信号data以及从外围电路123接收数据信号data。页缓冲器电路122可响应于页缓冲器控制信号pb_c来控制布置在存储器单元阵列110中的位线bl。例如,页缓冲器电路122可通过响应于页缓冲器控制信号pb_c感测存储器单元阵列110的位线bl的信号来检测存储在存储器单元阵列110的存储器单元中的数据,并且可根据所检测的数据来将数据信号data发送到外围电路123。页缓冲器电路122可响应于页缓冲器控制信号pb_c来基于从外围电路123接收的数据信号data将信号施加到位线bl,并且由此,可将数据写在存储器单元阵列110的存储器单元中。页缓冲器电路122可将数据写在与由行解码器121启用的字线联接的存储器单元中或者从该存储器单元读取数据。

31.外围电路123可从半导体存储器装置100外部的装置(例如,存储控制器)接收命令信号cmd、地址信号add和控制信号ctrl,并且可向半导体存储器装置100外部的装置发送数据data以及从其接收数据data。外围电路123可基于命令信号cmd、地址信号add和控制信号ctrl来输出用于将数据写在存储器单元阵列110中或者从存储器单元阵列110读取数据的信号(例如,行地址x_a、页缓冲器控制信号pb_c等)。外围电路123可生成半导体存储器装置100中所需的包括操作电压x_v的各种电压。

32.行解码器121、页缓冲器电路122和外围电路123可配置逻辑电路120。逻辑电路120可设置在存储器单元阵列110下方。此结构可被定义为puc(单元下外围)结构。存储器单元阵列110和逻辑电路120可在不同的晶圆上制造,然后可被结合和联接成一个。此结构可被定义为poc(单元上外围)结构。根据本公开的实施方式的半导体存储器装置100可包括puc结构或poc结构。

33.图2是示出图1所示的存储块blk之一的表示的等效电路图。

34.参照图2,存储块blk可包括与多条位线bl对应的多个单元串cstr以及公共源极线csl。

35.各个单元串cstr可联接在对应位线bl和公共源极线csl之间。各个单元串cstr可包括联接到公共源极线csl的源极选择晶体管sst、联接到位线bl的漏极选择晶体管dst以及联接在源极选择晶体管sst和漏极选择晶体管dst之间的多个存储器单元mc。源极选择晶体管sst的栅极可联接到对应源极选择线ssl。存储器单元mc的栅极可联接到对应字线wl。漏极选择晶体管dst的栅极可联接到对应漏极选择线dsl。源极选择线ssl、字线wl和漏极选择线dsl可通过在垂直方向上层叠在基板的表面上而形成三维结构。

36.包括在存储块blk中的存储器单元mc可被分成物理页单元或逻辑页单元。例如,共享字线wl并且联接到不同的单元串cstr的存储器单元mc可配置一个物理页pg。这种页可以

是读操作的基本单位。

37.图2示出在各个单元串cstr中设置一个漏极选择晶体管dst和一个源极选择晶体管sst。然而,要注意的是,在各个单元串cstr中可设置至少两个漏极选择晶体管或至少两个源极选择晶体管。

38.图3是示出图1所示的页缓冲器的表示的电路图。

39.参照图3,页缓冲器可响应于从外围电路(图1的123)提供的页缓冲器控制信号(图1的pb_c)而操作。下面要描述的参考符号blsel、pbsense、prechb、set、rst和tran可被包括在页缓冲器控制信号中。

40.页缓冲器可包括感测电路310、预充电电路320和锁存电路330。感测电路310可联接在位线bl与感测节点so之间,并且可对存储在联接到位线bl的存储器单元中的数据执行读操作。在读操作中,感测电路310可通过检测位线bl的电压电平已根据存储器单元的阈值电压而改变来读取存储在存储器单元中的数据。

41.感测电路310可包括位线选择区段311和位线感测区段312。位线选择区段311可响应于位线选择信号blsel而将位线bl和位线联接节点blcm联接。位线选择区段311可包括晶体管n1,晶体管n1联接在位线bl与位线联接节点blcm之间并响应于位线选择信号blsel而导通或截止。位线感测区段312可响应于位线感测信号pbsense而将位线联接节点blcm和感测节点so联接。位线感测区段312可包括晶体管n2,晶体管n2联接在位线联接节点blcm与感测节点so之间并响应于位线感测信号pbsense而导通或截止。

42.预充电电路320可响应于预充电信号prechb而对感测节点so进行预充电。在读操作中,预充电电路320可对要读取的存储器单元的位线bl进行预充电。预充电电路320可包括晶体管p1,晶体管p1联接在核心电压vcore与感测节点so之间并响应于预充电信号prechb而导通或截止。

43.锁存电路330可包括联接到感测节点so的多个锁存区段lc1至lc3。包括在锁存电路330中的锁存区段的数量可根据设计要求而变化。图3示出锁存电路330中包括三个锁存区段的实施方式。以下,为了说明方便,锁存区段lc1至lc3将被分别定义为第一锁存区段至第三锁存区段。

44.例如,在编程操作中,第一锁存区段lc1可暂时存储从外围电路(图1的123)提供的数据,并且可将所存储的数据传送至第二锁存区段lc2。在读操作中,第一锁存区段lc1可暂时存储从存储器单元读取的数据。在编程操作中,第二锁存区段lc2可根据从第一锁存区段lc1提供的数据来将编程禁止电压或编程允许电压施加到位线bl。在读操作中,第二锁存区段lc2可响应于位线bl的电压而暂时存储存储器单元中存储的数据,并且可将所存储的数据传送至第一锁存区段lc1。在编程操作之后执行的验证操作中,第三锁存区段lc3可存储通过比较存储器单元的阈值电压和目标电压而获得的比较结果值,并且可将与比较结果值对应的比较结果信号提供给外围电路(图1的123)。

45.第一锁存区段lc1可包括锁存器lat和多个晶体管n3至n6。锁存器lat可存储数据。晶体管n3可响应于传输信号tran而将锁存器lat的非反相节点q联接到感测节点so。晶体管n4可响应于重置信号rst而将锁存器lat的非反相节点q联接到公共节点com,并且晶体管n5可响应于设定信号set而将锁存器lat的反相节点q_n联接到公共节点com。晶体管n6可根据感测节点so的电位而将公共节点com联接到接地端子。

46.尽管未示出,第二锁存区段lc2和/或第三锁存区段lc3可具有与第一锁存区段lc1基本上相同的配置。不同信号可被提供给第一锁存区段lc1至第三锁存区段lc3。因此,尽管第一锁存区段lc1至第三锁存区段lc3可具有相同的配置,但第一锁存区段lc1至第三锁存区段lc3中的仅一个可被启用,或者第一锁存区段lc1至第三锁存区段lc3可执行不同的功能。

47.包括在页缓冲器中的晶体管n1至n6和p1可被分组为包括在感测电路310中的第一组和不包括在感测电路310中的第二组。晶体管n1和n2可被包括在第一组中,晶体管n3至n6和p1可被包括在第二组中。

48.图3的页缓冲器可通过电压感测方案读取存储在存储器单元中的数据。例如,在读操作中,可通过检测位线的电压电平已根据存储器单元的阈值电压而改变来读取存储在存储器单元中的数据。在其它实施方式中,页缓冲器可通过电流感测方案来读取存储在存储器单元中的数据。图4中示出采用电流感测方案的页缓冲器的示例。

49.图4是示出根据本公开的实施方式的页缓冲器的表示的电路图。

50.参照图4,页缓冲器可响应于从外围电路(图1的123)提供的页缓冲器控制信号(图1的pb_c)而操作。下面要描述的参考符号blsel、blpre_n、bldis、pbsense、transo、sa_prech_n、sa_csoc、sa_disch、sa_stb_n、srst、sset、trans、prechso_n、tran1、tran1_n、rst1、set1、tran2、tran2_n、rst2、set2、tranm、rst3、set3、trand、rst4和set4可被包括在页缓冲器控制信号pb_c中。

51.页缓冲器可包括感测电路410、预充电电路420和锁存电路430。感测电路410可联接到位线bl,并且可对存储在联接到位线bl的存储器单元中的数据执行读操作。也就是说,在读操作中,可通过检测位线bl的电流电平已根据存储器单元的阈值电压而改变来读取存储在存储器单元中的数据。感测电路410可包括位线选择区段411、位线充电区段412、位线感测区段413、感测节点联接区段414、电流控制区段415、感测锁存区段416和数据传输区段417。

52.位线选择区段411可响应于位线选择信号blsel而将位线bl和位线联接节点blcm联接。位线选择区段411可包括晶体管n10,晶体管n10联接在位线bl和位线联接节点blcm之间并且响应于位线选择信号blsel而导通或截止。

53.位线充电区段412可响应于位线预充电信号blpre_n而对位线联接节点blcm进行预充电,或者可响应于位线放电信号bldis而对位线联接节点blcm进行放电。位线充电区段412可包括晶体管p11,晶体管p11联接在核心电压vcore和位线联接节点blcm之间并且响应于位线预充电信号blpre_n而导通或截止。位线充电区段412还可包括晶体管n11,晶体管n11联接在位线联接节点blcm和接地端子之间并且响应于位线放电信号bldis而导通或截止。

54.位线感测区段413可响应于位线感测信号pbsense而将位线联接节点blcm和电流感测节点cso联接。位线感测区段413可包括晶体管n12,晶体管n12联接在位线联接节点blcm和电流感测节点cso之间并且响应于位线感测信号pbsense而导通或截止。

55.感测节点联接区段414可响应于节点联接信号transo而将电流感测节点cso和感测节点so联接。感测节点联接区段414可包括晶体管n13,晶体管n13联接在电流感测节点cso和感测节点so之间并且响应于节点联接信号transo而导通或截止。

56.电流控制区段415可包括基准电流发生部415a、放电部415b和电流感测部415c。基准电流发生部415a可包括晶体管p12,晶体管p12响应于感测锁存区段416的第一感测节点qs的电位而将核心电压vcore和感测放大器节点san联接。基准电流发生部415a还可包括:晶体管p13,其响应于基准电流预充电信号sa_prech_n而将感测放大器节点san和电流感测节点cso联接;以及晶体管n14,其响应于感测放大器联接信号sa_csoc而将感测放大器节点san和电流感测节点cso联接。

57.放电部415b可响应于感测放大器放电信号sa_disch和第一感测节点qs的电位而对电流感测节点cso进行放电。放电部415b可包括串联联接在电流感测节点cso与接地端子之间的晶体管n15和晶体管n16。晶体管n15可响应于感测放大器放电信号sa_disch而将电流感测节点cso和晶体管n16联接。晶体管n16可响应于第一感测节点qs的电位而将晶体管n15和接地端子联接。

58.电流感测部415c可响应于感测放大器选通信号sa_stb_n和电流感测节点cso的电位而将核心电压vcore和感测锁存区段416的第一感测节点qs联接。电流感测部415c可包括串联联接在核心电压vcore和第一感测节点qs之间的晶体管p14和晶体管n17。晶体管p14可响应于感测放大器选通信号sa_stb_n而将核心电压vcore和晶体管n17联接,并且晶体管n17可响应于电流感测节点cso的电位而将晶体管p14和第一感测节点qs联接。

59.感测锁存区段416可包括感测锁存器lats和感测锁存器重置/设置部rese。

60.感测锁存器lats可存储读取的数据。感测锁存器重置/设置部rese可联接到感测锁存器lats的第一感测节点qs和第二感测节点qs_n,并且可重置或设置感测锁存器lats。例如,感测锁存器重置/设置部rese可包括:晶体管n18,其响应于感测重置信号srst而将感测锁存器lats的第一感测节点qs和公共节点com联接;以及晶体管n19,其响应于感测设置信号sset而将感测锁存器lats的第二感测节点qs_n和公共节点com联接。

61.数据传输区段417可联接在感测锁存器lats和感测节点so之间,并且可响应于感测数据传输信号trans和第一感测节点qs的电位而改变感测节点so的电位。例如,数据传输区段417可包括串联联接在感测节点so和接地端子之间的晶体管n20和晶体管n21。晶体管n20可响应于感测数据传输信号trans而将感测节点so和晶体管n21联接,并且晶体管n21可响应于第一感测节点qs的电位而将晶体管n20和接地端子联接。预充电电路420可响应于预充电信号prechso_n而对感测节点so进行预充电。在读操作中,预充电电路420可对要读取的存储器单元的位线bl进行预充电。预充电电路420可包括晶体管p15,晶体管p15联接在核心电压vcore和感测节点so之间并且响应于预充电信号prechso_n而导通或截止。

62.锁存电路430可包括联接到感测节点so的多个锁存区段lc11至lc14。包括在锁存电路430中的锁存区段的数量可根据设计要求而变化。图4示出锁存电路430中包括四个锁存区段的实施方式。以下,为了说明方便,锁存区段lc11至lc14将被分别定义为第一至第四锁存区段。

63.第三锁存区段lc13和第四锁存区段lc14可具有与上面参照图3描述的锁存区段基本上相同的配置。因此,本文中将省略对相同配置的重复描述。当与第三锁存区段lc13和第四锁存区段lc14相比时,第一锁存区段lc11还可包括晶体管n22,晶体管n22响应于反相传输信号tran1_n而将锁存器lat1的反相节点q1_n联接到感测节点so。类似于第一锁存区段lc11,第二锁存区段lc12还可包括晶体管n23,晶体管n23响应于反相传输信号tran2_n而将

锁存器lat2的反相节点q2_n联接到感测节点so。

64.不同信号可被提供给第一锁存区段lc11至第四锁存区段lc14。因此,第一锁存区段lc11至第四锁存区段lc14中的仅一个可被启用,或者第一锁存区段lc11至第四锁存区段lc14可执行不同的功能。晶体管n24可联接在共同联接到第一锁存区段lc11至第四锁存区段lc14的公共节点com与接地端子之间。晶体管n24可响应于感测节点so的电位而对公共节点com进行放电。

65.晶体管n25可联接在感测节点so和页总线节点pbus之间。晶体管n25可响应于页数据传输信号tranpb而将感测节点so和页总线节点pbus联接。

66.下面将描述图4所示的页缓冲器的读操作。感测锁存器lats的第一感测节点qs被设定为低电平,并且流过位线bl的电流是第一基准电流。例如,如果感测锁存器lats的第一感测节点qs被设定为低电平,并且如果基准电流发生部415a的晶体管p12导通,则电流流过感测放大器节点san。接下来,如果随着位线选择信号blsel和位线感测信号pbsense上升至高电平而使晶体管n10和晶体管n12导通,并且如果随着基准电流预充电信号sa_prech_n下降至低电平而使晶体管p13导通,则第一基准电流流过电流感测节点cso和位线bl,因此,随着位线bl的电位增加,位线bl被预充电。

67.如果读电压或验证电压被施加到与所选存储器单元联接的所选字线,则流过位线bl的电流可根据存储器单元的状态而变化。例如,如果所选存储器单元的阈值电压低于读电压或验证电压,则在存储器单元中形成沟道。因此,位线bl的电位降低并且电流增加。如果所选存储器单元的阈值电压高于读电压或验证电压,则在存储器单元中不形成沟道。因此,维持位线bl的电位,并且由于此事实,电流减小。因此,根据所选存储器单元的状态,流过位线bl的电流可变得高于第一基准电流或变得低于第一基准电流。流过位线bl的电流被反映在电流感测节点cso上,并且晶体管n17可根据与电流感测节点cso的电流对应的电压电平而导通或截止。例如,如果流过电流感测节点cso的电流变得高于第一基准电流,则晶体管n17可导通,如果流过电流感测节点cso的电流维持在第一基准电流或变得低于第一基准电流,则晶体管n17可截止。此时,如果感测放大器选通信号sa_stb_n下降至低电平,进而晶体管p14导通,则根据晶体管n17的导通或截止状态,感测锁存器lats的第一感测节点qs的数据可改变或维持在先前状态。

68.包括在页缓冲器中的晶体管n10至n25和p11至p15可被分组为包括在感测电路410中的第一组和不包括在感测电路410中的第二组。晶体管n10至n21和p11至p14可被包括在第一组中,晶体管n22至n25和p15可被包括在第二组中。上面参照图3和图4描述的页缓冲器是示例性的,应该理解,本公开的页缓冲器的结构不限于此。

69.图5是示出配置页缓冲器的晶体管的表示的示意性横截面图。

70.参照图5,栅电极g可限定在基板10上方,栅极介电层gox插置在二者之间,结区域s和d可在栅电极g的两侧限定在基板10的有源区域中。结区域s和d可包括源极区域s和漏极区域d。栅极介电层gox、栅电极g、源极区域s和漏极区域d可配置晶体管。覆盖晶体管的介电层ild1可限定在基板10上,并且分别联接到源极区域s和漏极区域d的触点cnt1和cnt2可通过介电层ild1限定。参考符号10a表示用于限定有源区域的隔离层。

71.晶体管可包括从触点cnt1延伸到源极区域s,从源极区域s通过基板10中的沟道区域延伸到漏极区域d,并且从漏极区域d延伸到触点cnt2的导电路径。晶体管的驱动性能可

根据上述导电路径的特性而变化。例如,可通过在沟道区域中生成应变、增加源极区域s和漏极区域d的掺杂剂分布或降低接触电阻来实现优异的驱动性能。

72.为了实现低接触电阻,可采用增加分别联接到源极区域s和漏极区域d的触点cnt1和cnt2的横截面尺寸的方法。如果在维持晶体管的尺寸或面积的同时触点cnt1和cnt2的横截面尺寸增加,则触点cnt1和cnt2与栅电极g之间的距离d1减小,因此由于触点cnt1和cnt2引起的栅电极g的边缘电容增加。此效果可能对晶体管的驱动性能产生不利影响。为了防止由于触点的横截面尺寸的增加而引起的边缘电容的增加(这可导致晶体管的驱动性能劣化),应增加晶体管的尺寸或面积。

73.如上面参照图3和图4描述的,页缓冲器包括多个晶体管。如果联接到页缓冲器中包括的晶体管的触点的横截面尺寸增加,并且如果晶体管的尺寸也增加,则晶体管的驱动性能可改进。然而,随着页缓冲器的尺寸增加,集成度可降低。另一方面,如果联接到页缓冲器中的晶体管的触点的横截面尺寸减小,并且如果晶体管的尺寸也减小,则页缓冲器所占据的面积减小,因此,集成度可增加。然而,在任一示例中,晶体管的驱动性能可能劣化,并且页缓冲器的性能可能受影响。以下实施方式提出了能够在维持页缓冲器的性能的同时减小页缓冲器的尺寸的措施。

74.图6是示出根据本公开的实施方式的包括在页缓冲器中的晶体管的表示的俯视图。

75.参照图6,页缓冲器可包括第一晶体管tr1和第二晶体管tr2。第一晶体管tr1可以是配置页缓冲器的晶体管当中的包括在感测电路(图3的310和图4的410)中的晶体管。第二晶体管tr2可以是配置页缓冲器的晶体管当中的不包括在感测电路中的晶体管。

76.第一触点cnt11和cnt12可分别联接到第一晶体管tr1的源极区域s1和漏极区域d1。第二触点cnt21和cnt22可分别联接到第二晶体管tr2的源极区域s2和漏极区域d2。第一触点cnt11和cnt12可在参考符号ldch所指示的晶体管沟道长度方向上基本上按直线设置。第二触点cnt21和cnt22也可在晶体管沟道长度方向ldch基本上按直线设置。

77.在读操作中,页缓冲器的感测电路可通过根据存储器单元的阈值电压检测位线的经改变的电压电平或位线的电流电平来读取存储在存储器单元中的数据。因此,为了没有错误地读取存储在存储器单元中的数据,有必要在配置感测电路的第一晶体管tr1中保持高水平的驱动性能。另一方面,由于第二晶体管tr2不直接参与数据读操作,所以相对低水平的驱动性能可能足够了。

78.联接到第一晶体管tr1的第一触点cnt11和cnt12的横截面尺寸与联接到第二晶体管tr2的第二触点cnt21和cnt22的横截面尺寸可彼此不同。例如,可选择第一触点cnt11和cnt12的横截面尺寸以获得所需低接触电阻。相比之下,第二触点cnt21和cnt22的横截面尺寸可小于第一触点cnt11和cnt12的横截面尺寸。

79.触点cnt11、cnt12、cnt21和cnt22的横截面尺寸可被定义为触点cnt11、cnt12、cnt21和cnt22在任何高度处的横截面面积。第一触点cnt11和cnt12中的每一个在沟道长度方向ldch上的长度可具有第一尺寸a1。第二触点cnt21和cnt22中的每一个在沟道长度方向ldch上的长度可具有小于第一尺寸a1的第二尺寸a2。可在由形成第二触点cnt21和cnt22时所涉及的制造工艺技术设定的极限内减小第二尺寸a2。

80.可选择第一晶体管tr1的栅电极g1与第一触点cnt11或cnt12之间的距离以获得所

需低边缘电容。还可选择第二晶体管tr2的栅电极g2与第二触点cnt21或cnt22之间的距离以获得所需低边缘电容。例如,第一晶体管tr1的栅电极g1与第一触点cnt11或cnt12之间在沟道长度方向ldch上的距离以及第二晶体管tr2的栅电极g2与第二触点cnt21或cnt22之间在沟道长度方向ldch上的距离可以是相同的距离d2。

81.第二晶体管tr2在沟道长度方向ldch上的长度可具有比第一晶体管tr1在沟道长度方向ldch上的长度小l1的值。例如,l1可对应于(i)第一触点cnt11和cnt12在沟道长度方向ldch上的长度之和与(ii)第二触点cnt21和cnt22在沟道长度方向ldch上的长度之和之间的差。也就是说,l1可以是与a1和a2之间的差的两倍对应的值。

82.图7是沿着图6的线a-a’和b-b’截取的横截面图。

83.参照图7,第一晶体管tr1和第二晶体管tr2可通过基本上相同的工艺技术实现。如上面参照图6描述的,第二晶体管tr2在沟道长度方向ldch上的长度可具有比第一晶体管tr1在沟道长度方向ldch上的长度小l1的值。为了实现所需非对称晶体管tr1和tr2,可改变用于形成界定设置有晶体管tr1和tr2的有源区域的隔离层10a的工艺或者用于形成晶体管tr1和tr2的源极区域s1和s2和漏极区域d1和d2的工艺。

84.例如,为了确保第一晶体管tr1在沟道长度方向ldch上的长度和第二晶体管tr2在沟道长度方向ldch上的长度具有不同的目标值,可改变用于限定界定设置有晶体管tr1和tr2的有源区域的隔离层10a的掩模图案的形状。在另一示例中,可改变用于形成晶体管tr1和tr2的源极区域s1和s2和漏极区域d1和d2的离子注入工艺中使用的掩模图案的形状。

85.覆盖第一晶体管tr1和第二晶体管tr2的介电层ild1可限定在基板10上,并且可通过孔蚀刻工艺在介电层ild1中形成暴露第一晶体管tr1的源极区域s1和漏极区域d1并且暴露第二晶体管tr2的源极区域s2和漏极区域d2的多个接触孔。此后,当在接触孔中填充导电材料时,可配置第一触点cnt11和cnt12以及第二触点cnt21和cnt22。

86.第一触点cnt11和cnt12中的每一个在沟道长度方向ldch上的长度可具有第一尺寸a1,并且第二触点cnt21和cnt22中的每一个在沟道长度方向ldch上的长度可具有小于第一尺寸a1的第二尺寸a2。为了获得一方面第一触点cnt11和cnt12与另一方面第二触点cnt21和cnt22之间的所需横截面尺寸差异,可改变孔蚀刻工艺。例如,为了确保第一触点cnt11和cnt12的横截面尺寸和第二触点cnt21和cnt22的横截面尺寸具有不同的目标值,可提供在第一晶体管tr1的区域和第二晶体管tr2的区域中具有不同尺寸的开口的掩模图案。在另一示例中,可在孔蚀刻工艺期间为第一晶体管tr1和第二晶体管tr2中的每一个提供单独的掩模图案。可仅通过改变传统设计中的触点的目标尺寸来实现接触结构的不对称性。

87.图8是示出根据本公开的实施方式的半导体存储器装置的表示的横截面图。

88.参照图8,半导体存储器装置可具有puc(单元下外围)结构。逻辑结构ps可设置在存储器结构cs下方。

89.逻辑结构ps可包括第一基板10和限定在第一基板10上的逻辑电路logic。第一基板10可包括选自包括单晶硅层、soi(绝缘体上硅)、形成在硅锗(sige)层上的硅层、形成在介电层上的单晶硅层和形成在介电层上的多晶硅层的组中的至少一个。逻辑电路logic可包括上面参照图6和图7描述的第一晶体管tr1和第二晶体管tr2。介电层ild1可限定在第一基板10上以覆盖第一晶体管tr1和第二晶体管tr2。联接到第一晶体管tr1的第一触点cnt11和cnt12以及联接到第二晶体管tr2的第二触点cnt21和cnt22可通过介电层ild1限定。介电

层ild2可限定在介电层ild1上以覆盖第一触点cnt11和cnt12以及第二触点cnt21和cnt22。

90.存储器结构cs可包括限定在逻辑结构ps上的第二基板11、在第二基板11上交替地层叠的多个电极层40和多个层间介电层42、以及穿过多个电极层40和多个层间介电层42的多个垂直沟道ch。

91.电极层40可包括导电材料。例如,电极层40可包括选自掺杂半导体(例如,掺杂硅)、金属(例如,钨、铜或铝)、导电金属氮化物(例如,氮化钛或氮化钽)和过渡金属(例如,钛或钽)中的至少一种。层间介电层42可包括氧化硅。在电极层40当中,从最下电极层40的至少一个电极层40可配置源极选择线,从最上电极层40的至少一个电极层40可配置漏极选择线。源极选择线和漏极选择线之间的电极层40可配置字线。

92.各个垂直沟道ch可包括沟道层50和栅极介电层52。沟道层50可包括多晶硅或单晶硅,并且可在其一些区域中包括诸如硼(b)的p型杂质。栅极介电层52可包括从沟道层50的外侧壁依次层叠的隧道介电层、电荷存储层和阻挡层。在一些实施方式中,栅极介电层52可具有ono(氧化物-氮化物-氧化物)层叠结构,其中氧化物层、氮化物层和氧化物层依次层叠。源极选择晶体管、存储器单元和漏极选择晶体管可被配置在电极层40围绕垂直沟道ch的面积或区域中。

93.位线bl可限定在交替地层叠的电极层40和层间介电层42上方。位线触点blc可限定在位线bl下方以将垂直沟道ch和位线bl联接。

94.图8示出限定在存储器结构cs中的位线bl联接到逻辑结构ps的结构。布线w1可设置在位线bl上方。触点cnt3可限定在布线w1下方以将布线w1和位线bl联接。布线w1可通过触点cnt4联接到逻辑结构ps的布线w2。尽管未示出,布线w2可联接到逻辑电路logic。因此,电路径被配置为将位线bl和逻辑电路logic联接。

95.图9是示出根据本公开的另一实施方式的半导体存储器装置的表示的横截面图。

96.参照图9,半导体存储器装置可具有poc(单元上外围)结构。包括逻辑电路logic的外围晶圆pw可结合到包括存储器单元阵列的单元晶圆cw上。

97.外围晶圆pw和单元晶圆cw可单独地制造,然后彼此结合以联接成一个。逻辑电路logic可包括上面参照图6和图7描述的第一晶体管tr1和第二晶体管tr2。介电层ild1可限定在第一基板10上以覆盖第一晶体管tr1和第二晶体管tr2。联接到第一晶体管tr1的第一触点cnt11和cnt12以及联接到第二晶体管tr2的第二触点cnt21和cnt22可通过介电层ild1限定。

98.可在单元晶圆cw的第二基板11上制造存储器单元阵列。第一基板10和第二基板11可由相同的材料制成。第一基板10和第二基板11中的每一个可包括选自包括单晶硅层、soi(绝缘体上硅)、形成在硅锗(sige)层上的硅层、形成在介电层上的单晶硅层和形成在介电层上的多晶硅层的组中的至少一个。

99.第一焊盘pad1可限定在外围晶圆pw的一个表面上。尽管未详细示出,第一焊盘pad1可电联接到逻辑电路logic。第二焊盘pad2可限定在单元晶圆cw的一个表面上。各个第二焊盘pad2可通过触点cnt5联接到位线bl之一。

100.外围晶圆pw的一个表面和单元晶圆cw的一个表面可彼此结合,使得限定在外围晶圆pw的一个表面上的第一焊盘pad1和限定在单元晶圆cw的一个表面上的第二焊盘pad2彼此结合。因此,可配置将单元晶圆cw的存储器单元阵列与外围晶圆pw的逻辑电路logic联接

的电路径。

101.从以上描述显而易见的是,根据本公开的实施方式,联接到配置页缓冲器的晶体管当中的包括在感测电路中的第一晶体管的第一触点的横截面尺寸可被配置为使得第一晶体管的驱动性能保持较高,即,第一触点的电阻保持较低。另一方面,联接到配置页缓冲器的晶体管当中的不包括在感测电路中的第二晶体管的第二触点的横截面尺寸可被配置为具有小于第一触点的横截面尺寸的尺寸。因此,可使得第二晶体管的尺寸小于第一晶体管的尺寸。

102.换言之,通过将包括在页缓冲器中的晶体管分为参与页缓冲器的数据读操作的晶体管和不直接参与数据读操作的晶体管,并且通过调整联接到各个晶体管的触点的尺寸,可减小配置页缓冲器的一些晶体管的尺寸,同时维持页缓冲器的数据感测能力。结果,可在维持页缓冲器的性能的同时减小页缓冲器所占据的面积,从而有助于半导体存储器装置的经改进的集成。

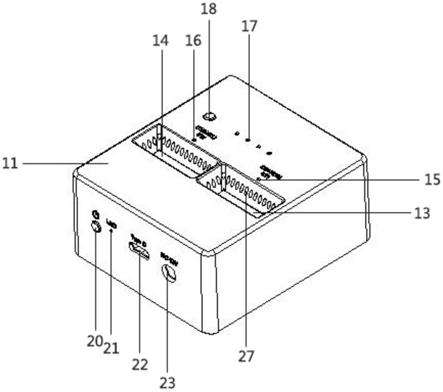

103.图10是示意性地示出包括根据本公开的实施方式的半导体存储器装置的存储器系统的框图。

104.参照图10,根据实施方式的存储器系统600可包括非易失性存储器装置(nvm装置)610和存储控制器620。

105.非易失性存储器装置610可由上述半导体存储器装置构成并且可按照上述方式操作。存储控制器620可被配置为控制非易失性存储器装置(nvm装置)610。非易失性存储器装置610和存储控制器620的组合可被配置为存储卡或者可提供固态盘(ssd)。sram 621用作处理单元(cpu)622的工作存储器。主机接口(主机i/f)623包括与存储器系统600联接的主机的数据交换协议。

106.纠错码块(ecc)624检测并纠正包括在从非易失性存储器装置(nvm装置)610读取的数据中的错误。

107.存储器接口(存储器i/f)625与本实施方式的非易失性存储器装置610接口。处理单元622执行用于存储控制器620的数据交换的一般控制操作。

108.尽管图中未示出,对于实施方式所属领域的技术人员而言显而易见的是,根据实施方式的存储器系统600可另外设置有rom,rom存储用于与主机接口的代码数据。非易失性存储器装置(nvm装置)610可作为由多个闪存芯片构成的多芯片封装来提供。

109.根据上述实施方式的存储器系统600可作为发生错误的概率低的高可靠性存储介质来提供。具体地,本实施方式的非易失性存储器装置可被包括在诸如最近正积极研究的固态盘(ssd)的存储器系统中。在这种情况下,存储控制器620可被配置为通过例如usb(通用串行总线)协议、mmc(多媒体卡)协议、pci-e(高速外围组件互连)协议、sata(串行高级技术附件)协议、pata(并行高级技术附件)协议、scsi(小型计算机系统接口)协议、esdi(增强小型磁盘接口)协议和ide(集成驱动电子设备)协议的各种接口协议之一来与外部(例如,主机)通信。

110.图11是示意性地示出包括根据本公开的实施方式的半导体存储器装置的计算系统的框图。

111.参照图11,根据实施方式的计算系统700可包括电联接到系统总线760的存储器系统710、微处理器(cpu)720、ram 730、用户接口740和调制解调器750(例如,基带芯片组)。在

根据实施方式的计算系统700是移动装置的情况下,可另外提供用于供应计算系统700的操作电压的电池(未示出)。尽管图中未示出,对于实施方式所属领域的技术人员而言显而易见的是,根据实施方式的计算系统700可另外设置有应用芯片组、相机图像处理器(cis)、移动dram等。存储器系统710可配置例如使用非易失性存储器来存储数据的ssd(固态驱动器/盘)。否则,存储器系统710可作为融合闪存(例如,onenand闪存)来提供。

112.尽管为了例示性目的描述了本公开的示例性实施方式,但本领域技术人员将理解,在不脱离本公开的范围和精神的情况下,可进行各种修改、添加和替换。因此,上面以及附图中所公开的实施方式应该仅在描述性意义上考虑,而非用于限制技术范围。本公开的技术范围不由实施方式和附图限制。本公开的精神和范围可结合所附权利要求解释并且涵盖落入所附权利要求的范围内的所有等同物。

113.相关申请的交叉引用

114.本技术要求2020年4月22日提交于韩国知识产权局的韩国专利申请no.10-2020-0048952的优先权,其整体通过引用并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。