1.本发明涉及一种差分放大器,且特别涉及一种高共模抑制比的差分放大器,其将第一电压信号放大为第二电压信号且同时能校正第二电压信号的占空比和/或相位差。

背景技术:

2.随着电子行业技术的发展,传统并行接口的速度提升愈加困难,取而代之的是速度更快的串行接口,于是原本用于光纤通信的串行解串(serializer/deserializer,serdes)系统成为了为高速串行接口的主流。serdes系统是一种时分多任务(tdm),点对点(p2p)的串行通信系统,在发送端,多路低速并行信号转换成高速串行信号,经过信道传输后,该高速串行信号在接收端重新转换成低速并行信号。serdes系统中的高速串行信号通常为差分信号,该高速串行信号具有功耗低,抗干扰强,速度快的特点。为了支持上述高速串行信号的传输,上述信道需要芯片内高速时钟的驱动,也就是说需要在serdes系统内建立高速时钟分配网络。

技术实现要素:

3.本发明的一实施例提供一种差分放大器。此差分放大器包括第一级放大电路、第二级放大电路以及交叉耦合反相器电路。第一级放大电路接收一第一输入电压信号以及一第二输入电压信号,且根据第一与第二输入电压信号产生一第一比较信号以及一第二比较信号。第二级放大电路耦接第一级放大电路,接收第一与第二比较信号,且根据第一与第二比较信号来产生第三比较信号以及第四比较信号。交叉耦合反相器电路耦接第二级放大电路,接收第三与第四比较信号,且分别根据第三与第四比较信号来产生第一输出电压信号以及第二输出电压信号。当第三与第四比较信号同时处于一第一电压电平时,交叉耦合反向器电路将第一与第二输出电压信号反相牵引至一第二电压电平。

附图说明

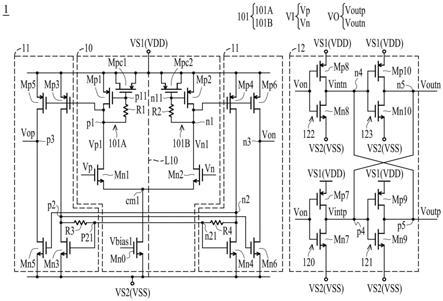

4.图1为本发明一实施例所述的差分放大器1的电路图;

5.图2a~2c分别为本发明一实施例所述的比较信号202~206的波形图;

6.图3a~3c分别为本发明一实施例所述的比较信号与输出电压信号间的占空比波形图;

7.图4a~4b分别为本发明一实施例所述的比较信号与输出电压信号间的相位差的波形图;以及

8.图5为本发明一实施例所述的差分放大器5的电路图。

具体实施方式

9.为使本发明的上述目的、特征和优点能更明显易懂,下文特举一优选实施例,并配合附图,作详细说明如下。

10.在串行解串(serializer/deserializer,serdes)系统中,每一信道通过时钟导线接收差分时钟信号,以供并行至串行信号转换。为了减少传输差分时钟信号所消耗的动态功率,serdes系统采用具有第一振幅的第一电压信号,例如采用非满摆幅(non

‑

full swing)的差分时钟信号。每一信道通过时钟导线接收该第一电压信号后,需要将其放大为具有第二振幅的第二电压信号,例如放大为满摆幅的(full swing)的差分时钟信号,与此同时,还需要使第二电压信号的占空比(duty cycle)和/或相位差符合标准,以能精确地进行并行至串行信号的转换。因此,本发明的各实施例提供了一种差分放大器,用于将第一电压信号放大为第二电压信号,并同时校准第二电压信号的占空比和/或相位差。

11.图1为本发明一实施例所述的差分放大器1的电路图。参阅图1,差分放大器1包括第一级放大电路10、第二级放大电路11以及交叉耦合反相器电路12。差分放大器1接收第一电压信号vi,并产生第二电压信号vo。第二电压信号vo的第二振幅(或第二摆幅)大于第一电压信号vi的第一振幅(或第一摆幅)。第一电压信号vi包括具有第一振幅的输入电压信号vp与vn,第二电压信号vo包括具有第二振幅的输出电压信号voutp与voutn。根据一实施例,当差分放大器1应用于serdes系统中的信道时,每一信道包括一个差分放大器1,每一差分放大器1通过一对时钟导线接收一对差分时钟信号,作为该差分放大器1的第一电压信号vi。详细来说,差分比较器1接收差分时钟信号中之一时钟信号作为第一电压信号vi的输入电压信号vp,且接收差分时钟信号中的另一时钟信号作为第一电压信号vi的另一输入电压信号vn。

12.参阅图1,第一级放大电路10包括p型晶体管mp1、mp2、mpc1与mpc2,n型晶体管mn0、mn1与mn2,以及电阻器r1与r2。在图1所示及本发明部分实施例中,所述晶体管的组件皆是以金属氧化物半导体晶体管或称为金属氧化物半导体(metal

‑

oxide

‑

semiconductor,mos)为例实现,但在其他实施例中不以此为限。n型晶体管mn1的漏极耦接节点p1,n型晶体管mn1的源极耦接共模节点cm1,n型晶体管mn1的栅极接收输入电压信号vp。n型晶体管mn2的漏极耦接节点n1,n型晶体管mn2的源极耦接共模节点cm1,n型晶体管mn2的栅极接收输入电压信号vn。

13.p型晶体管mp1的源极耦接电压源vs1,p型晶体管mp1的栅极耦接节点p11,p型晶体管mp1的漏极耦接节点p1。p型晶体管mpc1的源极与漏极耦接电压源vs1,p型晶体管mpc1的栅极耦接节点p11。基于p型晶体管mpc1的连接架构,p型晶体管mpc1相当于一电容器。电阻器r1耦接在节点p11与p1之间。上述p型晶体管mp1、p型晶体管mpc1以及电阻器r1组成有源电感101a。

14.p型晶体管mp2的源极耦接耦接电压源vs1,p型晶体管mp2的栅极耦接节点n11,p型晶体管mp2的漏极耦接节点n1。p型晶体管mpc2的源极与漏极耦接电压源vs1,p型晶体管mpc2的栅极耦接节点n11。基于p型晶体管mpc2的连接架构,p型晶体管mpc2相当于另一电容器。电阻器r2耦接在节点n11与n1之间。上述p型晶体管mp2、p型晶体管mpc2以及电阻器r2组成另一有源电感101b。有源电感101a与有源电感101b组成有源电感电路101。

15.n型晶体管mn0的源极耦接电压源vs2,n型晶体管mn0的栅极接收偏置电压vbias1,n型晶体管mn0的漏极耦接共模节点cm1。由于n型晶体管mn0的栅极接收偏置电压vbias1,n型晶体管mn0相当于一电流源。第一级放大电路10根据所接收的输入电压信号vp与vn,在节点p1上产生比较信号vp1,在节点n1上产生比较信号vn1。在此实施例中,电压源vs1提供差

分放大器1的操作电压vdd,电压源vs2提供差分放大器1的操作电压vss,其中,操作电压vdd的电压电平高于操作电压vss的电压电平。在另一实施例中,电压源vs2提供接地电压gnd。

16.参阅图1,第二级放大电路11包括p型晶体管mp3~mp6、n型晶体管mn3~mn6以及电阻器r3与r4。p型晶体管mp3的源极耦接电压源vs1,p型晶体管mp3的栅极耦接节点p1以接收比较信号vp1,p型晶体管mp3的漏极耦接节点p2。n型晶体管mn3的源极耦接电压源vs2,n型晶体管mn3的栅极耦接节点p21,n型晶体管mn3的漏极耦接节点p2。电阻器r3耦接在节点p2与p21之间。p型晶体管mp5的源极耦接电压源vs1,p型晶体管mp5的栅极耦接节点p1以接收比较信号vp1,p型晶体管mp5的漏极耦接节点p3。n型晶体管mn5的源极耦接电压源vs2,n型晶体管mn5的栅极耦接节点n2,n型晶体管mn5的漏极耦接节点p3。

17.p型晶体管mp4的源极耦接电压源vs1,p型晶体管mp4的栅极耦接节点n1以接收比较信号vn1,p型晶体管mp4的漏极耦接节点n2。n型晶体管mn4的源极耦接电压源vs2,n型晶体管mn4的栅极耦接节点n21,n型晶体管mn4的漏极耦接节点n2。电阻器r4耦接在节点n2与n21之间。p型晶体管mp6的源极耦接电压源vs1,p型晶体管mp6的栅极耦接节点n1以接收比较信号vn1,p型晶体管mp6的漏极耦接节点n3。n型晶体管mn6的源极耦接电压源vs2,n型晶体管mn6的栅极耦接节点p2,n型晶体管mn6的漏极耦接节点n3。

18.基于第一级放大电路10及第二级放大电路11的操作,第一级放大电路10及第二级放大电路11根据输入电压信号vp与vn,分别在节点p3及n3上产生比较信号vop及von。其中,输入电压信号vp可分解为共模部分与差模部分之和,而输入电压信号vn可分解为共模部分与差模部分之差,其中,该共模部分是指输入电压信号vp与输入电压信号vn之和的二分之一,该差模部分是指输入电压信号vp与输入电压信号vn之差的二分之一。对输入电压信号vp与输入电压信号vn而言,该差模部分的占空比等于(或近似于)50%,所以本发明的目的之一在于使第一级放大电路10及第二级放大电路11能够抑制该共模部分且放大该差模部分,以达到将占空比校正到50%的效果,也就是说,在于降低第一级放大电路10及第二级放大电路11的共模抑制比(common mode rejection ratio,cmmr),其中,共模抑制比是指该第一级放大电路10及第二级放大电路11对该差模部分的增益与第一级放大电路10及第二级放大电路11对该共模部分的增益之比的绝对值,共模抑制比越大,代表对该共模部分的抑制能力越强。此外,第一级放大电路10及第二级放大电路11组成n输入型放大电路,其中,n输入型是指接收输入电压信号vp与输入电压信号vn的皆为n型晶体管,因而,第一级放大电路10及第二级放大电路11适用于处理该共模部分较高的情形。

19.具体而言,第一级比较器电路10用于为差分放大器1提供较小的增益及较佳的线性度,而第二级放大电路11则用于为差分放大器1提供较大的增益。其中,第二级放大电路11包括电阻器r3与r4,电阻器r3与r4为无源器件(passive compoments),将使第二级放大电路11的线性范围增加,而避免因第一级放大电路10及第二级放大电路11的线性范围有限所致的比较信号von及vop失真,从而提高第一级放大电路10及第二级放大电路11的共模抑制比,保证第一级放大电路10及第二级放大电路11的占空比校正能力,使比较信号von及vop的占空比接近于50%。其中,第一级放大电路10采用的有源电感101a与101b,则将各自引入一零点,使差分放大器1的频率带宽增大,可以处理更高频的信号,并可以缩短差分放大器1所产生的内部信号翻转时的过渡时间,从而减少电源噪声、热噪声等所致的抖动。

20.根据本发明一实施例,在第一级放大电路10及第二级放大电路11中,关于图1中的

虚线l10轴对称的组件具有相同的尺寸。举例来说,p型晶体管mpc1与mpc2关于虚线l10轴对称且具有相同尺寸,p型晶体管mp1与mp2关于虚线l10轴对称且具有相同尺寸,n型晶体管mn1与mn2关于虚线l10轴对称且具有相同尺寸,p型晶体管mp3与mp4关于虚线l10轴对称且具有相同尺寸,p型晶体管mp5与mp6关于虚线l10轴对称且具有相同尺寸等等。此外,关于虚线l10轴对称的节点产生的信号形成差分信号,例如节点p1上的比较信号vp1与节点n1上的比较信号vn1形成一对差分信号,节点p3上的比较信号vop与节点n3上的比较信号von形成另一对差分信号。因此,关于虚线l10轴对称的电路在时钟响应上具有相同的零点与极点。

21.此外,如图1所示,差分放大器1还包括反相器电路12,以二次校正比较信号von及vop的占空比,使比较信号von及vop的占空比更接近于50%。反相器电路12包括反相器120~123。反相器120~123交叉耦合。其中,反相器120将接收到的比较信号vop反相,从而在节点p4产生反相信号vintp。反相器120包括p型晶体管mp7与n型晶体管mn7,p型晶体管mp7的漏极耦接节点p4,p型晶体管mp7的源极耦接电压源vs1,p型晶体管mp7的栅极耦接节点p3以接收比较信号vop。n型晶体管mn7的漏极耦接节点p4,n型晶体管mn7的源极耦接电压源vs2,n型晶体管mn7的栅极耦接节点p3以接收比较信号vop。反相器122将接收到的比较信号von反相,从而在节点n4产生反相信号vintn。反相器122包括p型晶体管mp8与n型晶体管mn8,p型晶体管mp8的漏极耦接节点n4,p型晶体管mp8的源极耦接电压源vs1,p型晶体管mp8的栅极耦接节点n3以接收比较信号von。n型晶体管mn8的漏极耦接节点n4,n型晶体管mn8的源极耦接电压源vs2,n型晶体管mn8的栅极耦接节点n3以接收比较信号von。

22.反相器121将接收到的反相信号vintp反相,从而在节点p5产生输出电压信号voutp。反相器121包括p型晶体管mp9与n型晶体管mn9,p型晶体管mp9的漏极耦接节点p5,p型晶体管mp9的源极耦接电压源vs1,p型晶体管mp9的栅极耦接节点p4以接收反相信号vintp。n型晶体管mn9的漏极耦接节点p5,n型晶体管mn9的源极耦接电压源vs2,n型晶体管mn9的栅极耦接节点p4以接收反相信号vintp。反相器123将接收到的反相信号vintn反相,从而在节点n5产生输出电压信号voutn。反相器123包括p型晶体管mp10与n型晶体管mn10,p型晶体管mp10的漏极耦接节点n5,p型晶体管mp10的源极耦接电压源vs1,p型晶体管mp10的栅极耦接节点n4以接收反相信号vintn。n型晶体管mn10的漏极耦接节点n5,n型晶体管mn10的源极耦接电压源vs2,n型晶体管mn10的栅极耦接节点n4以接收反相信号vintn。输出电压信号voutp与voutn组成第二电压信号vo。当差分放大器1应用于serdes系统中的信道时,第二电压信号vo用作对应的信道电路内的组件或装置的差分时钟信号。

23.参阅图1,反相器121的节点p5除了耦接晶体管mp9与mn9的漏极,更耦接产生反相信号vintn的节点n4。反相器123的节点n5除了耦接晶体管mp10与mn10的漏极,更耦接产生反相信号vintp的节点p4。从而使处理比较信号vop的反相器120~121与处理比较信号von的反相器122~123交叉耦合,即使反相器电路12为交叉耦合反相器电路。基于此交叉耦合架构,输出电压信号voutp的电平不仅受到反相信号vintp影响,亦受到节点n4上的反相信号vintn影响,且输出电压信号voutn的电平不仅受到反相信号vintn影响,亦受到节点p4上的反相信号vintp影响。反相器电路12的详细操作与此交叉耦合架构是如何影响输出电压信号voutp与voutn将在后文详细说明。

24.根据本发明一实施例,在反相器电路12中,关于图1中的虚线l10轴对称的组件也具有相同的尺寸。具体而言,反相器120与反相器122关于虚线l10轴对称且对应的器件具有

相同的尺寸,例如,p型晶体管mp7与mp8关于虚线l10轴对称且具有相同尺寸,n型晶体管mn7与mn8关于虚线l10轴对称且具有相同尺寸。反相器121与反相器123关于虚线l10轴对称且对应的器件具有相同的尺寸,例如,p型晶体管mp9与mp10关于虚线l10轴对称且具有相同尺寸,n型晶体管mn9与mn10关于虚线l10轴对称且具有相同尺寸。

25.以下结合图1与图2a~2c来说明比较器电路12的操作,图2a所示为比较信号vop与von各自的占空比皆为50%,且比较信号vop与von互为反相。当比较信号vop处于高电压电平(例如处于操作电压vdd的电压电平),比较信号von处于低电压电平(例如处于操作电压vss的电压电平),基于反相器120与122的操作,反相器120在节点p4产生低电压电平的反相信号vintp,而反相器122在节点n4产生高电压电平的反相信号vintn。接着,基于反相器121与123的操作,反相器121根据低电压电平的反相信号vintp在节点p5产生高电压电平的输出电压信号voutp,而反相器123根据高电压电平的反相信号vintn在节点n5产生低电压电平的输出电压信号voutn。根据上述,基于交叉耦合架构,节点p5耦接节点n4,且节点n5耦接节点p4。由于节点n4上的反相信号vintn与节点p5上的输出电压信号voutp皆处于高电压电平,因此输出电压信号voutp能反应于高电压电平的比较信号vop而稳定地处于高电压电平。此外,由于节点p4上的反相信号vintp与节点n5上的输出电压信号voutn皆处于低电压电平,因此输出电压信号voutn能反应于低电压电平的比较信号von而稳定地处于低电压电平。类似的,根据上述反相器电路12的相似操作,当比较信号vop处于低电压电平且比较信号von处于高电压电平,基于反相器120~123的操作与交叉耦合架构,输出电压信号voutp能稳定地处于低电压电平,且输出电压信号voutn能稳定地处于高电压电平。通过本技术反相器电路12的操作,当比较信号vop与von各自的占空比皆为50%且彼此反相时,输出电压信号voutp与voutn各自的占空比皆为50%且彼此反相。

26.当比较信号vop与von中至少一个的占空比不等于50%和/或当比较信号vop与von之间的相位差不等于180

°

时,在某些时刻,比较信号vop与von可能处于相同的电压电平,例如,同时为高电压电平或低电压电平。以下将以比较信号vop与von的占空比皆不等于50%为例来说明反相器电路12的操作。如图2b中的斜线部分所标示,在一例子中,当比较信号vop与von的占空比小于50%时,存在比较信号vop与von同时处于低电压电平的情况。如图2c中的斜线部分所标示,在另一例子中,当比较信号vop与von的占空比大于50%时,存在比较信号vop与von同时处于高电压电平的情况。

27.根据上述对反相器电路12的说明,对于图2b与图2c的示例而言,当比较信号vop处于高电压电平且比较信号von处于低电压电平,基于反相器120~123的操作,输出电压信号voutp处于高电压电平,且输出电压信号voutn处于低电压电平;当比较信号vop处于低电压电平且比较信号von处于高电压电平,基于反相器120~123的操作,输出电压信号voutp处于低电压电平,且输出电压信号voutn处于高电压电平。

28.具体地,参阅图1及图2b,当比较信号vop与von同时处于低电压电平时,基于反相器120与122的操作,反相器120在节点p4产生高电压电平的反相信号vintp,而反相器122在节点n4产生高电压电平的反相信号vintn。接着,基于反相器121与123的操作,反相器121根据高电压电平的反相信号vintp在节点p5产生低电压电平的输出电压信号voutp,而反相器123根据高电压电平的反相信号vintn在节点n5产生低电压电平的输出电压信号voutn。基于交叉耦合架构,节点n4上高电压电平的反相信号vintn反相牵引节点p5上的输出电压信

号voutp,且节点p4上高电压电平的反相信号vintp反相牵引节点n5上的输出电压信号voutn,使得输出电压信号voutp与voutn皆朝向高电压电平改变。通过上述节点n4与p4上的电压电平分别对节点p5与n5上的电压电平的反相牵引,输出电压信号voutp与voutn的占空比逐渐朝向50%增加,藉此实现占空比校正。

29.参阅图1及图2c,当比较信号vop与von同时处于高电压电平时,基于反相器120与122的操作,反相器120在节点p4产生低电压电平的反相信号vintp,而反相器122在节点n4产生低电压电平的反相信号vintn。接着,基于反相器121与123的操作,反相器121根据低电压电平的反相信号vintp在节点p5产生高电压电平的输出电压信号voutp,而反相器123根据低电压电平的反相信号vintn在节点n5产生高电压电平的输出电压信号voutn。基于交叉耦合架构,节点n4上低电压电平的反相信号vintn反相牵引节点p5上的输出电压信号voutp,且节点p4上低电压电平的反相信号vintp反相牵引节点n5上的输出电压信号voutn,使得输出电压信号voutp与voutn皆朝向低电压电平改变。通过上述节点n4与p4上的电压电平分别对节点p5与n5上的电压电平的反相牵引,输出电压信号voutp与voutn的占空比逐渐朝向50%减少,藉此实现占空比校正。

30.图3a~3c显示信号频率分别为2ghz、4ghz、8ghz时比较信号vp与vn的占空比(x轴)相对于经本技术的占空比校正后产生的输出电压信号voutp与voutn的占空比(y轴)的曲线图。在图3a~3c的每一个中,曲线30~34分别是在不同制程工艺、电压、温度(process,voltage,temperature,pvt)参数下所获得的。举例来说,曲线30是对应制程工艺参数tt(典型pmos与典型nmos、0.9v、60℃);曲线31是对应参数ffl(快pmos与快nmos、0.95v、

‑

40℃);曲线32是对应参数ffh(快pmos与快nmos、0.95v、125℃);曲线33是对应参数ssl(慢pmos与慢nmos制程工艺、0.85v、

‑

40℃);曲线34是对应参数ssh(慢pmos与慢nmos制程工艺、0.85v、125℃)。参阅图3a~3c,当比较信号vp与vn的占空比不等于50%时,经占空比校正后,相对于50%的占空比,输出电压信号voutp与voutn的占空比误差将减小至小于0.4%。

31.当比较信号vp与vn之间的相位差不等于180

°

时,比较信号vp与vn可能会在一时段同时处于高电压电平,而在另一时段同时处于低电压电平。根据上述的反相器电路12的操作,通过上述节点n4与p4上的电压电平分别对节点p5与n5上的电压电平的反相牵引,输出电压信号voutp与voutn之间的相位差逐渐逼近180

°

,且输出电压信号voutp与voutn的占空比逐渐朝向50%改变,藉此实现相位差校正与占空比校正。经相位差校正与占空比校正后,输出电压信号voutp与voutn互为反相且其各自的占空比接近或等于50%。

32.图4a为比较信号vp与vn间的相位差(x轴)相对于经相位差校正后产生的输出电压信号voutp与voutn间的相位差(y轴)的曲线图,图4b为比较信号vp与vn间的相位差(x轴)相对于经占空比校正后产生的输出电压信号voutp与voutn的占空比(y轴)的曲线图。图4a~4b的曲线是基于8ghz的信号频率而产生的。在图4a~4b所示曲线的每一个中,曲线40~44、45~49分别是在不同制程工艺、电压、温度(process,voltage,temperature,pvt)参数下所获得的。举例来说,曲线40与45是对应制程工艺参数tt(典型pmos与典型nmos、0.9v、60℃);曲线41与46是对应参数ffl(快pmos与快nmos、0.95v、

‑

40℃);曲线42与47是对应参数ffh(快pmos与快nmos、0.95v、125℃);曲线43与48是对应参数ssl(慢pmos与慢nmos制程工艺、0.85v、

‑

40℃);曲线44与49是对应参数ssh(慢pmos与慢nmos制程工艺、0.85v、125℃)。如图4a所示,当比较信号vp与vn间的相位差介于

‑

15ps(皮秒)~ 15ps时,相对于180

°

的标准值,

经相位差校正后产生的输出电压信号voutp与voutn间的绝对相位差误差减小至小于或等于0.53ps。在校正相位差的同时,如图4b所示,相对于50%的标准值,经占空比校正后产生的输出电压信号voutp与voutn的相对占空比误差减小至小于或等于0.7%。

33.根据上述各实施例,本技术之差分放大器1除了可通过第一级放大电路10与第二级放大电路11对第一电压信号vi进行放大,同时对占空比与相位差进行粗略的校正,还可以通过交叉耦合反相器电路12进一步对占空比与相位差进行细致的校正。因此产生的第二电压信号vo具有满摆幅,占空比接近50%且所包括的输出电压信号voutp与voutn反相的特征。

34.图5例示本发明另一实施例所述的差分放大器。参阅图5,差分放大器5包括第一级放大电路50、第二级放大电路51、以及交叉耦合反相器电路12。差分放大器5接收一第一电压信号vi,并产生一第二电压信号vo。第二电压信号vo的摆幅大于第一电压信号vi,举例来说,第一电压信号vi的输入电压信号vp与vn为非满摆幅信号,而第二电压信号vo的输出电压信号voutp与voutn为满摆幅信号。根据一实施例,当差分放大器5应用于一serdes系统中的信道时,每一信道包括差分放大器5,且通过一对时钟导线接收一对差分时钟信号作为其第一电压信号vi。详细来说,差分比较器5接收差分时钟信号中之一时钟信号作为第一电压信号vi的输入电压信号vp,且接收差分时钟信号中的另一时钟信号作为第一电压信号vi的另一输入电压信号vn。

35.参阅图5,第一级放大电路50包括p型晶体管mp0、mp51与mp52,包括n型晶体管mn51、mn52、mnc1与mnc2,以及包括电阻器r51与r52。在图5所示以及部分实施例中,所述晶体管的组件皆以金属氧化物半导体晶体管或称为金属氧化物半导体(metal

‑

oxide

‑

semiconductor,mos)为例实现,但在其他实施例中不以此为限。p型晶体管mp51的漏极耦接节点p51,p型晶体管mp51的源极耦接共模节点cm51,p型晶体管mp51的栅极接收电压信号vp。p型晶体管mp52的漏极耦接节点n51,p型晶体管mp52的源极耦接共模节点cm51,p型晶体管mp52的栅极接收电压信号vn。

36.n型晶体管mn51的漏极耦接节点p51,n型晶体管mn51的源极耦接电压源vs2,n型晶体管mn51的栅极耦接节点p511。n型晶体管mnc1的漏极与源极都耦接电压源vs2,n型晶体管mnc1的栅极耦接节点p511。n型晶体管mnc1的操作可视为一电容器。电阻器r51耦接在节点p511与p51之间。n型晶体管mn51、n型晶体管mnc1以及电阻器r51组成有源电感501a。

37.n型晶体管mn52的漏极耦接节点n51,n型晶体管mn52的源极耦接耦接电压源vs2,n型晶体管mn52的栅极耦接节点n511。n型晶体管mnc2的漏极与源极耦接电压源vs2,n型晶体管mnc2的栅极耦接节点n511。n型晶体管mnc2的操作可视为一电容器。电阻器r52耦接在节点n511与n51之间。n型晶体管mn52、n型晶体管mnc2、以及电阻器r52组成有源电感501b。有源电感501a与有源电感501b组成一有源电感电路。

38.p型晶体管mp0的漏极耦接共模节点cm51,p型晶体管mp0的源极耦接电压源vs1,p型晶体管mp0的栅极接收偏压vbias5。p型晶体管mp0作为一电流源。第一级放大电路50根据所接收的电压信号vp与vn操作而在节点p51上产生比较信号vp51,且在节点n51上产生比较信号vn51。

39.参阅图5,第二级放大电路51包括p型晶体管mp53~mp56、n型晶体管mn53~mn56、以及电阻器r53与r54。n型晶体管mn53的漏极耦接节点p52,n型晶体管mn53的源极耦接电压

源vs1,n型晶体管mn53的栅极耦接节点p51以接收比较信号vp51。p型晶体管mp53的漏极耦接节点p52,p型晶体管mp53的源极耦接电压源vs1,p型晶体管mp53的栅极耦接节点p521。电阻器r53耦接在节点p52与p521之间。n型晶体管mn55的漏极耦接节点p53,n型晶体管mn55的源极耦接电压源vs2,n型晶体管mn55的栅极耦接节点p51以接收比较信号vp51。p型晶体管mp55的漏极耦接节点p53,p型晶体管mp55的源极耦接电压源vs1,p型晶体管mp55的栅极耦接节点n52。

40.n型晶体管mn54的漏极耦接节点n52,n型晶体管mn54的源极耦接电压源vs2,n型晶体管mn54的栅极耦接节点n51以接收比较信号vn51。p型晶体管mp54的漏极耦接节点n52,p型晶体管mp54的源极耦接电压源vs1,p型晶体管mp54的栅极耦接节点n521。电阻器r54耦接在节点n52与n521之间。n型晶体管mn56的漏极耦接节点n53,n型晶体管mn56的源极耦接电压源vs2,n型晶体管mn56的栅极耦接节点n51以接收比较信号vn51。p型晶体管mp56的漏极耦接节点n53,p型晶体管mp56的源极耦接电压源vs1,p型晶体管mp56的栅极耦接节点p52。

41.基于第一级放大电路50及第二级放大电路51的操作,第一级放大电路50及第二级放大电路51根据输入电压信号vp与vn,分别在节点p3及n3上产生比较信号vop及von。其中,输入电压信号vp可分解为共模部分与差模部分之和,而输入电压信号vn可分解为共模部分与差模部分之差,其中,该共模部分是指输入电压信号vp与输入电压信号vn之和的二分之一,该差模部分是指输入电压信号vp与输入电压信号vn之差的二分之一。对输入电压信号vp与输入电压信号vn而言,该差模部分的占空比等于(或近似于)50%,所以本发明的目的之一在于使第一级放大电路50及第二级放大电路51能够抑制该共模部分且放大该差模部分,以达到将占空比校正到50%的效果,也就是说,在于降低第一级放大电路50及第二级放大电路51的共模抑制比,其中,共模抑制比是指该第一级放大电路50及第二级放大电路51对该差模部分的增益与第一级放大电路50及第二级放大电路51对该共模部分的增益之比的绝对值,共模抑制比越大,代表对该共模部分的抑制能力越强。此外,第一级放大电路50及第二级放大电路51组成p输入型放大电路,其中,p输入型是指接收输入电压信号vp与输入电压信号vn的皆为p型晶体管,因而,第一级放大电路50及第二级放大电路51适用于处理该共模部分较低的情形。

42.具体而言,第一级比较器电路50用于为差分放大器5提供较小的增益及较佳的线性度,而第二级放大电路51则用于为差分放大器5提供较大的增益。其中,第二级放大电路51包括电阻器r53与r54,电阻器r53与r54为无源器件,将使第二级放大电路51的线性范围增加,而避免因第一级放大电路50及第二级放大电路51的线性范围有限所致的比较信号von及vop失真,从而提高第一级放大电路50及第二级放大电路51的共模抑制比,保证第一级放大电路50及第二级放大电路51的占空比校正能力,使比较信号von及vop的占空比接近于50%。其中,第一级放大电路50采用的有源电感501a与501b,则将各自引入一零点,使差分放大器5的频率带宽增大,可以处理更高频的信号,并可以缩短差分放大器1所产生的内部信号翻转时的过渡时间,从而减少电源噪声、热噪声等所致的抖动。

43.根据本发明一实施例,在第一级放大电路50及第二级放大电路51中,关于图5中的虚线l10轴对称的组件具有相同的尺寸。举例来说,n型晶体管mnc1与mnc2关于虚线l10轴对称且具有相同尺寸,n型晶体管mn51与mn52关于虚线l10轴对称且具有相同尺寸,n型晶体管mn51与mn52关于虚线l10轴对称且具有相同尺寸,n型晶体管mn53与m n54关于虚线l10轴对

称且具有相同尺寸,n型晶体管mn55与mn56关于虚线l10轴对称且具有相同尺寸等等。此外,关于虚线l10轴对称的节点产生的信号形成差分信号,例如节点p51上的比较信号vp51与节点n51上的比较信号vn51形成一对差分信号,节点p53上的比较信号vop与节点n53上的比较信号von形成另一对差分信号。因此,关于虚线l10轴对称的电路在时钟响应上具有相同的零点与极点。

44.反相器电路12包括反相器120~123。图5中的反相器电路12的电路与图1所示反相器电路12的电路架构相同功用一致,因而可参阅图1的相关叙述,在此省略说明。

45.虽然本发明已以优选实施例公开如上,然其并非用以限定本发明,本领域技术人员,在不脱离本发明的精神和范围内,当可作更动与润饰,因此本发明的保护范围当视所附权利要求书界定范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。