1.本发明涉及集成电路技术领域,特别是一种基于开关瞬态特性优化的栅极驱动电路。

背景技术:

2.功率场效应晶体管(mosfet)是一种多数载流子导电的单极型电压控制器件,具有开关速度快、高频性能好、输入阻抗高、噪声小、驱动功率小等优点,因此在开关电源、交流变频调速器、逆变器等装置中得到越来越多的应用。

3.mosfet的驱动对其工作效果起着决定性的作用,为了获得良好的性能,功率器件需要合适的驱动电路,针对功率器件的栅极驱动电路的研究工作很多,主要是基于开关速度、开关损耗、过冲电流、过冲电压和电磁干扰这些方面的考虑。开关速度快会产生更高的电流、电压过冲和emi,开关速度慢会产生更长的导通和关断延时和更高的开关损耗。然而随着工作频率的不断增大,对于驱动速度的要求变得更高,高的开通和关断速度必然会导致明显的电压电流冲击、波形振荡现象,电磁干扰等问题,严重影响了电力系统设备的安全和可靠性,需要对驱动电路进行优化。

4.传统的驱动电路如图1所示,采用一个较大的栅极电阻ron用于驱动功率器件s1的导通,采用较低的栅极电阻roff用于驱动功率器件s1的关断,这种折中处理方法比较简单,无法满足对开关特性要求更高的场合;现有技术中一种栅电阻可调的栅驱动电路,具体优化方法是在外部功率管s1电流上升阶段,用大的栅电阻抑制反向恢复电流,而在外部功率管漏源电压下降阶段,用小的栅电阻控制下降速率,减小开通损耗;但改变栅电阻的方法比较粗糙,在单个开关过程中一般只改变一次电阻,开通和关断很难同时进行优化。现有技术中也有基于漏端电压检测,调整栅极电压的控制方式,通过检测外部功率管s1的漏端电压与参考电压进行比较,根据比较电压结果调整栅极驱动电压,从而达到调整di/dt和dv/dt的目的,但是这种漏端检测电路需要用到高压电路,同时检测电路也较为复杂;现有技术中也有很多基于di

c

/dt、dv

ce

/dt闭环检测实现优化驱动的控制方式,但对于闭环控制来说,检测精度很难控制,并且反馈必然存在一定的延时,然而检测的精度和反馈的延时对于控制的性能影响很大,电路优化起来比较困难。

技术实现要素:

5.本发明所要解决的技术问题是针对现有技术的不足,提供一种设计合理、结构简单、导通关断的驱动电流外部可调、易于优化功率器件开关特性的基于开关瞬态特性优化的栅极驱动电路。

6.本发明所要解决的技术问题是通过以下的技术方案来实现的。本发明是一种基于开关瞬态特性优化的栅极驱动电路,包括关断特性优化电路、导通特性优化电路、基准电路、欠压保护电路、上电复位电路、输入级施密特电路smt1、比较器电路com1、与门电路and1和and2、反相器电路inv1、nmos管mn1和mn2;

7.输入信号v

in

连接输入级施密特电路smt1的输入端,输入级施密特电路smt1的输出v

in1

连接到与门电路and1的一个输入端,上电复位电路的输出信号v

por

和欠压保护电路的输出信号v

uvlo

分别连接到与门电路and1的其它两个输入端,反相器电路inv1的输入端和关断特性优化电路的一个输入端互连并和与门电路and1的输出信号v

l1

连接;反相器电路inv1的输出端v

h1

连接到与门and2的一个输入端以及导通特性优化电路的一个输入端,基准电路的输出v

ref1

连接到导通特性优化电路的另一个输入端;导通特性优化电路的一个输出信号v

n2

连接到nmos管mn2的栅极,导通特性优化电路的另一个输出端v

ref2

连接到比较器电路com1的负向输入端,nmos管mn2的源端和mn1的漏端连接到一起,作为驱动电路的输出信号v

out

,用于驱动外部功率器件;mn2的漏端连接到vcc,mn1的源端连接到gnd,驱动信号v

out

连接到比较器电路com1的正向输入端,比较器电路com1的输出信号v

ct

连接到与门电路and2的另一个输入端,与门电路and2的输出信号v

hx

连接到关断特性优化电路的另一个输入端,关断特性优化电路的输出信号v

n1

连接到nmos管mn1的栅极。

8.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的关断特性优化电路包括:线性稳压电路ldo、选通电路mux1、或门电路or1、反相器inv2、pmos管mp1~mp5、nmos管mn3~mn7、电阻r1和r2;pmos管mp1~mp4、nmos管mn4~mn6和电阻r1构成偏置电路;下管驱动信号v

l1

连接到nmos管mn7的栅极和或门电路or1的一个输入端,脉冲信号v

hx

连接到或门电路or1的另一个输入端、反相器inv2的输入端、选通电路mux1的控制信号;反相器inv2的输出端连接nmos管mn3的栅极,线性稳压电路ldo的输出信号v

ldo

和gnd信号分别连接到选通电路mux1的两个输入端;选通电路mux1的输出信号v

tn

连接到nmos管mn4的栅极;nmos管mn4的源级和mn3的漏级连接到电阻r1的一端,电阻r1的另一端、nmos管mn3、mn5和mn7的源级连接到gnd;pmos管mp1、mp3和mp5的源级连接到vcc,pmos管mp1的栅极和漏级、pmos管mp3的栅极和mp2的源极连接到一起;mp2的栅极和漏级、mp4的栅极连接到nmos管mn4的漏级;pmos管mp3的漏级连接到pmos管mp4的源极;pmos管mp4的漏级和nmos管mn5的漏级连接到nmos管mn6的漏极;或门电路or1的输出信号v

lt

连接到nmos管mn6的栅极和pmos管mp5的栅极;nmos管mn6的源极、mn5的栅极和pmos管mp5的漏级连接到电阻r2的一端,电阻r2的另一端连接到nmos管mn7的漏级,作为关断特性优化电路的输出信号v

n1

。

9.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的关断特性优化电路中:当v

l1

变为低电平时,驱动电路开始关断,首先通过窄脉冲信号控制mux1电路和偏置电路,使得v

n1

输出一个低压窄脉冲驱动信号,用于驱动nmos管mn1的导通,以一个较低的电流驱动外部功率器件进行关断,该低压脉冲幅值大小记为v

lv1

,v

lv1

高于mn1的阈值电压,小于vcc电压,窄脉冲信号之后,v

lt

变为低电平,此时偏置电路被关断输出,v

n1

电压被pmos管mp5抬高到vcc电压,以一个较高的电流驱动外部功率器件进行快速关断。

10.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的关断特性优化电路中:v

lv1

的大小可以通过改变电阻r1的大小来调整,进而调整v

hx

脉冲宽度内关断电流的大小;该电阻可以做在片外进行调整,适应不同的功率器件,也可以做在片上驱动特定功率器件。

11.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上

所述的基于开关瞬态特性优化的栅极驱动电路,所述的关断特性优化电路中:v

l1

是下管mn2的驱动信号,v

hx

是输出v

out

关断后高于v

ref2

的窄脉冲信号,v

lt

驱动信号是在v

l1

脉冲宽度基础上增加一个v

hx

窄脉冲宽度;该关断特性优化电路利用v

hx

窄脉冲宽实现分段控制外部功率器件的关断驱动电流,进而降低关断时刻的过冲电压和emi。

12.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的导通特性优化电路包括:运放op1、pmos管mp6~mp15、nmos管mn8~mn14、电阻r3、r4、r5和电容c1;pmos管mp6~mp9和nmos管mn8、电阻r3和r4构成偏置电路1,pmos管mp10~mp13和nmos管mn10~mn13构成偏置电路2,pmos管mp6的源极、mp8的源极、mp10的源极、mp12的源极和mp14的源极连接到vcc;电阻r3的一端和电阻r4的一端、nmos管mn9的源极、mn11的源极、mn12的源极、mn14的源极、电容c1的一端连接到gnd;参考电压v

ref1

连接到运放op1的正向输入端,nmos管mn8的源极和电阻r3的另一端连接到运放op1的负向输入端,pmos管mp6的栅极和漏级与mp7的源极、mp8的栅极和mp10的栅极连接在一起;pmos管mp7的栅极和漏级与mp9的栅极、mp11的栅极、nmos管mn8的漏级连接在一起,pmos管mp8的漏级连接mp9的源极,pmos管mp9的漏级和电阻r4的另一端v

ref2

连接在一起,作为导通特性优化电路的一个输出信号;pmos管mp10的漏级连接mp11的源级,pmos管mp11的漏级与nmos管mn10的漏级和栅极、mn13的栅极、mn9的漏级连接,nmos管mn10的源极、mn11的漏级、mn11的栅极与mn12的栅极连接,nmos管mn12的漏级连接mn13的源极,nmos管mn13的漏级与pmos管mp13的栅极和漏级、mp15的栅极连接,pmos管mp13的源极与mp12的栅极和漏级、mp14的栅极连接,pmos管mp14的漏级连接mp15的源极,pmos管mp15的漏级与电阻r5的一端、nmos管mn14的漏级连接在一起,作为导通特性优化电路的输出驱动信号v

n2

,电阻r5的另一端连接电容c1的另一端,上管驱动信号v

h1

连接到nmos管mn9和mn14的栅极。

13.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的导通特性优化电路中:v

ref1

是芯片内部的基准电压,v

h1

是芯片内部的上管mn2的驱动信号,它是由输入信号v

in

进行逻辑反的信号,基准电压v

ref1

和电阻r3设定了初始的偏置电流,通过偏置电路1和偏置电路2对电流按照一定比列放大,进而调整输出信号v

n2

的电流驱动能力,v

h1

控制偏置电路2的开启和关断,进而控制上管nmos管mn2的导通和关断,当v

h1

为高时,关断偏置电路2,导通特性优化电路的输出v

n2

信号为低,上管nmos管mn2关断。

14.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,所述的导通特性优化电路中:通过改变电阻r3的大小调整内部上管mn2的驱动电流;通过改变电阻r4的大小调整基准电压v

ref2

的大小,进而调整用于关断控制信号v

hx

的窄脉冲宽度;通过改变电阻r5和c1的大小调整内部上管mn2的导通速度,进而调整外部功率器件的开启速度,该电阻r3、r4、r5和电容c1可以做在片外进行调整,适应不同的功率器件,也可以做在片上驱动特定功率器件。

15.本发明所要解决的技术问题还可以通过以下的技术方案来进一步实现,对于以上所述的基于开关瞬态特性优化的栅极驱动电路,该驱动电路内部的输出级上管和下管均为nmos管,下管mn1的栅极驱动信号由关断特性优化电路提供,上管mn2的栅极驱动信号由导通特性优化电路提供。

16.与现有技术相比,本发明的显著优点:

17.(1)本发明输出级驱动采用了nmos管图腾柱结构驱动外部功率器件,提升了电流驱动能力,同时优化方式是通过调整内部输出nmos的栅极驱动实现,而不是直接在外部功率管的栅极电路、源漏级电路添加电路进行调整,因此降低了系统的干扰,提升了可靠性;

18.(2)本发明对导通和关断过程分开优化并且参数可调,关断时通过控制内部输出级低侧nmos管的驱动电压,进而实现分段电流控制外部功率管的关断;导通时通过控制输出级高侧nmos管的栅极驱动电流以及栅极电容充放电速度进而调整外部功率管的导通;通过本发明降低了电流和电压尖峰的同时,改善了电磁干扰特性,优化了开关特性,进而保护了系统的安全;

19.(3)本发明通过调整电阻和电容对栅极开关特性进行优化,结构简单,驱动电路易于集成,可以实现片上驱动。

附图说明

20.图1为传统驱动电路的示意图;

21.图2为本发明驱动电路的示意图;

22.图3为本发明关断特性优化电路示意图;

23.图4为本发明导通特性优化电路示意图;

24.图5为本发明关断过程优化的波形示意图;

25.图6为本发明导通过程优化的波形示意图;

26.图7为本发明关断特性优化电路中线性稳压电路示意图。

具体实施方式

27.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

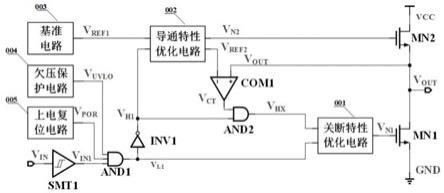

28.参照图2,一种基于开关瞬态特性优化的可调栅极驱动电路,包括关断特性优化电路001、导通特性优化电路002、基准电路003、欠压保护电路004、上电复位电路005、输入级施密特电路smt1、比较器电路com1、与门电路and1和and2、反相器电路inv1、nmos管mn1和mn2;

29.输入信号v

in

连接输入级施密特电路smt1的输入端,输入级施密特电路smt1的输出v

in1

连接到与门电路and1的一个输入端,上电复位电路005的输出信号v

por

和欠压保护电路004的输出信号v

uvlo

分别连接到与门电路and1的其它两个输入端,反相器电路inv1的输入端和关断特性优化电路的一个输入端互连并和与门电路and1的输出信号v

l1

连接;反相器电路inv1的输出端v

h1

连接到与门and2的一个输入端以及导通特性优化电路002的一个输入端,基准电路003的输出v

ref1

连接到导通特性优化电路002的另一个输入端;导通特性优化电路002的一个输出信号v

n2

连接到nmos管mn2的栅极,导通特性优化电路002的另一个输出端v

ref2

连接到比较器com1的负向输入端,nmos管mn2的源端和mn1的漏端连接到一起,作为驱动电路的输出信号v

out

,用于驱动外部功率器件;mn2的漏端连接到vcc,mn1的源端连接到

gnd,驱动信号v

out

连接到比较器电路com1的正向输入端,比较器电路com1的输出信号v

ct

连接到与门and2的另一个输入端,与门and2的输出信号v

hx

连接到关断特性优化电路001的另一个输入端,关断特性优化电路001的输出信号v

n1

连接到nmos管mn1的栅极;

30.v

in

作为驱动电路的输入信号,芯片内部采用了欠压保护电路和上电复位电路,分别输出保护信号v

por

和v

uvlo

,保护信号与v

in

经过施密特整形后的信号v

in1

一起经过三输入逻辑与门电路and1后输出v

l1

信号,作为关断特性优化电路的一个输入信号;v

l1

经过反相器inv1后输出v

h1

信号,作为导通特性优化电路的一个输入信号,比较器电路com1输出信号是v

ct

是指栅极驱动信号v

out

高于v

ref2

的方波信号,通过与门电路and2后输出v

hx

信号,v

hx

信号是指v

in

转变为关断信号后驱动电路的输出信号v

out

高于v

ref2

的窄脉冲信号,关断特性优化电路通过该窄脉冲实现外部功率器件的关断特性优化。

31.如图3所示,关断特性优化电路001包括:线性稳压电路ldo、选通电路mux1、或门电路or1、反相器inv2、pmos管mp1~mp5、nmos管mn3~mn7、电阻r1和r2;pmos管mp1~mp4、nmos管mn4~mn6和电阻r1构成偏置电路201;下管驱动信号v

l1

连接到nmos管mn7的栅极和或门or1的一个输入端,脉冲信号v

hx

连接到或门or1的另一个输入端、反相器inv2的输入端、选通电路mux1的控制信号;反相器inv2的输出端连接nmos管mn3的栅极,线性稳压电路ldo的输出信号v

ldo

和gnd信号分别连接到选通电路mux1的两个输入端;选通电路mux1的输出信号v

tn

连接到nmos管mn4的栅极;nmos管mn4的源级和mn3的漏级连接到电阻r1的一端,电阻r1的另一端、nmos管mn3、mn5和mn7的源级连接到gnd;pmos管mp1、mp3和mp5的源级连接到vcc,pmos管mp1的栅极和漏级、pmos管mp3的栅极和mp2的源极连接到一起。mp2的栅极和漏级、mp4的栅极连接到nmos管mn4的漏级;pmos管mp3的漏级连接到pmos管mp4的源极;pmos管mp4的漏级和nmos管mn5的漏级连接到nmos管mn6的漏极;或门电路or1的输出信号v

lt

连接到nmos管mn6的栅极和pmos管mp5的栅极;nmos管mn6的源极、mn5的栅极和pmos管mp5的漏级连接到电阻r2的一端,电阻r2的另一端连接到nmos管mn7的漏级,作为关断特性优化电路的输出信号v

n1

;

32.v

l1

是下管mn2的驱动信号,v

hx

是输出v

out

关断后高于v

ref2

的窄脉冲信号,v

lt

的驱动信号是在v

l1

脉冲宽度基础上增加一个v

hx

窄脉冲宽度;该关断特性优化电路利用v

hx

窄脉冲宽实现分段控制外部功率器件的关断驱动电流,进而降低关断时刻的过冲电压和emi;当v

l1

变为低电平时,驱动电路开始关断,首先通过窄脉冲信号控制mux1电路和偏置电路,选通电路mux1输出ldo电压,驱动nmos管mn4的开启,此时反相器inv2输出低电平,nmos管mn3截止,通过偏置电路201使得v

n1

输出一个低压窄脉冲驱动信号,用于驱动nmos管mn1的导通,以一个较低的电流驱动外部功率器件进行关断,该低压脉冲幅值大小记为v

lv1

,v

lv1

高于mn1的阈值电压,小于vcc电压,窄脉冲信号之后,v

lt

变为低电平,此时偏置电路被关断输出,v

n1

电压被pmos管mp5抬高到vcc电压,以一个较高的电流驱动外部功率器件进行快速关断。

33.如图4所示,导通特性优化电路002包括:运放op1、pmos管mp6~mp15、nmos管mn8~mn14、电阻r3、r4、r5和电容c1;pmos管mp6~mp9和nmos管mn8、电阻r3和r4构成偏置电路1 202,pmos管mp10~mp13和nmos管mn10~mn13构成偏置电路2 203,pmos管mp6的源极、mp8的源极、mp10的源极、mp12的源极和mp14的源极连接到vcc;电阻r3的一端和电阻r4的一端,nmos管mn9的源极、mn11的源极、mn12的源极、mn14的源极、电容c1的一端连接到gnd;参考电压v

ref1

连接到运放op1的正向输入端,nmos管mn8的源极和电阻r3的另一端连接到运放op1

的负向输入端,pmos管mp6的栅极和漏级与mp7的源极、mp8的栅极和mp10的栅极连接在一起;pmos管mp7的栅极和漏级与mp9的栅极、mp11的栅极、nmos管mn8的漏级连接在一起,pmos管mp8的漏级连接mp9的源极,pmos管mp9的漏级和电阻r4的另一端v

ref2

连接在一起,作为导通特性优化电路的一个输出信号;pmos管mp10的漏级连接mp11的源级,pmos管mp11的漏级与nmos管mn10的漏级和栅极、mn13的栅极、mn9的漏级连接,nmos管mn10的源极、mn11的漏级、mn11的栅极与mn12的栅极连接,nmos管mn12的漏级连接mn13的源极,nmos管mn13的漏级与pmos管mp13的栅极和漏级、mp15的栅极连接,pmos管mp13的源极与mp12的栅极和漏级、mp/4的栅极连接,pmos管mp14的漏级连接mp15的源极,pmos管mp15的漏级与电阻r5的一端、nmos管mn14的漏级连接在一起,作为导通特性优化电路的输出驱动信号v

n2

,电阻r5的另一端连接电容c1的另一端,上管驱动信号v

h1

连接到nmos管mn9和mn14的栅极;

34.v

ref1

是芯片内部的基准电压,v

h1

是芯片内部的上管mn2的驱动信号,该驱动信号是由输入v

in

信号进行逻辑反的信号,通过基准电压v

ref1

和电阻r3设置了初始的偏置电流的大小,如公式1所示,电阻r4上的电压v

ref2

的大小如公式2所示,通过偏置电路2 203对初始的偏置电流进行放大后,v

n2

的电流能力大小如公式3所示,v

h1

控制偏置电路2 203的开启和关断,进而控制上管nmos管mn2的导通和关断,当v

h1

为高电平时,关断偏置电路2 203,开启nmos管mn14,导通特性优化电路的输出v

n2

信号为低电平,上管nmos管mn2关断,当v

h1

位低电平时,导通特性优化电路的输出v

n2

信号为高电平;

[0035][0036][0037][0038]

其中n1为mp8与mp6的宽长比的比值,n2为mp10和mp6的宽长比的比值,n3为mn13和mn10的宽长比的比值,n4为mp14和mp12的宽长比的比值。

[0039]

图5是关断特性优化电路波形示意图,当v

l1

为高电平时,v

n1

为低电平,当v

l1

由高电平变为低电平时,此时v

hx

有一个t

hx

的脉冲信号,在该时间内,v

n1

上升并保持到一个低电平电压v

lv1

,驱动电路输出v

out

信号以较低的斜率下降,当v

hx

脉冲信号变低时,v

lt

信号变为低电平,v

n1

快速上升到vcc,驱动电路输出v

out

信号以较高的斜率快速下降,实际电路工作时,由于内部的比较器等电路具有一定的响应时间,驱动输出信号和v

n1

信号之间有一定的延时。

[0040]

图6是导通特性优化电路波形示意图,当v

l1

为低电平时,v

h1

为高电平,此时v

n2

为低电平,当v

l1

由低电平变为高电平时,v

h1

变为低电平,v

n2

开始变为高电平,由于电阻r5和c1的影响,v

n1

上升时间较慢一些,进而驱动电路的输出v

out

上升较为平滑,驱动电路的输出电压v

out

的高电平幅值大小为vcc

‑

v

gs

。

[0041]

v

lv1

的大小可以通过改变电阻r1的大小来调整,进而在开始关断时调整v

hx

脉冲宽度内关断电流的大小;改变电阻r4的大小可以调整基准电压v

ref2

的大小,进而调整开始关断时的窄脉冲宽度,因此通过改变电阻r1和r4的大小调整外部功率器件的关断速度;通过

改变电阻r3的大小可以调整内部上管mn2的驱动电流;通过改变电阻r5和c1的大小调整上管mn2的导通速度,进而调整外部功率器件的开启速度;导通特性优化电路和关断特性优化电路中的电阻r1、r3、r4、r5和电容c1可以做在片外调整,用于根据不同的功率器件进行调整,优化外部功率器件的开关特性,也可以做在片上驱动特定功率器件。

[0042]

图7是关断特性优化电路中线性稳压电路ldo的一种结构示意图,ldo电路包括运放op2、nmos管mn15、电阻r6、r7和电容c2;运放op2的正向输入端连接基准电压v

ref1

;负向输入端连接电阻r6和r7的一端,电阻r7的另一端和电容c2的一端连接gnd,电阻r6的另一端和电容c2的另一端连接nmos管mn15的源极,作为ldo电路的输出信号v

ldo

;运放op2的输出端连接mn15的栅极,mn15的漏级连接vcc。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。