1.本发明涉及微/纳机电系统技术领域,具体涉及一种谐振器及其形成方法,以及一种电子设备。

背景技术:

2.目前,谐振器等具有悬臂梁的器件大多采用带空腔的soi硅片制作。以谐振器为例,传统工艺中梁的制作一般为:在带空腔的soi上依次沉积并图形化下电极、压电层、上电极,随后将梁的自由端及两侧的顶硅和埋氧层刻蚀掉使梁形成,最后用键合硅帽的方式进行封装。该工艺过程中存在很多缺点,首先,如图1所示,由于空腔soi的空腔1004内气压较低,通常在大气压力下空腔1004上的顶硅1001会发生凹陷,在空腔1004上制作的器件也会相应的弯曲;如图2当梁被形成后空腔1004与大气连通,顶硅1001和埋氧层1002趋向于恢复平直状态而电极层1005、1007和压电层1006的初始状态是弯曲状态,因此在这个过程中顶硅1001和压电层1006之间产生较大应力。该应力将导致器件品质因数q降低。其次,由于soi制作过程中硅和氧化硅均为硬质材料,两种硬质材料键合形成较大的应力;虽然悬臂梁被形成但其固定端由soi原有的硅

‑

氧化硅键合界面固定在底硅1003上,因而soi中寄生应力严重影响器件的性能。最后,由于带空腔的soi在加工技术上较难且制作周期较长,导致带空腔soi硅片非常昂贵,因此采用空腔soi的工艺成本也较高。因此,采用带空腔soi和传统封装工艺制作的器件很难进一步提高品质因数且成本过高,成为实现产品商业化的关键障碍。

技术实现要素:

3.有鉴于此,本发明提出一种能够上述技术缺陷的谐振器及其制造方法,以及包括该谐振器的电子设备。

4.本发明第一方面提出一种谐振器的形成方法,该谐振器具有梁结构,其特征在于,该方法包括:对于包括顶硅层、埋氧层和底硅层的soi晶圆,在所述顶硅层之上依次形成图形化的压电层和底电极;将当前半导体结构倒置后键合到下硅帽之上,其中,当前半导体结构与所述下硅帽之间构成下空腔;去除所述底硅层;形成所述梁结构,其中,所述顶硅层作为所述梁结构的从动层;将上硅帽键合到当前半导体结构上,其中,当前半导体结构与所述上硅帽之间构成上空腔。

5.可选地,在形成所述梁结构的步骤之后,并且在将上硅帽键合到当前半导体结构上的步骤之前,还包括:去除所述梁结构之上的所述埋氧层。

6.可选地,所述梁结构为悬臂梁或者固支梁,或者包含悬臂梁或者固支梁的多梁结构。

7.可选地,所述梁结构与所述上硅帽之间以及所述梁结构与所述下硅帽之间均通过键合方式连接。

8.可选地,在去除所述底硅层的步骤之后,并且在形成所述梁结构的步骤之前,还包

括:形成贯穿所述顶硅层和埋氧层的电极连接;以及,在将上硅帽键合到当前半导体结构上的步骤之后,还包括:在所述上硅帽中形成上金属连接区,其中所述上金属连接区与所述电极连接接触。

9.可选地,在将当前半导体结构倒置后键合到下硅帽之上的步骤之前,还包括:在所述下硅帽中形成下金属连接区;以及,所述将当前半导体结构倒置后键合到下硅帽之上的步骤包括:将当前半导体结构倒置后,所述半导体结构的顶电极和/或底电极连接到所述下金属连接区。

10.可选地,还包括:在所述上硅帽的内侧和/或所述下硅帽的内侧形成吸气层。

11.可选地,在形成所述压电层的步骤之前,还包括:在所述顶硅层之上形成图形化的顶电极。

12.可选地,所述顶硅层为掺杂硅且掺杂浓度大于10

19

cm

‑3。

13.可选地,所述上空腔和所述下空腔的高度为:10微米至200微米,或者,20微米至100微米。

14.本发明第二方面提出一种谐振器,包括:一种谐振器,其特征在于,包括:梁结构,所述梁结构包括从上到下的从动层、压电层和底电极,其中所述从动层包含硅层;下硅帽,所述下硅帽与所述梁结构之间构成下空腔;上硅帽,所述上硅帽与所述梁结构之间构成上空腔。

15.可选地,还包括:位于所述从动层之上的埋氧层。

16.可选地,所述梁结构为悬臂梁或者固支梁,或者包含悬臂梁或者固支梁的多梁结构。

17.可选地,所述梁结构与所述上硅帽之间具有第一键合层,所述梁结构与所述下硅帽之间具有第二键合层。

18.可选地,所述第一键合层或/和所述第二键合层为金属键合层。

19.可选地,还包括:贯穿所述顶硅层的电极连接;以及位于所述上硅帽中的上金属连接区,其中所述上金属连接区与所述电极连接接触。

20.可选地,还包括:位于所述下硅帽中的下金属连接区,所述下金属连接区与所述梁结构的顶电极和/或底电极接触。

21.可选地,还包括:位于所述上硅帽的内侧和/或所述下硅帽的内侧的吸气层。

22.可选地,还包括:位于所述从动层与所述压电层之间的顶电极。

23.可选地,所述顶硅层为掺杂硅且掺杂浓度大于10

19

cm

‑3。

24.可选地,所述上空腔和所述下空腔的高度为:10微米至200微米,或者,20微米至100微米。

25.本发明第三方面提出一种电子设备,其特征在于,包括本发明公开的谐振器。

26.根据本发明的技术方案,采用普通soi硅片,避免了使用空腔soi硅片。倒置封装技术在降低成本的同时,由于直接使用普通soi取代带空腔soi,在悬臂梁制作过程中不存在弯曲现象,因此避免了由于空腔soi形成后带来的应力问题。其次,在本发明实例中soi底硅被完全去除,因此消除了由于氧化硅

‑

硅硬质结合带来的应力问题。在悬臂梁与基底的固定端之间采用韧性较好的材料作为键合层,如金材料,由于金具有延展性,和硬质键合相比有效地减小了外界应力向悬臂梁的耦合。由于应力的大幅度减少,使得器件的品质因数明显

提高,同时不受外界应力的干扰,稳定性提高。最后,两个空腔均通过硅的刻蚀完成,空腔的高度可控,避免了带空腔soi中空腔高度的限制。

附图说明

27.为了说明而非限制的目的,现在将根据本发明的优选实施例、特别是参考附图来描述本发明,其中:

28.图1为现有技术的带空腔的soi硅片的示意图;

29.图2为现有技术的带空腔的soi硅片形成悬臂梁后的示意图;

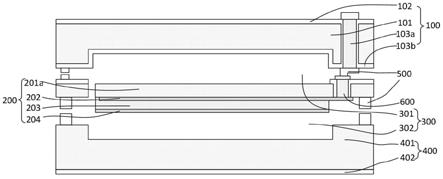

30.图3至图11为本发明第一实施例的具有悬臂梁的谐振器的形成方法的过程示意图;

31.图12为本发明第二实施例的具有悬臂梁的谐振器的剖面示意图;

32.图13为本发明第三实施例的具有悬臂梁的谐振器的剖面示意图;

33.图14为本发明第四实施例的具有悬臂梁的谐振器的剖面示意图;

34.图15为本发明第五实施例的具有固支梁的谐振器的剖面示意图。

具体实施方式

35.本发明实施方式的谐振器的形成方法中,将器件倒置进行键合实现谐振器真空腔的封装技术,该技术避免了带空腔soi硅片的使用,降低了成本。同时克服了空腔soi顶硅在形成后由弯曲恢复平直及由底硅与埋氧层硬键合带来的应力问题。

36.以下对说明书附图中各部分结构及材料加以说明:

37.100:上硅帽,包括:

38.101:上基底,材料可选单晶硅、多晶硅、玻璃或石英。

39.102:上绝缘层,具体材料可选氧化硅、氮化铝、氧化铝等。

40.103a:上金属连接区,具体材料可选钼、钌、金、铝、镁、钨、铜,钛、铱、锇、铬或以上金属的复合或其合金。

41.103b:上隔离层,具体材料可选氧化硅、氮化铝、氧化铝等。

42.需要说明的是,上金属连接区103a和上隔离层103b并非必选的结构。在其他的从下硅帽引出电极的实施例中(例如图12),可以省略103a和103b,改为设置下金属连接区403a(其材料、功能与103a相同)和下隔离层403b(其材料、功能与103b相同)。

43.200:梁结构,具体可以为悬臂梁或者固支梁,或者包含悬臂梁或者固支梁的多梁结构,例如:由两个悬臂梁组合而成的音叉型结构,或者由多个悬臂梁组合而成的梳齿状结构。梁结构200具体可以包括:

44.201a:顶硅层,材料可选单晶硅、氮化铝、砷化镓、蓝宝石等等。需要说明的是,该顶硅层201a来自初始提供的soi晶圆。soi晶圆中还包括埋氧层201b和底硅层201c。其中底硅层201c在加工过程中需要被去除。埋氧层201b可以根据器件需求而被去除或者被保留。埋氧层不被去除时,可以作为温补层存在于器件中。具体原理为:由于埋氧层(二氧化硅)通常具有正温度系数,而普通硅(掺杂浓度低于10

19

cm

‑3)、压电层(如aln)、电极层(mo)一般具有负温度系数,因此,无埋氧层时器件整体的频率温度系数呈现负温度系数,而保留埋氧层时可以改善器件的温漂特性(即减小器件频率随温度的漂移量)。

45.通过选择或调整埋氧层厚度,可以使器件一阶温漂系数接近于0。

46.202:顶电极,具体材料可选钼、钌、金、铝、镁、钨、铜、钛、铱、锇、铬或以上金属的复合或其合金,还可以采用掺杂硅等非金属导电材料。顶电极202为可选结构,当顶硅层201a为掺杂硅且掺杂浓度大于10

19

cm

‑3时可直接起到电极的作用,此时可以省略顶电极202。

47.203:压电层,可选氮化铝、氧化锌、pzt等材料并包含上述材料的一定原子比的稀土元素掺杂材料。

48.204:底电极,材料同顶电极202。

49.300:空腔,包括:上空腔301和下空腔302。

50.400:下硅帽,包括:

51.401:下基底,材料同上基底101。

52.402:下绝缘层,材料同上绝缘层102。

53.在一些实施例中(例如图12),下硅帽中还可以包括下金属连接区403a(其材料、功能与103a相同)和下隔离层403b(其材料、功能与103b相同)。

54.500:键合层,材料一般为金,也可以是其他金属或二氧化硅、高聚物等常用的键合材料等。需要说明的是,键合层500可以具体细分为位于梁结构200与上硅帽100之间的第一键合层,和位于梁结构200与下硅帽400之间的第二键合层。出于简便说明的目的,说明书附图中并不将第一键合层和第二键合层分别标号。

55.可选地,第一键合层或/和第二键合层为金属键合层。具体情况为:(1)若设计谐振器是从上硅帽100引出电极,则第一键合层采用金属键合层,第二键合层既可以采用si

‑

sio2或者si

‑

si的非金属键合层,也可以采用金属键合层;(2)若设计谐振器是从下硅帽400引出电极,则第二键合层采用金属键合层,第一键合层既可以采用si

‑

sio2或者si

‑

si的非金属键合层,也可以采用金属键合层。

56.600:电极连接,具体材料可选钼、钌、金、铝、镁、钨、铜、钛、铱、锇、铬或以上金属的复合或其合金。

57.700:吸气层,具体材料可选钛(ti)以及钛合金,锆(zr)以及锆合金。

58.下面结合附图对本发明作更进一步的说明。需要说明的是,这些实施例是用于说明本发明而不限于限制本发明的范围。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。

59.图3至图11为本发明第一实施例的具有悬臂梁的谐振器的形成方法的过程示意图,其具体工艺流程如下述(本专利中各部分以其中可行的一种材料为例进行说明,但不限于此)。

60.步骤1:提供在soi晶圆,之上沉积顶电极。

61.具体地,如图3所示,提供soi晶圆,该soi晶圆包括顶硅层201a、埋氧层201b和底硅层201c。先在顶硅层201a上沉积钼,随后以图形化的光刻胶作为掩膜刻蚀钼电极,使其图形化,得到顶电极202。需要说明的是,本步骤为可选的。当顶硅层201a为掺杂硅且掺杂浓度大于10

19

cm

‑3时可以直接充当电极,省略掉形成顶电极202的过程。

62.步骤2:沉积压电层和底电极。

63.具体地,如图4所示,先沉积一层氮化铝,在氮化铝上沉积氧化硅,随后以光刻胶为掩膜对氧化硅进行湿法刻蚀,然后以氧化硅作为硬掩模对氮化铝进行干法刻蚀使其图形

化,得到压电层203。然后再在压电层203上制作底电极204,制作过程参考步骤1中制作顶电极202的过程。

64.步骤3:制作下硅帽。

65.具体地,如图5所示,首先重新取一个硅片,该硅片包括下硅基底401和下绝缘层402,在硅片上沉积一层氮化铝并图形化,然后以图形化的氮化铝为掩膜,用干法刻蚀硅形成下空腔302,随后去除氮化铝,最后沉积一层金并图形化用于后续键合。至此得到了下硅帽400。其中,下空腔的高度可以为10微米至200微米,或者,20微米至100微米。

66.步骤4:倒置封装。

67.具体地,如图6所示,将步骤2得到的结构垂直翻转后盖在步骤3得到的下硅帽400上,然后进行键合连接。在顶硅层201a与下硅帽400的接触位置固定端之间可以采用韧性较好的材料作为键合层500,和硬质连接相比有效地减小了外界应力与顶硅层201a之间的耦合。至少一侧的键合可选择金属键合,一般为金

‑

金组合,也可以是其他金属组合,如:铝

‑

锗、铜

‑

铜、铜

‑

金

‑

铜、金

‑

锡、金

‑

锡

‑

铜等。也可以选用二氧化硅、高聚物等非金属键合方式。

68.步骤5:去除底硅层。

69.具体地,如图7所示,用干法刻蚀将底硅层201c完全刻蚀掉。

70.步骤6:制作电连接通孔。

71.具体地,如图8所示,首先沉积一层图形化的氮化铝,然后以氮化铝为掩膜干法刻蚀顶硅层以得到通孔600a,然后将氮化铝去掉,随后对通孔600a内壁进行氧化,防止后续电连接通过多晶硅短路。

72.步骤7:制作电极连接。

73.具体地,如图9所示,首先沉积金属铜至填满上述通孔600a,之后用铜刻蚀液去除上表面的铜,只保留通孔内部的铜;然后,沉积金并进行图形化。至此,得到了电极连接600。

74.步骤8:形成悬臂梁并且去除埋氧层。

75.具体地,如图10所示,首先以光刻胶为掩膜,以hf为刻蚀剂刻蚀氧化硅材料的埋氧层201b;然后以图形化了的氧化硅为硬掩模,在预设的悬臂梁的自由端的位置(即图9中位置a)进行干法刻蚀,直至顶硅层被刻穿形成空隙(即图10中空隙b),从而形成悬臂梁形式的梁结构200,其左端(按图中视角)即为悬臂梁形式的梁结构200自由端。再后,用光刻胶为掩膜用boe刻蚀去除悬臂梁形式的梁结构200上部的氧化硅材料的埋氧层201b。此时顶硅层201a变为悬臂梁形式的梁结构200的从动层。

76.步骤9:键合封装。

77.具体地,如图11所示,将事先制作好的上硅帽100置于步骤8得到的半导体结构上方进行键合封装,该半导体结构与上硅帽100之间构成上空腔301。其中,上空腔的高度可以为10微米至200微米,或者,20微米至100微米。其中上硅帽100和下硅帽400相比,增加了右侧的上金属连接区103a和上隔离层103b。因此上硅帽的制作过程可以以下硅帽100的制作过程为基础。上金属连接区103a和上隔离层103b的制作过程则可以参考步骤6、7。键合上硅帽100的具体方式可以是au

‑

au键合、也可以是al

‑

ge键合、cu

‑

au

‑

cu键合或其他聚合物键合等方式。

78.实施例2

79.图12为本发明第二实施例的具有悬臂梁的谐振器的剖面示意图。如图12所示,本

实施例与实施例1的区别在于:工作的电极并非从上硅帽100引出,而是从下硅帽400引出。该实施例中,无需在顶硅层201a中制作通孔600a及通孔中的金属连接600,简化了工艺,降低了成本;并且因为顶硅层201a中避免了异质结构,进一步降低了应力的存在,使得器件的品质因数进一步提高。

80.实施例3

81.图13为本发明第三实施例的具有悬臂梁的谐振器的剖面示意图。如图13所示,本实施例与实施例1的区别在于:工作的电极从下硅帽400引出;顶硅层201a中的金属连接600不再用于将梁结构的工作的电极从上硅帽100引出,而是用作测试电极,以便于在器件封装上硅帽之前进行晶圆级别测试和调频操作检测。

82.实施例4

83.图14为本发明第四实施例的具有悬臂梁的谐振器的剖面示意图。如图14所示,本实施例与实施例1的区别在于:在下硅帽400的内侧设置了吸气层700。在其他实施例中,吸气层700还可以只设置在上硅帽100的内侧,或者同时设置在上硅帽100的内侧和下硅帽400的内侧。吸气层用于吸收空腔中的气态分子,减缓由于键合材料释气及键合界面漏气造成的空腔内真空度漂移,从而使器件获得高的品质因数及较好的可靠性。传统的采用空腔soi制作的器件,吸气层700只能设置在上硅帽100的内侧。而本发明实施方式中由于采用倒置封装技术,因此可以更加灵活地设置吸气层。

84.实施例5

85.图15为本发明第五实施例的具有固支梁的谐振器的剖面示意图。如图15所示,本实施例与实施例1的区别在于:本实施例中并非实施例1所示的悬臂梁结构,梁结构200左右两端均不打开,只有梁结构200的两侧打开。换言之,本实施例采用固支梁形式的梁结构200。固支梁结构比悬臂梁结构的谐振频率更高,在对于高频情况下的应用中具有优势。需要说明的是,图15中谐振器的电极是从上硅帽引出,这仅仅是出于示例而非限定。在其他实施例中,具有固支梁的谐振器可以类似图13所示地从下硅帽引出,细节不再赘述。

86.本发明实施方式的电子设备,包括本发明公开的任一种谐振器。

87.根据本发明实施方式的技术方案中,谐振器采用普通soi硅片制作,避免了使用空腔soi硅片。倒置封装技术在降低成本的同时,由于直接使用普通soi取代带空腔soi,在悬臂梁制作过程中不存在弯曲现象,因此避免了由于空腔soi形成后带来的应力问题。其次,在本发明实例中soi底硅被完全去除,因此消除了由于氧化硅

‑

硅硬质结合带来的应力问题。在悬臂梁与基底的固定端之间采用韧性较好的材料作为键合层,如金材料,由于金具有延展性,和硬质键合相比有效地减小了外界应力向悬臂梁的耦合。由于应力的大幅度减少,使得器件的品质因数明显提高,同时不受外界应力的干扰,稳定性提高。最后,两个空腔均通过硅的刻蚀完成,空腔的高度可控,避免了带空腔soi中空腔高度的限制。

88.上述具体实施方式,并不构成对本发明保护范围的限制。本领域技术人员应该明白的是,取决于设计要求和其他因素,可以发生各种各样的修改、组合、子组合和替代。任何在本发明的精神和原则之内所作的修改、等同替换和改进等,均应包含在本发明保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。