1.本实用新型涉及芯片设计领域,特别是涉及一种全差分的高速逻辑转换电路、芯片及激光雷达。

背景技术:

2.随着集成电路的不断发展和需求的扩展,逻辑转换电路需要适配更大范围摆幅的输入信号,即同时适配高摆幅输入信号和低摆幅输入信号。

3.现有技术中,逻辑转换电路通常包括数字逻辑电路,例如差分级联逻辑,数字逻辑电路对于高摆幅输入信号的处理能力强。

4.但是,针对lvds,cml,vml,lvpecl等低摆幅输入信号,此时的数字逻辑电路会遇到差分输出高低电平压差过低甚至输出电平无法正常翻转的问题,则无法兼容多种电平标准。

5.这一问题的根本原因在于电路设计过程中需要兼顾信号跳变时电平的快速翻转及翻转结束稳定后的静态偏置,单纯的数字逻辑电路很难兼顾大的信号输入范围及大的输出压差。

技术实现要素:

6.本实用新型解决的技术问题在于,使得逻辑转换电路适配于不同摆幅的输入信号,提升逻辑转换电路的输入信号兼容性。

7.更进一步的,提升逻辑转换电路的工作频率。

8.本实用新型公开了一种全差分的高速逻辑转换电路,包括:

9.逻辑门电路;

10.电压串联正反馈电路,用于扩展该逻辑门电路的输入信号的范围。

11.所述的全差分的高速逻辑转换电路在该逻辑门电路的电源端与接地端分别设置有恒流源。

12.该逻辑门电路具有多路差分输入信号,一路差分输出信号;

13.每路差分输入信号均通过该电压串联正反馈电路实现正反馈。

14.该逻辑门电路包括非门、与门、或门、与非门、或非门、同或门、异或门中的至少其中之一。

15.该电压串联正反馈电路包括输入电阻和反馈电阻,该逻辑门电路的输出后的直流偏置取决于该输入电阻与该反馈电阻的阻值之比。

16.该电压串联正反馈电路包括第一输入电阻、第一反馈电阻、第二输入电阻、第二反馈电阻;

17.第一输入电阻的第一端接收该差分输入信号中的正极信号,第一输入电阻的第二端与该逻辑门电路的正极输入端连接,第一输入电阻的第二端还与第一反馈电阻的第一端连接,第一反馈电阻的第二端与该逻辑门电路的正极输出端连接;

18.第二输入电阻的第一端接收该差分输入信号中的负极信号,第二输入电阻的第二端与该逻辑门电路的负极输入端连接,第二输入电阻的第二端还与第二反馈电阻的第一端连接,第二反馈电阻的第二端与该逻辑门电路的负极输出端连接。

19.该逻辑门电路的输入信号包括lvds、cml、cmos、vml或lvpecl信号。

20.该逻辑门电路输出cmos信号。

21.该全差分的高速逻辑转换电路通过cmos工艺实现。

22.本实用新型公开了一种逻辑转换芯片,具有至少一个所述全差分的高速逻辑转换电路。

23.多个该全差分的高速逻辑转换电路相互级联排布。

24.本实用新型公开了一种激光雷达,设置有所述的全差分的高速逻辑转换电路,或者,设置有所述的逻辑转换芯片。

25.本实用新型的技术方案使得全差分的逻辑转换电路适配于不同摆幅的输入信号,提升全差分的逻辑转换电路的输入信号兼容性。同时,提升逻辑转换电路的工作频率。

附图说明

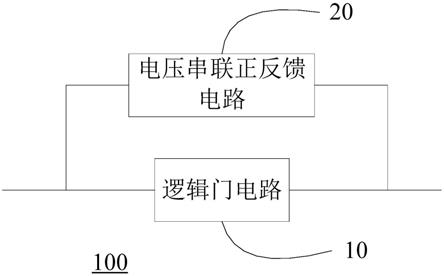

26.图1所示为本实用新型的逻辑转换芯片结构示意图。

27.图2所示为本实用新型公开的一种全差分的高速逻辑转换电路的结构示意图。

28.图3所示为该全差分的高速逻辑转换电路100的电路结构图。

29.图4、5所示为逻辑转换芯片的结构示意图。

具体实施方式

30.以下结合具体实施例描述本实用新型的技术方案的实现过程,不作为对本实用新型的限制。

31.本实用新型涉及芯片设计,如图1所示为本实用新型的逻辑转换芯片结构示意图。

32.在逻辑转换芯片中包括全差分的高速逻辑转换电路100、输出驱动级电路bf。n路同一类型的高速接口电平信号vin1‑

vin

n

作为高速输入信号输入全差分的高速逻辑转换电路100,实现逻辑运算,并输出cmos电平信号,该cmos电平信号经过输出缓冲级电路bf驱动下级负载。电流参考current ref用以提供各级模块偏置电流。

33.为了使得该全差分的高速逻辑转换电路适配于不同摆幅的高速输入信号,提升全差分的高速逻辑转换电路对不同输入信号的兼容性的技术问题,本实用新型的全差分的高速逻辑转换电路100采用正反馈设计,从而使全差分的高速逻辑转换电路100的输出信号幅度能够被下级电路识别。

34.如图2所示为本实用新型公开的一种全差分的高速逻辑转换电路的结构示意图。

35.一种全差分的高速逻辑转换电路100包括:

36.逻辑门电路10;

37.电压串联正反馈电路20,用于扩展该逻辑门电路的输入信号的范围,以兼容多种接口电气标准。

38.该全差分的高速逻辑转换电路100可接收输入信号,即依次接收多种高速接口电平并执行逻辑运算,最终输出cmos信号。

39.该逻辑门电路10具有多路差分输入信号,一路差分输出信号。每路差分输入信号均通过该电压串联正反馈电路20实现正反馈,由该电压串联正反馈电路20实现对该差分输入信号的放大。

40.如图3所示为该全差分的高速逻辑转换电路100的电路结构图。

41.该全差分的高速逻辑转换电路100接收n路同一类型的差分输入信号,输出一路差分输出信号,其中,vip[n]为差分输入信号vin

n

的正极信号,vin[n]为差分输入信号vin

n

的负极信号,vop为差分输出信号的正极信号,von为差分输出信号的负极信号。n=1

……

n,n为大于等于2的正整数。

[0042]

所有差分输入信号均经过电压串联正反馈电路20实现正反馈。该电压串联正反馈电路20包括由输入电阻r

in

p[n]、反馈电阻r

f

p[n]、输入电阻r

in

n[n]、反馈电阻r

f

n[n]实现的正反馈网络。

[0043]

r

in

p[n]的第一端接收vip[n],r

in

p[n]的第二端与该逻辑门电路10的第n正极输入端d[n]连接,r

in

p[n]的第二端还与r

f

p[n]的第一端连接,r

f

p[n]的第二端与该逻辑门电路10的第一输出端q连接。

[0044]

r

in

n[n]的第一端接收vin[n],r

in

n[n]的第二端与该逻辑门电路10的第n负极输入端dn[n]连接,r

in

n[n]的第二端还与r

f

n[n]的第一端连接,r

f

n[n]的第二端与该逻辑门电路10的第二输出端qn连接。

[0045]

在优选实施例中,所有输入电阻r

in

p[n]与所有输入电阻r

in

n[n]的阻值相同,所有反馈电阻r

f

p[n]与所有反馈电阻r

f

n[n]的阻值相同。

[0046]

该逻辑门电路10的输出后的直流偏置取决于该反馈电阻r

f

p[n]与该输入电阻r

in

p[n]的阻值之比x。

[0047]

该逻辑门电路10包括非门、与门、或门、与非门、或非门、同或门、异或门中的至少其中之一。由于该逻辑转换电路100的结构简约,该逻辑转换电路100可通过cmos工艺实现。采用cmos工艺便于进一步实现本实用新型的逻辑转换电路100与其他功能电路的集成,兼容性强,降低成本。

[0048]

在一优化实施例中,在该逻辑门电路10的电源端vcc设置有恒流源i1,接地端gnd设置有恒流源i2。通过上述恒流源的设置,使得该逻辑门电路10始终处于导通状态,则避免逻辑门电路10反复启动的时间损耗,为具有高速接口电平的输入信号提供了适配的高速工作频率,提高芯片的运行效率。

[0049]

恒流源i1与i2控制该全差分的高速逻辑转换电路100的驱动能力,有助于降低小幅度差分输入信号输入时逻辑反转难度,与电压串联正反馈电路20一起拓宽差分输入信号的输入范围。

[0050]

该逻辑门电路的输入信号可包括lvds、cml、cmos、vml或lvpecl信号,通过本实用新型的技术方案,可对低摆幅的输入信号进行输出范围的扩展,使其满足后续电路的信号需求。

[0051]

同时输出缓冲级电路bf具有驱动能力,可起到隔离后端负载与该全差分的高速逻辑转换电路的作用,同时可采用不同实现形式产生所需要的输出电平类型。

[0052]

以下对本实用新型所述方案进行举例说明。本例的情形适用于lvds、cml、cmos、vml或lvpecl信号作为输入信号。以下以该逻辑门电路10为两输入差分与门为例进行说明。

[0053]

情形一,vip[1]与vin[1]均为较高电平,vip[2]与vin[2]维持不变。

[0054]

例如,vip[1]=2/3*vcc,vin[1]=1/2*vcc,此时输入中心值高于0.5*vcc。如果未设置该电压串联正反馈电路20,则输出均为低电平,即vop=0.2*vcc,von=0.1*vcc,压差过小,此时的输出信号无法被下级bf识别,则无法输出有效逻辑运算值。

[0055]

在设置该电压串联正反馈电路20后,输入输出之间形成一条电流通路,使输出上升,由于vip[1]电平高于vin[1],vip[1]所在通路正反馈效果更强,则vop被拉高至高于0.5*vcc,von远小于0.5*vcc,压差放大,进而能够被下级bf识别并放大输出。

[0056]

情形二,vip[1]为高电平,vin[1]为低电平,vip[2]与vin[2]维持不变。

[0057]

此时,由于输入信号即存在压差,故而,输出也存在压差,即使未设置该电压串联正反馈电路20,也可以被下级bf识别。在设置该电压串联正反馈电路20后,该电压串联正反馈电路20并不会对vop、von进行较大调整,故而,输出信号可正常被下级bf识别并放大输出。

[0058]

情形三,vip[1]为低电平,vin[1]为高电平,vip[2]与vin[2]维持不变。

[0059]

此时,由于输入信号即存在压差,故而,输出也存在压差,即使未设置该电压串联正反馈电路20,也可以被下级bf识别。在设置该电压串联正反馈电路20后,该电压串联正反馈电路20并不会对vop、von进行较大调整,故而,输出信号可正常被下级bf识别并放大输出。

[0060]

情形四,vip[1]与vin[1]均为较低电平,vip[2]与vin[2]维持不变。

[0061]

例如,vip[1]=1/3*vcc,vin[1]=1/4*vcc,此时输入中心值低于0.5*vcc。如果未设置该电压串联正反馈电路20,则输出均为高电平,即vop=0.8*vcc,von=0.7*vcc,压差过小,此时输出的输出信号无法被下级bf识别,则无法输出有效逻辑运算值。

[0062]

在设置该电压串联正反馈电路20后,输入输出之间形成一条电流通路,使输出下降,由于vin[1]电平低于vip[1],vin[1]所在通路正反馈效果更强,则vop被拉低至高于0.5*vcc,von被拉低至远低于0.5*vcc,压差放大,进而能够被下级bf识别并放大输出。

[0063]

上述四种情形可以适用于lvds、cml、cmos、vml或lvpecl信号。

[0064]

其中,该逻辑门电路10的输出后的直流偏置,也就是vop、von的数值取决于该反馈电阻r

f

p[n]与该输入电阻r

in

p[n]的阻值之比x。

[0065]

本实用新型还公开了一种逻辑转换芯片,如图4所示为该逻辑转换芯片的结构示意图。

[0066]

该逻辑转换芯片包括级联的多个该全差分的高速逻辑转换电路100,第二级全差分的高速逻辑转换电路100接收第一级全差分的高速逻辑转换电路100的输出信号作为输入信号,第二级全差分的高速逻辑转换电路100还可接收来自外界或其他电路的差分输入信号。

[0067]

图5中以两个全差分的高速逻辑转换电路100的差分输出信号作为下一级全差分的高速逻辑转换电路100的输入信号,数量不以此为限。下一级全差分的高速逻辑转换电路100还可以接收来自外界或其他电路的差分输入信号。

[0068]

如图4、5所示的级联排布方式使得多个全差分的高速逻辑转换电路100可以密集排布,节省排线面积,节省空间,降低成本。

[0069]

本实用新型所公开的兼容多种高速接口电平的全差分的高速逻辑转换电路及其

对应的逻辑转换芯片,均设置于激光雷达设备中。

[0070]

本实用新型的技术方案使得全差分的高速逻辑转换电路适配于不同摆幅的输入信号,提升全差分的高速逻辑转换电路的输入信号兼容性,特别是兼容范围扩展至低电压,使得全差分的高速逻辑转换电路可以兼容于高、低压电平。同时,提升全差分的高速逻辑转换电路的工作频率。

[0071]

上述实施例仅为实现本实用新型的示例性描述,而不用以限制本实用新型的保护范围,本领域的技术人员可据以做出各种明显变形以及等同替换的技术方案,皆涵盖于本实用新型的公开范围内,本实用新型的保护范围请参阅后附带权利要求书中记载为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。