1.本公开涉及数模转换。具体地,示例涉及数模转换器(dac)、发射机和移动设备。

背景技术:

2.dac用于将数字信号转换为模拟信号。例如,容性射频(rf)dac用于基于数字基带发送信号直接生成模拟rf发送信号。

3.dac(例如,rfdac)的性能可以通过例如其效率、其最大输出功率、其频率范围或其线性度来描述。对于rfdac,线性度定义由rfdac生成的模拟rf信号的远离噪声(far off noise)和相邻信道泄漏比(aclr)。影响模拟rf信号的aclr的一个方面是rfdac的各个单元中的最后反相器的非线性输出。例如,如果以金属氧化物半导体(mos)技术实现rfdac,则反相器的部件的有限非线性mos电阻,以及反相器的nmos(n型mos)部件的导通电阻并不精确等于反相器的pmos(p型mos)部件的导通电阻这方面,在模拟rf信号中引起谐波失真。谐波失真作为aclr是可见的,并引起降级的误差矢量幅度(evm)。

4.因此,可能期望改进的dac架构。

附图说明

5.以下将仅通过示例的方式并参照附图描述装置和/或方法的一些示例,在附图中:

6.图1示出了dac的示例;

7.图2示出了dac的另一示例;

8.图3示出了dac单元的示例;

9.图4示出了dac的输出功率谱的示例;

10.图6示出了dac的输出功率谱的另一示例;

11.图6示出了dac单元的另一示例;以及

12.图7示出了包括dac的移动设备的示例。

具体实施方式

13.现在将参照示出了一些示例的附图更全面地描述各种示例。在附图中,为了清楚,可能夸大了线、层和/或区域的厚度。

14.因此,虽然进一步的示例有各种修改和替代形式,但是在附图中示出并且随后将详细描述其一些特定示例。然而,该详细描述并非将进一步的示例限制到所描述的特定形式。进一步的示例可以覆盖落入本公开的范围内的所有修改、等同物和替代物。贯穿附图的描述,相同或相似的数字指代相同或相似的要素,这些要素可以在相互比较时以相同方式或以修改的形式来实现,同时提供相同或相似的功能。

15.应理解,当要素称为“连接”或“耦合”到另一要素时,这些要素可以直接连接或耦合,或者经由一个或多个中间要素连接或耦合。如果使用“或”来组合两个要素a和b,则若并未明确或隐含地另外定义,那么这应被理解为公开所有可能的组合(即,仅a、仅b、以及a和

b)。对于相同组合的替代措辞是“a和b中的至少一个”或“a和/或b”。经必要修正后,这同样适用于多于两个的要素的组合。

16.本文用于描述特定示例的术语并非旨在对于进一步的示例是限制性的。每当使用单数形式(例如,“一”、“一个”和“所述”)并且仅使用单个要素既未明确地也未隐含地定义为强制时,进一步的示例也可以使用复数要素来实现相同的功能。同样,当随后将功能描述为使用多个要素来实现时,进一步的示例可以使用单个要素或处理实体来实现相同的功能。还将理解,术语“包括”、“包含”、“含有”和/或“具有”在使用时指明所声明的特征、整数、步骤、操作、过程、动作、要素和/或部件,但不排除存在或添加一个或多个其他特征、整数、步骤、操作、过程、动作、要素、部件和/或其任何群组。

17.除非另外定义,否则所有术语(包括技术和科学术语)在本文中以其示例所属领域的普通含义被使用。

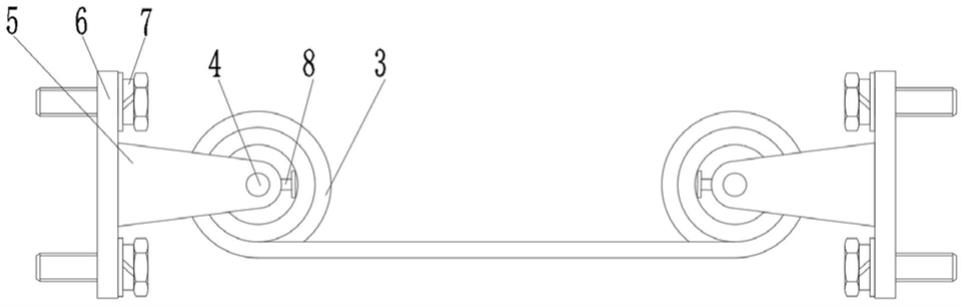

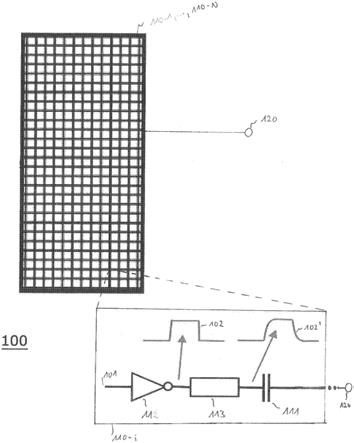

18.图1示出了示例性dac 100。dac 100包括多个dac单元110

‑

1、...、110

‑

n。多个dac单元110

‑

1、...、110

‑

n可以是(例如,与dac的期望分辨率有关的)任何数量n≥2的dac单元。多个dac单元110

‑

1、...、110

‑

n耦合到dac 100的输出节点120。

19.多个dac单元110

‑

1、...、110

‑

n中的至少一个dac单元110

‑

i(1≤i≤n)包括容性元件111,容性元件被配置为将dac单元110

‑

i的模拟输出信号供给到输出节点120。例如,容性元件111可以是(例如,在金属层内实现的或者由半导体衬底内的沟槽实现的)片上电容器。然而,容性元件111也可以是用于提供电容的任何其他合适的部件。容性元件111可以例如展现几飞法(例如,1至5ff之间)的电容。

20.dac单元110

‑

i可以是dac 100的多个dac单元110

‑

1、...、110

‑

n中的任何单元。

21.此外,至少一个dac单元110

‑

i包括反相器电路112,反相器电路112耦合到容性元件111。反相器电路被配置为:基于振荡信号101,输出容性元件111的反相器信号102。反相器电路112是dac单元110

‑

i的最后反相器电路。换言之,在反相器电路112与容性元件111之间没有耦合另外的反相器电路。

22.在本发明的各种实施例中,至少一个dac单元110

‑

i可以被配置为包括阻性元件113,阻性元件113耦合到反相器电路112和容性元件111,或在它们之间。阻性元件的电阻是至少50ω(欧姆)。换言之,(与例如耦合反相器电路112和容性元件111的导电迹线/路径相比)具有高电阻的元件耦合在反相器电路112与容性元件111之间。

23.阻性元件113可以允许减少反相器电路112的输出处的寄生电容,使得在反相器电路112的输出处等效地仅存在(非常)低的寄生电容。反相器电路112的瞬态响应可以因此基本上不受容性元件111的充电状态影响。如图1所示,由反相器电路112输出的反相器信号102可以展现基本上完美的矩形波形。仅阻性元件113之后的反相器信号102’受容性元件111的寄生电容影响。然而,阻性元件113和容性元件111的rc时间常数展现线性行为,因此不生成非线性。因此,在反相器电路112与容性元件111之间提供线性阻性元件113可以允许使dac单元110

‑

i的输出级线性化。

24.可以通过许多不同的方式实现阻性元件113。例如,阻性元件113可以是薄膜电阻器或多晶硅电阻器。在其他示例中,阻性元件113可以是晶体管,该晶体管可以操作为具有可调整的电阻的电阻器。例如,晶体管的控制端子(例如,栅极端子)可以被配置为:接收控制信号,以用于将晶体管的输入端子(例如,源极端子)与输出端子(例如,漏极端子)之间的

电阻调整到期望的值。

25.在一些示例中,阻性元件113的电阻可以高于50ω。例如,阻性元件113的电阻可以是至少500ω、1000ω、1500ω、2000ω、2500ω、3000ω、3500ω、4000ω、5000ω、6000ω或7000ω。阻性元件113的较高电阻使得至少一个dac单元110

‑

i的线性度增加。因此,可以通过对于阻性元件113选择较高的电阻值来增加至少一个dac单元110

‑

i的线性度。

26.为了进一步增加至少一个dac单元110

‑

i的线性度,对于反相器电路112可以使用具有低阈值电压的晶体管。阈值电压是晶体管的控制端子与输入端子之间的、在晶体管的输入端子与输出端子之间创建导通路径所需的最小电压。例如,对于场效应晶体管(fet),阈值电压是在源极端子与漏极端子之间创建导通路径所需的最小栅源电压。如果以互补mos(cmos)技术实现反相器电路112,则反相器电路112包括串联耦合在第一电位(例如,供给电压v

dd

)与第二电位(例如,地或供给电压v

ss

)之间的不同导电性的至少两个晶体管(例如,nmos和pmos fet;未示出)。至少两个晶体管中的每一个的阈值电压最大可以是第一电位与第二电位之间的电位差的15%、20%或25%。换言之,反相器电路112可以使用低电压阈值(lvt)或超低电压阈值(ulvt)晶体管代替标准电压阈值(svt)晶体管。因此,反相器电路112的阈值电压是低的,使得反相器电路112可以实现快速切换。快速反相器电路112和反相器电路112的输出处的减少的(低的)寄生电容的组合可以使得反相器电路112的输出处的反相器信号102的矩形波形近乎完美成为可能。

27.在图1的示例中,多个dac单元110

‑

1、...、110

‑

n之中的n≤n个dac单元可以与dac单元110

‑

i是相同的。在一些示例中,多个dac单元110

‑

1、...、110

‑

n中的所有dac单元可以是相同的。在其他示例中,多个dac单元110

‑

1、...、110

‑

n中的一个或多个dac单元可以不同于dac单元110

‑

i(例如,包括附加的或不同的元件)。

28.振荡信号101可以展现恒定相位或者被相位调制。此外,振荡信号101可以是rf振荡信号,即,振荡信号101的频率可以是至少10、100、500、1000、1500、2000或5000mhz。替代地,振荡信号101可展现较低的频率(例如,小于1mhz、1khz或100hz)。例如,dac 100可以用作用于直接生成rf信号的rfdac,或者用作不直接调制rf信号的容性dac(cdac)。

29.图2示出了经由匹配电路210耦合到(例如,代表天线的)负载220的dac 200的另一更详细的示例。匹配电路210向dac 200的输出节点205呈现定义的电感,以便使从dac 200的输出节点205到负载220的功率传送最大化,并使从负载220返回到输出节点205的信号反射最小化。在图2的示例中,dac 200操作为用于生成rf发送信号的rfdac。

30.综合器电路230基于要无线发送的数据(例如,基于数据中包含的或从数据导出的相位信息),生成用于dac 200的相位调制的rf振荡信号201。

31.dac 200包括多个dac单元210

‑

1、...、210

‑

n,它们耦合到dac的输出节点205。与上面关于dac 100描述的内容类似地,多个dac单元210

‑

1、...、210

‑

n中的每一个包括相应的反相器电路212

‑

1、...、212

‑

n(例如,包括具有低阈值电压的晶体管)、相应的阻性元件213

‑

1、...、213

‑

n和相应的容性元件211

‑

1、...、211

‑

n。此外,多个dac单元210

‑

1、...、210

‑

n中的每一个包括相应的逻辑电路214

‑

1、...、214

‑

n,它们使得能够选择对dac 200的输出信号有贡献的dac单元的数量。换言之,通过选择对dac的输出信号有贡献的dac单元的数量,可以调整dac输出信号的幅度。为了避免不必要的重复,以下仅关于dac单元210

‑

1的逻辑电路214

‑

1解释逻辑电路214

‑

1、...、214

‑

n的功能。应注意,其他dac单元210

‑

2、...、210

‑

n的逻

辑电路214

‑

2、...、214

‑

n相应地进行操作。

32.逻辑电路214

‑

1从综合器电路230接收相位调制的振荡信号201。此外,逻辑电路214

‑

1接收控制信号203

‑

1。在图2的示例中,逻辑电路214

‑

1是与非门(nand)。然而,逻辑电路214

‑

1不限于该具体实现方式。例如,可以使用一个或多个其他逻辑门来实现逻辑电路214

‑

1。

33.逻辑电路214

‑

1基于控制信号203

‑

1选择性地输出反相振荡信号201’。当控制信号203

‑

1代表逻辑值0(低信号电平)时,逻辑电路214

‑

1的输出是代表逻辑值1(高信号电平)的信号,而无论相位调制的振荡信号201的信号值如何。当控制信号203

‑

1代表逻辑值1时,相位调制的振荡信号201的信号值被逻辑电路214

‑

1反相。

34.反相器电路212

‑

1使逻辑电路214

‑

1的输出反相。因此,当控制信号203

‑

1代表逻辑值0时,由反相器电路212

‑

1输出的反相器信号恒定地处于低信号电平。当控制信号203

‑

1代表逻辑值1时,由反相器电路212

‑

1输出的反相器信号像相位调制的振荡信号201一样在低信号电平与高信号电平之间改变。换言之,当控制信号203

‑

1代表逻辑值0时,恒定的第一电压被供给到容性元件211

‑

1,而当控制信号203

‑

1代表逻辑值1时,第一电压和第二电压被交替地提供给容性元件211

‑

1。

35.即,控制信号203

‑

1、...、203

‑

n允许选择是将第一和第二电压交替地供给到相应的dac单元210

‑

1、...、210

‑

n的容性元件,还是将第一电压恒定地供给到相应的dac单元210

‑

1、...、210

‑

n的容性元件。

36.选择交替地将第一和第二电压提供给其容性元件的dac单元的数量以及选择恒定地将第一电压提供给其容性元件的dac单元的数量可以允许调整dac 200的输出节点205处提供的输出电压。例如,可以根据下式确定dac 200的输出电压v

out

:

[0037][0038]

其中,c

tot

是多个dac单元210

‑

1、...、210

‑

n的总电容,c

i

是被交替地提供有第一电压v

first

和第二电压v

second

的容性元件的电容。换言之,控制信号203

‑

1、...、203

‑

n允许激活(禁用)多个dac单元210

‑

1、...、210

‑

n中的各个dac单元。例如,可以基于要无线发送的数据中所包含的或从其导出的幅值(半径)信息来确定活跃单元的数量。例如,dac 200可以包括解码器电路,解码器电路被配置为:基于要无线发送的数据(例如,幅值信息),生成控制信号203

‑

1、...、203

‑

n。

[0039]

虽然在图1中没有明确示出,但是根据本发明的各种实施例,至少一个dac单元110

‑

i可以被配置为包括逻辑电路(例如,与非门),该逻辑电路接收振荡信号101和用于dac单元110

‑

i的控制信号。与上面关于dac 200的dac单元210

‑

1描述的内容类似地,逻辑电路可以基于控制信号选择性地生成反相振荡信号,使得反相器电路可以基于反相振荡信号生成反相器信号102。因此,dac 100可以被配置为还包括解码器电路,该解码器电路被配置为:基于数字输入数据(例如,要无线发送的数字数据),生成用于dac单元110

‑

i的控制信号。

[0040]

如上面结合图1所描述的,多个dac单元中的一个或多个dac单元可以实现得与上述dac单元不同。例如,根据所提出架构的dac可以包括第一数量的温度计编码dac单元和第二数量的二进制编码dac单元。虽然温度计编码dac单元全都展现相同的驱动强度,但是二

进制编码dac单元的驱动强度仅是温度计编码dac单元的驱动强度的一分数(fraction)。在图3中示出二进制编码dac单元310的示例。

[0041]

从图3可见,dac单元310包括容性元件311、反相器电路312和阻性元件313,如同上述dac单元110

‑

i和dac单元210

‑

1、...、210

‑

n。出于简化的原因,dac单元310被示为没有任何逻辑电路。然而,应注意,dac单元310可以包括如上面关于dac单元210

‑

1描述的逻辑电路。

[0042]

与dac单元110

‑

i相比,dac单元310附加地包括另外的容性元件314,另外的容性元件314耦合在地电位处的第一节点315与布置在阻性元件313和容性元件311之间的第二节点316之间。

[0043]

另外的容性元件314和容性元件311的总计容量等于dac单元110

‑

i的容性元件111的容量。换言之,dac单元110

‑

i中的容性元件111的电容被划分为想要的电容(容性元件311)和寄生电容(另外的容性元件314),以用于将dac单元310的驱动强度调整为dac单元110

‑

i的驱动强度的一分数。例如,容性元件311的电容可以是dac单元110

‑

i中的容性元件111的电容的1/2、1/4、1/8、1/16、1/32或1/64。因此,另外的容性元件311的电容可以是dac单元110

‑

i中的容性元件111的电容的1/2、3/4、7/8、15/16、31/32或63/64。dac单元310的瞬态行为等于dac单元110

‑

i的瞬态行为。

[0044]

返回参照图1所示的dac 100,多个dac单元110

‑

1、...、110

‑

n可以包括如上所述的至少一个dac单元110

‑

i和如上所述的至少一个dac单元310。dac单元310的阻性元件313的电阻可以等于dac单元110

‑

i的阻性元件111的电阻。

[0045]

例如,dac 100可以包括如dac单元110

‑

i那样实现的1024个温度计编码dac单元和如dac单元310那样实现的6个附加二进制编码dac单元。例如,六个容性元件311的相应电容可以是容性元件111的电容的1/2、1/4、1/8、1/16、1/32和1/64。

[0046]

从图4和图5可以看出所提出的将阻性元件集成到dac单元的输出级中以及所提出的使用具有低阈值的晶体管以用于反相器电路对dac线性度的影响。图4示出了根据所提出的架构的dac的示例性输出功率谱。在图4的示例中,以480mhz数据图案驱动dac(即,dac操作为rfdac)。

[0047]

线410代表dac的理想行为(即,dac的理想输出功率谱)。线420代表当阻性元件展现1ω的电阻并且将svt晶体管用于反相器电路时的输出功率谱。线430代表当阻性元件展现1ω的电阻并且将lvt晶体管用于反相器电路时的输出功率谱。线440代表当阻性元件展现1ω的电阻并且将ulvt晶体管用于反相器电路时的输出功率谱。线450代表当阻性元件展现4000ω的电阻并且将svt晶体管用于反相器电路时的输出功率谱。线460代表当阻性元件展现4000ω的电阻并且将lvt晶体管用于反相器电路时的输出功率谱。线470代表当阻性元件展现4000ω的电阻并且将ulvt晶体管用于反相器电路时的输出功率谱。

[0048]

从图4可见,对于低电阻值,通过减少反相器电路的晶体管的阈值电压,dac线性度增加。如果使用高电阻值而不是低电阻值,则dac线性度进一步增加。在图4的示例中,归因于快速反相器和阻性元件,aclr提升多于15db。

[0049]

图5示出了根据所提出的架构的dac的另外的输出功率谱。线505、510和515代表当阻性元件展现1ω的电阻并且当反相器电路包括svt、lvt和ulvt晶体管中的相应晶体管时的输出功率谱。线520、525和530代表当阻性元件展现1000ω的电阻并且当反相器电路包括

svt、lvt和ulvt晶体管中的相应晶体管时的输出功率谱。线535、540和545代表当阻性元件展现2000ω的电阻并且当反相器电路包括svt、lvt和ulvt晶体管中的相应晶体管时的输出功率谱。线550、555和560代表当阻性元件展现4000ω的电阻并且当反相器电路包括svt、lvt和ulvt晶体管中的相应晶体管时的输出功率谱。

[0050]

再次,从图5可见,通过减少反相器电路的晶体管的阈值电压,dac线性度增加。如果阻性元件的电阻增加,则dac线性度进一步增加。换言之,本公开的示例可以实现具有线性化输出级的rfdac。

[0051]

此外,从图5的中间部分可见,对于不同的电阻值,想要的rf信号分量的输出功率稍微变化。欧姆电阻降低dac单元的效率和输出功率。因此,阻性元件导致dac的输出功率减少,这取决于阻性元件的电阻值。电阻越高,dac输出功率的下降就越大。然而,另一方面,rf输出信号中的非线性得以减少(例如,在图5的示例中,减少大约20db)。

[0052]

如从图5的rf发送信号生成示例可见,所提出的dac架构可以实现60db aclr性能,使得可以实现非常低的evm。虽然存在输出功率的损失,但时减少的非线性可以例如允许省略数字预失真(dpd)或减少dpd复杂度。因此,与传统方法相比,可以用所提出的线性化架构减少生成rf发送信号所需的功率。

[0053]

在上述示例中,描述了dac和dac单元的单端实现方式。应注意,在一些示例中,可以另外以不同的方式实现上述dac和dac单元。图6中示出了根据所提出架构的用于dac的差分dac单元610的示例。在图6的示例中,dac单元610经由匹配电路670耦合到天线660。

[0054]

dac单元610包括第一逻辑电路615,第一逻辑电路615耦合到第一反相器电路620。第一反相器电路620耦合到第一容性元件625。第一阻性元件630耦合在第一反相器电路620与第一容性元件625之间。第一容性元件625耦合到dac的第一输出节点605。

[0055]

在图6的示例中,第一逻辑电路615被实现为nand门。第一逻辑电路615接收第一振荡信号601和第一控制信号603。基于第一控制信号603,第一逻辑电路615选择性地将第一反相振荡信号输出到第一反相器电路620,与上面结合图2关于dac单元210

‑

1描述的内容类似。第一反相器电路620基于第一反相振荡信号生成第一反相器信号。第一反相振荡信号被供给到第一容性元件625,并且第一容性元件625将dac单元610的第一模拟输出信号供给到输出节点605。

[0056]

此外,dac单元610包括第二逻辑电路635,第二逻辑电路635耦合到第二反相器电路640。第二反相器电路640耦合到第二容性元件645。第二阻性元件650耦合在第二反相器电路640与第二容性元件645之间。第二容性元件645耦合到dac的第二输出节点606。

[0057]

如同第一逻辑电路635,第二逻辑电路635被实现为nand门。第二逻辑电路635接收第二振荡信号602和第二控制信号604。第二振荡信号602相对于第一振荡信号601被反相。此外,第二控制信号604相对于第一控制信号603被反相。基于第二控制信号604,第二逻辑电路635选择性地将第二反相振荡信号输出到第二反相器电路640,与上面结合图2关于dac单元210

‑

1描述的内容类似。第二反相器电路640基于第二反相振荡信号生成第二反相器信号。第二反相振荡信号被供给到第二容性元件645,并且第二容性元件645将dac单元610的第二模拟输出信号供给到第二输出节点606。

[0058]

第二阻性元件650的电阻等于第一阻性元件630的电阻,其中,这两个阻性元件的电阻是至少50ω。

[0059]

此外,dac单元610包括第三容性元件655,第三容性元件655被配置为将dac单元610的第三模拟输出信号供给到第二输出节点606。第一对串联耦合的反相器电路660、661耦合到第三容性元件655。第一对反相器电路基于由第一逻辑电路615选择性地输出的第一反向振荡信号,输出用于第三容性元件655的第三反相器信号。第三阻性元件665耦合在第一对反相器电路660、661与第三容性元件655之间。第三阻性元件665的电阻等于第一阻性元件630的电阻。

[0060]

此外,dac单元610包括第四容性元件670,第四容性元件670被配置为将dac单元610的第四模拟输出信号供给到第一输出节点605。第二对串联耦合的反相器电路675、676耦合到第四容性元件670。第二对反相器电路基于由第二逻辑电路635选择性地输出的第二反相振荡信号,输出用于第四容性元件670的第四反相器信号。第四阻性元件680耦合在第二对反相器电路675、676与第四容性元件670之间。第四阻性元件680的电阻等于第一阻性元件630的电阻。

[0061]

因此,可以向输出节点605、606提供具有高线性度的差分对模拟输出信号。

[0062]

在图7中示出了使用根据所提出的技术的一个或多个方面或上述一个或多个示例的dac的实现方式的示例。图7示意性地示出了移动设备700(例如,移动电话、智能电话、平板计算机或膝上型设备)的示例,移动设备700包括发射机或收发机710(为了简单,以下仅将其称为发射机)。发射机710包括根据本文描述的示例的dac 720。此外,发射机710包括综合器电路730,综合器电路730被配置为:基于要无线发送的数据,生成用于dac 720的振荡信号。例如,综合器电路730可以是调制的本地振荡器或数字时间转换器(dtc)。然而,综合器电路730不限于上述示例。综合器电路730可以例如基于要无线发送的数据中所包含的或从要无线发送的数据导出的相位信息,生成振荡信号。

[0063]

振荡信号可以是(相位调制的)rf信号,使得振荡信号的频率是例如至少100、500、1000、1500、2000或5000mhz。因此,dac 720可以被理解为实现直接生成rf发送信号的rfdac。例如,对dac 720的输出信号(即,rf发送信号)有贡献的dac单元的数量可以由dac 720的解码器电路(未示出)基于要无线发送的数据来控制。解码器电路可以例如基于要无线发送的数据中所包含的或从要无线发送的数据导出的幅值(或半径)信息,控制对dac 720有贡献的输出信号的dac单元的数量。

[0064]

匹配电路740耦合到dac 720的输出节点。匹配电路740向dac 720的输出节点呈现定义的电感,以便使从dac 720的输出节点到移动设备的至少一个天线元件750的功率传送最大化,并使从至少一个天线元件750返回到dac 720的输出节点的信号反射最小化。

[0065]

移动设备700可以包括另外的元件(例如,应用处理器、存储器、音频驱动器、相机驱动器、触摸屏、显示驱动器、传感器、可移除存储器、电源管理集成电路或智能电池)。

[0066]

为此,可以提供实现以改善的aclr和低evm直接生成rf发送信号的移动设备。dac 720进行的改进的rf发送信号生成可以允许在发送路径中省略dpd,使得与传统技术相比可以减少移动设备的电流消耗。

[0067]

使用根据所提出的技术或上述一个或多个示例的dac的上述无线通信电路可以被配置为根据第3代合作伙伴项目(3gpp)标准化移动通信网络或系统之一进行操作。移动或无线通信系统可以对应于例如第5代新空口(5g nr)、长期演进(lte)、lte

‑

advanced(lte

‑

a)、高速分组接入(hspa)、通用移动电信系统(umts)或umts陆地无线接入网(utran)、演进

utran(e

‑

utran)、全球移动通信系统(gsm)、增强数据速率gsm演进(edge)网络或gsm/edge无线接入网(geran)。替代地,无线通信电路可以被配置为根据具有不同标准的移动通信网络进行操作,例如全球微波接入互操作性(wimax)网络ieee 802.16或无线局域网(wlan)ieee 802.11,一般地说是正交频分多址(ofdma)网络、时分多址(tdma)网络、码分多址(cdma)网络、宽带cdma(wcdma)网络、频分多址(fdma)网络、空分多址(sdma)网络等。

[0068]

本文描述的示例可以总结如下:

[0069]

示例1是一种dac,包括多个dac单元,所述多个dac单元耦合到所述dac的输出节点,其中,所述多个dac单元中的至少一个dac单元包括:容性元件,被配置为:向所述输出节点提供所述dac单元的模拟输出信号;反相器电路,耦合到所述容性元件,其中,所述反相器电路被配置为:基于振荡信号,生成所述容性元件的反相器信号;和阻性元件,耦合到所述反相器电路和所述容性元件,其中,所述阻性元件的电阻是至少50ω。

[0070]

示例2是如示例1所述的dac,其中,所述阻性元件的电阻是至少500ω。

[0071]

示例3是如示例1或示例2所述的dac,其中,所述阻性元件是薄膜电阻器。

[0072]

示例4是如示例1或示例2所述的dac,其中,所述阻性元件是多晶硅电阻器。

[0073]

示例5是如示例1或示例2所述的dac,其中,所述阻性元件是晶体管,并且其中,所述晶体管的控制端子被配置为:接收控制信号,以用于调整所述晶体管的输入端子与输出端子之间的电阻。

[0074]

示例6是如示例1至5中任一项所述的dac,其中,所述反相器电路包括串联耦合在第一电位与第二电位之间的至少两个晶体管,其中,所述至少两个晶体管中的每一个的阈值电压最大为所述第一电位与所述第二电位之间的电位差的25%。

[0075]

示例7是如示例6所述的dac,其中,所述阈值电压最大为所述第一电位与所述第二电位之间的电位差的15%。

[0076]

示例8是如示例1至7中任一项所述的dac,其中,在所述反相器电路与所述容性元件之间没有耦合另外的反相器电路。

[0077]

示例9是如示例1至8中任一项所述的dac,其中,所述多个dac单元中的所述至少一个dac单元还包括:逻辑电路,耦合到所述反相器电路,其中,所述逻辑电路被配置为:接收振荡信号和控制信号;以及基于所述控制信号,选择性地输出反相振荡信号,其中,所述反相器电路被配置为:基于所述反相振荡信号,生成所述反相器信号。

[0078]

示例10是如示例9所述的dac,其中,所述逻辑电路是nand门。

[0079]

示例11是如示例1至10中任一项所述的dac,其中,所述多个dac单元中的所述至少一个dac单元还包括:第二容性元件,被配置为:将所述dac单元的第二模拟输出信号供给到所述dac的第二输出节点;第二反相器电路,耦合到所述第二容性元件,其中,所述第二反相器电路被配置为:输出所述第二容性元件的第二反相器信号;和第二阻性元件,耦合在所述第二反相器电路与所述第二容性元件之间,其中,所述第二阻性元件的电阻等于所述阻性元件的电阻。

[0080]

示例12是如示例11所述的dac,其中,所述多个dac单元中的所述至少一个dac单元还包括:第二逻辑电路,耦合到所述第二反相器电路,其中,所述第二逻辑电路被配置为:接收第二振荡信号和第二控制信号,其中,所述第二振荡信号相对于所述振荡信号被反相,并且其中,所述第二控制信号相对于所述控制信号被反相;以及基于所述第二控制信号,选择

性地输出第二反相振荡信号,其中,所述第二反相器电路被配置为:基于所述第二反相振荡信号,生成所述第二反相器信号。

[0081]

示例13是如示例12所述的dac,其中,所述多个dac单元中的所述至少一个dac单元还包括:第三容性元件,被配置为:将所述dac单元的第三模拟输出信号供给到所述dac的所述第二输出节点;串联耦合的一对反相器电路,其中,所述一对反相器电路耦合到所述第三容性元件,并且其中,所述一对反相器电路被配置为:输出所述第三容性元件的第三反相器信号;和第三阻性元件,耦合在所述一对反相器电路与所述第三容性元件之间,其中,所述第三阻性元件的电阻等于所述阻性元件的电阻。

[0082]

示例14是如示例1至13中任一项所述的dac,其中,与所述多个dac单元中的所述至少一个dac单元相比,所述多个dac单元中的另一dac单元附加地包括:另一容性元件,耦合在地电位处的第一节点与布置在所述多个dac单元中的所述另一dac单元的所述阻性元件和所述容性元件之间的第二节点之间,其中,所述多个dac单元中的所述另一dac单元的所述另一容性元件和所述容性元件的总计容量等于所述多个dac单元中的所述至少一个dac单元的所述容性元件的容量。

[0083]

示例15是如示例14所述的dac,其中,所述多个dac单元中的所述另一dac单元的所述阻性元件的电阻等于所述多个dac单元中的所述至少一个dac单元的所述阻性元件的电阻。

[0084]

示例16是如示例1至13中任一项所述的dac,其中,所述多个dac单元是相同的。

[0085]

示例17是一种发射机,包括:如示例1至16中任一项所述的dac;和综合器电路,被配置为:基于要无线发送的数据,生成所述振荡信号。

[0086]

示例18是如示例17所述的发射机,其中,所述振荡信号的频率是至少100mhz。

[0087]

示例19是一种移动设备,包括:如示例17或示例18所述的发射机;和匹配电路,耦合到所述dac的所述输出节点,其中,所述匹配电路被配置为:向所述dac的所述输出节点呈现定义的电感。

[0088]

示例20是如示例19所述的移动设备,还包括耦合到所述匹配电路的至少一个天线元件。

[0089]

所提及和描述的方面和特征连同一个或多个先前详述的示例和附图也可以与一个或多个其他示例组合,以便替换其他示例的相似特征,或者以便附加地将特征引入其他示例。

[0090]

描述和附图仅示出本公开的原理。此外,本文叙述的所有示例主要明确地旨在仅用于说明性目的,以帮助读者理解本公开的原理和发明人为进一步推进本领域所贡献的构思。本文叙述本公开的原理、方面和示例及其具体示例的所有陈述旨在涵盖其等同物。

[0091]

框图可以例如示出实现本公开的原理的高层次电路图。类似地,流程图表、流程示图、状态转换图、伪码等可以表示各种过程、操作或步骤,它们可以例如基本上在计算机可读介质中表示并因此由计算机或处理器执行,而无论是否明确示出此类计算机或处理器。说明书中或权利要求中公开的方法可以由具有用于执行这些方法的各动作中的每一个的模块的设备来实现。

[0092]

应理解,说明书或权利要求中公开的多个动作、过程、操作、步骤或功能的公开可以不解释为在特定顺序内,除非明确或隐含地另外说明(例如,出于技术原因)。因此,除非

这些动作或功能出于技术原因而不是可互换的,否则多个动作或功能的公开将不把它们限制到特定顺序。此外,在一些示例中,单个动作、功能、过程、操作或步骤可以分别包括或可以分解为多个子动作、子功能、子过程、子操作或子步骤。除非明确排除,否则此类子动作可以被包括,并且是该单个动作的公开的一部分。

[0093]

此外,所附权利要求特此并入详细描述中,其中,每项权利要求可以自身代表单独的示例。虽然每项权利要求可以自身代表单独的示例,但是应注意,虽然从属权利要求可以在权利要求书中引用与一个或多个其他权利要求的特定组合,但是其他示例可以还包括该从属权利要求与每个其他从属权利要求或独立权利要求的主题的组合。除非声明并非旨在特定组合,否则本文明确提出此类组合。此外,旨在还将权利要求的特征包括到任何其他独立权利要求,即使该权利要求并非直接从属于该独立权利要求。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。