1.本实用新型涉及信号处理技术领域,尤其涉及一种数字信号处理装置。

背景技术:

2.传统的数字信号处理设备基本上采用dsp作为数字信号处理器,同时配合cpu或者arm等微处理器作为主控设备,对基带数据或者光纤接收的数据进行数字信号处理。该系统对于并行多通道的大数据处理需要多个模块并且系统复杂度极高。因此,如何解决现有系统存在的问题,是现阶段需要考虑的。

技术实现要素:

3.本实用新型的目的在于克服现有技术的缺点,提供一种数字信号处理装置,解决了传统数字信号处理设备存在的问题。

4.本实用新型的目的通过以下技术方案来实现:一种数字信号处理装置,它包括信号处理模块、外围接口模块、时钟模块和供电模块;所述外围接口模块与所述信号处理模块连接,所述时钟模块通过pll锁相环卫所述外围接口模块提供时钟参考;所述供电模块与所述信号处理模块和外围接口模块连接,通过dc

‑

dc及ldo转换为其进行供电;所述信号处理模块还连接有flash和ddr,并提供相应的调试接口和控制接口。

5.进一步地,所述外围接口模块包括rj45接口、qsfp 光模块和j30j连接器;所述信号处理模块连接一个以太网控制器,所述以太网控制器连接变压器,所述变压器连接rj45接口。

6.进一步地,所述信号处理模块包括两片型号为jfm7vx690t80的fpga芯片;所述两片fpga芯片外围分别各连接一个以太网控制器,所述以太网控制器连接变压器,所述变压器连接rj45接口

7.进一步地,所述qsfp 光模块的数量为两个,每个fpga芯片与一个qsfp 光模块连接;所述j30j连接器通过电平转换芯片与两个fpga芯片连接,分别实现rs232、jtag和gpio的调试。

8.进一步地,所述供电模块包括背板vpx和电源单元;所述信号处理模块与所述背板vpx连接,所述背板vpx与所述电源单元连接;所述电源单元包括dc

‑

dc转换子单元和ldo芯片,所述背板vpx输出12v直流电压经过dc

‑

dc转换子单元和ldo芯片转换后为各个模块供电。

9.本实用新型具有以下优点:

10.1、采用6u vpx架构,可靠性以及散热、功耗有保证。

11.2、采用2片690t fpga作为数字信号处理核心,能并行处理多通道数字信号。

12.3、板载高稳ocxo以及时钟单元,为并行处理多通道数据提供稳定时钟。时钟源支持外供时钟,提供用户时钟选择。

13.4、采用2个qsfp 光模块接口,最多提供8路光纤并行数据处理通道。

14.5、单板设计大容量ddr3缓存颗粒,用于2片fpga协同处理多通道高速数据。

15.6、单板每一片fpga提供1路千兆以太网接口,方便用户使用上位机管理设备以及和设备之间传输数据。

附图说明

16.图1 为本实用新型的结构示意图;

17.图2 为jtag连接示意图;

18.图3 为rj45接口连接示意图;

19.图4 为qsf 接口连接示意图;

20.图5 为j30j调试接口连接示意图;

21.图6 为背板vpx的高速信号连接示意图;

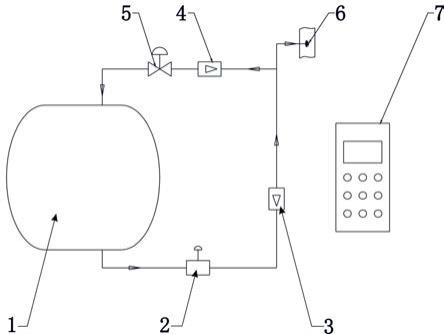

22.图7 为电源连接示意图;

23.图8 为电源详细连接示意图;

24.图9 为时钟连接示意图。

具体实施方式

25.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。因此,以下结合附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的保护范围,而是仅仅表示本技术的选定实施例。基于本技术的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。下面结合附图对本发明做进一步的描述。

26.如图1所示,本实用新型涉及一种数字信号处理装置,它包括信号处理模块、外围接口模块、时钟模块和供电模块;所述外围接口模块与所述信号处理模块连接,所述时钟模块通过pll锁相环卫所述外围接口模块提供时钟参考;所述供电模块与所述信号处理模块和外围接口模块连接,通过dc

‑

dc及ldo转换为其进行供电;所述信号处理模块还连接有flash和ddr,并提供相应的调试接口和控制接口。

27.其中,信号处理模块核心为两片型号为jfm7vx690t80的fpga芯片,该芯片与xilinx的xc7vx690t

‑

ffg1927兼容,负责信号处理以及提供外围接口。

28.2片jfm7vx690t80采用复旦微电子的16mb容量串行接口 flash存储器,可用于为fpga上电加载系统文件,系统文件版本确定之后最终可固化到flash中,因此2片fpga各有一个flash。jfm7系列fpga的配置方式大致可以分为串行和并行两种方式,其中串行方式主要是为了使配置引脚的数量最小化,并行方式则是为了更高的性能及标准接口连接。并行接口支持4

‑

bit、8

‑

bit、16

‑

bit或32

‑

bit位宽。

29.efm25f128a属于非挥发存储器,可多次写入写出,该容量用于整机系统中的程序存储介质容易足够了,该芯片带有写保护功能,可配置成软保护模式,且该芯片支持标准的fast read、dual read、quad read,依次可编程1~256 byte,可以进行扇区以及全芯片擦除操作。flash支持

‑

0.2v~4v的io电平标准,因为fpga支持hp,故本实用新型使用1.8v电平标

准设计,相应的连接到fpga的hp bank,bank电平为1.8v。

30.如图2所示,fpga在上电完成之后可采用jtag方式重新配置。jtag在fpga上电后的任意时刻均可通过仿真器配置fpga, jfm7系列还需要用到电平转换芯片,选择常用的sn74avc4t774芯片,电平转换芯片将fpga端的lvcmos18电平转换成外接口的lvcmos33。配置电平转换的方向为:tms、tdi、tck为jtag接插件到fpga方向,tdo为fpga到jtag接插件方向。

31.每个fpga的 pl端需满足设计满足ddr3为1gb。可选用常用的mt41k256m16,必须挂载32bit的ddr3颗粒才能满足需求1gb容量,选用两片mt41k256m16。

32.如图3所示,以太网部分采用pl端部分提供的以太网接口外加以太网phy的方式,以太网phy选用88e1111, 88e1111

‑

xx

‑

bab

‑

i000是mavell公司的款千兆以太网收发器;2片fpga外围分别各有一个以太网控制器,外置变压器,以太网接口对外采用rj45,对内接口实现千兆以太网,以太网接口的参考时钟要求不高,故选用了为低功耗、高精度的cmos晶振提供,供电电压1.8v,稳定度

±

25ppm,输出单端的125m时钟。

33.如图4所示,两片fpga采用两个单模的qsfp ,lc接口,单模qsfp 光模块的传输距离较长。vpx背面中的所有数据采集在fpga中,或者将光口从数据采集在fpga中,并在fpga代码中使用ip核aurora将数据恢复出来,通过单模光纤线传输可以实现不同的传输距离。

34.如图5所示,j30j接口主要是板卡的调试接口,为满足各个调试线的需求,选用的j30j接口为31pin,调试分别时rs232、jtag、gpio,为了防止fpga i/o接,接口被损坏,将外接口都加上电平转换芯片,电平转换芯片选用常用的sn74avc4t774芯片,支持电平方向可控,电平转换芯片作用一:起一定的隔离作用,作用二:将fpga的lvcmos18转换成lvcmos33。

35.如图6

‑

图8所示,p2、p3用于高速信号的传输。高速信号线共连接了16个lane,分布在fpga的四个bank,整板电源通过背板的vpx直流12v供电。电源芯片主要使用开关电源模块和ldo为主。使用开关电源模块主要是为了减少电源分立器件的数量,简化设计并保证电源的稳定性,并将电源芯片的power good 指示灯接到fpga检测。

36.其中,lym4644iy为板上大部分器件提供电源,减少了电源分离个数,本实用新型用2片lym4644iy输出4路电压。lym4644iy的外围电路很简单,和ti的ltm4644时兼容的,外部只需要接少许的电阻电容即可。

37.lym4627iv提供的电流能力为15a,为板上大电流需求器件提供电源,主要包括fpga核心电压。本实用新型在一个半高的lga封装内组合了一个带有功率金属氧化物半导体场效应管(mosfet)的15a dc

‑

dc转换器、一个屏蔽电感器以及无源元件。lym4627iv的外围电路很简单,外部只需要接少许的电阻电容即可。

38.如图9所示,时钟模块的时钟参考源为板载tcxo,支持外供时钟输入以及参考时钟输出,用户可选。背板的vpx gth由fpga数字基带板提供参考时钟2路参考时钟。

39.板上时钟需求较简单,fpga需要提供125m系统时钟,此外采用lmk04828给fpga、光口和gth等提供备用时钟,以便满足灵活的应用。

40.本实用新型得益于近年fpga技术的飞速发展,采用单板采用2片fpga作为数字信号处理核心,外部配合多通道光纤、高速vpx背板以及ddr3作为缓存存储单元。对各类射频前端或者光纤传输的多通道基带数据进行并行处理。并且2片fpga之间提供片间高速gth接口,使得单板2片fpga能进行协同数字信号处理。

41.本实用新型集成时钟模块,板载高稳ocxo,为数字信号处理提供高稳时钟源,同时,每片fpga提供1路千兆以太网接口,提供上位机对该设备的管理接口。

42.该设备在提供同样数据吞吐量的数据处理时,大大减小设备体积以及设备功耗,同时单板采用6u vpx架构,在结构可靠性方面以及散热方面提供了保证。

43.以上所述仅是本发明的优选实施方式,应当理解本发明并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。