1.本发明涉及集成电路技术领域,具体涉及一种输出端无过冲电压的线性稳压器电路。

背景技术:

2.线性稳压器电路广泛地应用在各种芯片设计以及电子系统设计中,它具有较低的漏失电压(输入和输出的压差)。在理想的情况下,线性稳压器电路能够输出可调节或固定的输出电压,该输出电压不随时间和温度变化,并且不受线路和负载变化的影响。

3.传统的线性稳压器电路如附图1所示,由运算放大器op、输出驱动管pmos、以及反馈电阻r1和r2组成。该线性稳压器电路采用pmos管作为输出驱动管,可以支持低压差应用,但快上电或输出端负载突变时输出电压会有过冲,即当电源快速上电(即以纳秒级快速上电到所需工作电压vcc)时,电路内部器件工作点建立的过程中,使输出驱动pmos管的栅极电压从低电平开始充电,输出驱动pmos管会产生巨大的瞬时导通电流,把ldo的输出端充到较高的电压,从而产生过冲现象。较高的过冲电压会给线性稳压器后级电路造成不可恢复的电应力损伤。现有技术大多数基于调整运算放大器op的内部设计来降低线性稳压器输出端的过冲电压,这些技术在降低线性稳压器输出端过冲电压的同时,也降低了线性稳压器的瞬态响应速度。

4.因此需要一个新的稳压器电路,能够在不改变线性稳压器瞬态特性的前提下,通过对线性稳压器输出端快速泄电的技术,可以有效降低线性稳压器输出端的过冲电压;从而保护其后级电路免受过电损伤。

技术实现要素:

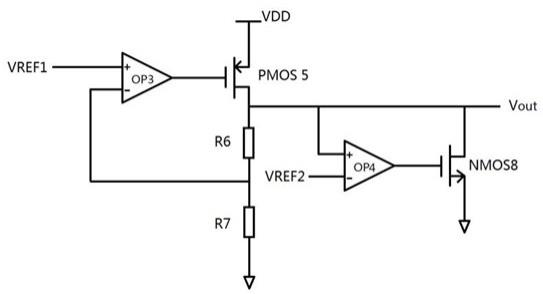

5.1.所要解决的技术问题:针对上述技术问题,本发明提供一种输出端无过冲电压的线性稳压器电路,本发明在典型线性稳压器电路基础上,增加一个比较器op4和一个泄流mos管nmos8;比较器op4用于将线性稳压器输出端电压vout和基准电压vref2进行比较,并根据比较结果输出一个控制nmos8栅极的电压,由此控制nmos8对输出端vout的泄电电流大小,以降低输出端vout的过冲电压。

6.2.技术方案:一种输出端无过冲电压的线性稳压器电路,其特征在于:包括运算放大器op3、晶体管pmos5、电阻r6、电阻r7、比较器op4、晶体管pmos5;所述运算放大器op3的正输入端与基准电压vref1相连;运算放大器op3的输出端与晶体管pmos5的g端相连;晶体管pmos5的s端连接电源电压vdd;晶体管pmos5的d端连接电阻r6;电阻r6连接电阻r7后,r7接地;所述运算放大器op3的负输入端连接至电阻r6与电阻r7的连接线上;晶体管pmos5的d端与比较器op4的正输入端相连;比较器op4的负输入端输入基准电压vref2,比较器op4的输出端与晶体管nmos8的g端相连;晶体管nmos8的d端与 晶体管pmos5的d端相连至输出电压vout;晶体管

nmos8的s端接地。

7.进一步地,所述基准电压vref2预设为在线性稳压器理论输出电压值vout0加上0.1v至0.3v之间的任意数值电压。

8.进一步地,所述比较器op4由线性稳压器输出端vout提供供电电源,基准电压vref2与比较器op4的负相输入端相连。

9.进一步地,所述晶体管nmos8为集成n型金属氧化物半导体场效应晶体管mos

‑

fet,其阈值电压介于0.5v至2.5v之间的任意数值电压。

10.3.有益效果:本发明提供的线性稳压器电路,是在典型线性稳压器基础上新增一个比较器op4和一个泄流mos管nmos8,即可在不改变线性稳压器瞬态特性前提下,可以有效降低线性稳压器电路输出端的过冲电压。

附图说明

11.图1为现有技术的线性稳压器电路的电路图;图2为本发明提供的线性稳压器电路电路图。

具体实施方式

12.下面结合附图对本发明进行具体的说明。

13.如附图2所示,一种输出端无过冲电压的线性稳压器电路,其特征在于:包括运算放大器op3、晶体管pmos5、电阻r6、电阻r7、比较器op4、晶体管pmos5;所述运算放大器op3的正输入端与基准电压vref1相连;运算放大器op3的输出端与晶体管pmos5的g端相连;晶体管pmos5的s端连接电源电压vdd;晶体管pmos5的d端连接电阻r6;电阻r6连接电阻r7后,r7接地;所述运算放大器op3的负输入端连接至电阻r6与电阻r7的连接线上;晶体管pmos5的d端与比较器op4的正输入端相连;比较器op4的负输入端输入基准电压vref2,比较器op4的输出端与晶体管nmos8的g端相连;晶体管nmos8的d端与 晶体管pmos5的d端相连至输出电压vout;晶体管nmos8的s端接地。

14.进一步地,所述基准电压vref2预设为在线性稳压器理论输出电压值vout0加上0.1v至0.3v之间的任意数值电压。

15.进一步地,所述比较器op4由线性稳压器输出端vout提供供电电源,基准电压vref2与比较器op4的负相输入端相连。

16.进一步地,所述晶体管nmos8为集成n型金属氧化物半导体场效应晶体管mos

‑

fet,其阈值电压介于0.5v至2.5v之间的任意数值电压。

17.下面对本专利实现原理进行分析:现有技术中的线性稳压器的输出端电压vout与基准电压vref1之间的关系,可由运算放大器op3两个输入端“虚短”的原理,即运算放大器正相输入端的电压等于负相输入端的电压,即为:根据输出端电压采样原理,得出:

联立上述两式,可得出:上式便是线性稳压器电路输出电压与输入基准电压之间的理论v

out0

计算公式。

18.本方案中,将基准电压vref2电压设置在线性稳压器理论输出电压值vout0 0.1v。根据比较器op4的工作原理,op4的输出电压vop4可由下式表示。

19.上式中av_op4是比较器op4的放大倍数。当线性调整器的输出端电压vout比其理论电压vout0高出0.1v后,vop4的电压就由上述表达式计算得出。

20.因vop4电压控制nmos8管对线性调制器输出端的泄电电流ids8的大小,其值由下述表达式确定:联合前述分析,可得知线性稳压器输出端过冲电压泄电电流ids8的最终表达式为:由上式可知,若线性稳压器输出端过冲电压越大,nmos8管对输出端的泄电电流也就越大,两者之间呈现平方律的关系。

21.本发明提供的一种输出端无过冲电压的线性稳压器电路中,运输放大器op4和nmos8组成的快速降低输出端过冲电压电路,能非常迅速的控制线性稳压器的泄电电流,从而能较好的控制线性稳压器输出端的电压,这一技术对快速响应线性稳压器的设计具有较好的参考意义。

22.虽然本发明已以较佳实施例公开如上,但它们并不是用来限定本发明的,任何熟习此技艺者,在不脱离本发明之精神和范围内,自当可作各种变化或润饰,因此本发明的保护范围应当以本申请的权利要求保护范围所界定的为准。

技术特征:

1.种输出端无过冲电压的线性稳压器电路,其特征在于:包括运算放大器op3、晶体管pmos5、电阻r6、电阻r7、比较器op4、晶体管pmos5;所述运算放大器op3的正输入端与基准电压vref1相连;运算放大器op3的输出端与晶体管pmos5的g端相连;晶体管pmos5的s端连接电源电压vdd;晶体管pmos5的d端连接电阻r6;电阻r6连接电阻r7后,r7接地;所述运算放大器op3的负输入端连接至电阻r6与电阻r7的连接线上;晶体管pmos5的d端与比较器op4的正输入端相连;比较器op4的负输入端输入基准电压vref2,比较器op4的输出端与晶体管nmos8的g端相连;晶体管nmos8的d端与 晶体管pmos5的d端相连至输出电压vout;晶体管nmos8的s端接地。2.根据权利要求1所述的一种输出端无过冲电压的线性稳压器电路,其特征在于:所述基准电压vref2预设为在线性稳压器理论输出电压值vout0加上0.1v至0.3v之间的任意数值电压。3.根据权利要求1所述的一种输出端无过冲电压的线性稳压器电路,其特征在于:所述比较器op4由线性稳压器输出端vout提供供电电源,基准电压vref2与比较器op4的负相输入端相连。4.根据权利要求1所述的一种输出端无过冲电压的线性稳压器电路,其特征在于:所述晶体管nmos8为集成n型金属氧化物半导体场效应晶体管mos

‑

fet,其阈值电压介于0.5v至2.5v之间的任意数值电压。

技术总结

本发明公开了一种输出端无过冲电压的线性稳压器电路,具体为运算放大器OP3的正输入端与基准电压VREF1相连,输出端与晶体管PMOS5的G端相连;晶体管PMOS5的S端连接电源电压VDD;晶体管PMOS5的D端连接电阻R6;电阻R6连接电阻R7后,R7接地;所述运算放大器OP3的负输入端连接至电阻R6与电阻R7的连接线上;晶体管PMOS5的D端与比较器OP4的正输入端相连;比较器OP4的负输入端输入基准电压VREF2,比较器OP4的输出端与晶体管NMOS8的G端相连;晶体管NMOS8的D端与晶体管PMOS5的D端相连至输出电压Vout;晶体管NMOS8的S端接地。本发明是在典型线性稳压器基础上新增一个比较器OP4和一个泄流MOS管NMOS8,即可在不改变线性稳压器瞬态特性前提下,可以有效降低线性稳压器电路输出端的过冲电压。端的过冲电压。端的过冲电压。

技术研发人员:赵星 胡瑞芳 彭力 李禄 曹发兵 冯冰

受保护的技术使用者:江苏万邦微电子有限公司

技术研发日:2021.05.25

技术公布日:2021/9/9

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。