1.所要求保护的发明涉及雪崩光电探测器(apd),apd是快速且高灵敏度的仪器,广泛用于lidar、通信系统、机器视觉、机器人、医学、生物学、环境监测等。

背景技术:

2.常规的雪崩光电探测器(apd)包括放置在半导体晶片上的多个半导体层。

3.一组半导体层形成光电转换器,在光电转换器中,信号光子被吸收以产生自由载流子,即电子或电子空穴。这些光产生的电荷载流子然后进入另一组半导体层,即雪崩放大器,在雪崩放大器内部形成电场强度足以使电荷载流子雪崩式倍增的区域。

4.为了减小雪崩放大器的暗电流,从而提高apd的阈值灵敏度,可以使雪崩放大器所占的面积相对于光电转换器所占的面积更小。

5.在专利us 9,035,410和ru 2,641,620公开的apd中,包括两层(接触层和倍增层)的雪崩放大器和光电转换器均位于同一晶片上,其中光电转换器的面积大于放大器的面积。

6.此类仪器的参数可以附加地被优化,即可以通过缩小雪崩放大器的面积来提高阈值灵敏度。在根据专利ru 2,641,620的apd中,倍增层由导电类型与信号光电转换器的导电类型相同的半导体材料制成,面向晶片并与自主光电转换器邻接,这允许减少由通过外部电路从光电转换器传输到雪崩放大器的光载流子引起的过度暗噪声(参见us 9,035,410)。

7.在根据专利ru 2,641,620的apd中,倍增层独立于光电转换器制成,这阻碍了光电转换器层中产生的光载流子到达倍增层,从而导致成倍的光信号损失。这导致阈值灵敏度下降,该阈值灵敏度是apd的基本参数。

8.本发明的目的是制造具有高阈值灵敏度的雪崩光电探测器(apd),该apd将不受光载流子从光电转换器到雪崩放大器的低效传输的限制。此外,要求保护的apd的建议的实施例允许减少apd的暗电流。

9.通过解决这些问题,将可能提高作为apd的基本参数的阈值灵敏度。

技术实现要素:

10.要求保护的发明包括雪崩光电探测器(apd)以及用于制造该apd的方法,其允许通过将倍增层全部放置在导电晶片上方来使光载流子从光电转换器到雪崩放大器的传输更高效。至少一个雪崩放大器的接触层形成在倍增层的某一区域中。因此,接触层外部的倍增层作为光电转换器起作用。结果,已在光电转换器中被引发的光载流子将无阻碍地进入雪崩放大器的倍增区域。雪崩光电探测器的第一电极和第二电极分别放置在接触层和晶片上。

11.为了减轻寄生近表面电荷载流子对雪崩放大器的影响,通过在倍增层中蚀刻凹口并在所述凹口的底部处形成雪崩放大器的接触层,来相对于光电转换器区域的上表面加深雪崩放大器的倍增区域。

12.为了减少apd的来自相邻晶片区域的暗电流,在倍增层表面上蚀刻封闭凹槽,封闭凹槽的深度大于或等于倍增层的厚度,但小于晶片和倍增层的组合的总厚度,并且在由所述凹槽界定的区域内部形成光电探测器。凹槽填充有导电类型与倍增层的导电类型相同的高掺杂多晶硅。

13.为了提高效率,半导体晶片应该由低电阻材料制成。

14.晶片和倍增层两者由相同的半导体材料制成是可行的。

15.晶片表面上的倍增层可以使用外延方法制成,并且可以通过用形成具有相反导电性的层的掺杂剂掺杂倍增层来制成接触层。

16.凹槽的宽度为1.5μm至2.0μm也是可行的。

17.还可以将高电阻层放置在雪崩放大器的接触层与第一电极之间。

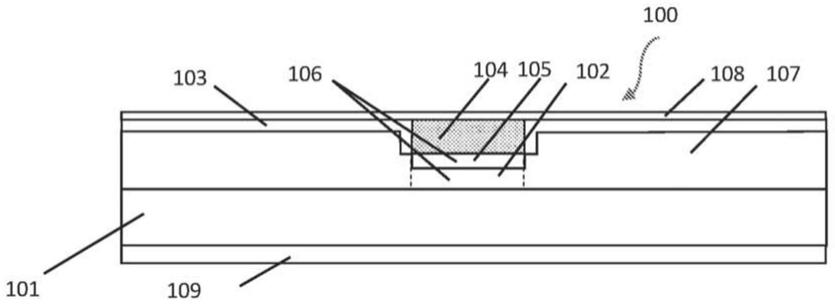

附图说明

18.本发明的目的、特征和优点将在详细说明和附图中进一步指出。

19.图1是根据第一实施例的所要求保护的apd的示意性横截面,该apd包括:半导体晶片101;倍增层102,覆盖导电类型与倍增层的导电类型相同的半导体晶片的整个表面;介电层103,覆盖倍增层102表面和凹口104的侧壁,凹口104的深度为0.5μm

‑

2.5μm,以用于接触层105;接触层105,通过导电性与倍增层的导电性相反的高掺杂多晶硅的扩散制成,其中至少一个雪崩放大器106和位于雪崩放大器外部的光电转换器107被形成;第一电极108,位于填充凹口104的高掺杂多晶硅和透明介电层103的顶部上;以及第二电极109,形成在半导体晶片101的底表面上。

20.图1a示出了将倍增层102放置在硅晶片101上的工艺。

21.图1b示出了将介电层103放置在倍增层102上的工艺。

22.图1c示出了通过填充凹口104的导电性与倍增层的导电性相反的高掺杂多晶硅的扩散而创建接触层105,来形成雪崩放大器106区域的工艺,凹口104深度为0.5μm

‑

2.5μm,其中至少一个雪崩放大器106和位于雪崩放大器外部的光电转换器107被形成。

23.图1d示出了在填充凹口104的高掺杂多晶硅和介电层103的表面上形成由透明导电材料制成的第一电极108的工艺。

24.图1e示出了在半导体晶片101上形成第二电极109的工艺。

25.图2是根据第二实施例的所要求保护的apd的示意性横截面,该apd包括:半导体晶片201;倍增层202,覆盖导电类型与倍增层的导电类型相同的半导体晶片的整个表面;介电层203,覆盖倍增层202的表面和用于接触层205的凹口204的侧壁;接触层205,通过导电性与倍增层的导电性相反的高掺杂多晶硅的扩散制成,该高掺杂多晶硅填充深度为0.5μm

‑

2.5μm的凹口204,其中至少一个雪崩放大器206和光电转换器207被形成;封闭凹槽210,该封闭凹槽的宽度为1.5μm至2.0μm并且深度大于或等于倍增层厚度但小于晶片和倍增层的组合的总厚度,该封闭凹槽210填充有导电类型与倍增层的导电类型相同的高掺杂多晶硅,并环绕雪崩放大器和光电转换器;高电阻层211,形成在填充凹口204的高掺杂多晶硅上;透明电极208,形成在高电阻层211和介电层203的表面上;以及第二电极209,形成在半导体晶片201上。

26.图2a示出了将倍增层202放置在硅晶片201上的工艺。

27.图2b表示形成封闭凹槽210的工艺,该封闭凹槽210填充有导电类型与倍增层的导电类型相同的高掺杂多晶硅,使得光电探测器可以形成在由所述凹槽界定的区域内部。

28.图2c示出了将介电层203放置在倍增层202上的工艺。

29.图2d示出了通过填充凹口204的导电性与倍增层的导电性相反的高掺杂多晶硅的扩散而创建接触层205,来形成雪崩放大器206区域的工艺,凹口104深度为0.5μm

‑

2.5μm,其中至少一个雪崩放大器206和位于雪崩放大器外部的光电转换器207被形成。

30.图2e示出了在雪崩放大器206的接触层205上形成高电阻层211的工艺。

31.图2f示出了在填充凹口204的高掺杂多晶硅和介电层203的表面上形成由透明导电材料制成的第一电极208的工艺。

32.图2g示出了在半导体晶片201上形成第二电极209的工艺。

33.图3a是根据第二实施例的包括单个雪崩放大器206和凹槽210在内的apd的示意性俯视图。

34.图3b是根据第二实施例的包括三个雪崩放大器206和凹槽210在内的apd的示意性俯视图。

具体实施方式

35.在本公开和附图中使用的附图标记(除了编号100(入射光)之外)由三位数字组成,其中第一位数字是图编号,最后两位数字标记设计的特定元素。

36.例如,标记206指向图2中的元素编号06(参见下面的列表)。

37.以下标记用于指向设计的特定元素:

38.01

‑

晶片,

39.02

‑

倍增层,

40.03

‑

介电层,

41.04

‑

填充有高掺杂多晶硅的凹口,

42.005

‑

接触层,

43.06

‑

雪崩放大器,

44.07

‑

光电转换器,

45.08

‑

第一透明电极,

46.09

‑

第二电极,

47.10

‑

封闭凹槽,

48.11

‑

高电阻材料层。

49.图1示出了根据第一实施例的所要求保护的apd的示意性横截面,该apd包括:半导体晶片101;倍增层102,覆盖导电类型与倍增层的导电类型相同的半导体晶片的整个表面;介电层103,覆盖倍增层102的表面;凹口104,填充有高掺杂多晶硅;接触层105,通过来自导电性与倍增层的导电性相反的高掺杂多晶硅的掺杂剂的扩散制成,其中,至少一个雪崩放大器106和位于雪崩放大器外部的光电转换器107被形成;第一电极108,由透明材料制成,所述第一电极108位于填充凹口104的高掺杂多晶硅和介电层103的顶部上;以及第二电极109,形成在半导体晶片101的底表面上。

50.用于制造图1所示的apd的方法进一步由图1a、图1b、图1c、图1d和图1e示出,包括

以下顺序的步骤:

51.将导电类型与晶片的导电类型相同的倍增层102放置在硅晶片101上(见图1a)。

52.将介电层103放置在倍增层102的顶部上(见图1b)。

53.在倍增层中,通过以下操作形成一个或多个雪崩放大器106区域:在介电层103和倍增层102两者中蚀刻0.5μm

‑

2.5μm深的凹口104,用介电层覆盖凹口104的侧壁并用高掺杂多晶硅填充凹口104(见图1c)。

54.通过来自填充凹口104的导电性与倍增层的导电性相反的高掺杂多晶硅的掺杂剂的扩散来形成接触层105,其中至少一个雪崩放大器106和雪崩放大器外部的光电转换器107被形成(见图1c)。

55.在填充凹口104的高掺杂多晶硅和介电层103的表面上形成由透明导电材料制成的第一电极108(见图1d)。

56.在半导体晶片101的底面上形成第二电极109(见图1e)。

57.可以使用涉及通过外延法形成倍增层102的方法来制造根据图1的示例性apd,倍增层102的宽度为5μm

‑

7μm,并且在掺杂浓度高于10

18

cm

‑3的p 型硅晶片101上由掺杂浓度为10

15

cm

‑3‑

10

17

cm

‑3的p型硅制成。通过以下操作在倍增层表面上形成至少一个雪崩放大器106:在介电层103和倍增层102两者上蚀刻0.5μm

‑

2.5μm深的凹口104,用介电层覆盖凹口104的侧壁,并用掺杂浓度高于10

18

cm

‑3且导电性与倍增层102的导电性相反的高掺杂多晶硅填充凹口104,然后使所述掺杂剂扩散到倍增层102中以形成接触层105,其中,在雪崩放大器106外部形成光电转换器层107。由ito或azo类型的透明材料制成的第一电极108形成在填充凹口104的高掺杂多晶硅和介电层104的表面上,而第二电极109形成在半导体晶片101的底表面上,该第二电极109是厚度约为0.5μm

‑

1.0μm的铝箔。

58.如图1所示的apd操作如下:

59.相对于电极109向电极106施加正电压,以足以触发雪崩放大器106的倍增层102中的碰撞电离,从而导致自由电荷载流子倍增。

60.落在光电转换器107的表面上的入射光100被吸收,产生自由电荷载体,即电子和电子空穴。在光电转换器107中的已由光导致的自由电子(光电子)在电场叠加(其中电场之一从雪崩放大器106渗出,另一电场由光电转换器中的第一电极108引起)的驱动下向雪崩倍增层102漂移,并在那里进行倍增,产生apd的输出信号,同时空穴进入晶片101。在光电转换器107的非耗尽区域中的已由光导致的光电子通过由光电转换器中的自由电子浓度梯度引起的扩散而聚集在光电转换器的耗尽区域中。

61.为了减轻寄生近表面电荷载流子对雪崩放大器的影响,

62.通过在倍增层中蚀刻凹口104并在所述凹口的底部处形成雪崩放大器106的接触层105,来相对于光电转换器区域的上表面加深雪崩放大器的倍增区域。同时,来自实际长波记录信号的光载流子可以高效地从光电转换器进入雪崩放大器区域,而暗载流子从电介质

‑‑

光电转换器界面的流入受到阻碍。

63.图2示出了根据第二实施例的所要求保护的apd的示意性横截面,该apd包括:半导体晶片201;倍增层202,覆盖导电类型与倍增层的导电类型相同的半导体晶片的整个表面;介电层203,覆盖倍增层202的表面;凹口204,填充有高掺杂多晶硅;接触层205,通过来自导电性与倍增层的导电性相反的高掺杂多晶硅的掺杂剂的扩散制成,该高掺杂多晶硅填充深

度为0.5μm

‑

2.5μm的凹口204,其中至少一个雪崩放大器206和位于雪崩放大器外部的光电转换器207被形成;封闭凹槽210,该封闭凹槽的宽度为1.5μm至2.0μm并且深度大于或等于倍增层厚度但小于晶片和倍增层的组合的总厚度,该封闭凹槽210填充有导电类型与倍增层的导电类型相同的高掺杂多晶硅,并环绕雪崩放大器和光电转换器;高电阻层211,形成在填充凹口204的高掺杂多晶硅上;透明电极208,形成在高电阻层211和介电层203的表面上;以及第二电极209,形成在半导体晶片201上。

64.用于制造图2所示的apd的方法进一步由图2a、图2b、图2c、图2d、图2e、图2f和图2g示出,并且包括以下顺序的步骤:

65.将导电类型与晶片的导电类型相同的倍增层202放置在硅晶片201上(见图2a)。

66.在倍增层202的表面上蚀刻封闭凹槽210,该封闭凹槽210的深度大于或等于倍增层厚度,但小于晶片和倍增层的组合的总厚度,并且该封闭凹槽210填充有导电类型与倍增层202的导电类型相同的高掺杂多晶硅,使得可以在由所述凹槽界定的区域内部形成光电探测器(见图2b)。

67.将介电层203放置在倍增层202和凹口204上(见图2c)。

68.在倍增层中,通过以下操作形成一个或多个雪崩放大器206区域:在介电层203和倍增层202两者中蚀刻深度为0.5μm

‑

2.5μm的凹口204,用介电层覆盖凹口204的侧壁并用高掺杂多晶硅填充凹口204(见图2d)。

69.通过来自填充凹口204的导电性与倍增层的导电性相反的高掺杂多晶硅的掺杂剂的扩散来形成接触层205,其中至少一个雪崩放大器206和雪崩放大器外部的光电转换器207被形成(见图2d)。

70.在填充凹口204的高掺杂多晶硅的表面上形成高电阻层211(见图2e)。

71.在高电阻层211和介电层203的顶部上形成由透明导电材料制成的第一电极208(见图2f);

72.在半导体晶片201的底表面上形成第二电极209(见图2g)。

73.可以使用涉及通过外延法形成倍增层202的方法来制造根据图2的示例性apd,倍增层202的宽度为5μm

‑

7μm,并且在掺杂浓度高于10

18

cm

‑3的p 型硅晶片201上由掺杂浓度为10

15

cm

‑3‑

10

17

cm

‑3的p型硅制成。然后,在倍增层202的表面上蚀刻封闭凹槽210,该封闭凹槽210的宽度为1.5μm至2.0μm,并且深度大于或等于倍增层厚度但小于晶片和倍增层的组合的总厚度,并且该封闭凹槽210填充有导电类型与倍增层202的导电类型相同的高掺杂多晶硅,使得可以在由所述凹槽界定的区域内部形成光电探测器。通过以下操作在倍增层202表面上形成至少一个雪崩放大器205:在介电层和倍增层两者上蚀刻深度为0.5μm

‑

2.5μm的凹口,用介电层覆盖凹口的侧壁,并用掺杂浓度高于10

18

cm

‑3且导电性与倍增层202的导电性相反的高掺杂多晶硅填充凹口,然后使所述掺杂剂扩散到倍增层202中以形成接触层205,其中,在雪崩放大器206外部形成光电转换器层207。在填充凹口204的高掺杂多晶硅上形成由高电阻多晶硅制成的高电阻层211。由ito或azo类型的透明材料制成的第一电极207形成在高电阻层211和介电层203两者的顶部上,而第二电极208形成在半导体晶片201的底表面上,第二电极208为厚度约为0.5μm

‑

1.0μm的铝箔。

74.根据如图2所示的实施例的apd(即具有封闭凹槽210)的特征在于,它允许抑制从相邻区域进入雪崩放大器的寄生电荷载流子的流入。为了有效地抑制这种寄生电流,深度

大于倍增层厚度的凹槽将填充有导电类型与倍增层的导电类型相同的高掺杂多晶硅。apd中的较少的暗电流导致阈值灵敏度的附加提高。

75.当雪崩被形成时,位于填充凹口104的高掺杂多晶硅的顶部上的高电阻层211提供负反馈,从而允许实现更高的倍增系数,特别是当以所谓的“盖革(geiger)”模式操作时。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。