1.本发明涉及一种半导体结构及其制造方法,尤其涉及一种存储器结构及其制造方法。

背景技术:

2.随着存储器元件逐渐缩小,上下相邻的导电层之间的重叠裕度(overlay window)也会变小,因此容易发生对准偏差。如此一来,当上下相邻的导电层产生重叠偏差(overlay shift)时,容易在存储器元件中产生电性缺陷(如,电路桥接(circuit bridging)等)。

技术实现要素:

3.本发明提供一种存储器结构及其制造方法,其可有效地提高重叠裕度。

4.本发明提出一种存储器结构,包括基底、位线结构、接触窗结构与电容器结构。位线结构位于基底上。接触窗结构位于位线结构一侧的基底上。电容器结构位于接触窗结构上。电容器结构包括第一电极、第二电极与绝缘层。第一电极包括第一底面与第二底面。第一底面低于第二底面。第一底面仅位于部分接触窗结构上。第二电极位于第一电极上。绝缘层位于第一电极与第二电极之间。

5.本发明提出一种存储器结构的制造方法,包括以下步骤。在基底上形成位线结构。在位线结构一侧的基底上形成接触窗结构。在接触窗结构上形成电容器结构。电容器结构包括第一电极、第二电极与绝缘层。第一电极以错位方式位于接触窗结构上。第一电极包括第一底面与第二底面。第一底面低于第二底面。第一底面位于接触窗结构上。第二电极位于第一电极上。绝缘层位于第一电极与第二电极之间。

6.基于上述,在上述存储器结构及其制造方法中,第一电极的第一底面低于第一电极的第二底面。如此一来,即使在第一电极与接触窗结构之间发生重叠偏差,也不容易在相邻两个接触窗结构之间形成桥接路径。因此,通过第一电极的上述结构设计,可有效地提升第一电极与接触窗结构之间的重叠裕度,且可防止因重叠偏差所产生电性缺陷(如,电路桥接)。

7.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

8.图1a至图1i为本发明一实施例的存储器结构的制造流程剖面图;

9.图2a至图2b为本发明另一实施例的存储器结构的制造流程剖面图。

10.附图标号说明:

11.10,20:存储器结构

12.100:基底

13.102:隔离结构

14.104:位线结构

15.106,122,124a,224a:接触窗

16.107,128:阻障层

17.108:导线

18.110,140:介电结构

19.112,114,142,144,146,148,150:介电层

20.116:硬罩幕层

21.118,120:罩幕层

22.124,224:接触窗材料层

23.126:金属硅化物层

24.130,132:间隙壁层

25.130a,132a,230,232:间隙壁

26.134,152,234:开口

27.136:接触窗结构

28.138:蚀刻终止层

29.154,158:电极

30.156:绝缘层

31.160,162:导体层

32.164:电容器结构

33.p1:上部

34.p2:下部

35.s1,s2:顶面

36.s3:第一底面

37.s4:第二底面

38.s5:连接面

39.w1~w7:宽度

具体实施方式

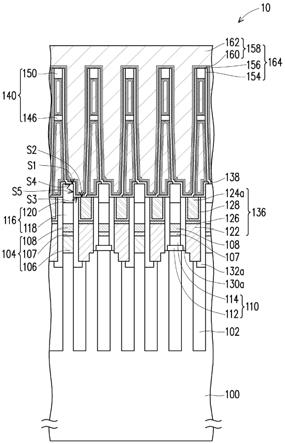

40.图1a至图1i为本发明一实施例的存储器结构的制造流程剖面图。

41.请参照图1a,提供基底100。基底100可为半导体基底,如硅基底。在基底100中可具有隔离结构102。隔离结构102例如是浅沟渠隔离结构(shallow trench isolation,sti)。此外,可根据需求在基底100中形成所需的掺杂区(未示出)。

42.在基底100上形成位线结构104。位线结构104可包括接触窗106与导线108。接触窗106位于基底100上。接触窗106的材料例如是掺杂多晶硅。导线108位于接触窗106上。部分导线108可位于介电结构110上。导线108的材料例如是钨等金属。介电结构110可为单层结构或多层结构。在本实施例中,介电结构110是以包括介电层112与介电层114的多层结构为例,但本发明并不以此为限。介电层112位于隔离结构102上。介电层112的材料例如是氧化硅。介电层114位于介电层112上。介电层114的材料例如是氮化硅。此外,位线结构104还可包括阻障层107。阻障层107位于导线108与接触窗106之间。部分阻障层107可位于导线108

与介电结构110之间。阻障层107的材料例如是钛(ti)、氮化钛(tin)或其组合。

43.另外,可在位线结构104上形成硬罩幕层116。硬罩幕层116可为单层结构或多层结构。在本实施例中,硬罩幕层116是以包括罩幕层118与罩幕层120的多层结构为例,但本发明并不以此为限。罩幕层118位于导线108上。罩幕层118的材料例如是氮化硅。罩幕层120位于罩幕层118上。罩幕层120的材料例如是氮化硅。

44.此外,可在位线结构104一侧的基底100上形成接触窗122。接触窗122的材料例如是掺杂多晶硅。另外,可在接触窗122上形成接触窗材料层124。接触窗材料层124的材料例如是钨等金属。在接触窗122上可形成金属硅化物层126,且金属硅化物层126位于接触窗122与接触窗材料层124之间。金属硅化物层126的材料例如是硅化钴(cosi)或硅化镍(nisi)。再者,可在接触窗材料层124与金属硅化物层126之间形成阻障层128。阻障层128的材料例如是ti、tin或其组合。

45.此外,可在接触窗材料层124的一侧壁上形成间隙壁层130,且可在接触窗材料层124的另一侧壁上形成间隙壁层132。间隙壁层130与间隙壁层132分别可为单层结构或多层结构。举例来说,间隙壁层130与间隙壁层132分别可为氮化硅层、氧化硅层/氮化硅层(no)的复合层或氮化硅层/氧化硅层/氮化硅层(non)的复合层。

46.请参照图1b,可对接触窗材料层124进行蚀刻处理,而形成接触窗124a,且在接触窗124a上方形成开口134,而使得硬罩幕层116的顶面s1可高于接触窗124a的顶面s2。亦即,硬罩幕层116的顶面s1可高于接触窗结构136的顶面s2。开口134可具有宽度w1。对接触窗材料层124所进行的蚀刻处理例如是干式蚀刻处理。此外,可移除开口134所暴露出的部分阻障层128。如此一来,可在位线结构104一侧的基底100上形成接触窗结构136。接触窗结构136可包括接触窗122与接触窗124a。接触窗122位于基底100上。接触窗124a位于接触窗122上。此外,接触窗结构136还可包括金属硅化物层126与阻障层128中的至少一者。金属硅化物层126位于接触窗122与接触窗124a之间。阻障层128位于接触窗124a与金属硅化物层126之间。

47.请参照图1c,在形成所述接触窗124a之后,可通过湿式蚀刻处理移除开口134所暴露出的部分间隙壁层130与部分间隙壁层132,而形成间隙壁130a与间隙壁132a,且扩大开口134的宽度。举例来说,可将开口134的宽度从宽度w1(图1b)扩大成宽度w2(图1c)。

48.请参照图1d,可在开口134的表面上形成蚀刻终止层138。蚀刻终止层138未填满开口134。在一实施例中,蚀刻终止层138可共形地形成在开口134的表面上。蚀刻终止层138的材料例如是氮化硅。蚀刻终止层138的形成方法例如是化学气相沉积法。

49.接着,可形成填入开口134的介电结构140。介电结构140可包括介电层142与位于介电层142上的介电层144。介电层142填入开口134。介电层142可为旋涂式介电材料(spin on dielectrics,sod)。介电层142的材料例如是氧化硅。介电层144的材料例如是氧化硅。介电层144的形成方法例如是化学气相沉积法。此外,介电结构140可包括介电层146、介电层148与介电层150中的至少一者。介电层146、介电层148与介电层150依序位于介电层144上。介电层146与介电层150的材料例如是氮化硅。介电层148的材料例如是氧化硅。

50.请参照图1e,可在介电结构140中形成暴露出部分接触窗124a的开口152。开口152的形成方法例如是通过微影处理与蚀刻处理对介电结构140进行图案化。上述蚀刻处理例如是干式蚀刻处理。此外,可移除部分蚀刻终止层138,而使得开口152暴露出部分接触窗

124a。开口152的底部在介电层142处可具有宽度w3-1,且开口152的底部在蚀刻终止层138处可具有宽度w3-2。另外,在图1c的处理中,可将开口134的宽度扩大为宽度w2,而有利于图1e中的蚀刻处理的进行,亦即有利于形成暴露出部分接触窗124a的开口152。

51.请参照图1f,可移除部分介电结构140与部分蚀刻终止层138,而扩大开口152的底部的宽度。举例来说,可将开口152的底部的宽度从宽度w3-1(图1e)扩大成宽度w4-1(图1f),藉此有助于增加后续形成于开口152中的电容器的电容值。此外,可将开口152的底部的宽度从宽度w3-2(图1e)扩大成宽度w4-2(图1f),藉此有助于增加后续形成于开口152中的电容器与接触窗结构136的接触面积。部分介电结构140与部分蚀刻终止层138的移除方法例如湿式蚀刻处理。上述湿式蚀刻处理对介电层142的蚀刻率可大于上述湿式蚀刻处理对介电层144的蚀刻率。此外,由于介电层142与蚀刻终止层138的材料不同,因此上述湿式蚀刻处理对介电层142的移除量可大于上述湿式蚀刻处理对蚀刻终止层138的移除量。

52.请参照图1g,可共形地在开口152中形成电极154。电极154以错位方式位于接触窗结构136上。电极154包括第一底面s3与第二底面s4。电极154的第一底面s3低于电极154的第二底面s4。电极154的第一底面s3可位于接触窗结构136的顶面s2上,且电极154的第二底面s4可位于硬罩幕层116的顶面s1上。举例来说,电极154的第一底面s3可连接于接触窗结构136的顶面s2,且电极154的第二底面s4可连接于硬罩幕层116的顶面s1。另外,电极154还可包括连接面s5。连接面s5连接于第一底面s3与第二底面s4之间。由电极154的第一底面s3、连接面s5与第二底面s4所形成的形状可为阶梯状。电极154的材料例如是ti、tin或其组合。电极154的形成方法例如是先在开口152表面与介电结构140的顶面上共形地形成电极材料层,再对电极材料层进行图案化。

53.请参照图1h,可移除介电结构140中的介电层142、介电层144与介电层148。介电层142、介电层144与介电层148的移除方法例如是湿式蚀刻法。

54.请参照图1i,可依序在电极154上形成绝缘层156与电极158。绝缘层156的材料可为介电材料,如高介电常数材料(high-k material)。电极158可为单层结构或多层结构。在本实施例中,电极158是以包括导体层160与导体层162的多层结构为例,但本发明并不以此为限。导体层160位于绝缘层156上。导体层160的材料例如是ti、tin或其组合。导体层162位于导体层160上。导体层162的材料例如是经掺杂的硅锗(sige)。

55.如此一来,可在接触窗结构136上形成电容器结构164。电容器结构164包括电极154、电极158与绝缘层156。电极158位于电极154上。绝缘层156位于电极154与电极158之间。

56.以下,通过图1i来说明本实施例的存储器结构10。此外,虽然存储器结构10的形成方法是以上述方法为例进行说明,但本发明并不以此为限。

57.请参照图1i,存储器结构10包括基底100、位线结构104、接触窗结构136与电容器结构164。此外,存储器结构10还可包括硬罩幕层116、蚀刻终止层138、间隙壁130a与间隙壁132a中的至少一者。存储器结构10可为动态随机存取存储器(dynamic random access memory,dram)。位线结构104位于基底100上。接触窗结构136位于位线结构104一侧的基底100上。电容器结构164位于接触窗结构136上。电容器结构164包括电极154、电极158与绝缘层156。电极154包括第一底面s3与第二底面s4。电极154的第一底面s3低于电极154的第二底面s4。电极154的第一底面s3仅位于部分接触窗结构136上。电极154还可包括连接面s5。

连接面s5连接于第一底面s3与第二底面s4之间。由电极154的第一底面s3、连接面s5与第二底面s4所形成的形状可为阶梯状。电极154的第一底面s3可连接于接触窗结构136的顶面s2。电极158位于电极154上。绝缘层156位于电极154与电极158之间。硬罩幕层116位于位线结构104上。硬罩幕层116的顶面s1可高于接触窗结构136的顶面s2。电极154的第二底面s4可连接于硬罩幕层116的顶面s1。蚀刻终止层138位于接触窗结构136上,且暴露出接触窗结构136的部分顶面s2。间隙壁130a位于接触窗结构136的一侧壁上。间隙壁132a位于接触窗结构136的另一侧壁上。

58.存储器结构10中的其余构件可参照上述实施例的说明。此外,存储器结构10中的各构件的材料、设置方式、形成方法与功效已于上述实施例进行详尽地说明,于此不再说明。

59.基于上述实施例可知,在上述存储器结构10及其制造方法中,电极154的第一底面s3低于电极154的第二底面s4。如此一来,即使在电极154与接触窗结构136之间发生重叠偏差,也不容易在相邻两个接触窗结构136之间形成桥接路径。因此,通过电极154的上述结构设计,可有效地提升电极154与接触窗结构之间的重叠裕度,且可防止因重叠偏差所产生电性缺陷(如,电路桥接)。

60.图2a至图2b为本发明另一实施例的存储器结构的制造流程剖面图。

61.请参照图1a与图2a,图1a的结构与图2的结构的差异如下。在图2的结构中,接触窗材料层224的上部p1的宽度w5可大于接触窗材料层224的下部p2的宽度w6。接触窗材料层224的上部p1可位于间隙壁230的顶面与间隙壁232的顶面上。此外,在图1a的结构与图2a的结构中,相同或相似的构件以相同或相似的符号表示,并省略其说明。

62.请参照图2b,可进行相似于图1b至图1i的步骤,而形成存储器结构20。存储器结构20的制造方法与存储器结构10的制造方法的差异如下。存储器结构10的制造方法可包括扩大开口134的宽度的处理,而使得开口134的宽度从宽度w1(图1b)扩大成宽度w2(图1c)。在存储器结构20的制造方法中,通过对接触窗材料层224进行蚀刻处理,而形成接触窗224a,且在接触窗224a上方形成开口234。由于接触窗224a是通过移除接触窗材料层224的部分上部p1所形成,因此接触窗224a可具有上部p1与下部p2,且接触窗224a的上部p1的宽度w5可大于接触窗224a的下部p2的宽度w6。开口234的宽度w7可大于接触窗224a的上部p1的宽度w5。此外,开口234的宽度w7可等于开口134的宽度w2。因此,存储器结构20的制造方法可省略存储器结构10的制造方法中的扩大开口134的宽度的步骤。此外,由于接触窗224a的上部p1的宽度w5可大于接触窗224a的下部p2的宽度w6,因此可增加电极154与接触窗224a的接触面积。

63.存储器结构20的制造方法中的其余步骤可参考图1b至图1i的说明,于此不再说明。另外,在图1i的存储器结构10与图2b的结构存储器结构20中,相同或相似的构件以相同或相似的符号表示,并省略其说明。

64.综上所述,在本发明所提出的存储器结构及其制造方法中,第一电极的第一底面低于第一电极的第二底面。如此一来,即使在第一电极与接触窗结构之间发生重叠偏差,也不容易在相邻两个接触窗结构之间形成桥接路径。因此,通过第一电极的上述结构设计,可有效地提升第一电极与接触窗结构之间的重叠裕度,且可防止因重叠偏差所产生电性缺陷。

65.虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中的技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。