1.本发明涉及一种有源矩阵基板以及具备有源矩阵基板的显示装置。

背景技术:

2.显示装置中所使用的有源矩阵基板包括含有多个像素区域的显示区域和显示区域以外的非显示区域(也称为“边框区域”或“周边区域”。)。像素区域是与显示装置的像素对应的区域。在各像素区域中,作为开关元件配置有薄膜晶体管(thin film transistor:以下,“tft”)。

3.近年来,作为tft的活性层的材料,提出了使用氧化物半导体来代替非晶硅、多晶硅的技术。将这样的tft称为“氧化物半导体tft”。氧化物半导体具有比非晶硅高的迁移率。因此,氧化物半导体tft与非晶硅tft相比能够以更高速动作。此外,氧化物半导体膜能够利用比多晶硅膜简便的工艺形成,因此也能够应用于需要大面积的装置。

4.氧化物半导体tft多数为底栅型tft,但也提出了顶栅型的氧化物半导体tft。例如,专利文献1公开了一种顶栅型tft,其隔着栅极绝缘层在氧化物半导体层的一部分上配置有栅极。

5.在有源矩阵基板的非显示区域中,存在单片(一体的)形成栅极驱动器等驱动电路的情况。通过单片形成驱动电路,从而实现非显示区域的狭小化、基于安装工序简化的成本降低。例如,有时在非显示区域中,栅极驱动器电路形成为单片,源极驱动器电路以cog(chip on glass)方式安装。

6.在智能手机等窄边框化要求较高的设备中,在提出了栅极驱动器的基础上,还提出了单片形成源切换(source shared driving:ssd)电路等多路分配器电路的方案(例如专利文献1)。ssd电路是将显示信号从来自源极驱动器的各端子的视频信号线一条分配至多条源极总线的电路。通过搭载ssd电路,能够进一步缩小非显示区域中的配置有端子部的区域(端子部形成区域)。此外,由于来自源极驱动器的输出数量减少,能够减小电路规模,因此能够降低驱动器ic的成本。

7.驱动电路、ssd电路等周边电路包含tft。在本说明书中,将作为开关元件配置于显示区域的各像素的tft称为“像素tft”,将构成周边电路的tft称为“电路tft”。此外,将电路tft中的在ssd电路中作为开关元件使用的tft称为“ssd电路用tft”,将栅极驱动器电路中所使用的tft称为“栅极驱动器电路用tft”。在使用氧化物半导体tft作为像素tft的有源矩阵基板中,从制造工艺的观点出发,作为电路tft,期望形成使用了与像素tft相同的氧化物半导体膜的氧化物半导体tft。现有技术文献专利文献

8.专利文献1:国际公开第2017/085591号

技术实现要素:

本发明所要解决的技术问题

9.本发明人研究后,在有源矩阵基板上形成的一部分的tft中,由于有源矩阵基板的驱动,其阈值电压有可能向正方向偏移(plus shift,正向偏移)。其结果是,得不到所期望的tft特性,有源矩阵基板的可靠性有可能降低。例如,在ssd电路用tft或者一部分栅极驱动器电路用tft中,阈值电压的平移容易变大。详情将后述。

10.本发明的一个实施方式提供一种有源矩阵基板,具备能够抑制阈值电压的正向偏移的氧化物半导体tft。用于解决技术问题的技术方案

11.本说明书公开了如下项目所记载的有源矩阵基板以及显示装置。

12.[项目1]一种有源矩阵基板,其具有:显示区域,其包括多个像素区域;以及非显示区域,其位于显示区域的周边,且包含形成有周边电路的周边电路形成区域,所述有源矩阵基板具备:基板;由所述基板支承的多条源极总线以及多条栅极总线;多个氧化物半导体tft,其由所述基板支承,并包括多个像素tft以及构成所述周边电路的多个像素tft,所述多个像素分别与所述多个像素区域中的一个对应设置,所述多个氧化物半导体tft的每一个氧化物半导体具有氧化物半导体层及栅极,所述氧化物半导体层包含沟道区域,所述栅极隔着栅极绝缘层配置于所述氧化物半导体层的所述沟道区域上,所述多个氧化物半导体tft包括多个第一tft以及多个第二tft和/或多个第三tft,所述多个第一tft的每一个第一tft具有第一遮光结构,其以从所述基板的法线方向观察时与所述沟道区域的整体重叠的方式配置于所述氧化物半导体层与所述基板之间,所述多个第二tft的每一个第二tft具有第二遮光结构,其在所述氧化物半导体层与所述基板之间未配置遮光层,所述多个第三tft的每一个第三tft具有第三遮光结构,其以从所述基板的法线方向观察时仅与所述沟道区域的一部分重叠的方式配置于所述氧化物半导体层与所述基板之间,所述多个第一tft包括所述多个像素tft,所述多个第二tft和/或所述多个第三tft包括所述多个电路tft的至少一部分。

[0013]

[项目2]根据项目1所述的有源矩阵基板,所述周边电路包括ssd电路,其向所述多条源极总线中的n条源极总线分配显示信号,所述多个第二tft和/或所述多个第三tft包含多个ssd电路用tft,其构成所述ssd电路。

[0014]

[项目3]

根据项目1或2所述的有源矩阵基板,所述周边电路还具备栅极驱动器,其与所述多条栅极总线连接,所述多个第二tft和/或所述多个第三tft包含多个栅极驱动器用tft,其构成所述栅极驱动器。

[0015]

[项目4]根据项目1~3中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第二tft和所述多个第三tft两者。

[0016]

[项目5]根据项目4所述的有源矩阵基板,所述周边电路包括ssd电路以及栅极驱动器,所述ssd电路向所述多条源极总线中的n条源极总线分配显示信号,所述栅极驱动器与所述多条栅极总线连接,所述多个第二tft包括多个ssd电路用tft,其构成所述ssd电路,所述多个第三tft包含多个栅极驱动器用tft,其构成所述栅极驱动器。

[0017]

[项目6]根据项目1~5中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第三tft,从所述基板的法线方向观察时,所述各第三tft的所述沟道区域具有遮光部和光入射部,所述遮光部与所述第二遮光层重叠,所述光入射部与所述第二遮光层不重叠,所述遮光部相对于所述沟道区域的面积比例ar为25%以上且75%以下。

[0018]

[项目7]根据项目1~6中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第三tft,从所述基板的法线方向观察时,所述各第三tft的所述沟道区域具有遮光部和光入射部,所述遮光部与所述第二遮光层重叠,所述光入射部与所述第二遮光层不重叠,所述多个第三tft包括多个tft,所述多个tft中从所述基板的法线方向观察时的所述遮光部相对于所述沟道区域的面积比例ar相互不同。

[0019]

[项目8]根据项目1~7中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第三tft,从所述基板的法线方向观察时,在所述多个第三tft的至少一部分的tft中,所述沟道区域具有遮光部和光入射部,所述遮光部与所述第二遮光层重叠,所述光入射部与所述第二遮光层不重叠,所述遮光部和所述光入射部在沟道长度方向上排列。

[0020]

[项目9]根据项目1~8中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第三tft,从所述基板的法线方向观察时,在所述多个第三tft的至少一部分的tft中,所述沟道区域具有遮光部和光入射部,所述遮光部与所述第二遮光层重叠,所述光入射部与所述第二遮光层不重叠,所述遮光部和所述光入射部在沟道宽度方向上排列。

[0021]

[项目10]

根据项目1~9中任一项所述的有源矩阵基板,所述多个氧化物半导体tft包括所述多个第三tft,从所述基板的法线方向观察时,在所述多个第三tft的至少一部分的tft中,所述沟道区域具有遮光部和光入射部,所述遮光部与所述第二遮光层重叠,所述光入射部与所述第二遮光层不重叠,所述光入射部位于所述遮光部的内部。

[0022]

[项目11]根据项目1~10中任一项所述的有源矩阵基板,所述氧化物半导体层包含in

‑

ga

‑

zn

‑

o系半导体。

[0023]

[项目12]根据项目11所述的有源矩阵基板,所述in

‑

ga

‑

zn

‑

o系半导体包含结晶质部分。

[0024]

[项目13]一种显示装置,其包括:显示面板;背光源,其配置在所述显示面板的背面侧;以及边框,其保持所述显示面板和所述背光源,所述显示装置的特征在于,所述显示面板包括:项目1~12中任一项所述的有源矩阵基板;相对基板,其以与所述有源矩阵基板相对的方式配置;液晶层,其设置于所述有源矩阵基板与所述相对基板之间,所述边框具有面板支承部,其位于所述显示面板和所述背光源之间,且支承所述显示面板的周缘部,所述面板支承部包括:遮光区域,其遮挡来自所述背光源的光;以及开口区域,其使来自所述背光源的光的一部分透射或通过,在从所述基板的法线方向观察时,所述开口区域与所述周边电路形成区域的至少一部分重叠。有益效果

[0025]

根据本发明的一个实施方式,提供一种具备能够抑制阈值电压的正向偏移的氧化物半导体tft的有源矩阵基板。

附图说明

[0026]

图1是表示有源矩阵基板1001的平面结构的一个例子的示意图。图2a是例示有源矩阵基板1001中的第一tft的俯视图。图2b是例示有源矩阵基板1001中的第二tft的截面图。图3a是表示具有第一遮光结构的样本tft1中的电流电压特性的测定结果的图。图3b是表示具有第二遮光结构的样本tft2中的电流电压特性的测定结果的图。图4a为表示样本tft1中的压力施加时间与阈值电压的偏移量δvth的关系的图。图4b为表示样本tft2中的压力施加时间与阈值电压的偏移量δvth的关系的图。图5是用于说明ssd电路sc的构成以及动作的图。图6是例示ssd电路sc的时序图的图。

图7是表示偏移寄存器中所包含的双稳态电路srk的构成(偏移寄存器的第k级的构成)的电路图。图8是偏移寄存器的各双稳态电路的时序图。图9a是例示有源矩阵基板1001中的第三tft300的示意性俯视图。图9b是第三tft300的截面图,表示沿着图9a中的ixb

‑

ixb’线的截面。图10a是例示变形例1的第三tft300a的示意性俯视图。图10b是变形例1的第三tft300a的截面图,表示沿着图10a中的xb

‑

xb’线的截面。图11a是例示变形例2的第三tft300b的示意性俯视图。图11b是变形例2的第三tft300b的截面图,表示沿着图11中的xib

‑

xib’线的截面。图12a是例示显示装置2000的概略图。图12b是显示装置2000的一部分的放大截面图,表示沿着图12a所示的xiib

‑

xiib’线的截面。图13是表示用于说明有源矩阵基板1001的制造方法的一个例子的工艺流程的图。图14是表示第一tft的其他例子的截面图。

具体实施方式

[0027]

如上所述,在有源矩阵基板的驱动中,在一部分电路tft中,产生阈值电压的正向偏移,存在无法得到期望的特性的问题。

[0028]

本发明人经研究后发现,上述问题在有源矩阵基板动作时,在以高占空比(duty)比向栅极施加规定的控制信号的tft上显著。在这些tft中,导通状态的期间相对于1周期(例如1水平扫描期间)的比大。因此,认为随着有源矩阵基板的动作,容易进行阈值电压的正向偏移,偏移量增大。其结果,tft的动作余量变小,根据情况,存在不能正常地动作的可能性。

[0029]

例如在有源矩阵基板的驱动时,由于以高占空比(例如约33%或约50%)向ssd电路用tft的栅极施加控制信号,因此阈值电压的正向偏移容易变大。此外,在栅极驱动器电路用tft的一部分(例如输出晶体管)中也可能产生比较大的正向偏移。

[0030]

另一方面,在氧化物半导体tft中,通过光(例如背光)入射到氧化物半导体层,氧化物半导体中的氧缺陷增加,存在阈值电压向负方向偏移(负向偏移)这样的问题。若产生阈值电压的负向偏移,则有可能截止漏电流增大或者产生深度化(正常导通状态)。相对于此,为了抑制背光源光所引起的tft特性的劣化(光劣化),已知有在顶栅型的氧化物半导体tft中,在氧化物半导体层的基板侧设置遮光层的结构。另外,在底栅型的氧化物半导体tft中,设置于氧化物半导体层的基板侧的栅极也作为遮光层发挥功能,因此也可以不另外设置遮光层。

[0031]

本发明人基于上述见解进行了研究,结果发现,在顶栅型的氧化物半导体tft中,通过利用由光劣化引起的特性变化,能够抑制阈值电压的正向偏移,想到了本技术发明。即,在本发明的实施方式的有源矩阵基板中,使规定量的光有意地入射到一部分的氧化物半导体tft中的氧化物半导体层而产生光劣化。由此,能够将伴随有源矩阵基板的动作而产生的阈值电压的向正方向的偏移量的一部分或全部以由光劣化引起的阈值电压的向负方向的偏移量抵消,因此能够抑制阈值电压的正向偏移。

[0032]

(第一实施方式)以下,参照附图说明第一实施方式的有源矩阵基板。

[0033]

图1是示意性地表示有源矩阵基板1001的平面结构的一个例子的图。有源矩阵基板1001具有对显示作贡献的显示区域dr和位于显示区域dr的外侧的周边区域(边框区域)fr。显示区域dr包括排列成矩阵状的多个像素区域pix。像素区域pix(有时也简称为“像素”)是与显示装置的像素对应的区域。非显示区域fr是位于显示区域dr的周边,对显示不作贡献的区域。

[0034]

有源矩阵基板1001在显示区域dr中具备基板1、由基板1支承的多个像素tft20、多个像素电极pe、向像素tft20供给栅极信号的多条栅极总线gl1~glx(x为2以上的整数,以下统称为“栅极总线gl”)、以及向像素tft20供给源极信号的多条源极总线sl1~sly(y为2以上的整数,以下统称为“源极总线sl”)。各像素区域pix例如由栅极总线gl以及源极总线sl规定。源极总线sl在与栅极总线gl交叉的方向上延伸。

[0035]

各像素tft20和各像素电极pe与多个像素区域pix的一个对应地设置。像素tft20的栅极与栅极总线gl之一电连接,源极与源极总线sl之一电连接。漏极与像素电极pe电连接。

[0036]

在将有源矩阵基板1001应用于ffs(fringe field switching:边缘场开关)模式等横向电场模式的显示装置的情况下,在有源矩阵基板1001中,多个像素pix设置有共用的电极(共用电极)ce。

[0037]

非显示区域fr可以设置驱动器等的周边电路。例如,也可以单片形成驱动栅极总线gl的栅极驱动器gd和以时间分割的方式驱动源极总线sl的ssd电路sc等。ssd电路sc与例如以cog(chip on glass)方式安装的源极驱动器sd连接。

[0038]

ssd电路sc配置在源极驱动器sd与显示区域dr之间。源极驱动器sd包括多个输出端子(未图示)。在位于源极驱动器sd与ssd电路sc之间的区域设置有多条信号输出线(视频信号线)vl1~vlz(z为2以上的整数,以下统称为“信号输出线vl”)。ssd电路sc将从1根信号输出线vl供给的显示信号分配为两条以上的源极总线sl。由此,能够削减源极驱动器sd的输出端子(输出引脚)的数量,因此能够降低非显示区域fr的面积(窄边框化)。

[0039]

<氧化物半导体tft的结构>有源矩阵基板1001具有多个氧化物半导体tft。多个氧化物半导体tft均是以氧化物半导体层为活性层的顶栅型的氧化物半导体tft。这些氧化物半导体tft包括多个像素tft20和构成ssd电路、栅极驱动器电路等周边电路的多个电路tft。本实施方式中的多个氧化物半导体tft还包括多个第一tft和多个第二tft。第一tft具有第一遮光结构,该第一遮光结构在氧化物半导体层的基板1侧具有遮光层。遮光层配置成在从基板1的法线方向观察时与氧化物半导体层的沟道区域整体重叠。另一方面,第二tft具有第二遮光结构,该第二遮光结构在氧化物半导体层的基板1侧未设置遮光层。在第二tft中,光(例如背光)容易从基板1侧入射到氧化物半导体层。

[0040]

第一tft包括像素tft。像素tft要求截止漏电流小。这是因为,当截止漏电流大时,写入到像素电极的电位的保持特性劣化,有可能引起亮度不均、闪烁这样的显示不良。通过像素tft具有第一遮光结构,能够抑制因光劣化引起的阈值电压的负向偏移,因此能够抑制截止漏电流的增大。另外,第一tft可以还包含一部分电路tft。第二tft包含多个电路tft中

的至少一部分电路tft。第二tft也可以包含例如ssd电路用tft。由于以比较高的占空比向ssd电路用tft施加控制信号,因此阈值电压的正方向的偏移量容易变大。通过将第二遮光结构应用于这种tft,能够利用由光劣化引起的阈值电压的负向偏移,降低阈值电压的正方向的偏移量。第二tft在ssd电路用tft的基础上,也可以包含栅极驱动器电路用tft,或者包含栅极驱动器电路用tft来代替该ssd电路用tft。

[0041]

以下,参照附图,以第一tft是像素tft,第二tft是电路tft的情况为例,具体说明各tft的结构。此处,以应用于ffs模式的显示装置的有源矩阵基板为例进行说明。ffs模式是横向电场方式的模式,在该横向电场方式的模式中,在一个基板上设置一对电极,对液晶分子在与基板面平行的方向(横向)施加电场。另外,本实施方式的有源矩阵基板也可以应用于在液晶层的厚度方向施加电压的纵向电场方式的模式(例如tn模式、垂直取向模式)的显示装置。

[0042]

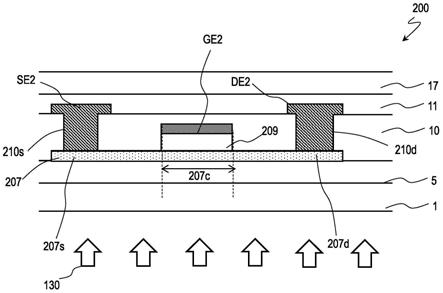

图2a及图2b是分别例示第一tft100及第二tft200的示意性截面图。

[0043]

第一tft100和第二tft200由基板1支承。此处,第一tft100是配置于显示区域dr中的各像素区域pix的像素tft。第二tft200是构成配置于非显示区域fr的周边电路的电路tft。

[0044]

第一tft100具有:配置于基板1的遮光层103、隔着下部绝缘层5配置于遮光层103上的氧化物半导体层107、配置于氧化物半导体层107上的栅极绝缘层109、配置于栅极绝缘层109上的栅极ge1、以及源极se1和漏极de1。

[0045]

氧化物半导体层107从基板1的主面的法线方向观察时,具有与栅极ge1重叠的沟道区域107c、和分别位于沟道区域107c的两侧的第一区域和第二区域。第一区域的一部分(源极接触区域)107s经由源极se1与对应的源极总线sl电连接。第二区域的一部分(漏极接触区域)107d经由漏极de与像素电极pe电连接。第一区域和第二区域是与沟道区域7c相比电阻率低的低电阻区域。第一区域以及第二区域也可以是导电体区域。

[0046]

遮光层103被配置为在从基板1的法线方向观察时,与tft100的沟道区域107c的整体重叠。由此,能更有效地抑制由来自基板1侧的光(背光)130引起的氧化物半导体层7的特性劣化。另外,遮光层103也可以配置成在从基板1的法线方向观察时,与整个氧化物半导体层107或者氧化物半导体层107中的位于源极接触区域107s与漏极接触区域107d之间的部分整体重叠。

[0047]

遮光层103也可以作为tft100的下部电极而发挥功能。例如,遮光层103也可以与栅极ge1(或对应的栅极总线gl)电连接。或者,遮光层103也可以固定于固定电位(例如源极电位)。

[0048]

栅极绝缘层109例如以覆盖氧化物半导体层107的一部分(此处为沟道区域107c)且不覆盖第一区域和第二区域的方式配置。栅极绝缘层109也可以仅位于氧化物半导体层107与栅极ge1之间。从基板1的法线方向观察时,栅极绝缘层109的周缘(在栅极绝缘层109具有锥形形状的情况下,栅极绝缘层109的上表面的周缘)也可以与栅极ge1的周缘匹配。这样的结构通过使用用于栅极ge1的图案化的掩模、或者以栅极ge1为掩模进行栅极绝缘层109的图案化而得到。

[0049]

栅极ge1被配置成在从基板1的法线方向观察时,与氧化物半导体层107的沟道区域107c重叠。栅极ge1例如使用与栅极总线gl相同的导电膜(栅极用导电膜)来形成。在本说

明书中,将包括使用栅极用导电膜形成的电极/布线的层称为“栅极金属层”。栅极ge1也可以与栅极总线gl一体形成(也可以相连)。例如,栅极ge1也可以是栅极总线gl的一部分。在该情况下,有时将栅极总线gl中的从基板1的法线方向观察时与氧化物半导体层107重叠的部分称为“栅极ge1”。

[0050]

氧化物半导体层107、栅极绝缘层109以及栅极ge1被层间绝缘层10覆盖。作为层间绝缘层10,也可以使用能够还原氧化物半导体的还原性的绝缘膜(例如氮化硅膜)。由此,能够抑制氧化物半导体层107中的与层间绝缘层10相接的部分(第一区域和第二区域)的电阻率的上升。在层间绝缘层10上形成有露出第一区域的源极接触区域107s的源极用开口部110s和露出第二区域的漏极接触区域107d的漏极用开口部110d。

[0051]

源极se1形成在层间绝缘层10之上和源极用开口部110s内,在源极用开口部110s内与氧化物半导体层7的源极接触区域107s连接。漏极de1形成在层间绝缘层10之上和漏极用开口部110d内,在漏极用开口部110d内与氧化物半导体层107的漏极接触区域107d连接。源极se1和漏极de1也可以使用与源极总线sl相同的导电膜形成。在本说明书中,将包含使用源极用导电膜形成的电极/布线的层称为“源极金属层”。源极se1也可以与源极总线sl一体地形成(也可以相连)。例如,源极se1也可以是源极总线sl的一部分。在该情况下,有时将源极总线sl1中的与氧化物半导体层107连接的部分称为“源极se1”。

[0052]

第一tft100为像素tft时,第一tft100的漏极de1与像素电极pe电连接。

[0053]

以覆盖第一tft100的方式形成有上部绝缘层13。上部绝缘层13例如包含无机绝缘层(钝化膜)11。如图所示,上部绝缘层13也可以具有包含无机绝缘层11和形成在无机绝缘层11上的有机绝缘层12的层叠结构。也可以不形成有机绝缘层12。或者,有机绝缘层12也可以仅形成于显示区域。

[0054]

在上部绝缘层13上形成有共用电极ce。共用电极ce也可以不按像素区域pix分离。例如,共用电极ce也可以在连接像素电极pe和漏极de的像素接触区域(形成有像素接触孔chp的区域)具有开口部,除了像素接触区域以外遍及像素区域pix整体而形成。

[0055]

像素电极pe隔着电介质层17配置在共用电极ce上。像素电极pe按每个像素区域pix分离。在各像素区域pix中,在像素电极pe上设置有一个或多个狭缝(开口部)或切口部。

[0056]

像素电极pe配置在电介质层17上,在形成于上部绝缘层13及电介质层17的像素接触孔chp内与漏极de1连接。像素接触孔chp由无机绝缘层11的开口部11p、有机绝缘层12的开口部12p和电介质层17的开口部17p构成。从基板1的法线方向观察时,开口部17p与开口部12p至少部分重叠。

[0057]

开口部11p和开口部17p也可以通过以电介质层17上的抗蚀剂掩模和有机绝缘层12为掩模,将电介质层17和无机绝缘层11一并蚀刻而形成。在该情况下,在像素接触孔chp内,开口部11p的侧面能与开口部17p或开口部12p匹配。

[0058]

另外,在图示的例子中,共用电极ce上隔着电介质层17形成有像素电极pe,但像素电极pe上也可以隔着电介质层17形成有共用电极ce。在该情况下,在各像素区域pix,在共用电极ce设置有狭缝或切口部。

[0059]

此外,第一tft100也可以不包含漏极。在该情况下,像素电极pe也可以直接连接于氧化物半导体层107的漏极接触区域107d。

[0060]

进一步地,如图14所例示的那样,源极总线sl和氧化物半导体tft的源极se也可以

使用与遮光层103相同的导电膜形成。这样,将在比栅极金属层和氧化物半导体层107更靠基板1侧配置有源极总线sl的基板结构称为“下部源极结构”。第二tft200除了在氧化物半导体层207的基板1侧没有遮光层这一点以外,也可以具有与第一tft100同样的结构。第二tft200具有配置在下部绝缘层5之上的氧化物半导体层207、配置在氧化物半导体层207之上的栅极绝缘层209、配置在栅极绝缘层209之上的栅极ge2、以及源极se2和漏极de2。氧化物半导体层207具有在从基板1的法线方向观察时与栅极ge2重叠的沟道区域207c和位于其两侧的第一区域和第二区域。源极se2在层间绝缘层10所形成的源极用开口部210s内与氧化物半导体层207的第一区域的一部分(源极接触区域)207s连接。漏极de2在层间绝缘层10所形成的漏极用开口部210d内与氧化物半导体层207的第二区域的一部分(漏极接触区域)207d连接。第二tft200的源极se2、漏极de2以及栅极ge2分别与构成电路的规定的布线电连接。在氧化物半导体层207的基板1侧,未设置有遮挡从基板1的下方朝向沟道区域207c行进的光的结构。

[0061]

第二tft200为电路tft时,第二tft200设置于非显示区域中的周边电路形成区域。第二tft200的上方也可以不形成有机绝缘层12。在该例中,第二tft200被无机绝缘层11及电介质层17覆盖。

[0062]

<效果>本实施方式的有源矩阵基板1001包括具有第一遮光结构的第一tft100和具有第二遮光结构的第二tft200。在具有第一遮光结构的第一tft100中,由于能够抑制光130入射到氧化物半导体层107的沟道区域107c,因此能够抑制因光劣化引起的阈值电压的负向偏移。其结果,能维持高的截止特性。另一方面,在第二tft200中,通过使背光源光130入射到氧化物半导体层207的沟道区域207c,故意地产生由光劣化引起的阈值电压的负向偏移。由此,能够抵消阈值电压的正方向的偏移量,因此能够将阈值电压的变化

△

vth抑制得较小。

[0063]

第一tft100可以包括要求高截止特性的像素tft,第二tft200也可以包括阈值电压的正向偏移大的电路tft(例如ssd电路用tft)。这样,通过根据用途分开制作形成于有源矩阵基板1001的各tft的结构,能够提高可靠性。

[0064]

如上所述,以往存在如下问题:在一部分电路tft中,随着有源矩阵基板的驱动,阈值电压向正方向的偏移量变大。与此相对地,根据本实施方式,通过在这样的电路tft中应用第二遮光结构,能够抑制阈值电压的正向偏移。

[0065]

<tft特性的评价>制作具有第一遮光结构的样本tft1和具有第二遮光结构的样本tft2,研究栅极电压(vg)的施加时间与tft特性的关系。

[0066]

样本tft1和样本tft2分别具有图2a和图2b所示的结构。这些样本tft除了遮光层的有无以外具有相同的结构。此处,在从背面对各样本tft照射背光源光(光度:4500cd)的状态下,对各tft施加 30v的栅极电压vg。测定温度为60℃、vg压力施加时间为0~3600秒,测定了各样本tft的电流电压特性。

[0067]

图3a及图3b是分别表示样本tft1及样本tft2中的电流电压特性的测定结果的图。横轴表示栅极电压vg,纵轴表示漏极电流id。此外,图4a以及图4b分别是表示样本tft1以及样本tft2中的压力施加时间与阈值电压的偏移量

△

vth的关系的图。

[0068]

根据这些结果可知,在具有遮光层的样本tft1中,与不具有遮光层的样本tft2相

比,阈值电压的正方向的偏移量δvth更大。例如,在vg压力施加时间3600秒时,样本tft1的偏移量δvth为 2.5v左右,与此相对地,样本tft2的tft的偏移量δvth为 1.9v左右。这是因为,在样本tft2中,背光源光入射到氧化物半导体层,由此产生光劣化,阈值电压vth向负方向侧偏移,其结果是,正方向的偏移量降低。

[0069]

<ssd电路>接下来,参照附图说明ssd电路的构成的一个例子。

[0070]

图5是用于说明本实施方式的有源矩阵基板1001中的ssd电路sc的构成以及动作的图。

[0071]

ssd电路sc配置在源极驱动器sd与显示区域dr之间。ssd电路sc包括被基板1支承的多个单位电路u。多个单位电路u的每一个从一条信号输出线vl向n条(n为2以上的整数)源极总线sl分配显示信号。图5表示了n=2的情况下,即各单位电路u从一条信号输出线vl向两条源极总线sl分配显示信号的情况。ssd电路具有多个单位电路,但在图5中,为了简单,仅表示4个单位电路(设为第一单位电路u1~第四单位电路u4)。

[0072]

各单位电路u包括n根(此处为两条)分支布线bl、和n个(此处为两个)ssd电路用的tft(在第一单位电路u1中是tft30a、30c)。两条分支布线bl与1根信号输出线vl连接。此外,两个tft分别与两条分支布线bl连接。这些tft单独地(独立)导通/断开控制两条分支布线bl与两条源极总线sl的电连接。在本实施方式中,tft分别是顶栅型的氧化物半导体tft,具有图2b所例示的第二遮光结构。

[0073]

以下,以第一单位电路u1及第二单位电路u2为例,对各单位电路u的构成进行更具体的说明。

[0074]

第一单位电路u1从信号输出线vl1向源极总线sl1和sl3分配显示信号s(1),第二单位电路u2从信号输出线vl2向源极总线sl2和sl4分配显示信号s(2)。

[0075]

第一单位电路u1中的一个tft30a对分支布线bl1和源极总线sl1的电连接进行导通/断开控制,另一个tft30c对分支布线bl3和源极总线sl3的电连接进行导通/断开控制。tft30a的源极以及漏极分别连接于分支布线bl1以及源极总线sl1,tft30c的源极以及漏极分别连接于分支布线bl3以及源极总线sl3。

[0076]

第二单位电路u2中的一个tft30b对分支布线bl2和源极总线sl2的电连接进行导通/断开控制,另一个tft30d对分支布线bl4和源极总线sl4的电连接进行导通/断开控制。tft30b的源极以及漏极分别连接于分支布线bl2以及源极总线sl2,tft30d的源极以及漏极分别连接于分支布线bl4以及源极总线sl4。

[0077]

ssd电路sc还具有n条(此处为两条)控制信号干线cl1、cl2。

[0078]

在第一单位电路u1中,从控制信号干线(第一控制信号干线)cl1向tft30a的栅极供给选择信号(ssd控制信号)asw1,从控制信号干线(第二控制信号干线)cl2向tft30c的栅极供给选择信号(ssd控制信号)bsw1。在第二单位电路u2中,从第一控制信号干线cl1向tft30b的栅极供给选择信号asw2,从第二控制信号干线cl2向tft30d的栅极供给选择信号bsw2。这些选择信号规定同一组内的选择开关的导通期间,与来自源极驱动器sd的时序性的信号输出同步。各单位电路u将对信号输出线vl的输出进行时间分割而得到的数据电位,按时序性地写入对应的两条源极总线sl(时间分割驱动)。

[0079]

图6是表示ssd电路sc的动作的时序图。如图所示,在最初的水平扫描期间1h中,选

择最上方的栅极总线gl1。在该水平扫描期间1h中,依次导通选择信号asw1、bsw1,依次选择第一单位电路u1中的两个tft30a、30c,从而依次向信号输出线vl1输出与位于栅极总线gl1与源极总线sl1、sl3的交叉部的两像素对应的量的数据电位。同样地,向信号输出线vl2依次输出与位于栅极总线gl1与源极总线sl2、sl4的交叉部的两像素对应的量的数据电位。其它信号布线也是同样的。另外,选择信号asw1~asw4由共用的第一控制信号干线cl1供给,选择信号bsw1~bsw4由共用的第二控制信号干线cl2供给。

[0080]

各单位电路u中的两个tft30的栅极分别与第一控制信号干线cl1以及第二控制信号干线cl2连接,因此,以约50%的高占空比施加规定的电压。因此,这些tft30易于伴随动作而产生阈值电压向正方向偏移的特性偏移。但是,在本实施方式中,各tft30具有从基板1侧向氧化物半导体层入射光的结构(第二遮光结构)。因此,在有源矩阵基板动作时,在各tft30的氧化物半导体层,背光源光从基板1侧入射,可能产生由光引起的阈值电压的负向偏移。其结果是,由于tft30的阈值电压向正方向的偏移量的一部分或全部被抵消,因此能够抑制tft特性的变化。

[0081]

另外,本实施方式的ssd电路不限于上述例示的构成,可以具有各种构成。例如,各单位电路u也可以配置于与r、g、b像素对应的三个源极总线sl(即,n=3)。在该情况下,对各单位电路u中的三个tft30的栅极分别以约33%的高占空比施加规定的电压。因此,容易产生阈值电压的正向偏移,但与上述例子同样地,通过故意地使光入射到tft30的氧化物半导体层,能降低阈值电压的偏移量。

[0082]

在本说明书中,关于使用了ssd电路sc的显示装置的动作、时间分割驱动的时序图等,为了参考,援引日本特开2008

‑

225036号公报、日本特开2006

‑

119404号和国际公开2011/118079号公报的全部公开内容。

[0083]

<栅极驱动器的构成>对在有源矩阵基板1001中单片形成的栅极驱动器gd的构成的一个例子进行说明。

[0084]

栅极驱动器gd由多个级构成的偏移寄存器构成。偏移寄存器的各级以与显示区域中的对应的一个像素行(双栅极驱动的情况下是多个像素行)对应的方式设置。移位寄存器的各级是在各时刻成为两个状态中的任意一个状态并输出表示该状态的信号(以下称为“状态信号”。)的双稳态电路。从移位寄存器的各级输出的状态信号作为扫描信号被提供到对应的栅极总线。

[0085]

在该例中,在各双稳态电路中设置有输入端子及输出端子,该输入端子用于接收第一时钟cka、第四时钟ckd、清零信号clr、基准电位vs、置位信号s以及复位信号r,该输出端子用于输出状态信号q。进一步地,从两级前的级输出的状态信号q作为置位信号s被提供,从三级后的级输出的状态信号q作为复位信号r被提供。即,着眼于k级,提供给第(k

‑

2)行的栅极总线的扫描信号gout(k

‑

2)作为置位信号s被提供,提供给第(k 3)行的栅极总线的扫描信号gout(k 3)作为复位信号r被提供。另外,向偏移寄存器的第一级和第二级的双稳态电路提供栅极开始脉冲信号gsp作为置位信号s。此外,向偏移寄存器的最后的三级的双稳态电路提供清除信号clr作为复位信号r。另外,双稳态电路中第一级和最后的三级是虚拟电路,从第二级到第(1 x)级的电路(k=2~1 x)分别与栅极总线gl1~glx连接。

[0086]

在如上的构成中,若对偏移寄存器的第一级提供作为置位信号s的栅极开始脉冲信号gsp的脉冲,则基于各时钟信号,栅极开始脉冲信号gsp所包含的脉冲(该脉冲包含于从

各级输出的状态信号q)从第一级依次传送到最后级。然后,根据该脉冲的传送,从各级输出的状态信号q依次成为高电平。而且,从这些各级输出的状态信号q作为扫描信号gout(k)提供给各栅极总线gl。

[0087]

图7是表示偏移寄存器所包含的双稳态电路srk的构成(偏移寄存器的第k级的构成)的电路图。如图所示,双稳态电路srk具备多个(此处为十二个)tft和一个电容器c1。多个tft具有向栅极输入清零信号clr的晶体管m2、m3、m12(也称为清零晶体管)、输出输出信号gout(k)的晶体管m10(也称为输出晶体管)、向栅极以及漏极输入置位信号(gout(k

‑

2)、k=1、k=2的情况下的gsp)(即,成为二极管连接)的晶体管m1、源极或者漏极与输出晶体管m10的栅极电连接的晶体管m8(也称为下拉晶体管)。将与晶体管m10的栅极连接的节点称为neta,将与晶体管m8的栅极连接的节点称为netb。晶体管m1的源极与neta连接。双稳态电路srk还具有漏极与netb连接的晶体管m3、m6、m6 。

[0088]

图8是偏移寄存器的各双稳态电路的时序图。当为时刻t1时,对晶体管m1提供gout(k

‑

2)的脉冲作为置位信号。由此,neta的电位从低电平变化为高电平。此外,由于晶体管m6 成为导通状态,netb的电位成为低电平。

[0089]

若为时刻t2,则第一时钟cka从低电平变化为高电平。由此,neta的电位上升。由此,扫描信号gout(k)的电位上升至第一时钟cka的高电平的电位,与该双稳态电路的输出端子连接的栅极总线成为选择状态。由于neta的电位上升,晶体管m6成为导通状态,因此netb的电位成为低电平。

[0090]

若为时刻t3,则扫描信号gout(k)的电位为低电平。关于neta的电位,虽然与t2~t3的期间相比下降,但是维持为高电平的状态。当在时刻t4向晶体管m9的栅极提供复位信号(gout(k 3))的脉冲时,neta的电位成为低电平。

[0091]

在所述多个晶体管中,特别要求抑制输出晶体管m10的特性偏移。因此,在本实施方式中,至少输出晶体管m10也可以具有第二遮光结构。另一方面,关于漏极与netb连接的晶体管m3、m6、m6 ,由于难以产生正向偏移,因此,也可以具有第一遮光结构。

[0092]

本实施方式的栅极驱动器的构成并不限定于图示的例子。本实施方式能够应用于公知的各种栅极驱动器。关于栅极驱动器的构成以及动作,为了参考而引用日本特开2019

‑

138923号公报以及日本特开2010

‑

192109号公报的全部公开内容。

[0093]

<第三tft>本实施方式的有源矩阵基板也可以在具备第二tft的基础上,还可以具备具有第三遮光结构的第三tft,或者,具备具有第三遮光结构的第三tft来代替第二tft。

[0094]

图9a及图9b分别是例示第三tft300的示意性的俯视图及截面图。图9b表示沿着图9a的ixb—ixb’线的截面。将第三tft300的沟道长度方向设为dl,将沟道宽度方向设为dw。

[0095]

第三tft300与图2a所示的第一tft100同样地,具有遮光层303。但是,遮光层303在从基板1的法线方向观察时,以仅与氧化物半导体层307的沟道区域307c的一部分重叠的方式配置,这一点与第一tft100不同。将这样的结构称为“第三遮光结构”。

[0096]

在从基板1的法线方向观察时,将沟道区域307c中的与遮光层303重叠的部分p1称为“遮光部”,将与遮光层303不重叠的部分p2称为“光入射部”。通过遮光部p1相对于沟道区域307c整体的面积比例p1/(p1 p2),能够控制入射到氧化物半导体层307的光的量。将上述面积比例p1/(p1 p2)(%)称为沟道区域307c的“遮光比例ar”。遮光比例ar例如可以为25%

以上且75%以下。另外,如图9所示,“沟道区域307c”是指,从基板1的法线方向观察时,位于与源极se连接的源极接触区域307s和与漏极de连接的漏极接触区域307d之间,且在从基板1的法线方向观察时与栅极ge重叠的区域。

[0097]

在设置于有源矩阵基板的电路tft中,如果采用第二遮光结构,则阈值电压向负方向的偏移量比向正方向的偏移量大,结果存在阈值电压的负向偏移成为问题的tft。如果将第三遮光结构应用于这样的tft,则能够根据该tft的用途和特性劣化的大小来调整沟道区域307c的遮光比例ar,因此能够确保规定的阈值电压。

[0098]

作为一个例子,像素tft也可以具有第一遮光结构(遮光比例ar:100%)、sdd电路用tft具有第二遮光结构(遮光比例ar:0%)、构成栅极驱动器的一部分的电路tft(例如输出晶体管)具有第三遮光结构(遮光比例ar:25%以上且75%以下)。

[0099]

在从基板1的法线方向观察时,遮光层303在沟道宽度方向dw上横穿沟道区域307c,在沟道区域307c,遮光部p1和光入射部p2也可以在沟道长度方向dl上排列。由此,即使在沟道宽度方向dw上产生对准偏离,也能够实现期望的遮光比例ar。此外,具有选择性地得到来自规定的方向(光入射部p2侧)的光这样的优点。

[0100]

在该例子中,遮光层303与位于沟道区域307c的漏极侧的部分重叠。在沟道区域307c中,遮光部p1位于光入射部p2的漏极侧。另外,遮光层303在从基板1的法线方向观察时,也可以仅与沟道区域307c中的位于源极侧的部分重叠,在沟道区域307c中,遮光部p1位于光入射部p2的源极侧。

[0101]

<第三tft的变形例>第三tft中的遮光部p1的配置及形状不限于图9a及图9b所示的例子。

[0102]

图10a以及图10b分别是表示变形例1中的第三tft300a的俯视图以及截面图。在第三tft300a中,从基板1的法线方向观察时,遮光层303在沟道长度方向dl上横穿沟道区域307c,在沟道区域307c中,遮光部p1和光入射部p2在沟道宽度方向dw上排列。换而言之,遮光部p1以及光入射部p2分别在沟道长度方向dl上延伸。由此,即使在沟道长度方向dl上产生对准偏离,也能够实现期望的遮光比例ar。此外,选择性地得到规定的方向(来自光入射部p2侧的光)。

[0103]

图11a和图11b分别是表示变形例2的第三tft300b的俯视图和截面图。第三tft300b中具有在从基板1的法线方向观察时,遮光层303与沟道区域307c的一部分重叠的开口部。在沟道区域307c中,在遮光部p1的内部存在光入射部p2。由此,即使产生位置偏移也具有以下优点,能够以规定的面积比例ar配置遮光部p1以及光入射部p2。

[0104]

<显示装置的构成>有源矩阵基板1001可以应用于液晶显示装置等各种显示装置。

[0105]

图12a是例示本实施方式的显示装置2000的概略图。图12b是显示装置2000中的沿着图12a所示的xiib—xiib’线的放大截面图。

[0106]

显示装置2000具备显示面板81、背光源83和边框85。

[0107]

虽然未图示,但显示面板81具有有源矩阵基板1001、具备彩色滤光片、黑矩阵等的相对基板、配置于有源矩阵基板1001以及相对基板之间的光调制层(例如液晶层)。有源矩阵基板具有栅极驱动器电路形成区域gdm等周边电路形成区域cr。

[0108]

背光源83配置在显示面板81的背面侧(与有源矩阵基板1001的液晶层相反的一

侧)。背光源83可以为具有导光板的边缘方式(称为侧光方式、导光板方式。),也可以是直下型方式。

[0109]

边框85用于保持背光源83及显示面板81。如图所示,边框85具有:第一部分85a,其位于背光源83的背面侧;第二部分85b,其从第一部分85a的周缘向显示面板81侧延伸;以及面板支承部85c,其从第二部分85b的一部分向内侧延伸,并位于背光源83与显示面板81之间。面板支承部85c支承显示面板81的周缘部。从基板1的法线方向观察时,面板支承部85c以与显示面板81的显示区域不重叠,与非显示区域(周边区域)的至少一部分重叠的方式配置。面板支承部85c配置成与从基板1的法线方向观察时将显示面板的非显示区域中的至少栅极驱动器电路形成区域gdm等周边电路以与单片形成的区域(周边电路形成区域)cr重叠,并具有遮光功能,以使背光源光不入射到显示面板81的周边电路形成区域cr。

[0110]

在本实施方式中,如图所示,也可以在面板支承部85c设置开口区域87。即,面板支承部85c包括遮挡来自背光源的光30的遮光区域以及使来自背光源的光30的一部分透射或通过的开口区域87。由此,能够使背光源光的一部分经由开口区域87入射到周边电路形成区域cr。

[0111]

开口区域87被配置为在从基板1的法线方向观察时,与周边电路形成区域cr的至少一部分重叠。例如,显示面板中由面板支承部85c支承的周缘部包括周边电路形成区域的至少一部分即第一电路区域(在该例子中为栅极驱动器电路形成区域gdm),开口区域87在从基板的法线方向观察时也可以与第一电路区域的至少一部分重叠。

[0112]

开口区域87只要是使来自背光源83的光通过或透射的区域即可。开口区域87也可以包含一个或多个狭缝、贯通孔或切口部。在开口区域87也可以设置透光率比面板支承部85c的其它部分(遮光部)高的光透射部。

[0113]

另外,开口区域87的一部分或者全部也可以配置在从基板1的法线方向观察时与周边电路形成区域cr不重叠的位置(例如周边电路形成区域cr的周边)。在该情况下,只要以通过或透射开口区域87的光的一部分因绕回等而入射到周边电路形成区域cr的方式配置开口区域87即可。

[0114]

背光源光对周边电路形成区域cr的入射量可根据开口区域87的位置及尺寸进行调整。入射到周边电路形成区域cr的光入射到第二tft的氧化物半导体层,在第二tft产生预定的阈值电压的负向位移。

[0115]

另外,本实施方式的显示装置也可以不具有上述开口区域87。在该情况下,通过背光源光的一部分也绕回到面板支承部85c与周边电路形成区域cr之间,入射到第二tft的氧化物半导体层,因此得到抑制阈值电压的正向偏移的效果。

[0116]

<有源矩阵基板的实施例>本技术发明的实施方式的有源矩阵基板只要具备至少一个第一tft和至少一个第二tft或第三tft即可。表1例示在有源矩阵基板上设置的各tft与遮光结构(遮光层的有无)的关系。

[0117]

[表1]

[0118]

实施例1~6的有源矩阵基板中,消除易于发生阈值电压的正向偏移的电路tft的遮光层(第二遮光结构),减小遮光层的遮光比例ar(第三遮光结构)。由此,与比较例的有源

矩阵基板相比,能够抑制电路tft的特性偏移。

[0119]

在实施例4~6中,栅极驱动器电路用tft和ssd电路用tft的遮光比例ar不同。由此,能根据在该电路tft产生的阈值电压的正方向的偏移量来调整向氧化物半导体层的光入射量。ssd电路用tft的遮光比例ar可以小于栅极驱动器电路用tft的遮光比例ar(实施例1、4、6)。

[0120]

此外,也可以使电路tft中背光源光容易入射的位置的tft中的遮光比例ar小于难以入射的位置的tft中的遮光比例ar。例如,如图12b所例示,在设置边框85的开口区域87的情况下,可以使靠近开口区域87的tft的遮光比例ar小于远离开口区域87的位置的tft的遮光比例ar。

[0121]

<有源矩阵基板1001的制造方法>接着,参照附图说明本实施方式的有源矩阵基板的制造方法的一个例子。此处,主要说明制造作为像素tft的第一tft100和作为电路tft的第二tft200的方法。另外,第三tft300、300a、300b仅遮光层的形状不同,可以通过与第二tft同样的方法来制造。

[0122]

图13为用于说明有源矩阵基板1001的制造方法的一个例子的工艺流程的图。

[0123]

·

step1:下部金属层的形成在基板1上,例如通过溅射法形成下部导电膜(厚度:例如50nm以上且500nm以下)。接着,通过公知的光刻工序,进行下部导电膜的图案化(例如湿式蚀刻)。这样,形成第二tft中的包含遮光层203的下部金属层。

[0124]

作为基板1,可以使用透明且具有绝缘性的基板,例如玻璃基板、硅基板、具有耐热性的塑料基板(树脂基板)等。

[0125]

下部导电膜的材料没有特别限定,可以适当使用铝(al)、钨(w)、钼(mo)、钽(ta)、铬(cr)、钛(ti)、铜(cu)等金属或其合金、或含有该金属氮化物的膜。此外,也可以使用层叠有这些多个膜的层叠膜。此处,作为下部导电膜,使用从基板1侧起依次包含ti膜(厚度:30nm)和cu膜(厚度:200nm)的层叠膜(cu/ti膜)。

[0126]

·

step2:下部绝缘层5的形成接着,以覆盖下部金属层的方式形成下部绝缘层5(厚度:例如200nm以上且600nm以下)。

[0127]

下部绝缘层5例如由cvd法形成。作为下部绝缘层5,可以适当使用氧化硅(siox)层、氮化硅(sinx)层、氮氧化硅(sioxny;x>y)层、氧氮化硅(sinxoy;x>y)层等。下部绝缘层5既可以是单层,也可以具有层叠结构。例如,也可以在基板侧(下层)上,为了防止来自基板1的杂质等的扩散,形成氮化硅(sinx)层、氮化氧化硅层等,在其上的层(上层),为了确保绝缘性,形成氧化硅(sio2)层、氧化氮化硅层等。此处,作为下部绝缘层5,也可以形成以氮化硅(sinx)层(厚度:50~600nm)为下层、氧化硅(sio2)层(厚度:50~600nm)为上层的层叠膜。作为下部绝缘层5(下部绝缘层5具有层叠结构的情况下,作为其最上层),若使用氧化硅膜等氧化物膜,则能够通过氧化物膜减少后形成的氧化物半导体层的沟道区域产生的氧化缺损,因此能够抑制沟道区域的低电阻化。

[0128]

·

step3:氧化物半导体层107、207的形成接着,在下部绝缘层5之上形成氧化物半导体膜。之后,可以进行氧化物半导体膜的退火处理。氧化物半导体膜的厚度例如可以为15nm以上且200nm以下。

[0129]

接着,通过公知的光刻工序进行氧化物半导体膜的图案化。氧化物半导体膜的图案化例如可以通过使用含有磷酸、硝酸和乙酸的pan系蚀刻液或者使用草酸系蚀刻液的湿式蚀刻来进行。由此,得到作为第一tft和第二tft的活性层的氧化物半导体层107、207。

[0130]

氧化物半导体膜可通过例如溅射法形成。此处,作为氧化物半导体膜,形成包含in、ga及zn的in

‑

ga

‑

zn

‑

o系半导体膜(厚度:50nm)膜。

[0131]

·

step4:栅极绝缘层、栅极金属层的形成接着,以覆盖氧化物半导体层107、207的方式,依次形成栅极绝缘膜(厚度:例如80nm以上且250nm以下)和栅极用导电膜(厚度:例如50nm以上且500nm以下)。

[0132]

作为栅极绝缘膜,能够使用与下部绝缘层5同样的绝缘膜(作为下部绝缘层5例示的绝缘膜)。此处,形成氧化硅(sio2)层作为栅极绝缘膜。如果使用氧化硅膜等氧化物膜作为绝缘膜,则能够通过氧化物膜减少在氧化物半导体层107、207的沟道区域产生的氧化缺损,因此能够抑制沟道区域的低电阻化。

[0133]

作为栅极用导电膜,例如可以使用钼(mo)、钨(w)、铝(al)、铜(cu)、钛(ti)、钽(ta)等金属或它们的合金。栅极用导电膜也可以具有包括由不同的导电材料形成的多个层的层叠结构。此处,作为栅极用导电膜,使用以ti膜为下层、以cu膜为上层的cu/ti层叠膜、或者以mo膜为下层、以cu膜为上层的cu/mo层叠膜。

[0134]

然后,在栅极用导电膜上形成抗蚀剂层,将抗蚀剂层作为掩模进行栅极用导电膜的图案化,由此形成包含栅极ge1、ge2及栅极总线gl的栅极金属层。接着,将上述抗蚀层或栅极金属层作为掩模,进行栅极绝缘膜的蚀刻,得到栅极绝缘层109、209。由此,氧化物半导体层107、207中隔着栅极绝缘层109、209而与栅极ge1、ge2重叠的区域成为沟道区域107c、207c。

[0135]

·

step5:低电阻化处理以及层间绝缘层10的形成接着,也可以进行氧化物半导体层107、207的低电阻化处理。作为低电阻化处理,例如可以进行等离子体处理。由此,从基板1的主面的法线方向观察时,氧化物半导体层107、207中位于沟道区域107c、207c的两侧,露出的区域(第一区域和第二区域)成为电阻率比沟道区域107c、207c低的低电阻区域。低电阻区域也可以是导电体区域(例如片电阻:200ω/

□

以下)。

[0136]

接着,形成覆盖氧化物半导体层107、207、栅极绝缘层109、209及栅极金属层的层间绝缘层10。作为层间绝缘层10,能够单层或层叠氧化硅膜、氮化硅膜、氮氧化硅膜、氧氮化硅膜等无机绝缘层而形成。无机绝缘层的厚度可以是100nm以上且500nm以下。若使用使氮化硅膜等氧化物半导体还原的绝缘膜来形成层间绝缘层10,则能够将氧化物半导体层107、207中与层间绝缘层10相接的区域(此处为低电阻区域)的电阻率维持为较低,因此优选。此处,作为层间绝缘层10,例如通过cvd法形成以sio2层为下层、以sinx层为上层的层叠膜。

[0137]

然后,通过例如干蚀刻进行层间绝缘层10的图案化。由此,在层间绝缘层10上形成露出氧化物半导体层107、207的第一区域的一部分(源极接触区域)的源极用开口部110s、210s和露出第二区域的一部分(漏极接触区域)的漏极用开口部110d、210d。

[0138]

·

step6:源极金属层的形成接着,在层间绝缘层10上形成源极用导电膜(厚度:例如50nm以上且500nm以下),进行源极用导电膜的图案化。由此,形成包含源极se1、se2、漏极de1、d2及源极总线sl的上部金属层。源极se1、se2分别在源极用开口部110s、210s内与氧化物半导体层107、207的第

一区域连接。漏极de1、de2在漏极用开口部110d、210d内与氧化物半导体层107、207的第二区域连接。这样,制造第一tft100和第二tft200。

[0139]

作为第二源极用导电膜,例如可以使用选自铝(al)、铬(cr)、铜(cu)、钽(ta)、钛(ti)、钼(mo)或钨(w)中的元素、或以这些元素为成分的合金等。例如,也可以具有钛膜

‑

铝膜

‑

钛膜的三层结构、钼膜

‑

铝膜

‑

钼膜等的三层结构等。此处,使用以ti膜(厚度:15~70nm)为下层、以cu膜(厚度:200~400nm)为上层的层叠膜。

[0140]

·

step7:无机绝缘层11及有机绝缘层12的形成接着,以覆盖层间绝缘层10和源极金属层的方式形成上部绝缘层13。此处,作为上部绝缘层13,依次形成无机绝缘层11(厚度:例如100nm以上且500nm以下)和有机绝缘层12(厚度:例如1~3μm,优选为2~3μm)。另外,也可以将有机绝缘层12中的位于非显示区域的部分整体除去。或者,也可以不形成有机绝缘层12。

[0141]

作为无机绝缘层11,能够使用与层间绝缘层10同样的无机绝缘膜(作为层间绝缘层10例示的绝缘膜)。此处,作为无机绝缘层11,例如通过cvd法形成sinx层(厚度:300nm)。有机绝缘层12例如也可以是包含感光性树脂材料的有机绝缘膜(例如丙烯酸系树脂膜)。

[0142]

之后,进行有机绝缘层12的图案化。由此,在各像素区域pix,在有机绝缘层12形成露出无机绝缘层11的一部分的开口部12p。开口部12p配置成当从基板1的法线方向观观察时与像素tft的漏极de1重叠。

[0143]

·

step8:共用电极ce的形成接着,在上部绝缘层13上形成共用电极ce。

[0144]

首先,在上部绝缘层13上和开口部12p内形成未图示的第一透明导电膜(厚度:20~300nm)。此处,例如,通过溅射法形成铟

‑

锌氧化物膜作为第一透明导电膜。作为第一透明电极膜的材料,可以使用铟

‑

锡氧化物(ito)、铟

‑

锌氧化物、zno等金属氧化物。然后,进行第一透明导电膜的图案化。在图案化中,例如也可以使用草酸系蚀刻液进行湿式蚀刻。由此,获得共用电极ce。共用电极ce例如除了形成有像素接触孔chp的像素接触孔形成区域以外,也可以配置成遍及显示区域的大致整体上。

[0145]

·

step9:电介质层17的形成接着,以覆盖共用电极ce的方式形成电介质层(厚度:50~500nm)17,进行电介质层17和无机绝缘层11的图案化。

[0146]

电介质层17在像素区域pix中形成于有机绝缘层12和共用电极ce上以及开口部12p内。电介质层17的材料也可以与作为无机绝缘层11的材料所例示的材料相同。此处,作为电介质层17,例如通过cvd法形成sin膜。

[0147]

然后,通过光刻工序,形成在电介质层17上形成的抗蚀剂层(未图示)。以该抗蚀剂层及有机绝缘层12作为掩模,进行电介质层17及无机绝缘层11的蚀刻(例如干式蚀刻)。电介质层17和无机绝缘层11的蚀刻也可以在同一蚀刻工序中进行。由此,在像素区域pix中,形成使氧化物半导体层7的第二区域7d的一部分露出的像素接触孔chp。像素接触孔chp由形成在无机绝缘层11上的开口部11p、有机绝缘层12的开口部12p和电介质层17的开口部17p构成。开口部17p在从基板1的法线方向观察时,只要至少局部地与开口部12p重叠即可。

[0148]

·

step10:像素电极pe的形成接着,在电介质层17上以及像素接触孔chp内形成未图示的第二透明导电膜(厚

度:20~300nm)。第二透明导电膜的材料可以与作为第二透明导电膜的材料例示的材料相同(例如ito)。

[0149]

然后,进行第二透明导电膜的图案化。例如,也可以使用草酸系蚀刻液,进行第二透明导电膜的湿式蚀刻。由此,得到像素电极pe。像素电极pe在像素区域pix中形成于电介质层17上以及像素接触孔chp内,在像素接触孔chp内与像素tft的漏极de连接。这样,制造有源矩阵基板1001。

[0150]

<关于氧化物半导体>本实施方式中的各tft的氧化物半导体层所包含的氧化物半导体可以是非晶氧化物半导体,也可以是具有结晶质部分的结晶质氧化物半导体。作为结晶质氧化物半导体,可举出多晶氧化物半导体、微晶氧化物半导体、c轴大体垂直于层面取向的结晶质氧化物半导体等。

[0151]

氧化物半导体层也可以具有两层以上的层叠结构。在氧化物半导体层具有层叠结构的情况下,氧化物半导体层也可以包含非晶氧化物半导体层和结晶质氧化物半导体层。或者,也可以包含结晶结构不同的多个结晶质氧化物半导体层。此外,也可以包含多个非晶氧化物半导体层。在氧化物半导体层具有包含上层和下层的两层结构的情况下,两层中位于栅极侧的层(如果是底栅结构则为下层,如果是顶栅结构则为上层)所包含的氧化物半导体的能隙也可以比位于与栅极相反的一侧的层(如果是底栅结构则为上层,如果是顶栅结构则为下层)所包含的氧化物半导体的能隙小。但是,在这些层的能隙之差较小的情况下,位于栅极侧的层的氧化物半导体的能隙也可以大于位于与栅极相反的一侧的层的氧化物半导体的能隙。

[0152]

非晶氧化物半导体及上述各结晶质氧化物半导体的材料、结构、成膜方法、具有层叠结构的氧化物半导体层的构成等例如记载于日本特开2014

‑

007399号公报中。为了参考,将日本特开2014

‑

007399号公报的公开内容全部援引于本说明书中。

[0153]

氧化物半导体层可以包含例如in、ga及zn中的至少一种金属元素。在本实施方式中,氧化物半导体层例如包含in

‑

ga

‑

zn

‑

o系的半导体(例如氧化铟镓锌)。此处,in

‑

ga

‑

zn

‑

o系的半导体是in(铟)、ga(镓)、zn(锌)的三元系氧化物,in、ga及zn的比例(组成比)没有特别限定,例如包含in:ga:zn=2:2:1、in:ga:zn=1:1:1、in:ga:zn=1:1:2等。这样的氧化物半导体层能够由含有in

‑

ga

‑

zn

‑

o系的半导体的氧化物半导体膜形成。

[0154]

in

‑

ga

‑

zn

‑

o系的半导体可以是非晶质,也可以是结晶质。作为结晶质in

‑

ga

‑

zn

‑

o系的半导体,优选c轴大体垂直于层面取向的结晶质in

‑

ga

‑

zn

‑

o系的半导体。

[0155]

另外,结晶质in

‑

ga

‑

zn

‑

o系的半导体的结晶结构例如在上述的日本特开2014

‑

007399号公报、日本特开2012

‑

134475号公报、日本特开2014

‑

209727号公报等中有所公开。为了参考,将日本特开2012

‑

134475号公报和日本特开2014

‑

209727号公报的公开内容全部援引于本说明书中。具有in

‑

ga

‑

zn

‑

o系半导体层的tft具有高迁移率(超出a

‑

sitft的20倍)和低漏电流(不到a

‑

sitft的百分之一),因此,可适宜地用作驱动tft(例如,在包含多个像素的显示区域的周边,与显示区域相同基板上设置的驱动电路中所包含的tft)和像素tft(在像素中设置的tft)。

[0156]

氧化物半导体层也可以包含其它氧化物半导体来代替in

‑

ga

‑

zn

‑

o系半导体。例如可以包含in

‑

sn

‑

zn

‑

o系半导体(例如in2o3‑

sno2‑

zno;insnzno)。in

‑

sn

‑

zn

‑

o系半导体是in

(铟)、sn(锡)及zn(锌)的三元系氧化物。或者,氧化物半导体层也可以包含in

‑

al

‑

zn

‑

o系半导体、in

‑

al

‑

sn

‑

zn

‑

o系半导体、zn

‑

o系半导体、in

‑

zn

‑

o系半导体、zn

‑

ti

‑

o系半导体、cd

‑

ge

‑

o系半导体、cd

‑

pb

‑

o系半导体、cdo(氧化镉)、mg

‑

zn

‑

o系半导体、in

‑

ga

‑

sn

‑

o系半导体、in

‑

ga

‑

o系半导体、zr

‑

in

‑

zn

‑

o系半导体、hf

‑

in

‑

zn

‑

o系半导体、al

‑

ga

‑

zn

‑

o系半导体、ga

‑

zn

‑

o系半导体、in

‑

ga

‑

zn

‑

sn

‑

o系半导体、in

‑

w

‑

zn

‑

o系半导体等。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。