1.本公开总体上涉及半导体封装,更具体地,涉及一种包括具有沿着方向交错的接合指状物的封装基板的半导体封装。

背景技术:

2.通常,半导体封装包括封装基板和安装在封装基板上的半导体芯片。半导体芯片可通过诸如凸块或接合引线的连接手段电连接到封装基板。

3.最近,响应于朝着更轻和更短的封装产品推进,已对封装基板和半导体芯片的结构进行了研究以在有限区域内有效地布置多个电路图案。

技术实现要素:

4.根据本公开的实施方式的半导体封装可包括:封装基板,其包括第一接合指状物阵列和第二接合指状物阵列,第一接合指状物阵列和第二接合指状物阵列中的每一个在封装基板的表面上布置在第一方向上;第一半导体芯片,其设置在封装基板的所述表面上并且包括与第一接合指状物阵列对应的第一芯片焊盘阵列;第二半导体芯片,其设置在封装基板的所述表面上并且包括与第二接合指状物阵列对应的第二芯片焊盘阵列;第一接合引线,其将第一接合指状物阵列的接合指状物连接到第一芯片焊盘阵列的芯片焊盘;以及第二接合引线,其将第二接合指状物阵列的接合指状物连接到第二芯片焊盘阵列的芯片焊盘。第一接合指状物阵列的接合指状物和第二接合指状物阵列的接合指状物沿着第一方向彼此至少部分地交叠。

5.根据本公开的另一实施方式的半导体封装可包括:封装基板,其包括在封装基板的表面上在第一方向上分别沿着第一线和第二线布置的第一接合指状物阵列和第二接合指状物阵列;第一半导体芯片,其包括在封装基板的所述表面上与第一接合指状物阵列对应并且被设置为更靠近第二接合指状物阵列而不是第一接合指状物阵列的第一芯片焊盘阵列;第二半导体芯片,其包括在封装基板的所述表面上与第二接合指状物阵列对应并且被设置为更靠近第一接合指状物阵列而不是第二接合指状物阵列的第二芯片焊盘阵列;第一接合引线,其将第一接合指状物阵列的接合指状物连接到第一芯片焊盘阵列的芯片焊盘;第二接合引线,其将第二接合指状物阵列的接合指状物连接到第二芯片焊盘阵列的芯片焊盘;第一迹线图案,其在封装基板的表面上将第一接合指状物阵列的接合指状物电连接到封装基板的第一布线;以及第二迹线图案,其在封装基板的表面上将第二接合指状物阵列的接合指状物电连接到封装基板的第二布线。第一接合指状物阵列的接合指状物和第二接合指状物阵列的接合指状物沿着第一方向交错。

附图说明

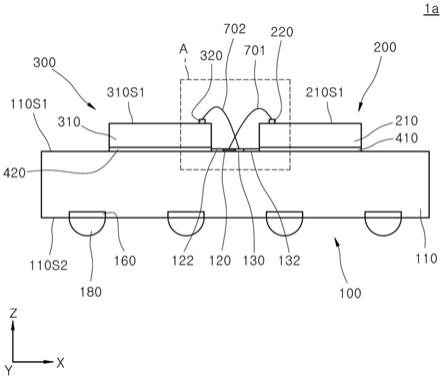

6.图1是示意性地示出根据本公开的实施方式的半导体封装的横截面图。

7.图2和图3是根据本公开的实施方式的半导体封装的平面图。

8.图4是图3的区域a1的放大图。

9.图5是根据本公开的另一实施方式的半导体封装的平面图。

具体实施方式

10.本文所使用的术语可对应于考虑其在所呈现的实施方式中的功能而选择的词语,术语的含义可被解释为根据实施方式所属领域的普通技术人员而不同。如果详细定义,则可根据定义来解释术语。除非另外定义,否则本文所使用的术语(包括技术术语和科学术语)具有实施方式所属领域的普通技术人员通常理解的相同含义。在本公开的实施方式的描述中,诸如“第一”和“第二”、“上”和“下”以及“左”和“右”的描述是为了区分构件,而非用于限制构件本身或意指特定顺序。

11.本文所描述的半导体芯片可包括集成有电子电路的半导体基板被切割成管芯的形式。半导体芯片可对应于存储器芯片、逻辑芯片(包括专用集成电路(asic)芯片)或系统芯片(soc)。存储器芯片可包括集成在半导体基板上的动态随机存取存储器(dram)电路、静态随机存取存储器(sram)电路、nand型闪存电路、nor型闪存电路、磁随机存取存储器(mram)电路、电阻式随机存取存储器(reram)电路、铁电随机存取存储器(feram)电路或相变随机存取存储器(pcram)电路。逻辑芯片可包括集成在半导体基板上的逻辑电路。半导体芯片可在划片工艺之后根据其形状而被称为半导体管芯。

12.在本说明书中,半导体封装可包括安装有半导体芯片的封装基板。封装基板可包括至少一层集成电路图案,并且在本说明书中可被称为印刷电路板(pcb)。半导体封装可包括层叠在封装基板上的多个半导体芯片。

13.半导体封装可用在诸如移动电话的各种通信系统、与生物技术或保健关联的电子系统或可穿戴电子系统中。

14.贯穿说明书,相同的标号可表示相同的元件。即使标号未参照一幅图提及或描述,该标号也可参照另一幅图提及或描述。另外,即使标号未在一幅图中示出,其也可参照另一幅图提及或描述。

15.在本说明书中,使用具有彼此垂直的x

‑

y

‑

z轴的笛卡尔坐标系来示出半导体封装。在这种情况下,x方向可意指平行于x轴的方向。类似地,y方向和z方向可分别意指平行于y轴的方向和平行于z轴的方向。

16.图1是示意性地示出根据本公开的实施方式的半导体封装1a的横截面图。参照图1,半导体封装1a可包括封装基板100、设置在封装基板100上的第一半导体芯片200以及设置为在横向方向上与第一半导体芯片200间隔开的第二半导体芯片300。第一半导体芯片200和第二半导体芯片300可以是同构芯片或异构芯片。第一半导体芯片200和第二半导体芯片300可分别通过引线接合电连接到封装基板100。

17.封装基板100可包括基板主体部分110。基板主体部分110可包括上表面110s1和与上表面110s1相对的下表面110s2。第一接合指状物阵列120和第二接合指状物阵列130可分别在基板主体部分110的上表面110s1上在第一半导体芯片200和第二半导体芯片300之间沿着第一方向(即,y方向)设置成一条线。即,在基板主体部分110的上表面110s1上,第一接合指状物阵列120可在y方向上沿着第一线布置并且第二接合指状物阵列130可在y方向上沿着第二线布置。尽管未示出,第一接合指状物阵列120和第二接合指状物阵列130中的每

一个可包括多个接合指状物。如稍后结合图2至图4描述的,第一接合指状物阵列120的接合指状物和第二接合指状物阵列130的接合指状物可被布置为彼此间隔开。另外,第一接合指状物阵列120的接合指状物和第二接合指状物阵列130的接合指状物可沿着第一方向(即,y方向)交错。这里,第一接合指状物阵列120的各个接合指状物的至少一部分和第二接合指状物阵列130的接合指状物的一部分可沿着第一方向(即,y方向)交叠。

18.参照图1,第一迹线图案122和第二迹线图案132可设置在上表面110s1上。第一迹线图案122可将第一接合指状物阵列120的接合指状物电连接到封装基板100的第一布线(未示出)。类似地,第二迹线图案132可将第二接合指状物阵列130的接合指状物电连接到封装基板100的第二布线(未示出)。第一迹线图案122和第二迹线图案132可分别在上表面110s1上延伸到第一半导体芯片200和第二半导体芯片300的下部,而不与第一半导体芯片200和第二半导体芯片300电接触。即,尽管未示出,第一迹线图案122和第二迹线图案132可在第一半导体芯片200和第二半导体芯片300下方在横向方向(例如,x方向)上延伸。

19.第一半导体芯片200可在上表面110s1上与第二接合指状物阵列130相邻设置。第一半导体芯片200可包括第一芯片主体部分210。第一芯片主体部分210可包括多个有源元件和无源元件以用于第一半导体芯片200的操作。作为示例,有源元件可至少包括场效应晶体管。作为示例,无源元件可至少包括电容器或电阻器。有源元件和无源元件可设置在第一芯片主体部分210的与上表面210s1相邻的内区域中。有源元件和无源元件可通过布线彼此连接以形成半导体集成电路。此外,第一芯片主体部分210可通过第一粘合层410接合到基板主体部分110的上表面110s1。

20.包括多个芯片焊盘的第一芯片焊盘阵列220可设置在第一芯片主体部分210的上表面210s1上。第一芯片焊盘阵列220可设置在上表面210s1的侧部并且可与第一接合指状物阵列120对应地沿着第一方向(即,y方向)设置成一条线。下面将参照图2至图4描述第一芯片焊盘阵列220的具体配置。

21.此外,第二半导体芯片300可在上表面110s1上与第一接合指状物阵列120相邻设置。第二半导体芯片300可包括第二芯片主体部分310。第二芯片主体部分310可包括多个有源元件和无源元件以用于第二半导体芯片300的操作。有源元件和无源元件可设置在第二芯片主体部分310的与上表面310s1相邻的内区域中。第二芯片主体部分310可通过第二粘合层420结合到基板主体部分110的上表面110s1。

22.包括多个芯片焊盘的第二芯片焊盘阵列320可设置在第二芯片主体部分310的上表面310s1上。第二芯片焊盘阵列320可设置在上表面310s1的一侧并且可与第二接合指状物阵列130对应地沿着第一方向(即,y方向)布置成一条线。下面将参照图2至图4描述第二芯片焊盘阵列320的具体配置。

23.参照图1,示出第一接合引线701,其将设置在基板主体部分110的上表面110s1上的第一接合指状物阵列120的接合指状物连接到设置在第一芯片主体部分210的上表面210s1上的第一芯片焊盘阵列220的芯片焊盘。另外,示出第二接合引线702,其将设置在基板主体部分110的上表面110s1上的第二接合指状物阵列130的接合指状物连接到设置在第二芯片主体部分310的上表面310s1上的第二芯片焊盘阵列320的芯片焊盘。如下面参照图2描述的,第一接合引线701和第二接合引线702可沿着第一方向(即,y方向)彼此交错。

24.此外,连接焊盘160可设置在基板主体部分110的下表面110s2附近。如图1所示,各

个连接焊盘160可部分地嵌入在基板主体部分110中,并且连接焊盘160的一个表面可在下表面110s2处暴露。然而,本公开不限于此,在未示出的其它实施方式中,连接焊盘160可设置在基板主体部分110的下表面110s2上。连接到外部系统的连接结构180可设置在连接焊盘160上。例如,各个连接结构180可包括焊料凸块或焊球。外部电源或电信号可通过连接结构180从外部系统输入到连接焊盘160。另外,可通过连接结构180提供外部接地端子的接地电位。输入到连接焊盘160的外部电源或电信号可分别通过基板主体部分110内的第一布线和第二布线(未示出)以及基板主体部分110上的第一迹线图案122和第二迹线图案132传送到第一接合指状物阵列120和第二接合指状物阵列130的接合指状物。另外,接地电位可被提供给第一接合指状物阵列120和第二接合指状物阵列130的接合指状物。接下来,外部电源、电信号和接地电位可分别通过第一接合引线701和第二接合引线702传送到对应的第一半导体芯片200和第二半导体芯片300的芯片焊盘,然后,第一半导体芯片200和第二半导体芯片300可使用外部电源和接地电位或者可处理电信号。

25.图2和图3是根据本公开的实施方式的半导体封装1a的平面图。具体地,图2和图3可以是图1的半导体封装1a的区域“a”的平面图。即,图2是示出图1的半导体封装的区域“a”的焊盘布置的平面图。图3是图2的平面图中省略第一接合引线701和第二接合引线702的示图。图4是图3的区域“a1”的放大图。以下,为了方便,将参照图3和图4详细描述与封装基板的接合指状物阵列和半导体芯片的芯片焊盘阵列的布置有关的配置,然后将参照图2描述与将接合指状物阵列和芯片焊盘阵列连接的接合引线的布置有关的配置。

26.参照图3和图4,第一接合指状物阵列120和第二接合指状物阵列130可设置在基板主体部分110的上表面110s1上。第一接合指状物阵列120和第二接合指状物阵列130可各自沿着第一方向(即,y方向)布置成一条线。参照图3,作为实施方式,第一接合指状物阵列120可包括彼此间隔开的第一至第六接合指状物120a、120b、120c、120d、120e和120f。另外,第二接合指状物阵列130可包括按间隔彼此间隔开的第一至第六接合指状物130a、130b、130c、130d、130e和130f。尽管图3示出第一接合指状物阵列120和第二接合指状物阵列130中的每一个具有六个接合指状物,但本公开未必限于此。在一些实施方式中,第一接合指状物阵列120和第二接合指状物阵列130中的每一个可具有不同的并且各种数量的接合指状物。

27.在实施方式中,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可以是信号指状物、电源指状物和接地指状物之一。第一至第六接合指状物120a、120b、120c、120d、120e和120f当中的与信号指状物对应的接合指状物可彼此电分离。另一方面,第一至第六接合指状物120a、120b、120c、120d、120e和120f当中的与电源指状物对应的接合指状物可彼此电连接。尽管图3和图4中未示出,与电源指状物对应的接合指状物的电连接可由第一迹线图案122和封装基板100的其它布线实现。类似地,第一至第六接合指状物120a、120b、120c、120d、120e和120f当中的与接地指状物对应的接合指状物可彼此电连接。尽管图3和图4中未示出,与接地指状物对应的接合指状物的电连接可由第一迹线图案122和封装基板100的其它布线实现。

28.另外,第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可分别是信号指状物、电源指状物和接地指状物之一。第一至第六接合指状物130a、130b、130c、130d、130e和130f当中的与信号指状物对应的接合指状物可

彼此电分离。另一方面,第一至第六接合指状物130a、130b、130c、130d、130e和130f当中的与电源指状物对应的接合指状物可彼此电连接。类似地,第一至第六接合指状物130a、130b、130c、130d、130e和130f当中的与接地指状物对应的接合指状物可彼此电连接。

29.参照图3和图4,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可在基板主体部分110的上表面110s1上彼此间隔开布置。另外,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可沿着第一方向(即,y方向)交错。参照图4,作为示例,第一接合指状物阵列120的第一接合指状物120a可沿着第一方向(即,y方向)设置在第二接合指状物阵列130的第一接合指状物130a和第二接合指状物130b之间。作为另一示例,第二接合指状物阵列130的第二接合指状物130b可沿着第一方向(即,y方向)设置在第一接合指状物阵列120的第一接合指状物120a和第二接合指状物120b之间。如图3中描述的,第一接合指状物阵列120和第二接合指状物阵列130的剩余接合指状物也可按相同方式设置在封装基板100的上表面110s1上。

30.在实施方式中,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可被布置为沿着第一方向(即,y方向)彼此至少部分地交叠。参照图4,作为示例,第一接合指状物阵列120的第一接合指状物120a和第二接合指状物120b以及第二接合指状物阵列130的第一接合指状物130a和第二接合指状物130b可在基板主体部分110的上表面110s1上沿着第一方向(即,y方向)在第一距离s1内具有交叠区域。类似地,图3所示的第一接合指状物阵列120的第三至第六接合指状物120c、120d、120e和120f以及第二接合指状物阵列130的第三至第六接合指状物130c、130d、130e和130f也可沿着第一方向(即,y方向)在相同的第一距离s1内具有交叠区域。在交叠区域中,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可沿着第一方向面向彼此。

31.如上所述,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f被布置为沿着第一方向(即,y方向)具有交叠区域,以使得第一接合指状物阵列120和第二接合指状物阵列130相对于第二方向(即,x方向)的集成密度可改进。即,第一接合指状物阵列120和第二接合指状物阵列130相对于第二方向(即,x方向)按更密集的形状设置,以使得可节省在基板主体部分110的上表面110s1上用于布置第一接合指状物阵列120和第二接合指状物阵列130的接合指状物的空间。

32.另外,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可被布置为沿着垂直于第一方向的第二方向(即,x方向)彼此部分地交叠。参照图4,第一接合指状物阵列120的第一接合指状物120a和第二接合指状物阵列130的第一接合指状物130a可在基板主体部分110的上表面110s1上沿着第二方向(即,x方向)在第二距离s2内具有交叠区域。类似地,一起参照图3和图4,第一接合指状物阵列120的第二至第六接合指状物120b、120c、120d、120e和120f以及第二接合指状物阵列130的第二至第六接合

指状物130b、130c、130d、120e和130f也可沿着第二方向(即,x方向)在相同的第二距离s2内具有交叠区域。在交叠区域中,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可沿着第二方向面向彼此。

33.如上所述,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f以及第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f被布置为沿着第二方向(即,x方向)彼此至少部分地交叠,以使得第一接合指状物阵列120和第二接合指状物阵列130相对于第一方向(即,y方向)的集成密度可改进。即,第一接合指状物阵列120和第二接合指状物阵列130相对于第一方向(即,y方向)以更密集的形式设置,以使得可节省在基板主体部分110的上表面110s1上用于布置接合指状物的空间。

34.对于一些实施方式,如上面参照图4描述的,接合指状物部分地交叠意指与接合指状物关联的区域(而非接合指状物本身)彼此交叠。类似地,对于一些实施方式,接合指状物的交叠部分意指与接合指状物的彼此交叠的部分关联的区域,而非接合指状物的那些部分本身。

35.一起参照图3和图4,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可包括指状物主体部分b和指状物边缘部分e。第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可在指状物主体部分b中具有基本上均匀的宽度w1。第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可在指状物边缘部分e中具有沿着第二方向(即,x方向)减小的宽度。第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可在指状物边缘部分e的距指状物主体部分b最远的端部ea处具有最小宽度w2。作为示例,如图3和图4所示,第一至第六接合指状物120a、120b、120c、120d、120e和120f中的每一个可在基板主体部分110的上表面110s1上具有六边形平面形状。

36.类似地,第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可包括指状物主体部分b和指状物边缘部分e。第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可在指状物主体部分b中具有基本上均匀的宽度w1。第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可在指状物边缘部分e中具有沿着第二方向(即,x方向)减小的宽度。第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可在指状物边缘部分e的距指状物主体部分b最远的端部ea处具有最小宽度w2。作为示例,如图3和图4所示,第一至第六接合指状物130a、130b、130c、130d、130e和130f中的每一个可在基板主体部分110的上表面110s1上具有六边形平面形状。

37.参照图3和图4,第一接合指状物阵列120的接合指状物120a、120b、120c、120d、120e和120f与第二接合指状物阵列130的接合指状物130a、130b、130c、130d、130e和130f之间沿着第一方向(即,y方向)的交叠可以是接合指状物120a、120b、120c、120d、120e和120f与接合指状物130a、130b、130c、130d、130e和130f的边缘部分e之间的交叠。

38.一起参照图3和图4,第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f的指状物边缘部分e可被设置为面向第一芯片焊盘阵列220的

对应芯片焊盘220a、220b、220c、220d、220e和220f。第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f的指状物边缘部分e可被设置为面向第二芯片焊盘阵列320的对应芯片焊盘320a、320b、320c、320d、320e和320f。

39.作为示例,第一延长线c1穿过第一接合指状物阵列120的第一接合指状物120a的中心轴线并在第二方向(即,x方向)上延伸。第一延长线c1可与第一芯片焊盘阵列220的第一芯片焊盘220a相遇。尽管图3和图4中未示出,可提供各自穿过第一接合指状物阵列120的第二至第六接合指状物120b、120c、120d、120e和120f的中心轴线并在第二方向(即,x方向)上延伸的多条延长线。多条延长线中的每一条与第一芯片焊盘阵列220的对应第二至第六芯片焊盘220b、220c、220d、220e和220f相遇。穿过第一接合指状物阵列120的第二至第六接合指状物120b、120c、120d、120e和120f的中心轴线延伸的多条延长线可平行于穿过第一接合指状物120a的中心轴线在第二方向(即,x方向)上延伸的第一延长线c1。

40.作为另一示例,第二延长线c2穿过第二接合指状物阵列130的第一接合指状物130a的中心轴线并在第二方向(即,x方向)上延伸。第二延长线c2可与第二芯片焊盘阵列320的第一芯片焊盘320a相遇。尽管图3和图4中未示出,可提供穿过第二接合指状物阵列130的第二至第六接合指状物130b、130c、130d、130e和130f的中心轴线在第二方向(即,x方向)上延伸的多条延长线。多条延长线中的每一条与第二芯片焊盘阵列320的对应第二至第六芯片焊盘320b、320c、320d、320e和320f相遇。穿过第二接合指状物阵列130的第二至第六接合指状物130b、130c、130d、130e和130f的中心轴线的多条延长线可平行于穿过第一接合指状物130a的中心轴线在第二方向(即,x方向)上延伸的第二延长线c2。

41.此外,第一延长线c1和第二延长线c2可彼此平行。因此,平行于第一延长线c1的多条延长线和平行于第二延长线c2的多条延长线可彼此平行。因此,如图2所示,可在形成第一接合引线701和第二接合引线702时有效地布置第一接合引线701和第二接合引线702以防止彼此之间的电短路。即,第一接合引线701和第二接合引线702可沿着第一方向(即,y方向)交替地布置以按距离彼此间隔开。

42.另外,当第一延长线c1、第二延长线c2和其它延长线彼此平行形成时,可减轻或抑制在将芯片焊盘和接合指状物与接合引线连接的工艺中发生的缺陷。具体地,引线接合可利用引线接合毛细管形成。可利用引线接合毛细管的移动来调节引线接合或连接路径的形状。当连接芯片焊盘和接合指状物的接合引线彼此平行时,用于连接接合引线的引线接合毛细管的移动路径可维持彼此平行。因此,可进行连接工艺,而不会使引线接合毛细管接触其它相邻接合引线。换言之,可减轻或防止在引线接合工艺中由于引线接合毛细管的移动而引起的相邻接合引线的变形或损坏。

43.一起参照图3和图4,第一迹线图案122和第二迹线图案132可设置在基板主体部分110的上表面110s1上。第一迹线图案122可从第一至第六接合指状物120a、120b、120c、120d、120e和120f的指状物主体部分b在第二半导体芯片300的方向上延伸。图4中的第一迹线图案122的宽度w3可小于指状物主体部分b的宽度w1。尽管未具体地示出,第一迹线图案122可延伸到第二半导体芯片300的下部并且可电连接到封装基板100的第一布线。作为示例,第一布线可包括封装基板100的外层电路图案、内层电路图案和通孔。第一迹线图案122可通过诸如通孔的第一布线电连接到图1所示的封装基板100中的对应连接焊盘160。因此,通过连接结构180输入到连接焊盘160的外部信号和外部电源可传送到第一接合指状物阵

列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f。

44.类似地,第二迹线图案132可从第一至第六接合指状物130a、130b、130c、130d、130e和130f的指状物主体部分b在第一半导体芯片200的方向上延伸。图4中的第二迹线图案132的宽度w3可小于指状物主体部分b的宽度w1。尽管未具体地示出,第二迹线图案132可延伸到第一半导体芯片200的下部并且可电连接到封装基板100的第二布线。第二迹线图案132可通过诸如通孔的第二布线电连接到图1所示的封装基板100中的对应连接焊盘160。因此,通过连接结构180输入到连接焊盘160的外部信号和外部电源可传送到第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f。

45.参照图3,第一半导体芯片200可被设置为在上表面110s1上更靠近第二接合指状物阵列130而不是第一接合指状物阵列120。第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f可与第一半导体芯片200间隔开距离d。另外,第二半导体芯片300可被设置为更靠近第一接合指状物阵列120而不是第二接合指状物阵列130。第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f可与第二半导体芯片300间隔开距离d。

46.一起参照图2至图4,第一接合引线701可将第一接合指状物阵列120的第一至第六接合指状物120a、120b、120c、120d、120e和120f连接到第一芯片焊盘阵列220的对应第一至第六芯片焊盘220a、220b、220c、220d、220e和220f。另外,第二接合引线702可将第二接合指状物阵列130的第一至第六接合指状物130a、130b、130c、130d、130e和130f连接到第二芯片焊盘阵列320的对应第一至第六芯片焊盘320a、320b、320c、320d、320e和320f。

47.第一半导体芯片200的第一至第六芯片焊盘220a、220b、220c、220d、220e和220f可通过第一接合引线701连接到第一接合指状物阵列120的对应第一至第六接合指状物120a、120b、120c、120d、120e和120f。第一接合指状物阵列120被设置为比第二接合指状物阵列130更远离第一半导体芯片200。另外,第二半导体芯片300的第一至第六芯片焊盘320a、320b、320c、320d、320e和320f可通过第二接合引线702连接到第二接合指状物阵列130的对应第一至第六接合指状物130a、130b、130c、130d、130e和130f。第二接合指状物阵列130被设置为比第一接合指状物阵列120更远离第二半导体芯片300。

48.在实施方式中,参照图2和图3,第一接合引线701和第二接合引线702可如下形成。首先,使用引线接合毛细管将接合引线的一端接合到第二半导体芯片300的第一芯片焊盘320a。随后,通过使引线接合毛细管移动以将接合引线的另一端接合到第二接合指状物阵列130的第一接合指状物130a来形成第二接合引线702。最后,将接合引线与第二接合引线702断开。此时,第一接合指状物130a被设置为与第一半导体芯片200充分间隔开距离d,以使得引线接合毛细管不接触半导体芯片并且可形成接合引线的环路形状。为了形成第一接合引线701,引线接合毛细管移动到第一半导体芯片200的第一芯片焊盘220a。接合引线的一端接合到第一半导体芯片200的第一芯片焊盘220a。随后,通过使引线接合毛细管移动以将接合引线的另一端接合到第一接合指状物阵列120的第一接合指状物120a来形成第一接合引线701。最后,接合引线与第一接合引线701断开。此时,第一接合指状物120a被设置为与第二半导体芯片300充分间隔开距离d,以使得引线接合毛细管不接触半导体芯片并且可形成接合引线的环路形状。以相同的方式,第二接合引线702和第一接合引线701可沿着第一方向(即,y方向)交替地形成。

49.此外,如上面参照图3描述的,穿过第一至第六接合指状物120a、120b、120c、120d、120e和120f的中心轴线延伸的多条延长线以及穿过第一至第六接合指状物130a、130b、130c、130d、130e和130f的中心轴线延伸的多条延长线可彼此平行。因此,第一接合引线701和第二接合引线702可在减轻或防止电短路的状态下沿着第一方向(即,y方向)彼此交错。另外,如上所述,可减轻或防止在引线接合工艺中由于引线接合毛细管的移动而引起的相邻接合引线的变形或损坏。

50.图5是根据本公开的另一实施方式的半导体封装1b的平面图。图5可示出上面参照图1至图4描述的半导体封装1a的封装基板100上设置的第一迹线图案122和第二迹线图案132的修改。除了第一迹线图案124和第二迹线图案134之外,图5所示的半导体封装1b可具有与上面参照图1至图4描述的半导体封装1a基本上相同的配置。

51.参照图5,此实施方式的第一迹线图案124可从第一接合指状物阵列120的接合指状物的指状物边缘部分e朝着第一半导体芯片200延伸。尽管未示出,第一迹线图案124可延伸到第一半导体芯片200的下部并且可电连接到封装基板100的第一布线。第一迹线图案124可通过诸如通孔的第一布线电连接到图1所示的封装基板100的对应连接焊盘160。通过这样,第一接合指状物阵列120的分别与信号指状物、电源指状物和接地指状物对应的接合指状物可接收通过连接焊盘160输入的外部信号、外部电源和外部接地电位。

52.类似地,第二迹线图案134可从第二接合指状物阵列130的接合指状物的指状物边缘部分e朝着第二半导体芯片300延伸。第二迹线图案134可延伸到第二半导体芯片300的下部并且可电连接到封装基板100的第二布线。第二迹线图案134可通过诸如通孔的第二布线电连接到图1所示的封装基板100的对应连接焊盘160。通过这样,第二接合指状物阵列130的接合指状物可接收通过连接焊盘160输入的外部信号和外部电源,并且可通过连接焊盘160连接到外部接地端子。

53.如上所述,根据本公开的一些实施方式的半导体封装包括在封装基板上分别与不同半导体芯片引线接合的第一接合指状物阵列和第二接合指状物阵列。第一接合指状物阵列和第二接合指状物阵列可分别沿着第一方向布置成一条线。第一接合指状物阵列的接合指状物和第二接合指状物阵列的接合指状物被设置为沿着第一方向和垂直于第一方向的第二方向彼此至少部分地交叠。因此,封装基板上的接合指状物在第一方向和第二方向上的集成度可改进。结果,可在封装基板上有效布置第一接合指状物阵列和第二接合指状物阵列。另外,通过节省第一接合指状物阵列和第二接合指状物阵列的布置空间,封装基板上实现的各种其它图案的设计自由度可改进。

54.出于例示性目的公开了本公开的实施方式。本领域技术人员将理解,在不脱离本公开和所附权利要求的范围和精神的情况下,可进行各种修改、添加和替换。

55.相关申请的交叉引用

56.本技术要求2020年4月20日提交的韩国申请no.10

‑

2020

‑

0047748的优先权,其整体通过引用并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。