1.本发明总体上涉及存储器设备,并且特别地涉及用于保护具有保护存储器功能的存储器的设备和方法。

背景技术:

2.随着处理性能的提高,现代计算系统和设备要求越来越多的存储容量。特别地,具有存储器保护功能(例如,刷新)的存储器广泛用于各种高速且存储器要求高的应用(例如,图形卡),以及执行各种任务的联网和通信应用。

3.然而,这样的存储器容易受到某些类型的侧信道攻击。例如,双倍数据速率(ddr)存储器特别容易遭受故障注入攻击,该故障注入攻击在于使用注入技术将故意(或“恶意”)故障注入ddr存储器,并观察对应的错误输出以提取或修改存储在存储器上的信息。一种类型的故障注入攻击称为行锤攻击(row hammer attack)。行锤攻击可以包括基本的行锤攻击或其变型:双侧行锤攻击。行锤攻击可以通过在存储器单元的刷新窗口内重复地访问存储器的单个行来导致ddr存储器的故障。因此,与被访问的行在物理上邻近的字线有非常高的概率发生数据损坏。行锤击(hammering)可以导致ddr存储器单元泄漏其电荷并且在ddr存储器单元之间发生电交互,从而可能由于两个刷新之间对ddr存储器访问次数过多而导致改变在原始存储器访问中未被寻址的附近存储器行(未被访问的在物理上邻近的行)的内容。

4.行锤攻击相应地使用被访问的单元的快速行激活,这可以导致被存储在未被访问的相邻行中的位的值的改变。因此,行锤攻击利用ddr缺陷来获得对ddr内容的不受限制的访问,由此允许对ddr存储器进行未经授权的读取/写入访问。

5.存在用于防止行锤效应的发生的不同的技术。一些现有的解决方案基于纠错码(ecc)、基于频繁刷新所有行或者基于概率性邻近行激活(probabilistic adjacent row activation,para),如在例如以下文献中公开的:

6.‑

yoongu kim;ross daly;jeremie kim;chris fallin;ji hye lee;donghyuk lee;chris wilkerson;konrad lai;onur mutlu(2014年6月24日),“flipping bits in memory without accessing them:an experimental study of dram disturbance errors”,ece.cmu.edu.ieee.,2015年3月10日检索。

7.‑

mark seaborn;thomas dulien(2015年3月9日),“exploiting the dram rowhammer bug to gain kernel privileges”,googleprojectzero.blogspot.com.google,2015年3月10日检索。

8.‑

sarani bhattacharya;debdeep mukhopadhyay(2016年8月4日),“curious case of rowhammer:flipping secret exponent bits using timing analysis”,eprint.iacr.org/2016,2017年11月6日检索。

9.然而,这样的方法是昂贵的。特别地,尽管ecc允许修复位翻转,但是针对行锤攻击的基于ecc的保护要求专门用于ecc的存储空间。因此,保护随存储器的量线性地缩放。此

外,检测能力是受限(最多两个错误位)且昂贵的(因为存储器的一部分专用于ecc,保护随存储器的量线性地缩放)。例如,要在常规的ddr3 dimm标准64位(8

×

8)中添加ecc,必须使用72位(8

×

9)。

10.而且,在针对行锤攻击的基于ecc的保护不能针对确定的攻击者提供保护的意义上,这种基于ecc的保护只是一种安全保护。因此,这要求在ddr芯片的cpu侧进行验证(例如,附加的ecc)。因此,基于ecc的解决方案不允许保护ddr芯片的cpu。因此,ddr芯片是不安全的。

11.此外,尽管基于频繁刷新所有行的解决方案和概率性邻近行激活(para)的解决方案呈现出较低的面积开销,但它们就性能而言具有高成本。

12.实际上,在频繁刷新所有行的情况下,当存储器处于刷新状态时,系统无法访问该存储器。因此,增加两个刷新之间的持续时间通常由制造商执行。

13.在概率性邻近行激活(para)方法中,为了尝试降低就性能而言的成本,仅在特定行上激活刷新,这些行对应于与以低概率被访问的行邻近的行。然而,这样的解决方案要求生成不必要的刷新,并且因此就性能而言具有附加的成本。

14.因此,用于防止行锤效应的常规方法要么基于使得ddr芯片能够本地地抵抗行锤攻击,要么基于昂贵的对行锤攻击的上游检测。

15.因此,需要对具有存储器保护功能的存储器的针对行锤攻击的改进的保护。

技术实现要素:

16.为了克服这些和其他问题,提供了一种存储器设备,包括存储器,该存储器包括至少一个芯片,每个芯片包括用于存储多个位的一个或多个存储体(bank),每个存储体包括行和列的集合,每个行和每个列包括多个位,该设备还包括:控制器,其被配置为生成:对存储器的访问命令、标识对应于存储器的给定行的地址的访问命令以及要对给定行执行的命令操作。

17.存储器设备还包括保护设备,该保护设备包括:

18.‑

变换单元,其被配置为响应于对标识地址的访问命令的接收而应用变换函数,以将所述地址变换为变换后的地址;

19.‑

地址存储数据结构,其被配置为取决于与地址相关联的访问的频率来存储变换后的地址,该地址存储数据结构响应于在存储器设备中执行的存储器保护操作而被重置。

20.保护设备还包括:访问频率管理器,其被配置为确定与地址存储数据结构中维护的地址相关联的访问频率是否大于或等于阈值,并且如果访问频率大于或等于阈值,则从存储器内触发存储器中的存储器保护操作。

21.在一个实施例中,保护设备可以包括至少一个访问计数器,该至少一个访问计数器被配置为对存储器的两个存储器保护操作之间的与给定地址相关的访问命令进行计数,与地址相关联的访问的频率是使用计数器值被确定的。

22.在一些实施例中,保护设备可以包括与每个地址相关联的一个访问计数器。

23.存储器设备可以根据时钟周期操作,并且变换函数可以是被定义的从存储器大小到α(n/h)个字的平衡且非单射函数,α为严格大于1的整数,n表示两个存储器保护操作之间的时钟周期的数量,并且h表示行锤攻击应访问一个地址以使其故障的平均次数。

24.在一个实施例中,变换函数可以是散列函数或加密函数。

25.特别地,变换函数可以被配置为每个时钟周期处理一个地址。

26.有利地,保护设备3还可以包括:加扰器,其被配置为对在由存储器接收到的访问命令中标识出的地址的至少一些选定位进行加扰。

27.选定位可以包括地址的最低有效位。

28.在一个实施例中,由加扰器进行的地址加扰可以是基于与关联于地址的访问频率相关的条件被触发的。

29.在一些实施例中,存储器设备可以包括处理器,由加扰器进行的地址加扰是由存储器设备的处理器触发的。

30.由加扰器进行的地址加扰可以使用由嵌入式随机数生成器生成的位序列来执行。

31.在一个实施例中,加扰器可以实现对地址的最低有效位(lsb)的置换(permutation)。

32.加扰器可以使用从线性仿射码中选择的随机码字,该线性仿射码具有高于或等于预定义值d的最小距离。

33.在一些实施例中,保护设备可以在存储器或控制器中实现。

34.在一个实施例中,存储器保护操作可以是刷新操作。

35.还提供了一种用于保护存储器的方法,存储器包括至少一个芯片,每个芯片包括用于存储多个位的一个或多个存储体,每个存储体包括行和列的集合,每个行和每个列包括多个位,该设备还包括:控制器,其被配置为生成:对存储器的访问命令、标识对应于存储器的给定行的地址的访问命令以及要对给定行执行的命令操作。有利地,方法可以包括:

36.‑

响应于对标识地址的访问命令的接收而应用变换函数,该变换函数被配置为将地址变换为变换后的地址;

37.‑

取决于与地址相关联的访问的频率来将变换后的地址存储在地址存储数据结构中,该地址存储数据结构响应于在存储器设备中执行的存储器保护操作而被重置。

38.方法还包括:确定与地址存储数据结构中维护的地址相关联的访问频率是否大于或等于阈值,并且如果访问频率大于或等于阈值,则从存储器内触发存储器中的存储器保护操作。

39.本发明的各种实施例提供了抵抗行锤攻击的ddr存储器,这消除了对攻击的上游检测的需要。此外,根据本发明的实施例的ddr存储器以可量化的方式使得行锤攻击利用非常困难。

附图说明

40.包含在本说明书中并构成本说明书一部分的附图示出了本发明的各种实施例,并且与上面给出的本发明的一般描述和下面给出的实施例的详细描述一起用于解释本发明的实施例。

41.图1是存储器设备的图解视图。

42.图2是根据一些实施例的存储器设备的图解视图。

43.图3描绘了根据一个实施例的其中可以实现存储器设备的示例性操作环境。

44.图4示出了示例性双侧行锤攻击。

45.图5是表示根据示例性硬件实现方式的保护设备的逻辑电路。

46.图6是描绘根据一些实施例的由保护设备实现的保护方法的流程图。

47.图7描绘了根据本发明的示例性实施例的加扰器。

具体实施方式

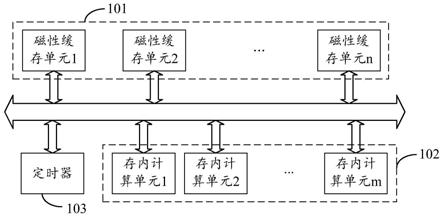

48.参考图1,示出了根据本发明一些实施例的存储器设备100。

49.存储器设备100包括被组织为矩阵的存储器1,其中数据位存储在行和列的交叉处。

50.更具体地,存储器1可以包括一个或多个芯片(或模块)2,每个芯片(或模块)2具有多存储体架构。仅出于说明的目的,在图1中仅表示一个芯片2。每个芯片2可以包括用于存储多个位的一个或多个存储体10。每个存储体10的尺寸为n

×

p并且包括行13和列4的集合。因此,每个行13(也称为“线”)包括由行大小n定义的多个位,并且每个列14包括由列大小p定义的位数。

51.存储器1可以是具有诸如刷新功能等之类的存储器保护功能的任何存储器。存储器1例如可以是易失性存储器,例如,基于ram的存储器,其例如可以是dram存储器或ddr存储器。仅出于说明的目的,将参考ddr类型的存储器1对本发明的一些实施例进行以下描述。然而,技术人员将容易理解,本发明通常适用于具有刷新功能的任何存储器。

52.存储器保护功能指定可以被实现以保护存储器以防止或停止存储器劣化的任何功能(或操作),例如,在于切断对存储器的访问的功能或刷新功能。如本文所使用的,刷新功能(或刷新操作)指定在于重置存储器的状态的功能。

53.仅出于说明的目的,将主要参考刷新操作类型的存储器保护操作对一些实施例进行以下描述。然而,本领域技术人员将容易理解,本发明通常适用于存储器保护功能或操作。

54.可以通过水平字线选择行13。每个行包括一个或多个晶体管。响应于接收到逻辑高信号,使能行的晶体管并将存储电容器连接到对应的垂直位线。垂直位线连接到读出放大器(sense amplifier),该读出放大器通过放大由存储电容器生成的小电压改变来提供放大信号。然后,存储器设备100输出放大信号并且位线被驱动回以刷新行。如果没有字线是活动的,则存储器阵列为空闲,并且位线维持在预充电状态。

55.为了访问存储器,必须首先选择一行并将其加载到读出放大器中。然后,该行为活动的,并且可以访问列以进行读取或写入。

56.存储器1还可以包括与每个存储体10相关联的行缓冲器15。存储器设备100还可以包括存储器设备控制器102以控制存储体行3的激活以及读取/写入操作。

57.每个存储器存储体10可以由行地址和列地址两者寻址。

58.存储器设备控制器102可以发出激活命令以激活指定存储体10中的给定行。为了激活由行地址标识的存储器存储体10的给定行13,可以激活所请求的行并将其复制到与存储器存储体10的给定行相关联的行缓冲器15。可以响应于活动命令将存储器设备10设置为活动状态。

59.在存储器设备100的活动状态下,可以执行读取和/或写入操作。为了执行读取和/或写入操作,可以向激活的行发出数据突发(burst)。

60.可以在读取或写入命令期间使用列14,以指向开放页(open page)内的用于读取/写入操作的特定地址。如本文所使用的,“页”(或“存储器页”)指代存储在ddr 1的相同行内的数据块。

61.为了对ddr存储器的行(存储器页)进行寻址,命令可以指定存储器存储体10和行地址。当存储器存储体10为活动时,“开放”页与存储体的缓冲器15相关联。

62.页在缓冲器15中保持开放,直到需要开放不同的页来访问不同的地址为止。

63.可以由存储器设备控制器102发出读取命令,以发起对到活动行的数据突发的读取。为了读取存储在由行地址标识的给定行中的数据突发,该行可以在行缓冲器15中充电并被读取。

64.为了从存储器1中读取,控制器102可以通过向存储器1发出活动命令来标识要在存储器1中寻址的芯片2、存储体10和行13。响应于活动命令,存储器1可以经由一个或多个读出放大器输出整行数据。被寻址的存储器芯片2然后可以接受读取命令。读取命令可以包括列地址。存储器1可以解码读取命令的列地址以选择要被读取的数据,并使用读出放大器输出被读取的数据。然后,响应于由存储器控制器102向存储器1发出的预充电命令,存储器1可以返回到空闲状态。

65.可以由存储器设备控制器102发出写入命令,以发起数据突发到活动行13的写入。为了将数据突发写入由行地址标识的给定行13中,可以将数据突发存储在行缓冲区15中并写回对应的行13。

66.响应于来自存储器设备控制器102的刷新命令,可以发起刷新操作。刷新操作可以包括对所有存储体10进行预充电,这涉及关闭所有存储体10的行13。响应于预充电,可以将存储器设备10设置为空闲状态。

67.这种存储器芯片10的两个刷新之间的时间可以是固定的。在刷新之后,存储器点(memory point)很强,因此免受锤击的影响。在多次新的访问之后,存储器点可能再次变得容易受到锤击。因此,如果攻击者设法在两个刷新之间对同一地址进行足够次数的访问(即,读取或写入),则行锤攻击可能是有效的。

68.两个刷新之间的时钟周期的数量用n表示。理论上,在该时间间隔内最多可以访问存储器n次。如本文所使用的,术语“时钟周期”指代ddr存储器设备100操作所依据的时钟周期。

69.攻击应访问一个地址以使存储器设备100(或具有高概率的邻居)故障的平均次数表示为h。理论上,行锤的安全性问题是h>n。因此,在常规的ddr存储器中,攻击者可以通过总是访问相同的地址来在存储器设备100中注入故障。需要注意的是,在实践中,很难在每个时钟周期处访问存储器设备100,因为高速缓冲存储器“记得”已经被访问的数据,并通过再次查询存储器设备100来立即返回记住的值。对于行锤攻击者,解决方法在于刷新高速缓存行,这可以以大约每一百个时钟周期一次的频率重复。在保守的方法中,假设行锤攻击者可以每个时钟周期访问一次。替代攻击被称为双侧锤击,其中攻击者通过连续访问地址a

‑

1和a 1来专注于使地址a故障。

70.因此,已经确定如果攻击者不能访问一个地址(或距离为2的地址)多于h次,则攻击可以停止。

71.根据本发明的各种实施例的存储器设备100改进了对存储器1免受包括自适应攻

击在内的行锤攻击的保护。

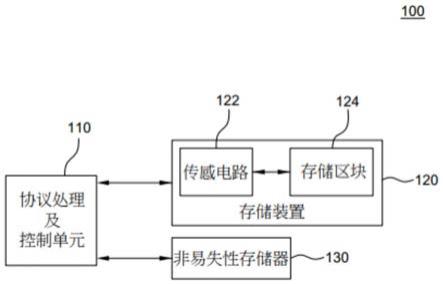

72.图2描绘了根据一些实施例的存储器设备100。

73.存储器设备100可以包括保护单元3,该保护单元3被配置为保护存储器设备100免受ddr类型的故障注入攻击。保护单元3可以包括已访问地址存储数据结构30,例如,一个或多个访问直方图,其被配置为使用平衡且非单射变换函数f针对每个存储芯片2维护两个刷新周期之间(或更一般地,两个存储器保护操作周期之间)的顶部已访问地址(或行)的列表,该平衡且非单射变换函数f被配置为确定在访问命令中标识出的地址的图像(也称为“变换后的图像”),该访问命令还指定命令操作(例如,读取或写入)和要在标识出的地址处执行命令操作的数据。出于说明的目的,将参考直方图类型的已访问地址存储数据结构30对一些实施例进行以下描述。

74.尽管保护设备3被描绘为与ddr控制器102和存储器1分开,但应注意,在一些实施例中,保护设备可以在ddr控制器102或存储器1中实现。

75.为了检测对相同地址的过多访问,可以使用利用与功能存储器1相同大小的影子存储器的访问直方图30。根据这种方法,每个地址将在刷新时被重置为零,并在每次访问时递增(即,值加一)。如果一个值等于h,则检测到攻击。

76.可替代地,为了避免与功能存储器1相同大小的新的影子存储器的实例化,存储器需要可以从要保护的存储器1的大小(可以等于几千兆字节)减少到n=h。根据这种方法,存储器设备100可以使用队列类型的已访问地址存储数据结构30来跟踪最频繁的访问并监视对存储器1的任何新访问。在这种基于存储器减少的方法中,队列30的管理可以包括以下步骤:

77.‑

第一步骤,包括针对标识地址的每个所请求的访问,通过检查地址是否存储在队列中来确定该地址是否已经被访问;

78.‑

如果是(在队列中找到地址),则该地址被怀疑是攻击的目标并在队列中维护,并且递增访问计数器。如果访问计数器等于h,则可以采取行动。

79.‑

如果地址尚未在队列30中,则如果有一些可用的自由空间,则将该地址插入队列中,并且(多个)最旧的访问地址(表示访问次数最少的(多个)最旧的地址)被丢弃到自由空间。

80.这种基于存储器减少的方法利用了这样的事实:旧访问不太可能是行锤的目标,因为它被访问的速度不够快。

81.然而,已经分析过这种基于存储器减少的方法不适于抵抗自适应攻击。事实上,攻击者可以例如访问个地址两次,以便以标记的频繁地址填充队列。任何新地址都会弹出先前的唯一地址。因此,将不会检测到a 1和a

‑

1处的锤击,因为a 1处的访问将弹出a

‑

1,反之亦然。因此,攻击可以绕过这种保护。

82.为了提供针对行锤攻击的鲁棒保护,保护设备3可以包括访问频率管理器32,其被配置为使用与地址的访问的频率相关的数据,从已访问地址存储数据结构30检测与给定地址相关联的访问频率何时大于或等于预定阈值。保护设备3可以包括至少一个访问计数器,其被配置为确定对ddr存储器1的两个刷新之间的与给定地址相关的访问命令进行计数,与关联于地址的访问的频率相关的数据是使用计数器值被确定的。在一个实施例中,每个地

址可以与访问计数器i相关联,该访问计数器i被配置为对ddr存储器1的两个刷新之间的对该地址的访问进行计数。如果与该地址相关联的访问频率大于或等于预定阈值,则访问频率管理器32可以从存储器芯片2内触发刷新周期而不是由控制器102触发。这使得能够检测行锤攻击。

83.在一些实施例中,存储器设备100还可以包括加扰器34,其被配置为对在访问命令中标识出的每个地址的至少一些选定位进行加扰以防止行锤攻击。在一个实施例中,选定位可以包括每个访问地址的最低有效位。每个地址加扰操作可以由与地址相关联的访问频率(如使用与地址相关联的访问计数器确定的)触发和/或由特定模式触发(例如,以防止双侧行锤攻击)。保护设备3被配置为执行标识地址的访问命令,例如,读取(如果命令指定读取操作)在命令中指定的数据或将该数据写入(如果命令指定“写入”操作)到存储器1中的加扰地址。

84.有利地,地址加扰可以是动态加扰。它可以由存储器设备100的处理器(cpu)编程或者是固有的(例如,可以使用由嵌入式随机数生成器生成的位序列来执行加扰)。在加扰由cpu编程的情况下,cpu可以向加扰器发送用于确保地址加扰的指令。如本文所使用的,“固有”加扰指代其中存储器设备1例如通过在存储器设备的每次重置时触发地址加扰来自身控制地址加扰的实施例。

85.在一些应用中,存储器1可能需要定期刷新(例如,每64ms)。在常规的sdram中,在刷新期间不能传输数据,而刷新可能要求一些时间(典型地大约为70纳秒或ns)。

86.在一些实施例中,存储器设备100的至少一些组件可以位于集成电路ic(例如,专用集成电路(asic)、可编程逻辑设备(pld)、现场可编程门阵列(fpga)或其组合)上。在一些实施例中,存储器1可以在集成电路的外部。集成电路可以包括存储器控制器102。

87.存储器设备控制器102可以包括请求缓冲器1020和响应缓冲器1021,请求缓冲器1020被配置为缓冲要发送到存储器1的请求,响应缓冲器1021被配置为缓冲从存储器1接收到的响应。

88.存储器设备控制器102还可以包括存储器映射器1022,其被配置为将由存储器请求标识的存储器地址解码为标识对应的存储体10、行13和列14的数据的三元组(triplet)。存储体10可以由整数标识(从0到k,k

‑

1表示存储体的数量)。每个行13可以由范围从0到n

‑

1的整数i标识。每个列14可以由表示列的位置的二进制数(例如,“00”、“01”、“10”、“11”)标识。

89.存储器地址具有预定义的位长度(例如,32位)。存储器地址可以包括:

90.‑

字节偏移,其具有预定义长度(例如,3位长度);

91.‑

存储体选择,其具有取决于存储体的数量的预定义的位长度;

92.‑

芯片选择,其具有取决于由存储器使用的芯片的数量的预定义的长度;

93.‑

列选择,其取决于存储器大小和类型而变化;

94.‑

行选择,其取决于存储器大小和类型而变化;

95.存储器设备控制器102还可以包括:命令生成器1022,其用于生成到存储器设备1的(多个)命令;存储器仲裁器1021,其被配置为取决于仲裁方案管理接收到的请求访问存储器1所依据的次序;数据路径(未示出),其被配置为将从存储器设备1接收到的响应发送到存储器控制器102的响应缓冲器。虽然存储器仲裁器1021在图1中被示为驻留在存储器控

制器102中,但是技术人员将容易地理解,存储器仲裁器1021可以驻留在存储器控制器102外部的计算机系统的其他组件中。

96.由命令生成器生成的命令可以标识命令操作(例如,读取、写入、激活)以及对应于(多个)行13和(多个)存储体10并从接收到的请求导出的地址。

97.在一个实施例中,存储器设备100可以是基于ddr(双倍数据速率)的存储器设备,例如,ddr、ddr2、ddr3存储器。基于ddr的存储器可以在下文被简称为“ddr存储器”。

98.ddr存储器被配置为在时钟周期的上升沿和下降沿两者上获取数据,从而针对给定时钟频率使数据速率加倍。例如,在ddr2设备中,数据传输频率为200mhz,其中总线速度为100mhz。因此,通过在时钟周期的上升沿和下降沿两者上进行数据获取,使处理速率加倍。

99.ddr存储器与临时属性(temporization property,或临时编号)相关联,该临时属性表示采用ddr存储器执行给定操作的时钟脉冲的数量。临时属性由数字表示,该数字越小,存储器就越快。

100.临时编号可以与以下操作中的一个相关联:

101.‑“

cl”或“列地址选通”(cas)时延,其表示存储器设备控制器102要求存储器1访问指定存储器列的时间与返回所请求的数据的时间之间的以时钟周期为单位的时间量(如果已经选择了一行,则其为将列地址发送到存储器设备控制器之后返回结果之前所需的时钟周期的数量)。

102.‑“

trcd”或“行地址选通(ras)到cas延迟”,其表示行被激活的时间与列经由cas信号被激活并且数据可以被写入存储器单元或从存储器单元读取的时间之间的以周期为单位的时间量。

103.‑“

trp”或“ras预充电”,其表示禁用一行访问并开始下一行访问所要求的周期的数量。

104.‑

活动与预充电命令之间的“tras”或“活动到预充电延迟”,即,存储器设备必须等待直到可以发起对存储器的下一次访问为止的时钟周期的数量。

105.‑“

cmd”或“命令速率”,其表示存储器设备激活与第一命令可以被发送到存储器设备的时间之间的时钟周期的数量。

106.当需要数据时,控制器102可以激活ras线以指定需要数据的行,并且然后激活cas线以指定列。

107.图3示出了其中可以实现存储器设备100的示例性操作环境。操作环境可以包括cpu 20和存储器设备100,该存储器设备100具有诸如ddr存储器之类的存储器1。存储器1可以用于存储可以由cpu 20执行的应用程序。

108.可以经由由存储器控制器102指定的行地址来访问存储器1的行。然后,可以提供被寻址的数据的列地址。另一列地址可以用于访问行内的其他数据,而无需再次提供行地址(称为“页命中”)。在一些实施例中,不要求针对每个列访问提供行地址。

109.cpu 20可以发起从存储器1向cpu 20传输数据的读取请求或从cpu向存储器1传输数据的写入请求。存储器请求(例如,读取或写入请求)可以与辅助信息(例如,标识命令的类型(读取或写入)的信息,或标识请求的优先级的优先级指示符)相关联。辅助信息可以被包括在存储器请求中或使用合适的通信协议在单独的消息中被发送。

110.cpu 20可以通过主机总线21连接到存储器控制器102。存储器控制器102可以通过存储器总线22连接到存储器1。在一些实施例中,存储器控制器102还可以连接到图形控制器24,该图形控制器24被配置为管理对存储图形数据的帧缓冲器的访问(存储或取回操作),以便管理这样的数据在图形用户接口上的呈现。可以在任何类型的显示设备25上生成图形用户接口。

111.存储器控制器102可以通过接口连接到i/o(输入/输出)控制器26。i/o控制器可以包括到i/o设备的接口。i/o控制器26可以被配置为路由i/o数据传输。

112.本发明的各种实施例提供了针对故障注入攻击(例如,行锤攻击或其变型(例如,双侧行锤攻击))的保护,该故障注入攻击在两个刷新之间使用对存储器(1)的大量访问以导致存储器中的错误。

113.如图4中示出的,图4描绘了示例性双侧行锤攻击,这种攻击通常使用(例如,在行13

i

‑1和13

i 1

中的)快速行激活,该快速行激活试图改变存储在与被激活的行13

i

‑1和13

i 1

相邻的目标行13

i

中的位的值。

114.本发明的实施例利用攻击者的机会错误(chancy fault),而不是昂贵的对这种攻击的检测。

115.在一个实施例中,为了避免直方图30的大小膨胀,可以将直方图的大小设置为n/h,其中n表示两个刷新之间的时钟周期的数量(理论上,存储器在这样的时间间隔中最多可被访问n次),而h表示攻击将访问一个地址以使存储器设备100(或具有高概率的邻居)故障的平均次数。

116.由保护设备3应用于顶部已访问行的平衡函数f可以是从存储器大小(例如,2

64

个字)到α(n/h)个字的非单射,α是严格大于1的整数。例如,α可以等于10。如本文所使用的,术语“平衡”指示函数的任何原像的数量相同。例如,如果α(n/h)=2

m

,则正好有2

64

‑

m

个字映射到[0;α(n/h)=2

m

[中的每个直方图箱(histogram bin)。如果n个访问是随机的,则可以期望[0;α(n/h)[中的计数器全部等于h/α。事实上,

[0117]

假设攻击者执行行锤攻击,则攻击者将需要命中唯一地址至少h次。因此,对于直方图中的一个输入,将有一个值优于或等于h(≥h),其中期望值更接近h/α。这样的值(命中≥h次)在直方图中脱颖而出,并且证明了行锤尝试。

[0118]

在一个实施例中,为了检测行锤,访问频率管理器32可以确定对相同地址的重复访问是否使计数器i增加超过期望值h/α(因为h>h/α)。应该注意的是,在这种行锤检测中可能会出现误报,而实际上没有攻击尝试。例如,如果良性程序在给定直方图输入的一组原像中执行访问,则可能会发生这种情况。为了避免这种误报,由平衡函数f执行的非单射映射可能是随机的,这使得其对于攻击者是无法预测的。

[0119]

在一些实施例中,函数f可以被配置为每个时钟周期处理一个地址。映射函数f可以是“流水线化”的,这意味着变换顶部已访问地址的过程可以在一个时钟周期内启动,即使最终结果仅在多个时钟周期之后输出。在一个实施例中,函数f还可以是“全组合”的,这意味着在一个时钟周期内终止变换顶部已访问地址的过程。

[0120]

在一个实施例中,函数f可以是被配置为将其输出(函数f的输出)截断为预期位宽的散列函数(例如,键控散列函数)。这防止攻击者执行第二原像攻击,该第二原像攻击将允

许攻击者始终命中散列表中的相同条目(散列表指代与散列函数结合使用的散列表)。

[0121]

可替代地,函数f可以是加密函数,其被配置为对已访问的地址计算轻量级加密,并且丢弃由这样的计算产生的位以匹配期望的位宽。函数f可以基于加密算法。由于加密算法是本地键控的,因此它们尊重关于攻击者的保密约束。

[0122]

函数f可以是例如轻量级密码函数,例如,函数present(andrey bogdanov、lars r.knudsen、gregor leander、christof paar、axel poschmann、matthew j.b.robshaw、yannick seurin和charlotte vikkelsoe的present:an ultra

‑

lightweight block ciphe(ches,lncs第4727卷,第450

‑

466页,springer,2007年9月10

‑

13日,奥地利维也纳))或成熟加密函数,例如,aes(高级加密标准)。

[0123]

使用散列函数或加密函数作为函数f来变换顶部已访问地址是特别有利的,因为这样的函数是迭代的,并且因此可以被流水线化。

[0124]

在另一实施例中,函数f可以在于将顶部已访问地址(例如,2

64

个地址)映射到大小为p的集合,其中p是被选择为小于α(n/h)同时值接近α(n/h)的秘密随机素数。因此,这种映射对应于归约模p。

[0125]

响应于确定访问频率超过给定阈值,访问频率管理器32可以从存储器1内触发刷新周期。

[0126]

加扰器34可以相对于访问频率管理器32的操作以并行或任何顺序的次序执行地址加扰。

[0127]

由于行锤攻击趋向于是确定性的,因此通过使用加扰器34,可以打乱地址数据或线性混合地址数据,从而防止攻击者预测故障的影响。

[0128]

在一个实施例中,加扰器34可以执行对给定地址的地址位中的至少一些的置换。可以对地址的最低有效位(lsb)执行该置换。该位数可以根据期望的保护级别和性能需要而变化。利用这种保护,攻击者必须在每次加扰之后重新查找目标行(“受害者”行)在存储器中所位于的位置以及哪些地址是相邻的。

[0129]

图5是表示根据示例性硬件实现的保护设备3的逻辑电路。

[0130]

保护设备3包括逻辑or门300,其接收并输入刷新信号和计数器值“count i”。

[0131]

如图5中示出的,如果检测到行锤攻击,则通过在刷新线301与外部刷新电线302之间执行or操作(逻辑or门300)来强制ddr存储器1刷新,从而导致ddr存储器1比预期更早刷新。需要注意的是,在大多数ddr存储器中,通常无法控制刷新速率。ddr控制器102确保对刷新速率的这种控制。然而,保护设备3实现多个逻辑(300、301、302)以能够触发(或强制)刷新。

[0132]

保护设备可以通过使用加扰器34来与行锤攻击的检测正交地实现预防对策。加扰器34可以被配置为打乱已访问地址的最低有效位(lsb)。在一个实施例中,加扰器34可以实现一种双射的加扰算法。示例性加扰算法可以在于从线性仿射码中选择一个随机码字(如本文所使用的,仿射码是线性码的陪集,线性码将零(0)值映射到零(0)值),其最小距离高于或等于某个值d。这种加扰器34避免直接邻居以2

d

<<1的概率被“行锤击”。然而,本发明不限于这种加扰算法,并且可以应用各种双射加扰算法。

[0133]

应当注意,构建直方图32的步骤和执行物理访问加扰的步骤(如由加扰器34实现的)可以被并行计算,由此组合它们的安全增益而不会对性能产生负面影响。

[0134]

此外,虽然在本技术中进行了联合描述,但是应当注意,本发明的某些方面可以被独立保护。特别地,在直方图30中存储变换后的地址之前使用函数f变换已访问地址的步骤以及执行物理访问加扰的步骤(如由加扰器34实现的)可以在不同的实现方式中独立地实现。

[0135]

图6是描述根据一些实施例的由保护设备实现的保护方法的流程图。

[0136]

在步骤601中,响应于刷新(块600),直方图30的条目被重置,即,被初始化为零值(重置步骤)。

[0137]

在步骤603中,响应于接收要求访问给定地址的访问命令(块602),与该地址相关联的访问计数器i递增。

[0138]

在步骤604中,通过应用变换函数f来确定命令中标识出的地址的图像。

[0139]

在步骤605中,将被寻址的图像(也称为“变换后的地址”)存储在直方图中。

[0140]

在步骤606中,可以对在步骤603中接收到的命令中标识出的地址进行加扰。需要注意的是,虽然步骤606表示为在步骤605之后顺序地执行,但是可替代地,步骤606可以与步骤604和步骤605中的任一个并行实现。

[0141]

在步骤607中,取决于访问命令中标识出的操作(例如,读取或写入),将对应于访问命令的数据读取(r)或写入(w)到与加扰地址相对应的行。

[0142]

图7描绘了根据本发明的示例性实施例的加扰器34。

[0143]

在图7的示例中,加扰器34被配置为对已访问地址的最低有效位应用置换变换。在另一实施例中,可以例如通过对一条线和不在计数器列表中的另一条线中访问较少的线进行交换来执行加扰。

[0144]

对已访问地址的加扰的操作可以在系统的每次启动时被触发。

[0145]

可替代地,对已访问地址的加扰的操作可以由访问频率管理器32触发。例如,在图7的实施例中,访问频率管理器32可以由有限状态机fsm实现,该有限状态机fsm被配置为:确定访问频率是否与被存储在直方图30中的已访问地址相关联;确定与已访问地址相关联的访问频率是否大于或等于预定阈值th,并且如果访问频率大于或等于预定阈值th,则:

[0146]

‑

从ddr存储器内触发ddr存储器的刷新周期;和/或

[0147]

‑

触发对已访问地址的加扰(例如,置换)。

[0148]

因此,ddr存储器1维护加扰地址,以使得攻击者难以在其攻击过程中对作为攻击的目标的行旁边的行进行锤击。

[0149]

本发明的实施例改进了对ddr存储器的保护。本发明的实施例可以在ddr存储器1或ddr存储器控制器102上实现。本发明的实施例可以采用仅包含软件、仅包含硬件或包含硬件和软件元件两者的实施例的形式。例如,实施例可以在cmos逻辑中实现。本发明的实施例可以容易地集成到任何ddr设备。它们提供可量化的安全增益。它们使攻击者难以标识哪些线在物理上与经受行锤攻击的线相邻。因此,根据本发明的实施例的保护方法和设备确保了针对行锤攻击的高效威慑保护。尽管根据本发明的实施例的保护方法和设备可以应用于其他类型的攻击,但是由于ram布局的随机化,它们对于故障注入攻击特别有效。

[0150]

本文所描述的方法可以通过供应给任何类型的计算机的处理器的计算机程序指令来实现,以产生具有执行指令以实现本文指定的功能/行为的处理器的机器。这些计算机程序指令也可以存储在计算机可读介质中,该计算机可读介质可以指导计算机以特定方式

运行。为此,计算机程序指令可被加载到计算机上,以引起一系列操作步骤的执行,由此产生计算机实现的过程,使得执行的指令提供用于实现本文指定的功能的过程。

[0151]

应当注意,流程图、序列图和/或框图中指定的功能、动作和/或操作可以与本发明的实施例一致地重新排序、串行处理和/或同时处理。此外,流程图、序列图和/或框图中的任一个可以包括比与本发明的实施例一致地示出的那些更多或更少的块。

[0152]

虽然已经通过对各种实施例的描述说明了本发明的实施例,并且虽然已经相当详细地描述了这些实施例,但申请人的意图并不是限制或以任何方式将所附权利要求书的范围局限于这种细节。本领域的技术人员将很容易看到附加的优点和修改。因此,本发明在其更宽泛的方面并不限于所示和所描述的具体细节、代表性方法和说明性示例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。