1.本发明涉及一种多层线路板及其制作方法。

背景技术:

2.随着印制电路板在电子领域的广泛应用,厚铜多层电路板在汽车电子、线圈等方面应用也越来越广,使用者对厚铜电路板的功能要求也越来越高,例如:为电子元器件提供必要的电气连接以及机械支撑、电源集成、提供大电流、高可靠性等。因此,厚铜多层电路板的前景广阔,利润空间较传统线路板大,具有非常大的开发价值。

3.然而,蚀刻设备、蚀刻制程能力的限制一直是局限厚铜技术发展的关键因素。具体地,蚀刻设备、蚀刻制程能力的限制会影响蚀刻因子等参数,导致细线路的线宽与线距不达标,影响细线路的制作。另外,多层电路板的厚度较大,使得导电通孔的纵深比较高,在增层用的基材的流动性不大的情况下,高纵深比会影响基材在导电通孔内的的填充性。

技术实现要素:

4.有鉴于此,本发明提供一种能够满足大功率大电流需求、能够降低蚀刻设备与蚀刻制程能力限制且填充性能优异的多层电路板。

5.另,还有必要提供一种如上所述的多层电路板的制作方法。

6.一种多层电路板,包括:一内层线路叠构体,所述内层线路叠构体包括交替堆叠在一起的至少一第一类导电线路层及至少一第二类导电线路层,所述第一类导电线路层及所述第二类导电线路层分别由具有差分蚀刻性质的第一类金属层及第二类金属层制作形成;一第一增层电路基板,所述第一增层电路基板与所述内层线路叠构体电连接;及一第二增层电路基板,所述第二增层电路基板与所述第一增层电路基板位于所述内层线路叠构体的两侧;所述第二增层电路基板分别与所述内层线路叠构体及所述第一增层电路基板电连接。

7.进一步地,所述第一类金属层为铜,所述第二类金属层为银。

8.进一步地,所述内层线路叠构体还包括多条内层线路,相邻的两条内层线路的形貌呈正梯形或倒梯形或两端窄中间宽的漏斗形,其中,漏斗形是由一个正梯形与一个倒梯形构成的;相邻的两条内层线路之间形成有线路沟槽。

9.进一步地,所述多层电路板还包括分别压合在所述内层线路叠构体相背两表面上的第一胶层和第二胶层,部分所述第一胶层与所述第二胶层填充在所述线路沟槽内。

10.进一步地,所述第一增层电路基板包括一形成在所述第一胶层上的第一基材层,所述第二增层电路基板包括一形成在所述第二胶层上的第二基材层,所述第一胶层及所述第二胶层的流动性优于所述第一基材层及所述第二基材层的流动性。

11.进一步地,所述第二增层电路基板通过至少一导电通孔与所述第一增层电路基板电连接;所述多层电路板还包括:一形成在所述第一增层电路基板上的第三胶层;一形成在所述第二增层电路基板上的第四胶层,部分所述第四胶层及部分所述第三胶层填充在所述

导电通孔内;一形成在所述第三胶层上的第三增层电路基板,所述第三增层电路基板与所述第一增层电路基板电连接;及一形成在所述第四胶层上的第四增层电路基板,所述第三增层电路基板与所述第二增层电路基板电连接。

12.一种如上所述的多层电路板的制作方法,包括:提供一金属叠构体,所述金属叠构体包括交替堆叠在一起的至少一第一类金属层及至少一第二类金属层,所述第一类金属层及所述第二类金属层具有差分蚀刻性质;在所述金属叠构体的一侧表面上贴合一图案化的干膜层并在所述金属叠构体的另一侧贴合一保护膜层;所述干膜层与所述保护膜层相背;所述第二类金属层从图案化的所述干膜层中裸露出来;使用第一种蚀刻药水蚀刻从图案化的所述干膜层中裸露出来的所述第二类金属层,以在所述第二类金属层上形成第一线路沟槽,进而将所述第二类金属层形成第一导电线路层;使用第二种蚀刻药水蚀刻从所述第一线路沟槽中裸露出来的第一类金属层,以在所述第一类金属层形成第二线路沟槽,进而将所述第一类金属层形成第二导电线路层;所述第二导电线路层及所述第一导电线路层构成一内层线路叠构体;去除所述干膜层;及分别在所述内层线路叠构体的相背两表面之上形成一第一增层电路基板及第二增层电路基板,并使得所述第一增层电路基板及所述第二增层电路基板分别与所述内层线路叠构体电连接并使得所述第一增层电路基板及所述第二增层电路基板电连接。

13.进一步地,所述内层线路叠构体包括多条内层线路,相邻的两条内层线路之间形成有线路沟槽;在“分别在所述内层线路叠构体的相背两表面之上形成一第一增层电路基板及第二增层电路基板”的步骤之前,还包括:分别在所述第一类导电线路层及所述第二类导电线路层上压合一第一胶层及一第二胶层;部分所述第一胶层与部分所述第二胶层填充在所述线路沟槽内;所述第一增层电路基板形成在所述第一胶层上,所述第二增层电路基板形成在所述第二胶层上。

14.进一步地,在“分别在所述内层线路叠构体的相背两表面之上形成一第一增层电路基板及第二增层电路基板”的步骤之前,还包括:在所述第一导电线路层上压合一第一胶层,并去除保护膜层;使用所述第二种蚀刻药水蚀刻所述金属叠构体,以在贴过保护膜层一侧的第一类金属层上形成第三线路沟槽,进而形成第三导电线路层;使用所述第一种蚀刻药水蚀刻所述金属叠构体,从所述第三线路沟槽中裸露出来的第二类金属层被蚀刻形成第四线路沟槽,以形成第四导电线路层;及在所述第三导电线路层上压合第二胶层,所述第二胶层填充在所述第三线路沟槽与所述第四线路沟槽内。

15.进一步地,所述第二增层电路基板通过至少一导电通孔与所述第一增层电路基板电连接;还包括:在所述第一增层电路基板上压合一第三胶层;在所述第二增层电路基板上压合一第四胶层;所述第三胶层与所述第四胶层填充在所述导电通孔内;在所述第三胶层上形成一第三增层电路基板;及所述第三增层电路基板与所述第一增层电路基板电连接;及在所述第四胶层上形成一第四增层电路基板;所述第四增层电路基板与所述第二增层电路基板电连接。

16.本发明提供的多层电路板及其制作方法,1)采用具有差分蚀刻性质的第一类金属层及第二类金属层制作内层线路叠构体110(厚铜线路),由于第一类金属层及第二类金属层之间的差分蚀刻作用,对第一类金属层和第二类金属层的蚀刻可以分别进行,如此,既能够对多层电路板大电流、大功率的需求,又能够降低蚀刻设备与蚀刻制程能力限制,使得线

路的线宽与线距达标;2)采用流动性好的胶层进行增层并填充在导电通孔内,可以满足高纵深比的填充性,提升所述多层电路板的信赖性。

附图说明

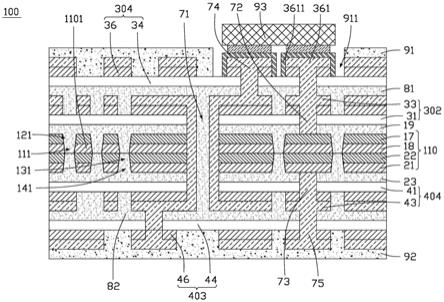

17.图1为本发明一较佳实施方式提供的一多层电路板的剖视图。

18.图2为本发明一较佳实施方式提供的一金属叠构的剖视图。

19.图3为在图2所示的金属叠构的上下两表面上分别形成一干膜层及一保护膜层并对所述干膜层进行曝光、显影,在干膜层上形成线路图案后的剖视图。

20.图4为对从图3所示的干膜层中裸露出来的金属叠构中的第二金属层进行蚀刻,形成第一导电线路层后的剖视图。

21.图5为对从图4所示的第一线路沟槽中裸露出来的金属叠构中的第一金属层进行蚀刻,形成第二导电线路层后的剖视图。

22.图6为去除图5所示的所述干膜层后的剖视图。

23.图7为在图6所示的第一导电线路层的表面上压合一第一胶层并去除图6所示的保护膜层后的剖视图。

24.图8为将图7所示的第三金属层及第四金属层制作形成第三导电线路层及第四导电线路层,形成内层线路叠构体后的剖视图。

25.图9为在图8所示的第三导电线路层上压合一第二胶层后的剖视。

26.图10为在图8所示的第一及第二胶层上分别形成一第一铜箔基板及一第二铜箔基板,形成一第一增层叠构后的剖视图。

27.图11为在图10所示的第一增层叠构上形成一贯通孔、一第一盲孔及一第二盲孔并对贯通孔、第一及第二盲孔进行金属化及镀铜依次形成导电通孔、第一导电盲孔及第二导电盲孔后的剖视图。

28.图12为将图11所述的第一及第二铜箔基板的第一铜箔层及第二铜箔层分别制作形成一第一增层导电线路层及一第二增层导电线路层后的剖视图。

29.图13为分别在图12所示的第一及第二增层导电线路层行分别压合一第三胶层及一第四胶层后的剖视图。

30.图14为在图13所示的第三及第四胶层上分别形成一第三铜箔基板及一第四铜箔基板,形成一第二增层叠构后的剖视图。

31.图15为在图14所示的第二增层叠构上形成一第三盲孔及第四盲孔并对第三及第四盲孔进行金属化及镀铜依次形成第三导电盲孔及第四导电盲孔后的剖视图。

32.图16为将图15所示的第三及第四铜箔基板中的第三、第四铜箔层分别制作形成第三增层导电线路层及第四增层导电线路层后的剖视图。

33.图17分别在第三及第四增层导电线路层上贴合一第一覆盖膜及第二覆盖膜后的剖视图。

34.主要元件符号说明

35.36.[0037][0038]

如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

[0039]

为能进一步阐述本发明达成预定发明目的所采取的技术手段及功效,以下结合附图1-17及较佳实施方式,对本发明提供的多层电路板及其制作方法的具体实施方式、结构、特征及其功效,作出如下详细说明。显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0040]

需要说明的是,当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中设置的元件。当一个元件被认为是“设置在”另一个元件,它可以是直接设置在另一个元件上或者可能同时存在居中设置的元件。

[0041]

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的

技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

[0042]

请参阅图1,本发明提供一种多层电路板100。其中,所述多层电路板100包括一内层线路叠构体110、一第一胶层19、一第二胶层23、一第一增层电路基板302及一第二增层电路基板402。所述第一胶层19及第二胶层23分别形成在所述内层线路叠构体110的相背两表面上,所述第一增层电路基板302形成在所述第一胶层19上,所述第二增层电路基板402形成在所述第二胶层23上。

[0043]

其中,所述内层线路叠构体110包括交替堆叠在一起的至少一第一类导电线路层及至少一第二类导电线路层。所述第一类导电线路层及所述第二类导电线路层分别由具有差分蚀刻性质的第一类金属层及第二类金属层制作形成。其中,差分蚀刻性质是指:采用第一种蚀刻药水只能蚀刻第一类金属层而不蚀刻第二类金属层,采用第二种蚀刻药水只能蚀刻第二类金属层而不蚀刻第一类金属层。

[0044]

由于第一类金属层及第二类金属层之间的差分蚀刻作用,对第一类金属层和第二类金属层的蚀刻可以分别进行,如此,可以降低金属厚度对蚀刻能力的限制,使得线路的线宽与线距达标,从而所述多层电路板100满足大电流、大功率的需求。

[0045]

另外,所述内层线路叠构体110省略了核心板,从而可以降低所述多层电路板100的厚度,有利于电路板轻薄化。

[0046]

另外,由于所述内层线路叠构体110是由至少两个金属层形成的,从而所述内层线路叠构体110的厚度较一般的单层金属形成的导电线路层的厚度厚,在贯通孔51(见下文)的纵深比增加的情况下,能够降低电镀的风险,有利于提升电镀贯孔能力。

[0047]

在本实施方式中,所述第一类金属层为铜,所述第二类金属层为银。其中,金属银的导入不仅有利于信号传输,还有利于所述多层电路板100的散热。

[0048]

在本实施方式中,所述第一类导电线路层的数量与所述第二类导电线路层的数量一致,也即是说,所述内层线路叠构体110的最外侧的两个导电线路层是不同类的导电线路层。

[0049]

在本实施方式中,所述内层线路叠构体110包括两个第一类导电线路层及两个第二类导电线路层。具体地,所述内层线路叠构体110包括依次叠设在一起的一第一导电线路层17、一第二导电线路层18、一第四导电线路层22及一第三导电线路层21。所述第一导电线路层17与所述第四导电线路层22分属于第二类导电线路层,所述第二导电线路层18与所述第三导电线路层21分属于第一类导电线路层。

[0050]

在其他实施方式中,所述内层线路叠构体110还可以包括一个第一类导电线路层及一个第二类导电线路层,或者包括更多个第一类导电线路层及第二类导电线路层。

[0051]

其中,所述内层线路叠构体110还包括多条内层线路1101。由于第一种金属与第二种金属之间的差分蚀刻作用,使得相邻的两条内层线路1101的形貌呈正梯形或倒梯形或两端窄中间宽的漏斗形。其中,漏斗形是由一个正梯形与一个倒梯形构成的。相邻的两条内层线路1101之间形成有线路沟槽,部分所述第一胶层19与所述第二胶层23填充在所述线路沟槽内。

[0052]

具体地,在本实施方式中,所述第一导电线路层17上形成有多个第一线路沟槽

121,多个所述第一线路沟槽121用于形成所述第一导电线路层17的线路图案。

[0053]

具体地,在本实施方式中,所述第二导电线路层18上形成有多个第二线路沟槽111,多个所述第二线路沟槽111用于形成所述第二导电线路层18的线路图案。

[0054]

具体地,在本实施方式中,所述第三导电线路层21上形成有多个第三线路沟槽141,多个所述第三线路沟槽141用于形成所述第三导电线路层21的线路图案。

[0055]

具体地,在本实施方式中,所述第四导电线路层22上形成有多个第四线路沟槽131,多个所述第四线路沟槽131用于形成所述第四导电线路层22的线路图案。

[0056]

其中,所述第一线路沟槽121与所述第二线路沟槽111位置正对且构成所述内层线路叠构体110的第一类线路沟槽,所述第一类线路沟槽呈倒梯形。所述第三线路沟槽141与所述第四线路沟槽131位置正对且构成所述内层线路叠构体110的第二类线路沟槽,所述第二类线路沟槽呈正梯形,所述第一类线路沟槽与所述第二类线路沟槽呈两端宽中间窄的漏斗形。

[0057]

其中,所述第一胶层19形成在所述第一导电线路层17上,所述第二胶层23形成在所述第三导电线路层21上。所述第一胶层19与所述第二胶层23具有良好的流动性,且部分填充在相邻的两条内层线路1101之间的线路沟槽内。具体地,在本实施方式中,部分所述第一胶层19填充在所述第一线路沟槽121及所述第二线路沟槽111内,部分所述第二胶层23填充在所述第三线路沟槽141及所述第四线路沟槽131内。所述第一胶层19与所述第二胶层23具有良好的流动性,不仅可以满足高纵深比的填充性,提升所述多层电路板100的信赖性,还可以节省塞孔等制程。

[0058]

其中,所述第一增层电路基板302包括一第一基材层31及一第一增层导电线路层33。所述第一基材层31形成在所述第一胶层19上,所述第一增层导电线路层33形成在所述第一基材层31上。

[0059]

其中,所述第二增层电路基板402包括一第二基材层41及一第二增层导电线路层43。所述第二基材层41形成在所述第二胶层23上,所述第二增层导电线路层43形成在所述第二基材层41上。

[0060]

其中,所述第一胶层19及所述第二胶层23的流动性优于所述第一基材层31及所述第二基材层41的流动性。

[0061]

其中,所述多层电路板100还包括至少一导电通孔71、至少一第一导电盲孔72及至少一第二导电盲孔73。

[0062]

其中,所述导电通孔71电连接所述内层线路叠构体110、所述第一增层导电线路层33及所述第二增层导电线路层43。所述第一导电盲孔72电连接所述第一增层导电线路层33及所述内层线路叠构体110的所述第一导电线路层17或所述第二导电线路层18。所述第二导电盲孔73电连接所述第二增层导电线路层43及所述第三导电线路层21或所述第四导电线路层22。

[0063]

在本实施方式中,所述第一导电盲孔72电连接所述第一增层导电线路层33及所述内层线路叠构体110的所述第一导电线路层17,所述第二导电盲孔73电连接所述第二增层导电线路层43及所述第三导电线路层21。

[0064]

在本实施方式中,所述多层电路板100还包括一第三胶层81、一第四胶层82、一第三基材层34、一第四基材层44、一第三增层导电线路层36及一第四增层导电线路层46。其

中,所述第三胶层81形成在所述第一增层导电线路层33上,所述第四胶层82形成在所述第二增层导电线路层43上。所述第三基材层34形成在所述第三胶层81上,所述第四基材层44形成在所述第四胶层82上,所述第三增层导电线路层36形成在所述第三基材层34上,所述第四增层导电线路层46形成在所述第四基材层44上。

[0065]

其中,部分所述第三胶层81及所述第四胶层82填充在所述第一导电通孔71内。所述第三胶层81及所述第四胶层82具有较好的流动性,可以很轻易地填充进所述第一导电通孔71内。

[0066]

在本实施方式中,所述多层电路板100还包括至少一第三导电盲孔74及至少一第四导电盲孔75。所述第三导电盲孔74电连接所述第三增层导电线路层36及所述第一增层导电线路层33,所述第四导电盲孔75电连接所述第四增层导电线路层46及所述第二增层导电线路层43。

[0067]

其中,所述第三基材层34及所述第三增层导电线路层36构成所述多层电路板100的第三增层电路基板304,所述第四基材层44及所述第四增层导电线路层46构成所述多层电路板100的第四增层电路基板404。

[0068]

在其他实施方式中,也可以不包括第三增层电路基板304或第四增层电路基板404。

[0069]

在其他实施方式中,所述多层电路板100包括的增层电路基板的数量并不局限于2个或4个,还可以包括3个或者更多个。更多的增层电路基板可以在第三增层电路基板304或第四增层电路基板404的一侧或两侧进行增层。

[0070]

其中,所述多层电路板100还包括一第一覆盖膜91及一第二覆盖膜92。所述第一覆盖膜91及所述第二覆盖膜92分别形成在所述多层电路板100的最外侧的两个相背的增层电路基板的增层导电线路层上。在本实施方式中,所述第一覆盖膜91形成在所述第三增层导电线路层36上,所述第二覆盖膜92形成在所述第四增层导电线路层46上。

[0071]

其中,所述第一覆盖膜91上形成有至少一开口911,部分所述多层电路板100的最外侧的一个增层电路基板的增层导电线路层从所述开口911内裸露出来,形成所述多层电路板100的接触垫。在本实施方式中,部分所述第三增层导电线路层36从所述开口911内裸露出来,形成接触垫361。在所述接触垫361上还形成有一化金层3611。

[0072]

其中,所述多层电路板100还包括至少一电子元件93,所述电子元件93与所述接触垫361电连接。

[0073]

在其他实施方式中,所述开口911还可以形成在所述第二覆盖膜92上。

[0074]

请参阅图1-17,本发明还提供一种所述多层电路板100的制作方法,包括步骤:

[0075]

步骤s1,请参阅图2,提供一金属叠构体10。

[0076]

其中,所述金属叠构体10包括交替堆叠在一起的至少一第一类金属层及至少一第二类金属层。所述第一类金属层及所述第二类金属层具有差分蚀刻性质。

[0077]

在本实施方式中,所述第一类金属层的材质为铜,所述第二类金属层的材质为银。

[0078]

在本实施方式中,所述金属叠构体10包括一第一金属层11、一第二金属层12、一第三金属层13及一第四金属层14。所述第二金属层12、所述第一金属层11、所所述第三金属层13及一第四金属层14依次堆叠在一起。其中,所述第一金属层11与所述第四金属层14分属于第一类金属层,所述第二金属层12及所述第三金属层13分属于第二类金属层。

[0079]

步骤s2,请参阅图3-6,在所述金属叠构体10的一侧表面上贴合一图案化的干膜层15并在所述金属叠构体10的另一侧贴合一保护膜层16;所述干膜层15与所述保护膜层16相背;所述第二类金属层(所述第二金属层12)从所述干膜层15中裸露出来;使用第一种蚀刻药水蚀刻从所述干膜层15中裸露出来的所述第二类金属层(所述第二金属层12),以在所述第二类金属层(所述第二金属层12)上形成第一线路沟槽121,进而将所述第二类金属层(所述第二金属层12)形成第一导电线路层17;使用第二种蚀刻药水蚀刻从所述第一线路沟槽121中裸露出来的第一类金属层(所述第一金属层11),以在所述第一类金属层(所述第一金属层11)形成第二线路沟槽111,进而将所述第一类金属层(所述第一金属层11)形成第二导电线路层18;及去除所述干膜层15;所述第二导电线路层18及所述第一导电线路层17构成一内层线路叠构体110。

[0080]

其中,所述第一种蚀刻药水只能蚀刻第二金属层12(银),不蚀刻第一金属层11(铜)。

[0081]

其中,在蚀刻过程中,所述第二金属层12上被蚀刻出第一线路沟槽121,所述第一线路沟槽121用于构成所述第一导电线路层17的所述线路图案。

[0082]

在本实施方式中,所述第一线路沟槽121呈倒梯形。

[0083]

其中,所述第二种蚀刻药水只能蚀刻第一金属层11(铜),不蚀刻第二金属层12(银)。

[0084]

在本实施方式中,所述第二线路沟槽111呈倒梯形。

[0085]

步骤s3,请参阅图7,在所述第一导电线路层17上压合一第一胶层19,所述第一胶层19填充在所述第一线路沟槽121及所述第二线路沟槽111内。

[0086]

请参阅图8,在本实施方式中,还可以包括步骤s4,去除所述保护膜层16;使用所述第二种蚀刻药水蚀刻第四金属层14(第一类金属层),以形成具有所述线路图案的第三导电线路层21;使用所述第一种蚀刻药水蚀刻第三金属层13(第二类金属层),以形成具有所述线路图案的第四导电线路层22。

[0087]

其中,在蚀刻过程中,所述第四金属层14上被蚀刻出第三线路沟槽141,所述第三线路沟槽141用于构成所述第三导电线路层21的所述线路图案。所述第三金属层13上被蚀刻出第四线路沟槽131,所述第四线路沟槽131用于构成所述第四导电线路层22的所述线路图案。所述第三线路沟槽141及所述第四线路沟槽131与所述第一线路沟槽121及第二线路沟槽111位置相对。

[0088]

在本实施方式中,所述第三线路沟槽141及所述第四线路沟槽131呈正梯形。

[0089]

其中,所述第一导电线路层17、所述第二导电线路层18、所述第三导电线路层21及所述第四导电线路层22构成所述多层电路板100的内层线路叠构体110。

[0090]

请参阅图9,在本实施方式中,还可以包括步骤s5,在所述第三导电线路层21的表面上压合一第二胶层23,部分所述第二胶层23填充在所述第三线路沟槽141及所述第四线路沟槽131内。

[0091]

步骤s6,请参阅图10-12,在所述第一胶层19上形成一第一增层电路基板302,在所述第二胶层23上形成一第二增层电路基板402,并使得所述第一增层电路基板302与所述第二增层电路基板402、所述第一增层电路基板302与所述内层线路叠构体110、第二增层电路基板402与所述内层线路叠构体110分别电连接。

[0092]

其中,所述第一增层电路基板302包括一第一基材层31及一第一增层导电线路层33。所述第一基材层31形成在所述第一胶层19上,所述第一增层导电线路层33形成在所述第一基材层31上。

[0093]

其中,所述第二增层电路基板402包括一第二基材层41及一第二增层导电线路层43。所述第二基材层41形成在所述第二胶层23上,所述第二增层导电线路层43形成在所述第二基材层41上。

[0094]

具体地,步骤s6具体包括:

[0095]

步骤s61,请参阅图10,在所述第一胶层19上压合一第一铜箔基板301,在所述第二胶层23上压合一第二铜箔基板401,以形成一第一增层叠构120。

[0096]

其中,所述第一铜箔基板301包括一形成在所述第一胶层19上的第一基材层31及一形成在所述第一基材层31上的第一铜箔层32。

[0097]

其中,所述第一基材层31及所述第一铜箔层32可以依次压合在第一胶层19上,也可以作为一个整体一次压合在所述第一胶层19上。

[0098]

其中,所述第二铜箔基板401包括一形成在所述第二胶层23上的第二基材层41及一形成在所述第二基材层41上的第二铜箔层42。

[0099]

其中,所述第二基材层41及所述第二铜箔层42可以依次压合在第二胶层23上,也可以作为一个整体一次压合在所述第二胶层23上。

[0100]

步骤s62,请参阅图11,通过机械钻孔、激光等方式在所述第一增层叠构120上形成至少一贯通孔51、至少一第一盲孔52及至少一第二盲孔53,并对所述贯通孔51、所述第一盲孔52及所述第二盲孔53进行金属化并电镀,在所述贯通孔51、所述第一盲孔52及所述第二盲孔53内形成第一镀铜层61,从而形成至少一导电通孔71、至少一第一导电盲孔72及至少一第二导电盲孔73。

[0101]

其中,所述贯通孔51贯穿所述第一增层叠构120,所述第一盲孔52贯穿所述第一铜箔基板301及所述第一胶层19,所述第二盲孔53贯穿所述第二铜箔基板401及所述第二胶层23。

[0102]

在本实施方式中,所述第一镀铜层61形成在所述贯通孔51的内壁上、所述第一铜箔层32上、所述第二铜箔层42上、并填充在所述第一盲孔52及第二盲孔53内。

[0103]

在其他实施方式中,所述第一镀铜层61还可以不形成在所述第一铜箔层32及所述第二铜箔层42上。

[0104]

步骤s63,请参阅图12,通过影像转移制程将所述第一铜箔层32及所述第二铜箔层42分别制作形成第一增层导电线路层33及第二增层导电线路层43。

[0105]

其中,所述第一基材层31及所述第一增层导电线路层33构成第一增层电路基板302,所述第二基材层41及所述第二增层导电线路层43构成第二增层电路基板402。

[0106]

步骤s7,请参阅图13,在所述第一增层电路基板302上压合一第三胶层81,并在所述第二增层电路基板402上压合一第四胶层82,所述第三胶层81及所述第四胶层82填充在所述导电通孔71内。

[0107]

具体地,所述第三胶层81形成在所述第一增层导电线路层33上,所述第四胶层82形成在所述第二增层导电线路层43上。

[0108]

步骤s8,请参阅图14-16,在所述第三胶层81上形成一第三增层电路基板304,在所

述第四胶层82上形一第四增层电路基板404,并使得所述第三增层电路基板304与所述第一增层导电线路层33、所述第四增层电路基板404与所述第二增层导电线路层43分别电连接。

[0109]

其中,所述第三增层电路基板304包括一第三基材层34及一第三增层导电线路层36。所述第三基材层34形成在所述第三胶层81上,所述第三增层导电线路层36形成在所述第三基材层34上。

[0110]

其中,所述第四增层电路基板404包括一第四基材层44及一第四增层导电线路层46。所述第四基材层44形成在所述第四胶层82上,所述第四增层导电线路层46形成在所述第四基材层44上。

[0111]

具体地,步骤s8的具体包括:

[0112]

步骤s81,请参阅图14,在所述第三胶层81上压合一第三铜箔基板303,在所述第四胶层82上压合一第四铜箔基板403,以形成一第二增层叠构130。

[0113]

其中,所述第三铜箔基板303包括一形成在所述第三胶层81上的第三基材层34及一形成在所述第三基材层34上的第三铜箔层35。

[0114]

其中,所述第三基材层34及所述第三铜箔层35可以依次压合在第三胶层81上,也可以作为一个整体一次压合在所述第三胶层81上。

[0115]

其中,所述第四铜箔基板403包括一形成在所述第四胶层82上的第四基材层44及一形成在所述第四基材层44上的第四铜箔层45。

[0116]

其中,所述第四基材层44及所述第四铜箔层45可以依次压合在第四胶层82上,也可以作为一个整体一次压合在所述第四胶层82上。

[0117]

步骤s82,请参阅图15,通过机械钻孔、激光等方式在所述第二增层叠构130上形成至少一第三盲孔54及至少一第四盲孔55,并对所述第三盲孔54及所述第四盲孔55进行金属化并电镀,在所述第三盲孔54及所述第四盲孔55内形成第二镀铜层62,从而形成至少一第三导电盲孔74及至少一第四导电盲孔75。

[0118]

其中,所述第三盲孔54贯穿所述第三铜箔基板303及所述第三胶层81,所述第四盲孔55贯穿所述第四铜箔基板403及所述第四胶层82。

[0119]

在本实施方式中,所述第二镀铜层62形成在所述第三铜箔层35上、所述第四铜箔层45上、并填充在所述第三导电盲孔74及第四导电盲孔75内。

[0120]

在其他实施方式中,所述第二镀铜层62还可以不形成在所述第三铜箔层35及所述第四铜箔层45上。

[0121]

步骤s83,请参阅图16,通过影像转移制程将所述第三铜箔层35及所述第四铜箔层45分别制作形成第三增层导电线路层36及第四增层导电线路层46。

[0122]

步骤s9,在所述第三增层导电线路层36上形成一第一覆盖膜91,并在所述第四增层导电线路层46上形成一第二覆盖膜92。

[0123]

其中,所述第一覆盖膜91上形成有至少一开口911,部分所述第三增层导电线路层36从所述开口911内裸露出来,形成接触垫361。

[0124]

在其他实施方式中,所述开口911还可以形成在所述第二覆盖膜92上。

[0125]

步骤s10,请参阅图1,在所述接触垫361上形成有一化金层3611并使得至少一电子元件93与所述接触垫361电连接,形成所述多层电路板100。

[0126]

当然,在其他实施方式中,所述多层电路板100还可以包括更多的增层电路基板或

者不包括第三增层电路基板304或第四增层电路基板404。

[0127]

本发明提供的多层电路板及其制作方法,1)采用具有差分蚀刻性质的第一类金属层及第二类金属层制作内层线路叠构体110(厚铜线路),由于第一类金属层及第二类金属层之间的差分蚀刻作用,对第一类金属层和第二类金属层的蚀刻可以分别进行,如此,既能够对多层电路板大电流、大功率的需求,又能够降低蚀刻设备与蚀刻制程能力限制,使得线路的线宽与线距达标;2)采用流动性好的胶层进行增层并填充在导电通孔内,不仅可以满足高纵深比的填充性,提升所述多层电路板100的信赖性,还可以节省塞孔等制程;3)采用铜和银叠构制作内层线路叠构体110,金属银的导入不仅有利于信号传输,还有利于所述多层电路板100的散热;4)所述多层电路板100为无核心层叠构,以降低所述多层电路板100的厚度,有利于电路板轻薄化。

[0128]

以上所述,仅是本发明的较佳实施方式而已,并非对本发明任何形式上的限制,虽然本发明已是较佳实施方式揭露如上,并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施方式,但凡是未脱离本发明技术方案内容,依据本发明的技术实质对以上实施方式所做的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。