技术特征:

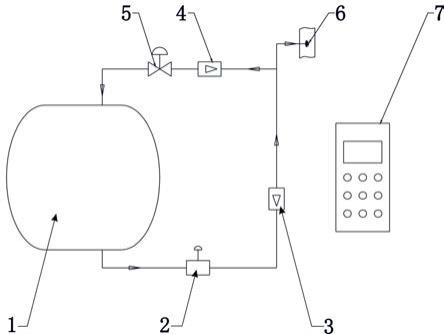

1.一种基于异步fifo芯片的处理电路,其特征在于,包括有读操作同步单元(1)、有效帧数计算单元(2)、读写地址产生单元(3)和随机存储器ram(4);所述读操作同步单元(1)连接至所述有效帧数计算单元(2),所述有效帧数计算单元(2)连接至所述读写地址产生单元(3),所述读写地址产生单元(3)连接至所述随机存储器ram(4);所述读操作同步单元(1)用于监视外部总线的读操作;所述有效帧数计算单元(2)用于计算有效帧数;所述读写地址产生单元(3)用于产生读写的地址并将数据写入所述随机存储器ram(4);所述随机存储器ram(4)用于储存数据。2.根据权利要求1所述的基于异步fifo芯片的处理电路,其特征在于,所述fifo芯片包括有写时钟模块(5)和读时钟模块(6);所述写时钟模块(5)分别与所述读操作同步单元(1)、有效帧数计算单元(2)、读写地址产生单元(3)和随机存储器ram(4)连接;所述读时钟模块(6)分别与所述读写地址产生单元(3)和随机存储器ram(4)连接。3.根据权利要求2所述的基于异步fifo芯片的处理电路,其特征在于,所述写时钟模块(5)为所述fifo芯片的系统时钟,所述读时钟模块(6)为i2c接口或spi接口的时钟。4.根据权利要求1所述的基于异步fifo芯片的处理电路,其特征在于,所述随机存储器ram(4)包括读地址端、读数据端、写地址端和写数据端;所述读地址端、写地址端和写数据端分别连接至所述读写地址产生单元(3),所述读数据端用于连接外部数据读取接口;所述读地址端用于所述读写地址产生单元(3)读取所述随机存储器ram(4)的地址;所述写地址端用于所述读写地址产生单元(3)在所述随机存储器ram(4)中写入地址;所述写数据端用于所述读写地址产生单元(3)在所述随机存储器ram(4)中写入数据。5.根据权利要求1所述的基于异步fifo芯片的处理电路,其特征在于,还包括分别连接至所述读写地址产生单元(3)和随机存储器ram(4)的模式转换单元(7),所述fifo芯片的工作模式包括fifo模式、stream模式和bypass模式,所述模式转换单元(7)用于控制所述fifo模式、stream模式和bypass模式之间相互转换。

技术总结

本实用新型请求保护一种基于异步FIFO芯片的处理电路,其包括有读操作同步单元、有效帧数计算单元、读写地址产生单元和随机存储器RAM。读操作同步单元连接至有效帧数计算单元,有效帧数计算单元连接至读写地址产生单元,读写地址产生单元连接至随机存储器RAM。本实用新型具有以下有益效果:该基于异步FIFO芯片的处理电路设计成具有不同的工作模式,适应了传感器特定的使用要求,一个是写数据侧的工作状态未知,同样地,读数据一侧因为是直接与主机通信并受软件控制,对于读数据的时间和频率也无法预测,灵活的工作模式适应了这种需求。灵活的工作模式适应了这种需求。灵活的工作模式适应了这种需求。

技术研发人员:袁本翔

受保护的技术使用者:袁本翔

技术研发日:2021.02.18

技术公布日:2021/10/8

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。