技术特征:

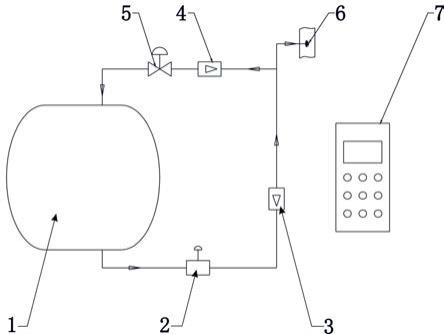

1.一种io电路,其特征在于,包括上拉单元和下拉单元,所述上拉单元包括至少两个pmos管、与所述pmos管数量相同的上拉多晶硅电阻以及第一共享总线,所述pmos管的源极均连接供电电压,所述pmos管的栅极均用于接收控制信号,所述pmos管的漏极与所述上拉多晶硅电阻的一端一一对应连接,且所述第一共享总线连接所有所述上拉多晶硅电阻的一端,所述下拉单元包括至少两个nmos管、与所述nmos管数量相同的下拉多晶硅电阻以及第二共享总线,所述nmos管的源极均接地,所述nmos管的栅极均用于接收控制信号,所述nmos管的漏极与所述下拉多晶硅电阻的一端一一对应连接,且所述第二共享总线连接所有所述下拉多晶硅电阻的一端,所述下拉多晶硅电阻的另一端均与所有所述上拉多晶硅电阻的另一端连接。2.根据权利要求1所述的io电路,其特征在于,还包括板级总线103,所述板级总线103与所有所述下拉多晶硅电阻的另一端连接。3.一种io电路控制方法,其特征在于,应用于如权利要求1至2任一项所述的io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向所有所述nmos管的栅极施加所述关断控制信号,以关断所有所述nmos管,向部分所述pmos管的栅极施加所述导通控制信号,以导通部分所述pmos管,向剩余部分所述pmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管。4.一种io电路控制方法,其特征在于,应用于如权利要求1至2任一项所述的io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向所有所述pmos管的栅极施加关断控制信号,以关断所有所述pmos管,向部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述nmos管,向剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述nmos管。5.一种io电路控制方法,其特征在于,应用于如权利要求1至2任一项所述的io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向部分所述pmos管的栅极和部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述pmos管和部分所述nmos管的栅极,向剩余部分所述pmos管的栅极和剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管和剩余部分所述nmos管。

技术总结

本发明提供了一种IO电路,包括上拉单元和下拉单元,所述上拉单元包括PMOS管、上拉多晶硅电阻以及第一共享总线,所述PMOS管的漏极与所述上拉多晶硅电阻的一端一一对应连接,且所述第一共享总线连接所有所述上拉多晶硅电阻的一端,所述下拉单元包括NMOS管、下拉多晶硅电阻以及第二共享总线,所述NMOS管的源极均接地,所述NMOS管的漏极与所述下拉多晶硅电阻的一端一一对应连接,且所述第二共享总线连接所有所述下拉多晶硅电阻的一端,所述上拉单元共享所述上拉多晶硅电阻,所述下拉单元共享所述下拉多晶硅电阻,从而降低多晶硅电阻上的电流密度,提高IO电路的可靠性。本发明还提供了IO电路的控制方法。电路的控制方法。电路的控制方法。

技术研发人员:周建冲

受保护的技术使用者:上海安路信息科技股份有限公司

技术研发日:2021.07.12

技术公布日:2021/9/17

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。