io电路及其控制方法

技术领域

1.本发明涉及fpga技术领域,尤其涉及一种io电路及其控制方法。

背景技术:

2.现场可编程门阵列(field programmable gate array,fpga)中的输入/输出(input/output),i/o)是不可获缺的重要模块,io具有输入输出功能,在输出时提供所需阻抗对应的驱动能力,作为输入时需要片内端接阻抗来缓解信号完整性问题。

3.目前高速io的输出驱动和片内端接阻抗采用复用的方式,输出时充当驱动器,输入时作为片内端接阻抗。考虑到高速io的特性和静电释放(electro

‑

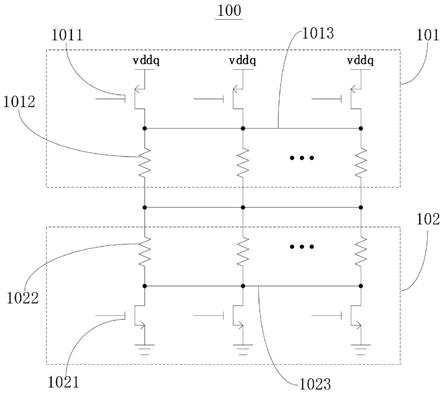

static discharge,esd)需求,一般采用mos管与多晶硅电阻相串联的方式分别实现上拉和下拉单元,传统的结构如图1所示,上拉单元由n个并联的pmos管和多晶硅电阻串联组成,下拉单元由m份并联的nmos晶体管和多晶硅电阻串联组成,其中,n和m为大于1的自然数。由于多晶硅电阻的电流承载能力相比于晶体管和互联金属走线来说弱很多,因此,往往成为电流密度限制的瓶颈,极大地影响io电路的可靠性问题。

4.因此,有必要提供一种新型的io电路及其控制方法以解决现有技术中存在的上述问题。

技术实现要素:

5.本发明的目的在于提供一种io电路及其控制方法,降低多晶硅电阻上的电流密度,提高io电路的可靠性。

6.为实现上述目的,本发明的所述io电路,包括上拉单元和下拉单元,所述上拉单元包括至少两个pmos管、与所述pmos管数量相同的上拉多晶硅电阻以及第一共享总线,所述pmos管的源极均连接供电电压,所述pmos管的栅极均用于接收控制信号,所述pmos管的漏极与所述上拉多晶硅电阻的一端一一对应连接,且所述第一共享总线连接所有所述上拉多晶硅电阻的一端,所述下拉单元包括至少两个nmos管、与所述nmos管数量相同的下拉多晶硅电阻以及第二共享总线,所述nmos管的源极均接地,所述nmos管的栅极均用于接收控制信号,所述nmos管的漏极与所述下拉多晶硅电阻的一端一一对应连接,且所述第二共享总线连接所有所述下拉多晶硅电阻的一端,所述下拉多晶硅电阻的另一端均与所有所述上拉多晶硅电阻的另一端连接。

7.所述io电路的有益效果在于:所述第一共享总线连接所有所述上拉多晶硅电阻的一端,第二共享总线连接所有所述下拉多晶硅电阻的一端,所述上拉单元共享所述上拉多晶硅电阻,所述下拉单元共享所述下拉多晶硅电阻,从而降低多晶硅电阻上的电流密度,提高io电路的可靠性。

8.优选地,所述的io电路还包括板级总线103,所述板级总线103与所有所述下拉多晶硅电阻的另一端连接。

9.本发明还提供了一种io电路控制方法,应用于所述io电路,所述控制信号包括导

通控制信号和关断控制信号,所述io电路控制方法包括向所有所述nmos管的栅极施加所述关断控制信号,以关断所有所述nmos管,向部分所述pmos管的栅极施加所述导通控制信号,以导通部分所述pmos管,向剩余部分所述pmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管。

10.所述io电路控制方法的有益效果在于:向部分所述pmos管的栅极施加所述导通控制信号,以导通部分所述pmos管,上拉单元共享所述上拉多晶硅电阻,从而降低上拉多晶硅电阻上的电流密度,提高io电路的可靠性。

11.本发明还提供了一种io电路控制方法,应用于所述io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向所有所述pmos管的栅极施加关断控制信号,以关断所有所述pmos管,向部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述nmos管,向剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述nmos管。

12.所述io电路控制方法的有益效果在于:向部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述nmos管,下拉单元共享所述下拉多晶硅电阻,从而降低下拉多晶硅电阻上的电流密度,提高io电路的可靠性。

13.本发明还提供了一种io电路控制方法,应用于所述io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向部分所述pmos管的栅极和部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述pmos管和部分所述nmos管的栅极,向剩余部分所述pmos管的栅极和剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管和剩余部分所述nmos管。

14.所述io电路控制方法的有益效果在于:向部分所述pmos管的栅极和部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述pmos管和部分所述nmos管的栅极,上拉单元共享所述上拉多晶硅电阻,下拉单元共享所述下拉多晶硅电阻,从而降低多晶硅电阻上的电流密度,提高io电路的可靠性。

附图说明

15.图1为现有技术中io电路的电路示意图;

16.图2为本发明的一些实施例中io电路的电路图;

17.图3为本发明一些实施例中io电路作为输出驱动器输出高电平信号的电流分布示意图;

18.图4为本发明一些实施例中io电路作为输出驱动器输出低电平信号的电流分布示意图;

19.图5为本发明一些实施例中io电路使用上拉单元作为片内端接电阻接收低电平信号的电流分布示意图;

20.图6为本发明一些实施例中io电路使用下拉单元作为片内端接电阻接收高电平信号的电流分布示意图;

21.图7为本发明一些实施例中io电路使用上拉单元和下拉单元作为片内端接电阻接收低电平信号的电流分布示意图;

22.图8为本发明一些实施例中io电路使用上拉单元和下拉单元作为片内端接电阻接

收高电平信号的电流分布示意图。

具体实施方式

23.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

24.针对现有技术存在的问题,本发明的实施例提供了一种io电路,应用于fpga,按照图2,io电路100包括上拉单元101和下拉单元102,所述上拉单元101包括至少两个pmos管1011、与所述pmos管1011数量相同的上拉多晶硅电阻1012以及第一共享总线1013,所述pmos管1011的源极均连接供电电压vddq,所述pmos管1011的栅极均用于接收控制信号,所述pmos管1011的漏极与所述上拉多晶硅电阻1012的一端一一对应连接,且所述第一共享总线1013连接所有所述上拉多晶硅电阻1012的一端,所述下拉单元102包括至少两个nmos管1021、与所述nmos管1021数量相同的下拉多晶硅电阻1022以及第二共享总线1023,所述nmos管1021的源极均接地,所述nmos管1021的栅极均用于接收控制信号,所述nmos管1021的漏极与所述下拉多晶硅电阻1022的一端一一对应连接,且所述第二共享总线1023连接所有所述下拉多晶硅电阻1022的一端,所述下拉多晶硅电阻1022的另一端均与所有所述上拉多晶硅电阻1012的另一端连接。

25.一些实施例中,所述的io电路100还包括板级总线103,所述板级总线103与所有所述下拉多晶硅电阻1022的另一端连接。

26.图3为本发明一些实施例中io电路作为输出驱动器输出高电平信号的电流分布示意图。图4为本发明一些实施例中io电路作为输出驱动器输出低电平信号的电流分布示意图。图5为本发明一些实施例中io电路使用上拉单元作为片内端接电阻接收低电平信号的电流分布示意图。图6为本发明一些实施例中io电路使用下拉单元作为片内端接电阻接收高电平信号的电流分布示意图。图7为本发明一些实施例中io电路使用上拉单元和下拉单元作为片内端接电阻接收低电平信号的电流分布示意图。图8为本发明一些实施例中io电路使用上拉单元和下拉单元作为片内端接电阻接收高电平信号的电流分布示意图。参照图2~图8,图3~图8与图2的区别点包括:所述上拉单元101包括三个所述pmos管1011和三个所述上拉多晶硅电阻1012,三个所述pmos管1011分别为第一pmos管10111、第二pmos管10112和第三pmos管10113,三个所述上拉多晶硅电阻1012分别为第一上拉多晶硅电阻10121、第二上拉多晶硅电阻10122和第三上拉多晶硅电阻10123,所述下拉单元102包括三个所述nmos管1021和三个所述下拉多晶硅电阻1022,三个所述nmos管1021分别为第一nmos管10211、第二nmos管10212和第三nmos管10213,三个所述下拉多晶硅电阻1022分别为第一下拉多晶硅电阻10221、第二下拉多晶硅电阻10222和第三下拉多晶硅电阻10223,所述第一上拉多晶硅电阻10121的另一端、所述第二上拉多晶硅电阻10122的另一端、所述第三上拉多晶硅电阻10123的另一端、所述第一下拉多晶硅电阻10221的另一端、所述第二下拉多晶

硅电阻10222的另一端和所述第三下拉多晶硅电阻10223的另一端均与第三共享总线104连接,所述第三共享总线104的一端与所述板级总线103的一端连接。

27.参照图3~图8,所述第一共享总线1013与所述第一pmos管10111的漏端和所述第一上拉多晶硅电阻10121的一端连接于第一焊点10131,所述第一共享总线1013与所述第二pmos管10112的漏端和所述第二上拉多晶硅电阻10122的一端连接于第二焊点10132,所述第一共享总线1013与所述第三pmos管10113的漏端和所述第三上拉多晶硅电阻10123的一端连接于第三焊点10133。

28.参照图3~图8,所述第二共享总线1023与所述第一nmos管10211的漏端和所述第一下拉多晶硅电阻10221的一端连接于第四焊点10231,所述第一共享总线1013与所述第二nmos管10212的漏端和所述第二下拉多晶硅电阻10222的一端连接于第五焊点10232,所述第二共享总线1023与所述第三nmos管10213的漏端和所述第三下拉多晶硅电阻10223的一端连接于第六焊点10233。

29.参照图3~图8,所述第一上拉多晶硅电阻10121的另一端和所述第一下拉多晶硅电阻10221的另一端连接于所述第三共享总线104的第七焊点1041,所述第二上拉多晶硅电阻10122的另一端和所述第二下拉多晶硅电阻10222的另一端连接于所述第三共享总线104的第八焊点1042,所述第三上拉多晶硅电阻10123的另一端和所述第三下拉多晶硅电阻10223的另一端连接于所述第三共享总线104的第九焊点1043。

30.本发明提供了一种io电路控制方法,应用于所述io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向所有所述nmos管的栅极施加所述关断控制信号,以关断所有所述nmos管,向部分所述pmos管的栅极施加所述导通控制信号,以导通部分所述pmos管,向剩余部分所述pmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管。

31.参照图3,所述板级总线103的另一端与电阻r

term

的一端连接,在所述io电路应用于内存规格为ddr3的电路时,电阻r

term

的另一端接0.5倍的供电电压vddq,在所述io电路应用于低功耗双倍数据率同步动态随机存储器(low power double data rate synchronous dynamic random access memory,lpddr sdram)时,电阻r

term

的另一端接地gnd。

32.参照图3,所述io电路控制方法包括向所述第一pmos管10111的栅极和所述第二pmos管10112的栅极施加导通控制信号,以导通所述第一pmos管10111和所述第二pmos管10112,同时向所述第三pmos管10113、所述第一nmos管10211、所述第二nmos管10212和所述第三nmos管10213的栅极施加关断控制信号,以关断所述第三pmos管10113、所述第一nmos管10211、所述第二nmos管10212和所述第三nmos管10213。所述第一pmos管10111上的电流i1的大小为3个单位,经过所述第一共享总线1013的分流,所述第一焊点10131流向所述第二焊点10132的电流i3的大小为1个单位,则所述第一上拉多晶硅电阻10121上的电流i5的大小为2个单位,则所述第七焊点1041流向所述第八焊点1042的电流i8的大小为2个单位,所述第二pmos管10112上的电流i2的大小为3个单位,经过所述第一共享总线1013的分流,所述第二焊点10132流向所述第三焊点10133的电流i4的大小为2个单位,则所述第二焊点10132剩余1个单位的电流流向所述第二上拉多晶硅电阻10122,则所述第二上拉多晶硅电阻10122上的电流i6的大小为2个单位,所述第三上拉多晶硅电阻10123上的电流i7的大小为2个单位,所述第八焊点1042流向所述第九焊点1043的电流i9的大小为4个单位,所述第

九焊点1043流向所述板级总线103的电流i10的大小为6个单位,即io电路充当输出驱动器流出的电流大小为6个单位。

33.参照图1和图3,采用图1的电路,为了保持和图3相同的信号幅度,则图1中pmos管开启的数量为2~3个,流经每个多晶硅电阻的电流为2~3个单位,明显大于图3中流经所述第一上拉多晶硅电阻10121、所述第二上拉多晶硅电阻10122和所述第三上拉多晶硅电阻10123的2个单位的电流,本技术缓解了上拉多晶硅电阻电流密度的压力。

34.参照图5,当所述io电路应用于内存规格为ddr4的电路时,通过输出阻抗为r

out

的驱动器向对端do发送低电平。

35.参照图5,所述io电路控制方法包括向所述第一pmos管10111的栅极和所述第二pmos管10112的栅极施加导通控制信号,以导通所述第一pmos管10111和所述第二pmos管10112,同时向所述第三pmos管10113、所述第一nmos管10211、所述第二nmos管10212和所述第三nmos管10213的栅极施加关断控制信号,以关断所述第三pmos管10113、所述第一nmos管10211、所述第二nmos管10212和所述第三nmos管10213。所述第一pmos管10111上的电流i1的大小为3个单位,经过所述第一共享总线1013的分流,所述第一焊点10131流向所述第二焊点10132的电流i3的大小为1个单位,则所述第一上拉多晶硅电阻10121上的电流i5的大小为2个单位,则所述第七焊点1041流向所述第八焊点1042的电流i8的大小为2个单位,所述第二pmos管10112上的电流i2的大小为3个单位,经过所述第一共享总线1013的分流,所述第二焊点10132流向所述第三焊点10133的电流i4的大小为2个单位,则所述第二焊点10132剩余1个单位的电流流向所述第二上拉多晶硅电阻10122,则所述第二上拉多晶硅电阻10122上的电流i6的大小为2个单位,所述第三上拉多晶硅电阻10123上的电流i7的大小为2个单位,所述第八焊点1042流向所述第九焊点1043的电流i9的大小为4个单位,所述第九焊点1043流向所述板级总线103的电流i10的大小为6个单位,即io电路充当片内端接电阻流出的电流大小为6个单位。

36.参照图1和图5,采用图1的电路,为了保持和图5相同的信号幅度,则图1中pmos管开启的数量为2~3个,流经每个多晶硅电阻的电流为2~3个单位,明显大于图5中流经所述第一上拉多晶硅电阻10121、所述第二上拉多晶硅电阻10122和所述第三上拉多晶硅电阻10123的2个单位的电流,本技术缓解了上拉多晶硅电阻电流密度的压力。

37.本发明还提供了另一种io电路控制方法,应用于所述io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向所有所述pmos管的栅极施加关断控制信号,以关断所有所述pmos管,向部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述nmos管,向剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述nmos管。

38.参照图4,所述板级总线103的另一端与电阻r

term

的一端连接,在所述io电路应用于内存规格为ddr3的电路时,电阻r

term

的另一端接0.5倍的供电电压vddq,在所述io电路应用于内存规格为ddr4的电路时,电阻r

term

的另一端接供电电压vddq。

39.参照图4,所述io电路控制方法包括向所述第一nmos管10211和所述第二nmos管10212的栅极施加导通控制信号,以导通所述第一nmos管10211和所述第二nmos管10212,同时向所述第一pmos管10111、所述第二pmos管10112、所述第三pmos管10113和所述第三nmos管10213的栅极施加关断控制信号,以关断所述第一pmos管10111、所述第二pmos管10112、

所述第三pmos管10113和所述第三nmos管10213。所述第一nmos管10211上的电流i11的大小为3个单位,所述第二nmos管10212上的电流i12的大小为3个单位,所述第一下拉多晶硅电阻10221上的电流i15的大小为2个单位,所述第五焊点10232流向所述第四焊点10231的电流i13大小为1个单位,所述第二下拉多晶硅电阻10222上的电流i16的大小为2个单位,所述第三下拉多晶硅电阻10223上的电流i17的大小为2个单位,所述第六焊点10233流向所述第五焊点10232的电流i14的大小为2个单位,所述第八焊点1042流向所述第七焊点1041的电流i18的大小为2个单位,所述第九焊点1043流向所述第八焊点1042的电流i19的大小为个4单位,所述板级总线103流向所述第九焊点1043的电流i20的大小为个6单位,即io电路充当输出驱动器流入的电流大小为6个单位。

40.参照图1和图4,采用图1的电路,为了保持和图4相同的信号幅度,则图1中nmos管开启的数量为2~3个,流经每个多晶硅电阻的电流为2~3个单位,明显大于图4中流经所述第一下拉多晶硅电阻10221、所述第二下拉多晶硅电阻10222和所述第三下拉多晶硅电阻10223的2个单位的电流,本技术缓解了下拉多晶硅电阻电流密度的压力。

41.参照图6,当所述io电路应用于lpddr sdram的电路时,通过输出阻抗为r

out

的驱动器向对端do发送高电平。

42.参照图1和图6,所述io电路控制方法包括向所述第一nmos管10211和所述第二nmos管10212的栅极施加导通控制信号,以导通所述第一nmos管10211和所述第二nmos管10212,同时向所述第一pmos管10111、所述第二pmos管10112、所述第三pmos管10113和所述第三nmos管10213的栅极施加关断控制信号,以关断所述第一pmos管10111、所述第二pmos管10112、所述第三pmos管10113和所述第三nmos管10213。所述第一nmos管10211上的电流i11的大小为3个单位,所述第二nmos管10212上的电流i12的大小为3个单位,所述第一下拉多晶硅电阻10221上的电流i15的大小为2个单位,所述第五焊点10232流向所述第四焊点10231的电流i13大小为1个单位,所述第二下拉多晶硅电阻10222上的电流i16的大小为2个单位,所述第三下拉多晶硅电阻10223上的电流i17的大小为2个单位,所述第六焊点10233流向所述第五焊点10232的电流i14的大小为2个单位,所述第八焊点1042流向所述第七焊点1041的电流i18的大小为2个单位,所述第九焊点1043流向所述第八焊点1042的电流i19的大小为个4单位,所述板级总线103流向所述第九焊点1043的电流i20的大小为个6单位,即io电路充当片内端接电阻流入的电流大小为6个单位。

43.参照图1和图6,采用图1的电路,为了保持和图6相同的信号幅度,则图1中nmos管开启的数量为2~3个,流经每个多晶硅电阻的电流为2~3个单位,明显大于图6中流经所述第一下拉多晶硅电阻10221、所述第二下拉多晶硅电阻10222和所述第三下拉多晶硅电阻10223的2个单位的电流,本技术缓解了下拉多晶硅电阻电流密度的压力。

44.本发明还提供了又一种io电路控制方法,应用于所述io电路,所述控制信号包括导通控制信号和关断控制信号,所述io电路控制方法包括向部分所述pmos管的栅极和部分所述nmos管的栅极施加所述导通控制信号,以导通部分所述pmos管和部分所述nmos管的栅极,向剩余部分所述pmos管的栅极和剩余部分所述nmos管的栅极施加所述关断控制信号,以关断剩余部分所述pmos管和剩余部分所述nmos管。

45.参照图7,当所述io电路应用于内存规格为ddr3的电路时,通过输出阻抗为r

out

的驱动器向对端do发送低电平。

46.参照图8,当所述io电路应用于内存规格为ddr3的电路时,通过输出阻抗为r

out

的驱动器向对端do发送高电平。

47.参照图7和图8,所述io电路控制方法包括向所述第一pmos管10111、所述第二pmos管10112、所述第一nmos管10211和所述第二nmos管10212的栅极施加导通控制信号,以导通所述第一pmos管10111、所述第二pmos管10112、所述第一nmos管10211和所述第二nmos管10212,同时向所述第三pmos管10113和所述第三nmos管10213的栅极施加关断控制信号,以关断所述第三pmos管10113和所述第三nmos管10213。

48.参照图7,所述第一pmos管10111上的电流i1的大小为6个单位,经过所述第一共享总线1013的分流,所述第一焊点10131流向所述第二焊点10132的电流i3的大小为2个单位,则所述第一上拉多晶硅电阻10121上的电流i5的大小为4个单位,所述第二pmos管10112上的电流i2的大小为6个单位,经过所述第一共享总线1013的分流,所述第二焊点10132流向所述第三焊点10133的电流i4的大小为4个单位,则所述第二焊点10132剩余2个单位的电流流向所述第二上拉多晶硅电阻10122,则所述第二上拉多晶硅电阻10122上的电流i6的大小为4个单位,所述第三上拉多晶硅电阻10123上的电流i7的大小为4个单位,所述第一nmos管10211上的电流i11的大小为3个单位,所述第二nmos管10212上的电流i12的大小为3个单位,所述第一下拉多晶硅电阻10221上的电流i15的大小为2个单位,所述第五焊点10232流向所述第四焊点10231的电流i13大小为1个单位,所述第二下拉多晶硅电阻10222上的电流i16的大小为2个单位,所述第三下拉多晶硅电阻10223上的电流i17的大小为2个单位,所述第六焊点10233流向所述第五焊点10232的电流i14的大小为2个单位,所述第七焊点1041流向所述第八焊点1042的电流i8的大小为2个单位,所述第八焊点1042流向所述第九焊点1043的电流i9的大小为4个单位,所述第九焊点1043流向所述板级总线103的电流i10的大小为6个单位,即所述io电路充当片内端接电阻流出的电流大小为6个单位。

49.参照图1和图7,采用图1的电路,为了保持和图7相同的信号幅度,则图1中nmos管和pmos管开启的数量为2~3个,流经上拉单元中多晶硅电阻的电流为4~6个单位,明显大于图7中流经所述第一上拉多晶硅电阻10121、所述第二上拉多晶硅电阻10122和所述第三上拉多晶硅电阻10123的4个单位的电流,流经下拉单元中多晶硅电阻的电流为2~3个单位,明显大于图7中流经所述第一下拉多晶硅电阻10221、所述第二下拉多晶硅电阻10222和所述第三下拉多晶硅电阻10223的2个单位的电流,本技术缓解了上拉多晶硅电阻和下拉多晶硅电阻电流密度的压力。

50.参照图8,所述第一pmos管10111上的电流i1的大小为3个单位,经过所述第一共享总线1013的分流,所述第一焊点10131流向所述第二焊点10132的电流i3的大小为1个单位,则所述第一上拉多晶硅电阻10121上的电流i5的大小为2个单位,所述第二pmos管10112上的电流i2的大小为3个单位,经过所述第一共享总线1013的分流,所述第二焊点10132流向所述第三焊点10133的电流i4的大小为2个单位,则所述第二焊点10132剩余1个单位的电流流向所述第二上拉多晶硅电阻10122,则所述第二上拉多晶硅电阻10122上的电流i6的大小为2个单位,所述第三上拉多晶硅电阻10123上的电流i7的大小为2个单位,所述第一nmos管10211上的电流i11的大小为6个单位,所述第二nmos管10212上的电流i12的大小为6个单位,所述第一下拉多晶硅电阻10221上的电流i15的大小为4个单位,所述第五焊点10232流向所述第四焊点10231的电流i13大小为2个单位,所述第二下拉多晶硅电阻10222上的电流

i16的大小为4个单位,所述第三下拉多晶硅电阻10223上的电流i17的大小为4个单位,所述第六焊点10233流向所述第五焊点10232的电流i14的大小为4个单位,所述第八焊点1042流向所述第七焊点1041的电流i8的大小为2个单位,所述第九焊点1043流向所述第八焊点1042的电流i9的大小为4个单位,所述板级总线103流向所述第九焊点1043的电流i10的大小为6个单位,即所述io电路充当片内端接电阻流入的电流大小为6个单位。

51.参照图1和图8,采用图1的电路,为了保持和图8相同的信号幅度,则图1中nmos管和pmos管开启的数量为2~3个,流经上拉单元中多晶硅电阻的电流为2~3个单位,明显大于图7中流经所述第一上拉多晶硅电阻10121、所述第二上拉多晶硅电阻10122和所述第三上拉多晶硅电阻10123的2个单位的电流,流经下拉单元中多晶硅电阻的电流为4~6个单位,明显大于图8中流经所述第一下拉多晶硅电阻10221、所述第二下拉多晶硅电阻10222和所述第三下拉多晶硅电阻10223的4个单位的电流,本技术缓解了上拉多晶硅电阻和下拉多晶硅电阻电流密度的压力。

52.本发明的一些实施例中,所述导通控制信号为高电平信号,所述关断控制信号为低电平信号。

53.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。