1.本发明属于电子电路技术领域,具体涉及一种快速响应无外接电容型线性稳压器。

背景技术:

2.线性稳压器(ldo)以其工作电压低、输出噪声低、体积小以及应用简单的特点,被广泛地应用到电子产品中。传统的ldo都需要在输出端外接大电容以保证ldo在电路系统中正常工作。随着片上系统(soc)的发展,要求尽可能地减少外围电路,越来越多的模块被纳入芯片内部。对于soc而言,系统中的ldo如果在片内集成电容,会大幅增加芯片面积;如果采用片外电容,则需要增加芯片的引脚,浪费整体soc模块的封装面积。而且,一个soc系统通常具有多个电源域的多种电路模块,且线宽低于40nm的小尺寸数字模块所需的供电电压不应太高。所以,无论从soc的应用成本还是从ldo自身可靠性而言,设计一种无外接电容型(capless)ldo电路已成为当今ldo设计领域的热点技术。但是传统的无外接电容型ldo面临着稳定性差、静态功耗大和瞬态特性不足等多重压力,严重影响电路系统性能。

技术实现要素:

3.针对上述传统无外接电容型ldo在静态功耗和瞬态特性等方面存在的问题,本发明提出了一种应用于片内soc系统的低功耗无外接电容型ldo电路。

4.本发明的技术方案为:

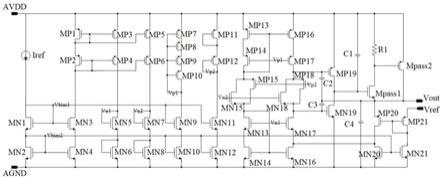

5.一种快速响应无外接电容型线性稳压器,包括偏置电路、输出电流调整环路、功率级和输出电压确定环路。

6.所述偏置电路包括第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5、第六nmos管mn6、第七nmos管mn7、第八nmos管mn8、第九nmos管mn9、第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12、第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10、第十一pmos管mp11、第十二pmos管mp12和第一偏置电流iref;

7.第一偏置电流iref流入端接电源(avdd),流出端接第一nmos管mn1的漏极;

8.第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第九nmos管mn9、第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12构成共源共栅nmos电流镜,第一nmos管mn1、第三nmos管mn3、第九nmos管mn9、第十一nmos管mn11栅极共同接到第一nmos管mn1的漏极,第一nmos管mn1的源极与第二nmos管mn2的漏极相连,第三nmos管mn3其源极与第四nmos管mn4的漏极相连,其漏极与第二pmos管mp2的漏极相连,第九nmos管mn9其源极与第十nmos管mn10的漏极相连,其漏极与第十pmos管漏极相连,第十一nmos管mn11其源极与第十二nmos管mn12的漏极相连,其漏极与第十二pmos管mp12的漏极相连,第二nmos管mn2、第四nmos管mn4、第十nmos管mn10、第十二nmos管mn12栅极共同接到第二nmos管mn2的

漏极,第二nmos管mn2、第四nmos管mn4、第十nmos管mn10、第十二nmos管mn12源极共同接地(agnd);

9.第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6共同构成共源共栅pmos电流镜,第一pmos管mp1、第三pmos管mp3、第五pmos管mp5栅极共同接到第一pmos管mp1的漏极,源极共同接到电源(avdd),第二pmos管mp2、第四pmos管mp4、第六pmos管mp6栅极共同接到第二pmos管mp2的漏极,第二pmos管mp2的源极与第一pmos管mp1的漏极相连,第四pmos管mp4其源极与第三pmos管mp3的漏极相连,其漏极与第五nmos管mn5的漏极相连,第六pmos管mp6其源极与第五pmos管mp5的漏极相连,其漏极与第七nmos管mn7的漏极相连;

10.第五nmos管mn5、第六nmos管mn6采用二极管连接形式,其中第五nmos管mn5的栅漏电压作第一偏置电压vn1,第六nmos管mn6其漏极与第五nmos管mn5的源极相连,其源极接到地(agnd);

11.第七nmos管mn7、第八nmos管mn8采用二极管连接形式,其中第七nmos管mn7的栅漏电压作第二偏置电压vn2,第八nmos管mn8其漏极与第七nmos管mn7的源极相连,其源极接到地(agnd);

12.第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10其栅极共同接到第十pmos管mp10的漏极,第七pmos管mp7其源极接到电源(avdd),其漏极与第八pmos管mp8的源极相连,第九pmos管mp9其源极与第八pmos管mp8的漏极相连,其漏极与第十pmos管mp10的源极相连,第十pmos管mp10的栅漏电压作第三偏置电压vp1;

13.第十一pmos管mp11、第十二pmos管mp12采用二极管连接形式,其中第十一pmos管mp11其源极接到电源(avdd),其漏极与第十二pmos管mp12的源极相连,第十二pmos管mp12的栅漏电压作第四偏置电压vp2;

14.所述输出电流调整环路包括第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15、第十六nmos管mn16、第十七nmos管mn17、第十八nmos管mn18、第十九nmos管mn19、第二十nmos管mn20、第十三pmos管mp13、第十四pmos管mp14、第十五pmos管mp15、第十六pmos管mp16、第十七pmos管mp17、第十八pmos管mp18、第十九pmos管mp19、第二十pmos管mp20、第二电容c2、第三电容c3、第四电容c4;

15.第十三nmos管mn13、第十四nmos管mn14、第十六nmos管mn16、第十七nmos管mn17构成共源共栅nmos电流镜,第十四nmos管mn14和第十六nmos管mn16的源极均接地(agnd),其栅极共同接到第十三nmos管mn13的漏极,第十三nmos管mn13的源极和第十四nmos管mn14的漏极相连,第十七nmos管mn17的源极和第十六nmos管mn16的漏极相连,第十三nmos管mn13和第十七nmos管mn17的栅极共同接到第一偏置电压vn1;

16.第十三pmos管mp13、第十四pmos管mp14、第十六pmos管mp16、第十七pmos管mp17构成共源共栅pmos电流镜,第十三pmos管mp13和第十六pmos管mp16的源极都接到电源(avdd),其栅级共同接到第十四pmos管mp14的漏极,第十四pmos管mp14的源极和第十三pmos管mp13的漏极相连,第十七pmos管mp17的源极和第十六pmos管mp16的漏极相连,第十四pmos管mp14和第十七pmos管mp17的栅极共同接到第三偏置电压vp1;

17.第十五nmos管mn15和第十五pmos管mp15构成浮动电流源,第十五nmos管mn15的源极和第十五pmos管mp15的漏极相连,共同连接到第十三nmos管mn13的漏极,第十五nmos管

mn15的漏极和第十五pmos管mp15的源极相连,共同连接到第十四pmos管mp14的漏极,第十五nmos管mn15的栅极接第二偏置电压vn2,第十五pmos管mp15接第四偏置电压vp2;

18.第十八nmos管mn18和第十八pmos管mp18构成浮动电压源,第十八nmos管mn18的源极和第十八pmos管mp18的漏极相连,共同连接到第十七nmos管mn17的漏极,第十八nmos管mn18的漏极和第十八pmos管mp18的源极相连,共同连接到第十七pmos管mp75的漏极,第十八nmos管mn18的栅极接第二偏置电压vn2,第十八pmos管mp18接第四偏置电压vp2;

19.第十九nmos管mn19和第十九pmos管mp19构成class

‑

ab输出级,第十九nmos管mn19的源极接地,其栅极接第十七nmos管mn17的漏极,第十九pmos管mp19的源极接电源,其栅极接第五pmos管mp15的漏极,第十九nmos管mn19的漏极和第十九pmos管mp19的漏极相连,共同接到第一nmos功率管mpass1的栅极;

20.第二电容c2接在输出端(vout)和第十九pmos管mp19的栅极之间,第三电容c3接在输出端(vout)和第十九nmos管mn19的栅极之间。第四电容c4接在输出端(vout)和地(agnd)之间;

21.所述功率级包括第一nmos功率管mpass1、第一pmos功率管mpass2、第一电容c1、第一电阻r1;

22.第一电容c1接在第一nmos功率管mpass1的栅极和电源(avdd)之间,第一电阻r1一段接到电源(avdd),另一端与第一nmos功率管mpass1的漏极相连,共同接到第一pmos功率管mpass2的栅极,第一pmos功率管mpass2其源极接到电源(avdd),其漏极与第一nmos功率管的源极相连,共同接到输出端(vout);

23.所述输出电压确定环路由第二十nmos管mn20、第二十一nmos管mn21、第二十pmos管mp20、第二十一pmos管mp21和参考电压vref组成,第二十nmos管mn20和第二十一nmos管mn21的源极均接地,其栅极连在一起共同接到第二nmos管mn2的栅极,第二十pmos管mp20和第二十一pmos管mp21的栅连在一起共同接到第二十一pmos管mp21的漏极,第二十pmos管mp20的源极接输出端(vout),其漏极和第二十nmos管mn20相连,并共同接到第十七nmos管mn17的源极,第二十一pmos管mp21的漏极和第二十一nmos管mn21的漏极相连,其源极接参考电压vref。

24.本发明的有益效果为:本发明的电路采用nmos与pmos管共同作输出调整管的双功率管结构,有效地提高了功率级的跨导和电源抑制比,同时降低输出阻抗,对瞬态响应的欠冲和过冲具有抑制作用;具有双环路控制的fvf电路架构,将输出电压确定环路和输出电流调整环路分开,在保证低静态功耗和高瞬态响应特性的同时,提高输出电压的精度;输出电流调整环路具有含线性跨导环的共源共栅中间级和class

‑

ab输出级,增大环路增益,在保证功率管具有大范围栅极电压调节能力的同时提高了其栅极电容的充放电速率,改善了电路的稳定性和瞬态响应特性。

附图说明

25.图1所示为本发明提出的一种无电容型线性稳压器在实施例中的电路结构示意图。

26.图2所示为本发明提出的一种无电容型线性稳压器的瞬态响应特性示意图。

27.图3所示为本发明提出的一种无电容型线性稳压器在pvt下负载电流为100μa的功

耗示意图。

28.图4所示为本发明提出的一种无电容型线性稳压器在负载电流为100μa时的电源抑制比psrr示意图。

具体实施方式

29.下面结合附图,对本发明技术方案进行详细描述:

30.本发明提出的一种无外接电容型线性稳压器,包括偏置电路、输出电流调整环路、功率级、输出电压确定环路和补偿电路。其中,偏置电路用于提供输出电压调整环路所需的第一偏置电压vn1、第二偏置电压vn2、第三偏置电压vp1、第四偏置电压vp2、第一偏置电流iref。如图1所示给出了偏置电路的一种实现形式,包括第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5、第六nmos管mn6、第七nmos管mn7、第八nmos管mn8、第九nmos管mn9、第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12、第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10、第十一pmos管mp11、第十二pmos管mp12;其中,第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第九nmos管mn9、第十nmos管mn10、第十一nmos管mn11、第十二nmos管mn12构成共源共栅nmos电流镜,用于精确复制第一偏置电流iref;第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6构成共源共栅pmos电流镜,用于精确复制第一偏置电流iref,提供给偏置电路中的其他支路;通过镜像基准电流iref作用于第五nmos管mn5和第六nmos管mn6、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9和第十pmos管mp10分别产生第一偏置电压vn1和第三偏置电压vp1,为输出电流调整环路的共源共栅对管提供栅极偏置电压。

31.第七nmos管mn7、第八nmos管mn8、第十一pmos管mp11、第十二pmos管mp12、第十五nmos管mn15、第十五pmos管mp15构成浮动电流镜;通过调整上述mos管的宽长比,使得第十五nmos管mn15和第七nmos管mn7的源极电位相等,第十五pmos管mp15和第十二pmos管mp12的源极电位也相等,并且由于上述两对mos管的栅极分别相连,在忽略沟道长度调制效应的情况下,可以实现较为精确的电流镜像,从而确定输出电流调整环路的静态工作电流。

32.本发明中提出的输出电流调整环路由电压采样电路、共源共栅中间级、class

‑

ab输出级共同构成。电压采样电路由第二十pmos管mp20和第二十nmos管mn20组成,用于采样输出电压信号的变化;其工作机理是,当输出电压发生变化时,由于第二十pmos管mp20采用了共基极的接法,使得其源极处产生的交流小信号在其漏极产生同相放大的交流小信号,实现对输出电压的采样;共源共栅中间级由第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15、第十六nmos管mn16、第十七nmos管mn17、第十八nmos管mn18、第十三pmos管mp13、第十四pmos管mp14、第十五pmos管mp15、第十六pmos管mp16、第十七pmos管mp17、第十八pmos管mp18组成,由于浮动电压源的低交流阻抗和第十七nmos管mn17的共基极接法,导致从第十七nmos管mn17源极输入的采样信号能够在浮动电压源的两侧均产生同相放大的信号,并作用于后级class

‑

ab输出级的输入端,同时,采用共源共栅中间级能大幅提高电路的环路增益,进而提高ldo的线性调整率和负载调整率;class

‑

ab输出级由第十九nmos管mn19和第十九pmos管mp19组成,用于产生第一nmos功率管mpass1的栅极信号来调整输出电

流的大小,class

‑

ab结构特有的高瞬态摆率优势有利于实现功率管栅极电容的快速充放电,提高了环路的瞬态特性;接在共源共栅中间级和class

‑

ab输出级之间的第二电容c2和电容c3采用密勒补偿的方式保证输出电流调整环路的稳定性;第四电容c4用于抑制输出电压的欠冲和过冲,提高电路瞬态响应特性。

33.所述功率级由第一nmos功率管mpass1、第一pmos功率管mpass2、第一电容c1、第一电阻r1组成;第一nmos功率管mpass1、第一pmos功率管mpass2的基本作用是根据负载情况调节输入电源和输出电压之间的阻抗,其中只有在大负载电流下mpass2才开启以提高功率管的跨导;电容c3的作用是在负载电流发生瞬态跳变的时候稳定nmos管的栅极电压,借由source

‑

follower接法nmos管自身的源级电压反馈特性稳定输出电压,同时进行环路稳定性补偿;电阻r3的作用是为mpass2提供栅极偏置,决定了mpass2开启时的负载电流阈值。

34.所述输出电压确定环路由第二十nmos管mn20、第二十一nmos管mn21、第二十pmos管mp20、第二十一pmos管mp21和参考电压vref组成。其工作原理是,通过设置第二十nmos管mn20和第二十一nmos管mn21、第二十pmos管mp20和第二十一pmos管mp21两组电流镜具有相同的宽长比,可以使得流过两条支路的电流呈一定的比例,那么,当第二十一pmos管mp21的源极电位确定之后,为了保证两条支路的电流保持一定的比例,第二十pmos管mp20的源极电位必将和第二十一pmos管mp21的源极电位相等,由此确定了输出电压大小。值得注意的是,如图1所示,本实例中的输入参考电压vref需要具备一定的电流输出能力,为第二十一pmos管mp21和第二十一nmos管mn21供电,可以采用基准电压和buffer电路的组合实现。

35.图2是本发明提出的一种快速响应无电容型线性稳压器的瞬态响应特性示意图,在3.3v直流工作电压下,负载电流在200μa和20ma之间以1ns的时间进行切换,输出直流电压为1.2v时,输出电压的最大欠冲为113.8mv,即1.2v输出电压的9.48%;最大过冲为87.3mv,即1.2v输出电压的7.28%;恢复为稳定输出电压(1.2v

±

1%)所需时间小于2μs,从中可以看出电路具有优异的瞬态特性。

36.图3是本发明提出的一种快速响应无电容型线性稳压器在pvt下负载电流为100μa的功耗示意图(包含100μa的负载电流),从图中可以看出电路最大静态功耗小于6.2μa,满足低功耗应用场景。

37.图4是本发明提出的一种快速响应无电容型线性稳压器在负载电流为100μa时的电源抑制比psrr示意图,从图中可以看出电路在低频时电源抑制比达到59db,频率为1khz时电源抑制比为51db,体现出良好的电源抑制比特性。

38.本发明中的电路,所有nmos管的衬底均接地(agnd),所有pmos管的衬底均接电源电压(avdd)。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。