1.本发明涉及一种显示装置,且特别是涉及一种具有提升的可靠度的显示装置。

背景技术:

2.在显示器产品的设计中,窄边框已成趋势,可在相同分辨率下,将画面可视范围极大化,且在拼接成大尺寸面板时,可减小边框的视觉干扰。

3.然而,由于窄边框的设计,在基板对组(例如元件阵列基板与滤光基板对组)的过程中,液晶会接触到框胶而发生污染或穿刺等状况,造成显示器产品出现漏光的现象,导致显示器产品的可靠度不佳。

技术实现要素:

4.本发明提供一种显示装置,具有提升的可靠度。

5.本发明的一个实施例提出一种显示装置,包括:第一基板;第二基板,与第一基板相对;框胶,位于第一基板与第二基板之间;显示介质层,位于第一基板、第二基板以及框胶之间;疏水性薄膜,位于显示介质层与第一基板之间,且邻近框胶;以及多个电极组,位于疏水性薄膜与显示介质层之间,且各电极组包括多个电极对。

6.在本发明的一实施例中,上述的疏水性薄膜具有矩形回圈形状。

7.在本发明的一实施例中,上述的多个电极组包括2至10组电极组。

8.在本发明的一实施例中,上述的各电极组的宽度小于100μm。

9.在本发明的一实施例中,上述的多个电极对包括2至10对电极对。

10.在本发明的一实施例中,上述的多个电极对包括透明导电材料。

11.在本发明的一实施例中,上述的各电极对包括两条平行导线。

12.在本发明的一实施例中,上述的各平行导线的线宽介于2μm至5μm之间。

13.在本发明的一实施例中,上述的两条平行导线的间距介于10μm至16μm之间。

14.在本发明的一实施例中,上述的两条平行导线的线宽与间距比介于1:2至1:8之间。

15.在本发明的一实施例中,上述的各平行导线具有弯折形状。

16.在本发明的一实施例中,上述的各平行导线具有弯折角度,且弯折角度介于10度至50度之间。

17.在本发明的一实施例中,上述的各电极组还包括两电极端,且两电极端分别电连接两条平行导线。

18.在本发明的一实施例中,上述的多个电极组的两电极端分别相互电连接。

19.在本发明的一实施例中,上述的显示装置还包括像素电极,且多个电极对与像素电极属于相同膜层。

20.本发明的一个实施例提出一种显示装置的组装方法,包括:提供元件阵列基板,其中元件阵列基板包括第一基板、疏水性薄膜以及多个电极组,疏水性薄膜位于多个电极组

与第一基板之间且邻近第一基板的周缘,多个电极组位于疏水性薄膜上且分别包括多个电极对;提供滤光基板,其中滤光基板包括第二基板及框胶,框胶邻近第二基板的周缘;将显示介质滴注于元件阵列基板上;以及在对多个电极组施加电压的同时对组元件阵列基板与滤光基板,使得框胶粘合元件阵列基板与滤光基板,多个电极组邻近框胶的内侧,且显示介质位于元件阵列基板、滤光基板以及框胶之间。

21.在本发明的一实施例中,上述的对多个电极组施加电压是从外侧往内侧依序对各电极组施加电压。

22.在本发明的一实施例中,上述的各电极对的电压差介于10伏至100伏之间。

23.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附的附图作详细说明如下。

附图说明

24.图1a是本发明一实施例的显示装置10的上视示意图;

25.图1b是沿图1a的剖面线a

‑

a’所作的剖面示意图;

26.图1c是图1a的显示装置10的电极组es1的区域i的放大示意图;

27.图1d是图1a的显示装置10的电极组es1的区域ii的放大示意图;

28.图1e是图1c的电极对ep1的区域iii的放大示意图;

29.图2a至图2d是图1a至图1e所示的显示装置10的组装方法的步骤流程的剖面示意图;

30.图3a是本发明一实施例对多个电极组160施加电压的时序图;

31.图3b是本发明一实施例对多个电极组160施加电压的时序图;

32.图4是本发明一实施例的元件阵列基板as’的上视示意图。

33.符号说明

34.10:显示装置

35.100:母基板

36.110:第一基板

37.120:第二基板

38.122:彩色滤光层

39.124:配向膜

40.130:框胶

41.140:显示介质层

42.150:疏水性薄膜

43.160:多个电极组

44.a

‑

a’:剖面线

45.as、as’:元件阵列基板

46.ch:半导体层

47.cl:中心线

48.d1:宽度

49.d2:线宽

50.de:漏极

51.dm:显示介质

52.e11、e12:电极端

53.ea、ef:周缘

54.ep1、ep2、ep3、ep4:电极对

55.es1、es2、es3、es4、es5、es6:电极组

56.fs:滤光基板

57.ge:栅极

58.gi:栅极绝缘层

59.i、ii、iii:区域

60.is:内侧

61.p1、p2:共电极

62.pe:像素电极

63.pl:平坦层

64.se:源极

65.sl:切割线

66.sp:间距

67.t1、t2、t3、t4、t5、t6:时间

68.th:通孔

69.ts:薄膜晶体管

70.v1、v2、v3、v4、v5、v6:电压

71.vs1、vs2:电压源

72.w1、w2:导线

73.w11、w12、w13、w14、w21、w22、w23、w24:导线

74.θ:弯折角度

具体实施方式

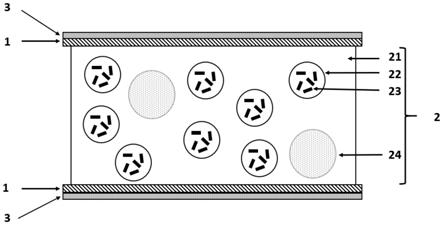

75.图1a是依照本发明一实施例的显示装置10的上视示意图。图1b是沿图1a的剖面线a

‑

a’所作的剖面示意图。图1c是图1a的显示装置10的电极组es1的区域i的放大示意图。图1d是图1a的显示装置10的电极组es1的区域ii的放大示意图。图1e是图1c的电极对ep1的区域iii的放大示意图。为了使附图的表达较为简洁,图1a省略了图1b中除第一基板110、框胶130、疏水性薄膜150以及电极组160以外的其他构件。以下,请同时参照图1a~图1e,以清楚地理解显示装置10的整体结构。

76.请同时参照图1a至图1e,显示装置10包括:第一基板110、第二基板120、框胶130、显示介质层140、疏水性薄膜150以及多个电极组160。第二基板120与第一基板110相对。框胶130位于第一基板110与第二基板120之间。显示介质层140位于第一基板110、第二基板120以及框胶130之间。疏水性薄膜150位于显示介质层140与第一基板110之间,且邻近框胶130。多个电极组160位于疏水性薄膜150与显示介质层140之间,且各电极组160包括多个电极对。

77.承上述,在本发明的一实施例的显示装置10中,通过设置多个电极组160来改变显示介质层140中的显示介质对疏水性薄膜150的接触角,能够避免在第一基板110与第二基板120的对组过程中显示介质接触框胶130所导致的污染或穿刺现象,进而提升显示装置10的可靠度。

78.以下,配合图1a至图1e,继续说明显示装置10的各个元件与膜层的实施方式,但本发明不以此为限。

79.请同时参照图1a与图1b,显示装置10的第一基板110可为透明基板,其材料包括石英基板、玻璃基板、高分子基板等,但本发明不限于此。

80.第一基板110上可设置用以形成开关元件、信号线、驱动元件、储存电容等的各种膜层。举例而言,在本实施例中,显示装置10还包括薄膜晶体管ts及像素电极pe,其中薄膜晶体管ts包括栅极ge、半导体层ch、源极se及漏极de,且像素电极pe通过平坦层pl中的通孔th电连接至薄膜晶体管ts的漏极de。薄膜晶体管ts的栅极ge重叠半导体层ch,且半导体层ch重叠栅极ge的区域可视为薄膜晶体管ts的通道区。栅极ge与半导体层ch之间配置有栅极绝缘层gi。薄膜晶体管ts的源极se与漏极de彼此分离,且源极se与漏极de分别接触半导体层ch。此外,栅极ge可电连接至显示装置10的扫描线(图未示),且源极se可电连接至显示装置10的数据线(图未示)。如此一来,薄膜晶体管ts可通过扫描线所传递的信号而开启或关闭,并且薄膜晶体管ts开启时可将数据线上所传递的信号传递给像素电极pe,像素电极pe可进一步驱动显示介质层140中的显示介质旋转。

81.显示装置10的第二基板120与第一基板110相对,且第二基板120可以是透明基板,例如石英基板、玻璃基板、高分子基板等。显示介质层140位于第一基板110与第二基板120之间,显示介质层140可以包括例如液晶材料、电泳材料或电湿润材料等显示材料。

82.第二基板120上可设置用以形成彩色滤光元件以及配向层的各种膜层。举例而言,在本实施例中,显示装置10还包括彩色滤光层122以及配向膜124,彩色滤光层122位于配向膜124与第二基板120之间,且配向膜124位于显示介质层140与彩色滤光层122之间。彩色滤光层122还可进一步包括红色滤光元件、绿色滤光元件以及蓝色滤光元件,以实现全彩化的显示效果。配向膜124可对显示介质层140中的显示介质(例如液晶分子)的初始偏转角度进行限定。在本实施例中,第二基板120以及设置于其上的彩色滤光层122以及配向膜124可构成显示装置10的滤光基板fs。

83.显示装置10的框胶130被夹置于第一基板110与第二基板120的周边区域之间,以密封第一基板110与第二基板120之间的空间,如此一来,由第一基板110、第二基板120以及框胶130所构成的封闭空间内可以封存显示介质而形成显示介质层140。框胶130的材料可以包括光固化胶、热固化胶或上述的组合,但本发明不限于此。

84.疏水性薄膜150可位于第一基板110上邻近框胶130的区域。举例而言,在本实施例中,疏水性薄膜150可设置于平坦层pl上邻接框胶130的区域,且疏水性薄膜150可具有矩形回圈的形状,但本发明不以此为限。在一些实施例中,疏水性薄膜150还可部分位于框胶130与平坦层pl之间。疏水性薄膜150的材料可以包括介电材料,例如液晶高分子(liquid crystal polymer),但本发明不限于此。

85.多个电极组160可设置于疏水性薄膜150上。当多个电极组160被施加电压时,可使疏水性薄膜150上产生电荷分布,从而改变显示介质层140中的显示介质对疏水性薄膜150

的接触角度。此外,在本实施例中,第一基板110以及设置于其上的疏水性薄膜150、多个电极组160、薄膜晶体管ts、像素电极pe、平坦层pl、栅极绝缘层gi、扫描线、数据线等可构成显示装置10的元件阵列基板as。

86.多个电极组160中电极组的数量并没有特别限制。在一些实施例中,多个电极组160可以包括2至10组电极组。举例而言,在本实施例中,多个电极组160可以包括6组电极组es1、es2、es3、es4、es5、es6。在某些实施例中,多个电极组160可以包括2组、3组、4组、5组、7组、8组、9组或10组电极组。

87.在本实施例中,多个电极组160的6组电极组es1、es2、es3、es4、es5、es6可从第一基板110的外侧至内侧依序设置于疏水性薄膜150上,且每一电极组都以镜像对称的方式设置于第一基板110的中心线cl的两侧,但本发明不限于此。

88.电极组es1、es2、es3、es4、es5、es6可具有彼此相同或相似的结构,以下以电极组es1为例进行说明。

89.请同时参照图1c与图1d,电极组es1的宽度d1可以小于100μm。举例而言,在本实施例中,电极组es1的宽度d1可以约为80μm,但本发明不以此为限。

90.在本实施例中,电极组es1可包括4对电极对ep1、ep2、ep3、ep4,但本发明不限于此。在一些实施例中,电极组es1可包括2至10对电极对。电极对ep1、ep2、ep3、ep4可与像素电极pe属于相同膜层,但本发明不以此为限。电极对ep1、ep2、ep3、ep4可以包括透明导电材料,例如金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物或其它合适的材料、或是上述导电材料的堆叠层。在一些实施例中,电极对ep1、ep2、ep3、ep4可以包括铟锡氧化物、铟锌氧化物、铝锡氧化物、铝锌氧化物、铟镓锌氧化物或其他适合的氧化物或者是上述至少二者的堆叠层。

91.每一电极对可包括两条平行导线,举例而言,在本实施例中,电极对ep1可包括平行的导线w11、w21,电极对ep2可包括平行的导线w12、w22,电极对ep3可包括平行的导线w13、w23,电极对ep4可包括平行的导线w14、w24。

92.在本实施例中,电极组es1还可包括两个电极端e11、e12,其中电极端e11可电连接导线w11、w12、w13、w14,且电极端e12可电连接导线w21、w22、w23、w24。在一些实施例中,电极端e11、e12还可与薄膜晶体管ts的漏极de或栅极ge属于相同膜层。另外,电极端e11可电连接至共电极p1,且电极组es2、es3、es4、es5、es6中与电极端e11同侧的电极端也可电连接至共电极p1,使得电极端e11以及电极组es2、es3、es4、es5、es6中与电极端e11同侧的电极端可经由共电极p1相互电连接。同样地,电极端e12以及电极组es2、es3、es4、es5、es6中与电极端e12同侧的电极端可经由共电极p2相互电连接。

93.请参照图1e,电极对ep1的导线w11、w21之间的间距sp可以介于9μm至18μm之间。举例而言,在本实施例中,导线w11、w21的间距sp可以约为14μm,但本发明不以此为限。

94.导线w11、w12、w13、w14、w21、w22、w23、w24的线宽可以介于2μm至6μm之间。举例而言,在本实施例中,导线w11的线宽d2可以约为4μm,但本发明不以此为限。

95.电极对ep1的导线w11、w21的线宽d2与间距sp的比可以介于1:2至1:8之间。举例而言,在本实施例中,线宽d2与间距sp的比约为1:3.5,但本发明不以此为限。

96.在本实施例中,导线w11、w12、w13、w14、w21、w22、w23、w24可以具有弯折形状,且导线w11、w12、w13、w14、w21、w22、w23、w24可以具有弯折角度θ。弯折角度θ可以介于10度至50

度之间。举例而言,在本实施例中,弯折角度θ可以是30度,但本发明不以此为限。

97.图2a至图2d是图1a至图1e所示的显示装置10的组装方法的步骤流程的剖面示意图。以下,配合图2a至图2d,以说明显示装置10的组装方法。

98.请参照图2a,首先,提供元件阵列基板as。在本实施例中,元件阵列基板as可以包括如前所述的第一基板110、薄膜晶体管ts、像素电极pe、平坦层pl、栅极绝缘层gi、疏水性薄膜150、多个电极组160等元件及膜层,其中薄膜晶体管ts包括栅极ge、半导体层ch、源极se及漏极de,且像素电极pe电连接薄膜晶体管ts的漏极de。疏水性薄膜150位于多个电极组160与第一基板110之间,且疏水性薄膜150可邻近第一基板110的周缘ea,例如疏水性薄膜150可具有矩形回圈的形状。多个电极组160位于疏水性薄膜150上,且多个电极组160可包括6组电极组es1、es2、es3、es4、es5、es6。电极组es1、es2、es3、es4、es5、es6都包括如图1c至图1d所示的4对电极对ep1、ep2、ep3、ep4以及两个电极端e11、e12,其中电极对ep1可包括平行的导线w11、w21,电极对ep2可包括平行的导线w12、w22,电极对ep3可包括平行的导线w13、w23,电极对ep4可包括平行的导线w14、w24,且电极端e11可电连接导线w11、w12、w13、w14,电极端e12可电连接导线w21、w22、w23、w24。

99.接着,请参照图2b,提供滤光基板fs,且滤光基板fs可以包括如前所述的第二基板120、彩色滤光层122以及配向膜124。在本实施例中,滤光基板fs还包括框胶130,且框胶130邻近第二基板120的周缘ef设置。

100.接着,请参照图2c,将显示介质dm滴注于元件阵列基板as上。在本实施例中,显示介质dm可以包括液晶分子,但本发明不限于此。

101.接着,请参照图2d,将如图2b所示的滤光基板fs反转180度,且对位放置于如图2c所示的元件阵列基板as上方,其中经由对位可使多个电极组160于第二基板120的正投影邻近框胶130于第二基板120的正投影的内侧is。然后,对多个电极组160施加电压,以使疏水性薄膜150上的显示介质dm朝向远离周缘ea的方向移动,同时将元件阵列基板as与滤光基板fs对组,以使框胶130粘合元件阵列基板as与滤光基板fs,且可随即将框胶130固化,使得显示介质dm可被封存于元件阵列基板as、滤光基板fs以及框胶130之间。如此一来,在元件阵列基板as与滤光基板fs对组的过程中,显示介质dm完全不会接触到未固化的框胶130。此外,在对组完成之后,可停止对多个电极组160施加电压,使显示介质dm可往周缘ea的方向移动,而得到如图1b所示的显示装置10。

102.图3a是依照本发明一实施例对多个电极组160施加电压的时序图。在本实施例中,对多个电极组160施加电压是从外侧往内侧依序对各电极组施加电压。举例而言,请参照图3a,在本实施例中,对多个电极组160施加电压可依序在时间t1开始对电极组es1施加电压v1、在时间t2开始对电极组es2施加电压v2、在时间t3开始对电极组es3施加电压v3、在时间t4开始对电极组es4施加电压v4、在时间t5开始对电极组es5施加电压v5以及在时间t6开始对电极组es6施加电压v6。上文所述的「对电极组es1施加电压v1」是指使电极组es1的两个电极端e11、e12的电压差约为v1,也就是说,使电极对ep1的导线w11与导线w21的电压差约为v1,且「对电极组es2施加电压v2」、「对电极组es3施加电压v3」、「对电极组es4施加电压v4」、「对电极组es5施加电压v5」以及「对电极组es6施加电压v6」也具有相似的含意,于此不再赘述。

103.在本实施例中,可在时间t1至时间t6期间将元件阵列基板as与滤光基板fs对组。

另外,电压v1、v2、v3、v4、v5、v6可以相同,但本发明不限于此。此外,电压v1、v2、v3、v4、v5、v6可以介于10伏至100伏之间。在本实施例中,电压v1、v2、v3、v4、v5、v6约为15伏,但本发明不限于此。

104.图3b是依照本发明一实施例对多个电极组160施加电压的时序图。在本实施例中,请参照图3b,可以在时间t1开始对电极组es1施加电压v1,且在时间t2开始对电极组es2施加电压v2之后停止对电极组es1施加电压v1。同样地,可以在时间t2开始对电极组es2施加电压v2,且在时间t3开始对电极组es3施加电压v3之后停止对电极组es2施加电压v2。同样地,可以在时间t3开始对电极组es3施加电压v3,且在时间t4开始对电极组es4施加电压v4之后停止对电极组es3施加电压v3。同样地,可以在时间t4开始对电极组es4施加电压v4,且在时间t5开始对电极组es5施加电压v5之后停止对电极组es4施加电压v4。同样地,可以在时间t5开始对电极组es5施加电压v5,且在时间t6开始对电极组es6施加电压v6之后停止对电极组es5施加电压v5。

105.在图3b所示的实施例中,对电极组es1施加电压v1的持续时间、对电极组es2施加电压v2的持续时间、对电极组es3施加电压v3的持续时间、对电极组es4施加电压v4的持续时间、对电极组es5施加电压v5的持续时间以及对电极组es6施加电压v6的持续时间可以相同,但不以此为限。同样地,可以在时间t1至时间t6期间将元件阵列基板as与滤光基板fs对组。

106.图4是依照本发明一实施例的元件阵列基板as’的上视示意图。请参照图4,元件阵列基板as’可以包括多个如图2a所示的元件阵列基板as。也就是说,元件阵列基板as’经切割后可形成多个元件阵列基板as,且元件阵列基板as’的母基板100经切割后可形成多个前述的第一基板110。如前所述,每一元件阵列基板as可包括多个电极组160,且多个电极组160的两个电极端分别电连接至共电极p1、p2。在本实施例中,各元件阵列基板as的共电极p1可经由导线w1电连接至电压源vs1,同时各元件阵列基板as的共电极p2可经由导线w2电连接至电压源vs2。如此一来,当提供元件阵列基板as’进行如图2a至图2d所示的组装方法的步骤流程时,在对多个电极组160施加电压的过程中,可通过电压源vs1、vs2同时对各元件阵列基板as的共电极p1、p2施加偏压。此外,在如图2a至图2d所示的组装方法的步骤流程完成之后,可沿切割线sl进行切割,而一次制得多个如图1a至图1e所示的显示装置10。

107.综上所述,本发明通过设置多个电极组来改变显示介质对疏水性薄膜的接触角,能够避免显示介质在基板对组的过程中接触框胶,进而提升显示装置的可靠度。

108.虽然结合以上实施例公开了本发明,然而其并非用以限定本发明,任何所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,可作些许的更动与润饰,故本发明的保护范围应当以附上的权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。