具有低速serdes接口的发送器、接收器及其电路设计方法

技术领域

1.本发明涉及serdes技术领域,尤其涉及一种具有低速serdes接口的发送器、接收器及其电路设计方法。

背景技术:

2.随着科学技术的不断发展,在电子通信领域,传输数据的技术不断提高,传输的速率也不断的加快。serdes (serializer/deserializer,串行器/解串器)技术是高速串行数据传输领域的一个重大发明。serdes这个名字的由来,是由串行器(serlializer)和解串器(deserializer)这两个单词组合而来的。serdes是典型的数模混合系统,目前serdes中主要采用自同步的方式,即接口传送的数据中包含了时钟的信息,通过接收端(rx)的时钟数据恢复(clock data recovery,cdr)电路完成对接收数据的时钟抽取和数据再采样,最终恢复出正确的数据。serdes其实就是一种串并/并串转换设备,通常在发送的过程中将低速的并行数据转换为高速的串行数据发送出去,而在接收的过程中将高速的串行数据转换回低速的并行数据。最大程度的利用串行数据传输快的特点,而将数据传输的速率提高到gbps 的量级。

3.随着集成电路设计和芯片制造工艺的快速发展,通信设备的芯片中用于高速数据传输的serdes接口速率快速提高并可以兼容多种通信传输协议,目前各大ic制造厂商通用的serdes接口芯片一般可以支持rapidio 3.2,pcie 4.0(peripheral component interconnect express,高速串行计算机扩展总线标准),16g/8g/4g/2g fc(fibre channel,光纤总线),1000base

‑

x(光纤吉比特以太网),10gbase

‑

kr(背板以太网接口标准)等协议。由于历史原因,目前交换芯片通信网络中仍然存在大量低速率的通信接口,典型的低速通信接口为1g fc协议的1.0625gbps和1g srio协议的1.25gbps。由于现有的高速serdes接口ip为了支持更高速率信号而提高了锁相环中心频率,现有的高速serdes接口ip的模拟电路部分已经无法提供1.0625gbps和1.25gbps所需的采样时钟。

4.为了兼容交换芯片网络中1g fc协议的1.0625gbps serdes或者1g srio协议的1.25gbps接口ip,继续采用过去的低速工艺和低速接口ip设计1.0625gbps/1.25gbpsserdes芯片,将导致整个芯片低速和高功耗的缺陷。在现有的制造工艺下重新研究开发1.0625gbps/1.25gbps serdes接口ip,或者将旧的1.0625gbps/1.25gbps serdes接口ip移植到新的制造工艺上,其研究开发的代价很大,存在适配新技术的风险,而且旧的serdes接口ip的需求量不大,导致成本较高,经济效益差。

技术实现要素:

5.针对在现有的制造工艺下重新研究开发1.0625gbps serdes接口ip,或者将旧的1.0625gbps serdes接口ip移植到新的制造工艺上所存在的成本高、适配新技术风险大的问题,本发明提供一种具有低速serdes接口的发送器、接收器及其电路设计方法。

6.第一方面,本发明提供一种具有低速serdes接口的发送器,包括serdes模拟电路

和serdes数字电路,所述serdes数字电路包括:四分频模块、异步fifo模块、tx_data_repeat_gen模块和位宽转换模块;所述四分频模块,用于将所述serdes模拟电路产生的serdes并行数据发送时钟tx_clk_20t进行四分频产生控制器的并行数据发送时钟pma_tx_clk输入至协议控制器;所述异步fifo模块,用于对来自协议控制器的数据进行跨异步读取;所述tx_data_repeat_gen模块,用于将异步fifo模块读取的一个位宽为40bit的数据rd_data_40中的每一bit均重复发送一次,得到一个位宽为80bit的数据tx_data_80;所述位宽转换模块,用于对tx_data_repeat_gen模块输出的数据tx_data_80进行80bit到20bit的位宽转换;所述serdes模拟电路,用于对位宽转换模块输出的数据进行并串转换处理,并通过其高速差分串行通道线tx_p/tx_n将数据发送出去;以及产生并行数据发送时钟tx_clk_20t;其中,当serdes模拟电路的速率配置为2.125gbps时,所述发送器为具有1.0625gbps低速serdes接口的发送器,对应的协议控制器为fc控制器;当serdes模拟电路的速率配置为2.5gbps时,所述发送器为具有1.25gbps低速serdes接口的发送器,对应的协议控制器为srio控制器。

7.第二方面,本发明提供一种具有低速serdes接口的接收器,包括serdes模拟电路和serdes数字电路,所述serdes数字电路包括:四分频模块、位宽转换模块和rx_data_rm_repeat_gen模块;所述serdes模拟电路,用于将从其高速差分串行通道线rx_p/rx_n接收到的高速差分串行数据转换为位宽为20bit的并行数据rx_data_20,以及产生serdes并行数据接收时钟rx_clk_20t;所述四分频模块,用于将所述serdes模拟电路产生的serdes并行数据接收时钟rx_clk_20t进行四分频产生控制器的并行数据接收时钟rx_par_clk输入至协议控制器;所述位宽转换模块,用于对所述serdes模拟电路输出的数据rx_data_20进行20bit到80bit的位宽转换;所述rx_data_rm_repeat_gen模块,用于将位宽转换模块输出的一个位宽为80bit的数据rx_data_80的每两个bit均删除一个bit,得到一个位宽为40bit的rx_data_40,并将其输入至协议控制器,进行后续数据处理;其中,当serdes模拟电路的速率配置为2.125gbps时,所述接收器为具有1.0625gbps低速serdes接口的接收器,对应的协议控制器为fc控制器;当serdes模拟电路的速率配置为2.5gbps时,所述接收器为具有1.25gbps低速serdes接口的接收器,对应的协议控制器为srio控制器。

8.第三方面,本发明提供一种具有低速serdes接口的发送器的电路设计方法,不改变发送器中的原有serdes模拟电路,对发送器中的原有serdes数字电路进行修改,修改后的serdes数字电路包括四分频模块、异步fifo模块、tx_data_repeat_gen模块和位宽转换模块,所述方法还包括:当需要支持fc协议时,将serdes模拟电路的速率配置为2.125gbps,所述serdes模拟电路产生serdes并行数据发送时钟tx_clk_20t;或者,当需要支持srio协议时,将serdes

模拟电路的速率配置为2.5gbps,所述serdes模拟电路产生serdes并行数据发送时钟tx_clk_20t;采用四分频模块对serdes并行数据发送时钟tx_clk_20t进行四分频产生控制器的并行数据发送时钟pma_tx_clk输入至协议控制器;采用异步fifo模块将来自协议控制器的数据进行跨异步读取;采用tx_data_repeat_gen模块将异步fifo模块读取的一个位宽为40bit的数据rd_data_40中的每一bit均重复发送一次,得到一个位宽为80bit的数据tx_data_80;采用位宽转换模块对tx_data_repeat_gen模块输出的数据tx_data_80进行80bit到20bit的位宽转换;通过serdes模拟电路对位宽转换模块输出的数据进行并串转换处理,并通过其高速差分串行通道线tx_p/tx_n将数据发送出去。

9.第四方面,本发明提供一种具有低速serdes接口的接收器的电路设计方法,不改变接收器中的原有serdes模拟电路,对接收器中的原有serdes数字电路进行修改,修改后的serdes数字电路包括四分频模块、位宽转换模块和rx_data_rm_repeat_gen模块,所述方法还包括:当需要支持fc协议时,将serdes模拟电路的速率配置为2.125gbps,所述serdes模拟电路产生serdes并行数据接收时钟rx_clk_20t,并将从其高速差分串行通道线rx_p/rx_n接收到的高速差分串行数据转换为20bit的并行数据rx_data_20;或者,当需要支持srio协议时,将serdes模拟电路的速率配置为2.5gbps,所述serdes模拟电路产生serdes并行数据发送时钟tx_clk_20t;采用所述四分频模块对所述serdes并行数据接收时钟rx_clk_20t进行四分频产生控制器的并行数据接收时钟rx_par_clk输入至协议控制器;采用所述位宽转换模块对所述serdes模拟电路输出的数据rx_data_20进行20bit到80bit的位宽转换;采用所述rx_data_rm_repeat_gen模块将位宽转换模块输出的一个位宽为80bit的数据rx_data_80的每两个bit均删除一个bit,得到一个位宽为40bit的rx_data_40,并将其输入至协议控制器,进行后续数据处理。

10.本发明的有益效果:本发明提供的一种具有低速serdes接口的发送器、接收器及其电路设计方法,使用现有的2.125gbps或者2.5gbps高速serdes模拟电路提供的采样时钟进行数据采样,保证serdes模拟电路设计不变,通过只修改数字电路部分实现兼容1.0625gbps或者1.25gbps的功能,能够在最大限度地利用现有高速serdes接口的基础上,满足低速1.0625gbps或者1.25gbps接口的要求,节约芯片的端口,降低芯片设计风险以及成本,缩短开发周期;在发送器设计中,对发送数据进行重复采样放在位宽转换之前,在接收器设计中,对接收数据的重复bit进行删除时放在位宽转换之后,保证了数据传输的完整性,提高数据的传输效率,确保数据传输无误码。

附图说明

11.图1为现有serdes发送器的电路结构示意图;

图2为本发明实施例提供的具有低速serdes接口的发送器的电路结构示意图;图3为现有serdes接收器的电路结构示意图;图4为本发明实施例提供的具有低速serdes接口的接收器的电路结构示意图。

具体实施方式

12.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

13.本发明提供的发送器、接收器及其电路设计方法是一种通用的低速serdes接口关键电路设计方法,可以适用于fc协议所支持的速率,也可以适用于srio协议速率的低速serdes接口电路设计。下面以fc协议作为举例。

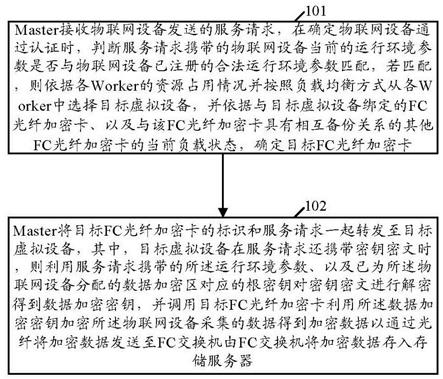

14.实施例1现有的serdes发送器电路基本结构如图1所示,serdes模拟部分电路根据速率配置产生serdes并行数据发送时钟tx_clk_20t,时钟频率为速率/并行数据位宽,serdes并行数据位宽为20bit,因此当速率配置为8.5g时,tx_clk_20t = 425mhz(8.5g/20bit);当速率配置为4.25g时,tx_clk_20t = 212.5mhz(4.25g/20bit);当速率配置为2.125g时,tx_clk_20t = 106.25mhz(2.125g/20bit)。由于fc控制器发送数据并行位宽为40bit,serdes数字部分首先将tx_clk_20t进行二分频产生控制器的并行数据发送时钟pma_tx_clk(53.125mhz)输入到fc控制器用于40bit并行数据的发送,然后将fc控制器发送过来的数据经过异步fifo进行跨异步读取,然后对发送数据进行40bit到20bit的位宽转换,最后发送到serdes模拟电路部分进行并串转换处理,并通过高速差分串行通道线tx_p/tx_n将数据发送出去。

15.基于现有的2.125gbps serdes发送器电路设计,本发明实施例提供一种具有1.0625gbps低速serdes接口的发送器,通过修改数字电路部分实现兼容1.0625gbps的功能,serdes模拟部分电路保持原设计不变,其基本结构如图2所示,此时协议控制器为fc控制器。由于serdes模拟部分电路保持原设计不变并且此时serdes模拟电路速率配置为2.125gbps,因此tx_clk_20t = 106.25mhz(2.125g/20bit),而fc控制器的发送速率是按照1.0625gbps配置的,我们将tx_clk_20t进行四分频产生控制器的并行数据发送时钟pma_tx_clk(26.565mhz)输入到fc控制器用于40bit并行数据的发送,然后将fc控制器发送过来的数据经过异步fifo进行跨异步读取,此时将rd_data_40经过tx_data_repeat_gen模块处理,即将发送的40bit数据的每一bit都重复发送一次,这样得到一个80bit位宽的tx_data_80,然后对发送数据进行80bit到20bit的位宽转换,最后发送到serdes模拟电路部分进行并串转换处理,并通过高速差分串行通道线tx_p/tx_n将数据发送出去。因为我们采用2.125gbps的速率将每一个bit都重复发送了一次,因此serdes模拟电路部分最终发送的就是1.0625gbps速率的数据。

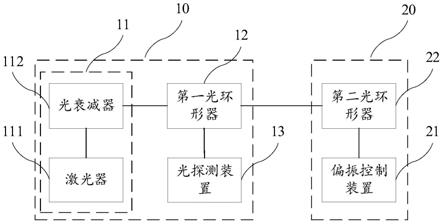

16.实施例2现有的serdes接收器电路基本结构如图3所示,serdes模拟部分电路根据速率配置产生serdes并行数据接收时钟rx_clk_20t,时钟频率为速率/并行数据位宽,serdes并行

数据位宽为20bit,因此当速率配置为8.5g时,rx_clk_20t = 425mhz(8.5g/20bit);当速率配置为4.25g时,rx_clk_20t = 212.5mhz(4.25g/20bit);当速率配置为2.125g时,rx_clk_20t = 106.25mhz(2.125g/20bit)。serdes模拟电路首先将从rx_p/rx_n接收到的高速差分串行数据转换为20bit的并行数据rx_data_20,同时生成20t的serdes并行数据接收时钟rx_clk_20t,由于fc控制器接收数据并行位宽为40bit,serdes数字部分首先将rx_clk_20t进行二分频产生控制器的并行数据接收时钟rx_par_clk(53.125mhz)输入到fc控制器用于40bit并行数据的接收,然后对接收数据进行20bit到40bit的位宽转换,最后输入到fc控制器进行后续处理。

17.基于现有的2.125gbps serdes接收器电路设计,本发明实施例提供一种具有1.0625gbps低速serdes接口的接收器,通过修改数字电路部分实现兼容1.0625gbps的功能,serdes模拟部分电路保持原设计不变,其基本结构如图4所示,此时协议控制器为fc控制器。由于serdes模拟部分电路保持原设计不变并且此时serdes模拟电路速率配置为2.125gbps,因此rx_clk_20t = 106.25mhz(2.125g/20bit),而fc控制器的接收速率是按照1.0625gbps配置的,我们将rx_clk_20t进行四分频产生控制器的并行数据接收时钟rx_par_clk(26.565mhz)输入到fc控制器用于40bit并行数据的接收,由于对端设备是按照1.0625gbps的速率发送的数据,而serdes模拟电路是按照2.125gbps的速率采样的,其实每一bit数据都重复采了一次,因此接收到的20bit数据rx_data_20其实只有10bit有效数据。然后对接收数据进行20bit到40bit的位宽转换,我们首先将每4拍20bit数据组成一个80bit的rx_data_80,然后再将rx_data_80经过rx_data_rm_repeat_gen模块处理,即将接收到的80bit数据的每两个bit都删除一个bit,这样得到一个40bit位宽的rx_data_40,最后输入到fc控制器进行后续处理。

18.实施例3基于与实施例1同样的设计原理,本发明实施例还提供一种具有1.25gbps低速serdes接口的发送器,与实施例1不同的是,本发明实施例基于现有的2.5gbps serdes发送器电路设计,即将serdes模拟电路的速率配置为2.5gbps,将协议控制器调整为srio控制器,其他内容同实施例1,此处不再赘述。

19.实施例4基于与实施例2同样的设计原理,本发明实施例还提供一种具有1.25gbps低速serdes接口的接收器,与实施例2不同的是,本发明实施例基于现有的2.5gbps serdes接收器电路设计,即将serdes模拟电路的速率配置为2.5gbps,将协议控制器调整为srio控制器,其他内容同实施例2,此处不再赘述。

20.利用本发明提供的1.0625gbps/1.25gbps低速serdes接口ip,具有以下优点:1、采用现有的2.125gbps/2.5gbps高速serdes模拟电路提供的采样时钟进行数据采样,保证模拟电路部分不做任何修改,通过只修改数字电路部分实现兼容1.0625gbps/1.25gbps的功能,能够在最大限度地利用现有高速serdes接口的基础上,满足低速1.0625gbps/1.25gbps接口的要求,节约芯片的端口,降低芯片设计风险以及成本,缩短开发周期。

21.2、本发明在进行发送器设计时,将发送数据首先进行重复采样然后再进行80bit到20bit的位宽转换,保证了发送数据的完整性,提高数据的发送效率,确保数据发送无误

码。

22.3、本发明在进行接收器设计时,将接收到的20bit数据每4拍先组合成一个80bit的数据,然后再将80bit数据的每两个bit都删除一个bit,从而得到一个有效的40bit并行数据,保证了接收数据的完整性,提高数据的传输效率,确保数据接收无误码。

23.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。