一种针对set效应的版图加固方法

技术领域

1.本发明涉及集成电路设计技术,尤其涉及一种针对set(单粒子瞬态脉冲)效应的版图加固方法。

背景技术:

2.在集成电路制作过程中,空间重离子、α粒子以及中子等轰击集成电路的敏感节点,将直接或者间接导致集成电路发生软错误。随着工艺的持续缩减、集成电路复杂度的不断增加、电源电压的不断降低以及工作频率的不断升高,软错误逐渐成为深亚微米工艺下最重要的可靠性问题。当工艺缩减到深亚微米阶段之后,单粒子翻转(seu)、单粒子瞬态脉冲(set)和多位翻转(mbu)成为软错误的主要来源。随着集成电路制造工艺继续向纳米尺度缩减,set变得越来越严重,已成为软错误的第一来源。

3.带电粒子轰击电路的敏感节点,将产生一个瞬态脉冲。如果瞬态脉冲发生在存储单元、锁存器和触发器等时序电路的敏感节点并且收集足够的电荷,则会发生seu,瞬态脉冲从而演变为“持久”性的错误,直到数据被重写,错误数据才有可能恢复正确。如果瞬态脉冲发生在组合逻辑节点并且收集足够的电荷,则会沿着数据通路向下传播,并有可能被下一级时序单元锁存,变为“持久”性的错误。这类发生在组合逻辑节点的瞬态脉冲被称为set。

4.set能够被下一级时序单元俘获必须至少满足四个条件:(1)粒子轰击必须产生一个能够沿电路传播的脉冲,亦即产生的脉冲具有足够的宽度和高度;(2)必须存在一条从被轰击节点到下一级时序单元的敏化路径;(3)set传播到下一级时序单元时必须具有足够的宽度和高度从而能够改变时序单元的状态,亦即满足时序单元的建立和保持时间要求;(4)在同步电路中,set必须在有效的时钟沿到达。当被轰击节点处产生的set脉冲宽度较小时,继而在传播过程中宽度不断减小,直至最终消失。因此,具体如何减小set脉冲宽度,实现版图加固的最终效果,已成为一项亟待解决的关键技术问题。

技术实现要素:

5.本发明要解决的技术问题:针对现有技术存在的上述问题,提供一种针对set效应的版图加固方法,旨在解决时钟树、置复位网络等全局信号的set效应将对全芯片带来严重影响的问题,对此类全局信号进行加固。

6.为了解决上述技术问题,本发明采用的技术方案为:

7.一种针对set效应的版图加固方法,包括:在经过增加阱接触和衬底接触加固后的标准单元的版图设计的基础上,通过无缝阱/衬底接触和分割有源区两种方式中的至少一种,形成具有set加固效果的版图结构。

8.可选地,所述无缝阱/衬底接触是指取消阱/衬底接触与有源区之间的浅沟道隔离sti,使阱/衬底接触与有源区紧邻以增加阱/衬底接触对体区电势的控制能力。

9.可选地,所述取消阱/衬底接触与有源区之间的浅沟道隔离sti之后,还包括阱接

触和衬底接触同时往版图设计的中部延伸,分别与标准单元的pmos晶体管和nmos晶体管的源极有源直接相连。

10.可选地,所述分割有源区是指将较宽的晶体管拆分为若干个较窄的晶体管,且拆分后的晶体管以并联的方式进行连接并替代原来较宽的晶体管,从而不影响电路的功能,所述晶体管是指pmos晶体管或nmos晶体管。

11.可选地,所述将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管之间用浅沟道隔离sti进行隔离。

12.可选地,所述将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管间共栅。

13.可选地,所述将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管之间在版图中以公用的栅极作为中心呈算盘状分布。

14.此外,本发明还提供一种集成电路,所述集成电路包含标准单元,所述标准单元为采用所述针对set效应的版图加固方法加固处理得到的标准单元。

15.可选地,所述标准单元为inv_8单元。

16.可选地,所述inv_8单元包括相互并联连接的pmos晶体管和nmos晶体管。

17.和现有技术相比,本发明具有下述优点:本发明包括在经过增加阱接触和衬底接触加固后的标准单元的版图设计的基础上,通过无缝阱/衬底接触和分割有源区两种方式中的至少一种,形成具有set加固效果的版图结构,通过上述手段,能够有效减小set脉冲宽度,能够解决时钟树、置复位网络等全局信号的set效应将对全芯片带来严重影响的问题,对此类全局信号进行加固。

附图说明

18.图1为nmos常规阱接触与抗辐照能力示意图(图中p 和sti应当紧邻)。

19.图2为本实施例中nmos无缝阱/衬底接触抗辐照能力示意图。

20.图3为本实施例中分割mos管有源区示意图。

21.图4是本实施例中inv_8单元的电路图。

22.图5为增加阱接触和衬底接触加固的inv_8单元的物理版图。

23.图6为只做无缝阱/衬底接触加固设计的inv_8单元的物理版图。

24.图7为只做分割有源区加固设计的inv_8单元的物理版图。

25.图8为结合无缝阱/衬底接触和分割有源区加固后的inv_8单元的物理版图。

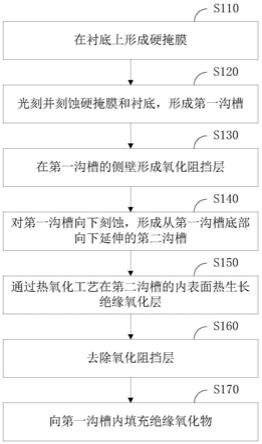

26.图9是本实施例中的实验模拟流程。

具体实施方式

27.本实施例提供一种针对set效应的版图加固方法,包括:在经过增加阱接触和衬底接触加固后的标准单元的版图设计的基础上,通过无缝阱/衬底接触和分割有源区两种方式中的至少一种,形成具有set加固效果的版图结构。

28.本实施例中,无缝阱/衬底接触是指取消阱/衬底接触与有源区之间的浅沟道隔离sti(shallow trench isolation),在标准单元中阱接触(pmos器件)和衬底接触(nmos器件)与有源区之间用浅沟道隔离技术sti(shallow trench isolation)进行隔离,可使阱/

衬底接触与有源区紧邻以增加阱/衬底接触对体区(bulk)电势的控制能力。

29.本实施例中,取消阱/衬底接触与有源区之间的浅沟道隔离sti之后,还包括阱接触和衬底接触同时往版图设计的中部延伸,分别与标准单元的pmos晶体管和nmos晶体管的源极有源直接相连。

30.图1所示为作为对比的nmos管的常规连接方式剖面图。研究表明,敏感节点被粒子轰击带来的电荷收集会造成单粒子效应,电荷收集量的大小将直接影响单粒子瞬态的脉冲宽度和峰值。器件的电荷收集量越大,单粒子瞬态的脉冲宽度越宽,峰值越高,越容易造成软错误。传统的体硅工艺下,器件电荷收集机制包括漂移、扩散和双极放大效应,其中双极放大效应占主要地位。本实施例中采用无缝阱/衬底接触降低双极放大效应,从而减小set脉冲宽度,如图2所示。无缝阱/衬底接触方式可能导致晶体管的长度不能使用最小栅长。在s40ll下,最小栅长为40nm,如果使用本实施例方法,则靠近无缝的晶体管长度必须为60nm以上才能通过设计规则检查(drc)。

31.本实施例中,分割有源区是指将较宽的晶体管拆分为若干个较窄的晶体管,且拆分后的晶体管以并联的方式进行连接并替代原来较宽的晶体管,从而不影响电路的功能,所述晶体管是指pmos晶体管或nmos晶体管。

32.本实施例中,将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管之间用浅沟道隔离sti进行隔离。

33.本实施例中,将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管间共栅。

34.本实施例中,将较宽的晶体管拆分为若干个较窄的晶体管时,拆分后的晶体管之间在版图中以公用的栅极作为中心呈算盘状分布。在经过增加阱接触和衬底接触加固后的标准单元的版图设计的基础上,通过无缝阱/衬底接触和分割有源区的方式,形成具有一定set加固效果的版图结构,其版图形状如同算盘。

35.很多研究表明体硅器件由于“漏斗效应”和寄生双极放大效应的电荷收集机制,器件漏区一直是set最敏感的区域。当重离子轰击器件漏区中心时电荷收集量最大。并且器件电荷收集量的大小与漏区面积成正相关。因此,减少器件漏区面积可以有效减少器件电荷收集量,从而抑制单粒子瞬态脉冲的宽度和峰值。基于此,本发明在宽度上对晶体管进行拆分。当mosfet宽度较大,造成敏感面积过大时,可以通过分割有源区的方式,将较宽的晶体管拆分为若干个较窄的晶体管。拆分后的晶体管以并联的方式进行连接,替代原来较宽的晶体管,从而不影响电路的功能。拆分后的晶体管之间用sti进行隔离。当重离子轰击敏感节点时,因为晶体管的漏区面积减少且晶体管之间相互隔离。使得单个粒子沉积的电荷只有少部分将被晶体管的漏极收集。这将减小电荷的收集,从而达到降低set脉冲宽度的目的。如图3中(1)和图3中(2)所示的晶体管具有相同的w和l,通过分割有源区,图3中(2)所示的版图有效减小了受到轰击时电荷的收集面积,以此达到减小受轰击时脉冲宽度的目的。

36.此外,本实施例还提供一种集成电路,所述集成电路包含标准单元,标准单元为采用前述针对set效应的版图加固方法加固处理得到的标准单元。

37.本实施例中,标准单元为inv_8单元。如图4所示,本实施例中inv_8单元包括相互并联连接的pmos晶体管和nmos晶体管。

38.表1显示了本实施例四种作为对比的单元所用的加固方式,用轰击能量为let=

37mev

·

cm2/mg的重离子分别对inv_8_a、inv_8_b、inv_8_c和inv_8_d进行轰击,仿真条件如表2所示。

39.表1:加固方式说明。

40.单元加固方式inv_8_a无加固轰击inv_8_b只做无缝阱/衬底接触加固inv_8_c只做分割有源区加固inv_8_d无缝阱/衬底接触加固 分割有源区加固

41.表2:重离子轰击仿真条件。

42.工艺smic40ll工艺角tt电压1.1v温度25℃

43.表3为4个单元受重离子轰击后的脉冲宽度。通过对比inv_8_b和inv_8_a的结果,可以得出无缝接触加固设计在一定程度上减小了脉冲宽度,较于nmos,pmos的加固效果更为明显;通过对比inv_8_c和inv_8_a的结果,可以得出算盘状加固设计在一定程度上减小了脉冲宽度,较于pmos,nmos的加固效果更为明显;通过对比inv_8_d和inv_8_a的结果,可以得出结合无缝接触和算盘状加固设计能同时在很大程度上减小pmos和nmos的脉冲宽度,从而得到很好的set加固效果。

44.表3:脉冲宽度(单位:ps)。

45.单元轰击pmos轰击nmosinv_8_a200.5224.7inv_8_b105.7184.5inv_8_c121.968.3inv_8_d70.461.3

46.图5为未做无缝阱/衬底接触加固和分割有源区加固,只增加阱接触和衬底接触加固的inv_8单元的物理版图。从图中可以看出,阱接触和衬底接触分别位于版图的顶部和底部,通过金属层分别与pmos和nmos的源极有源相连。

47.图6为只做无缝阱/衬底接触加固设计的inv_8单元的物理版图,从图中可以看出,阱接触和衬底接触同时往版图中部延伸,分别与pmos和nmos的源极有源直接相连。这样的设置可以使阱/衬底接触,能更好地控制体区电势,从而有效抑制双极放大效应。

48.图7为只做分割有源区加固设计的inv_8单元的物理版图,从图中可以看出,单个mos的有源宽度较小,且多个mos管共用同一根栅。着眼看整个单元版图,其形状类似算盘。大量的研究结果表明,漏区面积减小,当单个粒子轰击时,收集的电荷也将减小,进而产生的脉冲宽度也会减小。

49.图8为结合无缝阱/衬底接触和分割有源区加固后的inv_8单元的物理版图。这样的加固设计充分结合了无缝接触和算盘状加固的优点。

50.图9是实验模拟的流程。使用著名的ic设计软件开发商美国新思科技公司发布的

sentaurus tcad工具来构造3d器件模型并进行单粒子模拟。为了对40nm工艺下inv_8单元的单粒子效应进行模拟及分析,如图4所示,实验模拟的不足后包括:(1)用virtuoso软件画出了inv_8_a、inv_8_b和inv_8_c单元版图;(2)基于版图给出的连接关系和单元之间的间距,将所画版图转换为三维tcad模型;(3)用let为37mev

·

cm2/mg的重离子分别轰击标准单元的pmos晶体管和nmos晶体管的漏极中心;(4)观察let为37mev

·

cm2/mg时,重离子轰击产生的节点的脉冲宽度变化。本实施例中得到的结果如下:

51.(1)在40nm工艺下,用轰击能量let=37mev

·

cm2/mg的重离子分别轰击未加固和采用无缝阱/衬底接触加固的inv_8单元的漏极中心。与未加固的单元相比,采用无缝阱/衬底接触加固的单元所产生的set脉冲宽度在一定程度上减小。其中pmos器件set脉冲减少了47.3%,nmos器件set脉冲减少了17.9%。

52.(2)在40nm工艺下,用轰击能量let=37mev

·

cm2/mg的重离子分别轰击未加固和采用分割有源区加固的inv_8单元的漏极中心。与未加固的单元相比,采用分割有源区加固的单元所产生的set脉冲宽度减小。其中pmos器件set脉冲减少了39.2%,nmos器件set脉冲减少了69.6%。

53.(3)在40nm工艺下,用轰击能量let=37mev

·

cm2/mg的重离子分别轰击未加固和采用结合分割有源区和无缝阱/衬底接触加固的inv_8单元的漏极中心。与未加固的单元相比,采用结合分割有源区和无缝阱/衬底接触加固的单元所产生的set脉冲宽度更窄。其中pmos器件set脉冲减少了64.9%,nmos器件set脉冲减少了72.7%。

54.本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可读存储介质(包括但不限于磁盘存储器、cd

‑

rom、光学存储器等)上实施的计算机程序产品的形式。本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

55.以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。